Изобретение относится к вычислительной технике, в частности к устройствам распределения заданий между процессорами, и может быть использовано в многомашинных вычислительных системах для распределения нагрузки между процессорами (ЭВМ).

Целью изобретения является расширение области применения и повышение отказоустойчивости за счет возможности перераспределения запросов абонентов от отказавших процессоров через общую магистраль.

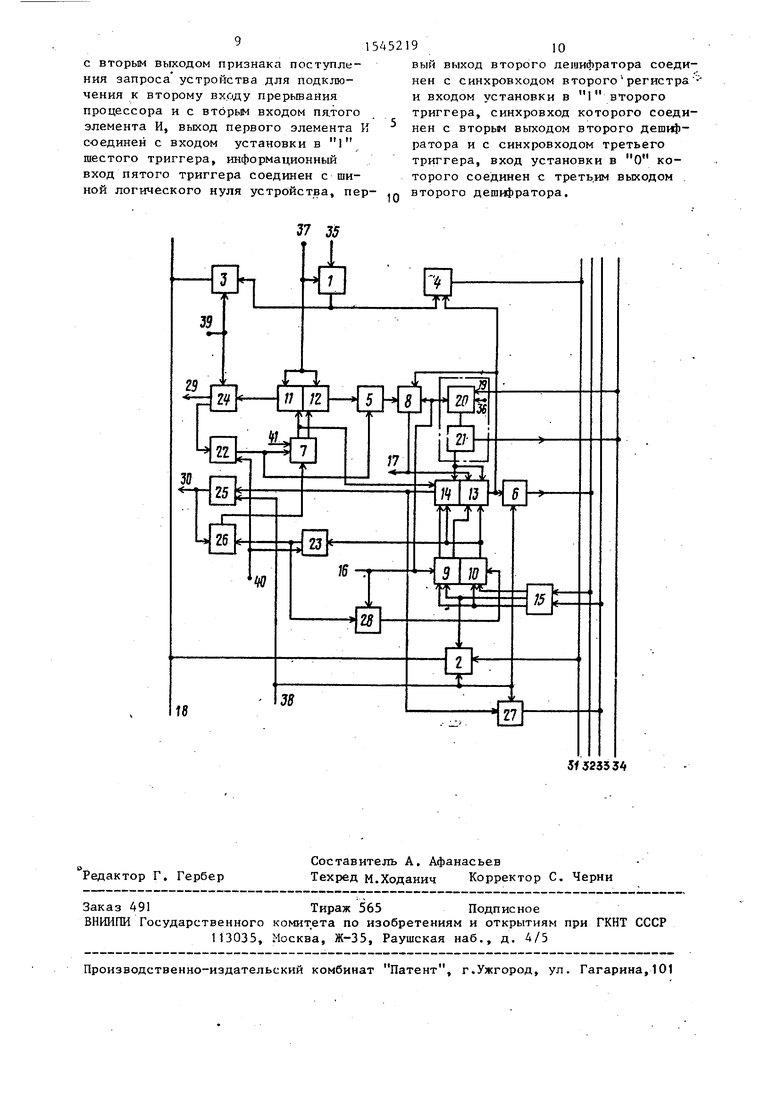

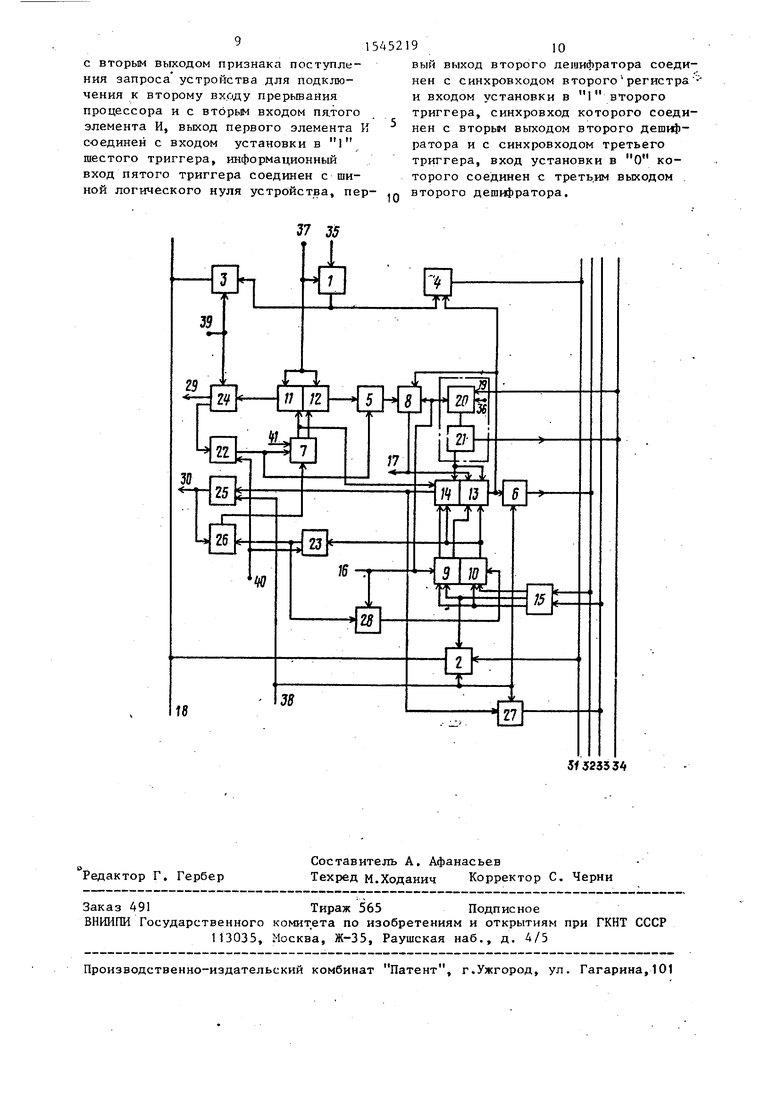

На чертеже представлена структур- «.дя схема (одного канала устройства).

Канал устройства содержит регистры 1 и 2, группы элементов И (магистральные усилители) 3 и 4, элемент ИЛИ 5 и 6, триггеры 7-10, элементы И 11-14, дешифратор 15, вход 16 начальной установки, сигнальный выход 17 готовности, кодовый выход 18 канала устройства, распределитель 19 импульсов, содержащий счетчик 20 и дешифратор 21, счетчики 22 и 23, триггеры 24 и 25 запроса, элемент И 26, ИЛИ 27 и 28, сигнальные выходы 29 и 30, общую магистраль 31, общие линии 32-34, кодовый вход 35 канала, вход 36 синхронизации распределителя 19 импульсов, вход 37 запроса, управляющие входы 38 и 39 чтения, синхровход 40 канала, вход 41 установки триггера 7.

Устройство работает следующим образом.

Для начальной установки подается сигнал на вход 16, при этом в триггеры 8 и 9 записьюается О, в триггер 10 - 1, а счетчик 20 устанавливается в исходное нулевое состояние .

Запрос от К-го источника запросов (абонента) заносится в регистр 1

с входа 35 по сигналу 37. Если К-и процессор, закрепленный для обслуживания запросов от К-го абонента, исправен, о чем свидетельствует состояние триггера 7, то через элемент И 11 по сигналу 37 в триггер 24 записываете я 1 и подается сигнал на вход 29 прерывания К-го процессора. Код запроса процессор счи- тывает с регистра 1 через группу элементов ИЗ по сигналу 39, при этом в триггере 24 записывается О. Если К-й процессор неисправен, о чем свидетельствует состояние триггера 7, то по синналу на входе 37 через элемент И12 и элемент ИЛИ 5 производится запись 1 в триггер 8. Единичное состояние триггера 8 К-го канала соответствует запросу от К-го канала устройства на перераспределения запросов от К-го абонента через общую магистраль 31. Распределители 19 импульсов всех каналов последовательно циклически перебирают числа от 0 до М (М - число каналов), причем состояния счетчиков 20 распределителя 19 импульсов различных каналов совпадают, так как для их работы используется одинаковая частота с входа 36.

.Если в триггере 8 К-го канала имеется 1 и счетчик 20 находится в К-м состоянии, при котором на К-м выходе дешифратора 21 и выходе распределителя 19 К-го канала появляется 1, то при О состоянии триггера 9 на выходе элемента И 13 формируется сигнал, по которому через группу элементов И 4 код запроса с регистра 1 К-го канала выдается на общую магистраль 31. По сигналу с выхода элемента И13 через элемент ИЛИ7 на линию 32 выдается 1, на линии 33 в это время имеется О,

так как при О состоянии триггера 9 на выходе элемента HI 4 - О. При 1 на линий 32 и О на линии 33 возбуждается первый выход дешифратора 15, и в триггеры 9 записывается 1 при этом состоянии триггеров 9 и 1 0 блокируется формирование единицы на выходе элемента И 13, в результате чего блокируется передача запросов че- рез общую магистраль 31. При состоянии триггеров 9 и 10 начинает- .ся поиск процессора, способного принять на обслуживание запрос, переданный через общую магистраль 31 и

Q Q 5 Q

Q ,

5

0

занесенный в регистры 2 всех каналов по сигналу на первом выходе дешифратора 1 5.

При (К + 1)-м состоянии счетчика 20, если (К + 1)-й процессор исправен (в триггере 7 имеется 1), то на выходе элемента появляется сигнал 1 записи в триггер 25. При состоянии триггера 25 на выход 30 требования прерьюания процессора соответствующего канала выставляется сигнал. Если процессор (К + 1)-го канала не исправен, то при (К + 2)-м состоянии счетчика 20 проверяется исправен ли процессор (К + 2)-го канала и т.д. По сигналу на выходе элемента И14, вырабатываемого при выделении процессора, загружаемого на выполнение запроса, переданного через общую магистраль 31 , кроме выдачи этому процессору требования прерывания на вход 30, Производится выдача 1 на линию 33 через элемент ИЛИ27. При этом, так как триггер 9 в состоянии, на выходе элемента И13 и на линии 32 имеется О, в результате чего возбуждается второй выход дешифратора 15. По сигналу на втором выходе дешифратора 15 триггер 10 устанавливается в состояние,- блокирующее прохождение сигналов через элемент Ш4 (прохождение сигналов через элемент И13 блокируется сохраненной состоянием триггера 9).

Процессор, получивший требование приема запроса, распределенного через общую магистраль 31, с выхода 30 считывает код запроса с регистра 2 по сигналу с входа 38, при этом в триггер 25 записывается О и через элементы ИЛИ 5 и 27 на линии 32 и 33 выставляются 1, в результату чего возбуждается третий выход дешифратора 15, устанавливающий триггеры 9 и 10 в исходное состояние 01, при котором расрешается распределение через общую магистраль 31 запросов от абонентов неисправных процессоров.

Выдача запросов абонентов с входа 35 в регистр 1 разрешена при О в триггере 8.

Для исключения рассогласования ра боты счетчиков 20 при достижении счетчиком 20 какого-либо канала максимального кода М через выход 18 на линию 34 выдается сигнал установки

51

счетчика 20 всех каналов н исходное состояние.

Неисправность процессора определяется по отсутствию реакции на запрос прерывания с выхода 29 в течение заданного времени, определяемо jro коэффициентом пересчета счетчика 22 (сторожевого таймера) и частоты на входе 40. Считается, что, если

процессор в течение указанного времени производит считывания кода запроса с регистра 1, то он исправен, если нет, то не исправен. При требовании прерывания н триггер 24 за- писывается 1, при этом снимается уровень установки счетчика 22 и разблокируется его счетный режим. Но сигналу 39 чтения содержимого регистра 1 считывается через группу элементов К 3, при этом в триггер 24 записывается О. При О в триггере 24 в счетчик 22 записывается О, а счетный режим блокируется. Если за заданный интервал времени считывания содержимого регистра 1 по сигналу 39 не производится, то по сигналу переноса счетчика 22 в триггер 7 записывается О, чем фиксируется факт отказа процессора. По сигналу переноса счетчика 22 в триггер 24 записывается О, а в триггер 8 - 1. При записи 1 в триггер 8 выставляется требование на перераспре- деление запроса через общую магистраль. При формировании сигнала на выходе элемента И 13 производится распределение запроса, занесенного в регистр 1, через общую магистраль 31, как это рассмотрено выше. Второй счетчик 23 предназначен для идентификации отказа процессора по отсутствию его реакции в течение заданного интервала времени на запрос, перераспределенный через общую магистраль 31 .

Счетный режим счетчика 23 разблокируется после передачи запроса с регистра 1 канала, отказавшего процессора, через общую магистраль 31 при записи О в триггер 10. Если в течение заданного интервала -времени (определяемого коэффициентом пересчета счетчик 23 и частотой на входе 40) запрос принят в один из процессоров (т.е. произошло чтение кода запроса с регистра 2 по сигналу чтения на входе 38), то по сигналу 38 чтения и передаче через линии 32

д

5 0

5

0

5

0

5

0

5

9

н 33 кода 11 по сигналу на третьем

выходе дешифратора 1 5 в триггеры 9 ; и 10 всех каналов устанавливаются в состояние 01, при котором счетный режим счетчиков 23 блокируется. Если за заданный интервал времени сигнала Подтверждения приема запроса не передается (сигнал 11 через линии 34 и 33), то на выходе переноса счетчика 23 всех каналов формируется сигнал, по которому во всех каналах триггер 10 устанавливается в -е состояние (триггер 9 в 1), разрешающее формирование сигнала на выходе элемента И14. При этом реализуется распределение запроса, занесенного в регистры 2, в один из исправных процессоров, как это описано выше. (Продолжается поиск процессора, способного принять запрос, распределенный через общую магистраль). По сигналу переноса счетчика 23 канала, процессор которого получил запрос на прерывание с выхода 30, происходит запись О в триггер 7, чем фиксируется факт отказа процессора соответствующего канала. Сигнал переноса счетчика 23 передается на вход обнуления триггера 7 через элемент И26, открытый при состоянии триггера 25.

Формула изобретения

Многоканальное устройство для распределения заданий процессорам, со держащее К (где К - число процессоров) каналов, каждый из которых содержит первую и вторую группы элементов И, первый и второй регистры, первый счетчик, первый и второй дешифраторы, с первого по третий триггеры, с первого по четвертый элементы К, первый и второй элементы ИЛИ, причем вход запроса каждого канала устройства соединен с синхровходами первого регистра, информационный вход которого соединен с входом кода запроса канала и является входом устройства, первый вход чтения кода запроса которого является входом устройства для подключения к одноименному выходу процессора и соединен с первыми входами элементов И первой группы, выходы которых объединены по схеме МОНТАЖНОЕ ИЛИ с соответствующими выходами второго регистра и являются информационным выходом канала устройства для подключения к информационному входу процессора,вход начал.нон установки устройства соединен с входами установки в О первого и второго триге- геров и первого счетчика, выход которого соединен с входом первого дешифратора, первый выход которого соединен с первыми входами первого и второго элементов И, второй вход пер вого элемента И соединен с прямым выходом второго триггера, инверсный выход которого соединен с вторым входом второго элемента И, вход третьего триггера соединен с третьими входами первого и второго элементов И, выход второго элемента И соединен с первым входом первого элемента ИЛИ, с синхровходом первого триггера и первыми входами элементов И второй группы, вторые входы которых соединены с вторыми входами элементов И первой группы и с соответствующими выходами первого регистра, выходы элементов И второй группы всех каналов объединены по схеме МОНТАЖНОЕ ИЛИ и соединены с соответствующими информационными входами вторых регистров всех каналов устройства, вторые выходы первых дешифраторов всех каналов устройства объединены по схема МОНТАЖНОЕ ИЛИ и соединены с входами управления записью первых счетчиков всех каналов устройства, выходы первых элементов ИЛИ объединены по схеме МОНТАЖНОЕ 1 1ПИ и соединены с первыми входами вторых дешифраторов всех каналов устройства, выходы вторых элементов ИЛИ всех каналов объединены по схеме МОНТАЖНОЕ ИЛИ и соединены с вторыми входами вторых дешифраторов всех каналов устройства, в каждом канале второй вход чтения кода запроса канала является выходом устройства для подключения к одноименному выходу процессора и соединен с вторым входом первого и первым входом второго элемента ИЛИ, второй вход второго элемента ИЛИ соединен с выходом первого элемента И, четвертый вход второго элемента И соединен с выходом первого триггера, информационные входы первого и второго триггеров и первого счетчика соединены с шиной логического нуля устройства, первый тактовый вход канала устройства соединен с с уммируклним входом перво0

0

5

0

5

0

5

0

5

го счетчика, информационный вход третьего триггера соединен с тиной логической единицы устройства, о т - л и ч а ю щ е е с.я тем, что, с целью расширения области применения и повышения отказоустойчивости устройства за счет возможности перераспределения запросов абонентов от отказавшего процессора, в каждый канал введены второй и третий счетчики, третий и четвертый элементы ИЛИ, с четвертого по шестой триггеры, пятый элемент И, причем вход запроса канала устройства соединен с первыми входами третьего и четвертого элементов И, выходы которых соединены соответственно с входом установки в 1 четвертого триггера и с первым входом третьего элемента ИЛИ, выход которого соединен с вхо- дом установки в 1 первого триггера, второй вход третьего триггера ИЛИ соединен с входом установки в О пятого триггера и с выходом пе- репопнения третьего счетчика, вход блокировки которого соединен с инверсным выходом четвертого триггера, пятый выход и выход установки в О которого соединены соответственно с первым выходом признака поступления запроса устройства для подключения к первому входу прерывания процессора и с первым входом чтения кода запроса канала устройства, прямой выход пятого триггера соединен с вторым входом третьего и четвер- тцм входом первого элементов И, второй вход четвертого элемента И соединен с инверсным выходом пятого триггера, синхровход которого соединен с выходом пятого элемента И, первый вход которого соединен с выходом переполнения четвертого счетчика и первым входом четвертого элемента ИЛИ, второй вход которого соединены соответственно с входом начальной установки канала устройства и с входом установки в 1 третьего , прямой выход которого соединен с входом блокировки четвертого счетчика, суммирующие входы третьего и четвертого счетчиков соединены с вторым тактовым входом канала устройства, второй вход чтения кода запроса которого соединен с входом разрешения чтения второго регистра и с входом установки в О шестого триггера, выход которого соединен

37 35

1

7

39

30

10

TL

Изобретение относится вычислительной технике и может быть использовано в многомашинных вычислительных системах для распределения нагрузок между ЭВМ. Цель - расширение области применения и повышение отказоустойчивости за счет возможности перераспределения запросов абонентов от отказавшихся процессоров. Многоканальное устройство для распределения заданий процессорам содержит K(K - число процессоров) каналов, каждый из которых содержит две группы элементов И, два регистра, шесть триггеров, пять элементов И, четыре элемента ИЛИ, два дешифратора, три счетчика . 1 ил.

| Устройство для распределения заданий процессорам | 1983 |

|

SU1124309A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1471191A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-23—Публикация

1987-06-11—Подача