Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных системах и локальных сетях для распределения нагрузки между процессорами (ЭВМ).

Цель изобретения - повышение производительности за счет конвейерного распределения запросов через общую магистраль при перегрузках отдельных процессоров.

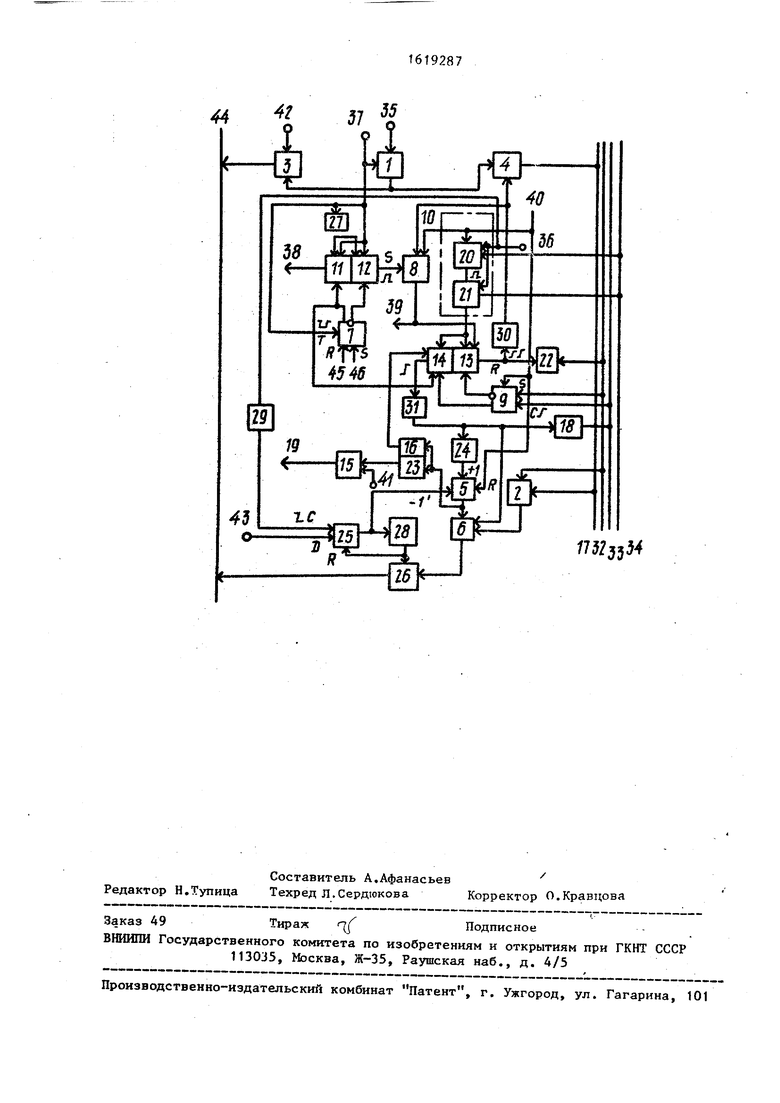

На чертеже представлена структурная схема одного канала устройства.

Устройство содержит в каждом канале регистры 1 и 2, группы элементов И 3 и 4, счетчик 5, блок 6 памяти, триггеры 7-9, распределитель 10 импульсов, элементы И 11-15, эле- мент И-НЕ 16, информационные магистрали 17, элемент 18 развязки,выход 19 признака наличия запросов, счетчик 20, дегаифратор 21, формирователь 22 импульса, элемент ИЛИ 23, формирователь 24 импульса, триггер 25, группу элементов И 26, элементы 27-29 задержки, формирователи 30 и 31 импульсов,общие линии 32-34, вход 35 кода запроса, синхровход 36, вход 37 запроса, выход 38 запроса, выход .39 признака перераспределения запроса, вход 40 начальной установки, вход 41 чтения признака наличия запросов, вход 42 чтения кода запроса, вход 43 чтения кода перераспределения запроса, выход 44 кода запроса, вход 45 признака занятости процессора, вход 46 признака освобождения процессора канала устройства.

о

го

00

л

10

15

20

Устройство работает следующим образом.

Для начальной установки подается сигнал на вход 40, при этом триггеры 8 и 9 и счетчики 5 и 20 устанавливаются в нулевое состояние.

Запрос от К-го источника запро- сов (абонента) заносится в регистр 1 с входа 35 по сигналу 37 при нулевом состоянии триггера 8, выход которого подключен к сигнальному выходу 39 канала.

Если К-й процессор, закрепленный для обслуживания запросов К-го абонента, способен принять запрос (не перегружен), о чем свидетельствует единичное состояние триггера 7, то через элемент И 1 по сигналу 37 подается сигнал на выход 38 (на вход прерывания К-го процессора). Код запроса (ректор прер.гаания) считывается процессором с регистра 1 через группу элементов И по сигналу 42„

Если К-й ттроцессор не способен принять запрос (перегружен), о чем свидетельствует нулевое состояние триггера 7, то по сигналу на входе 37 при записи кода запроса в регистр 1 через элемент И 12 производился за-, пись 1 в триггер 8.

Для исключения появления укороченного сигнала как на выходе элемента И 11, так и на выходе элемента И 12 при переброске триггера 7 в случае прихода сигнала на входы 37 и 45 или 46 - запись в триггер 7 разрешается при отсутствии сигнала на входе 37. Для этого вход 37 подключен к Т-входу триггера 7, работа входов которого разрешена при низком уровне на Т-входе. Элемент 27 обеспечивает задержку сигнала на время срабатывания триггера 7 (по перед25

35

40

ется одинаковая частота синхрониза ции с входа 36. Если в триггере 8 К-го канапа 1 и счетчик 20 находится в К-м состоянии, при котором К-и выход дешифратора и соответственно выход распределителя 10 им пульсов возбужден, то при нулевом состоянии триггера 9 с выхода элемента И 13 на формирователе 30 фор мируется сигнал, по которому через группу элементов И 4 код запроса регистра 1 К-го канала выдается на С общую магистраль 17.По сигналу ,на выходе элемента И 13 на формироват ле 22 импульса вырабатывается сигн сопровождения запроса,выдаваемый на общую линию 32, по которому код запроса с общей магистрали 17 запи сывается в регистр 2 всех каналов, в триггеры 9 всех каналов при этом записываются 1. По сигналу на вы ходе элемента И 13 производится на формирователе 30 формирование импу са установки в О триггера 8 К-го канала, выдавшего запрос на общую магистраль. При единичном состояни триггера 9 блокируется формировани сигнала на выходе элемента И 13 и разрешается на выходе элемента И 1 при этом передача запросов через о щую магистраль 17 блокируется.

При единичном состоянии триггеров 9 начинается поиск процессора, способного принять на обслуживание запрос, переданный через общую магистраль 17 и занесенный в регистры 2 всех каналов. При К-м состоянии счетчика 20 сигнал на выходе элемента И 14 не формируется, так как в триггере 7 К-го канала ,0. При К+1-м состоянии счетчика 20, если К+1-ч способен принять запрос (в триггере 7 1) и блок 6 памяти канему фронту), снятие сигнала с входа ., нала не переполнен (на выходе эле50

37 вызывает блокировку работы элементов И 11 и 12 без задержки.

Единичное состояние триггера 8 (сформированное по сигналу с выхода элемента И 12) К-го канала соответствует запросу от К-го канала на перераспределение запроса от К-го абонента через общую магистраль 17.

Распределители 10 импульсов всех каналов последовательно циклически перебирают числа от 0 до М (М - чис- 55 ло каналов), причем состояния счетчиков 20 и распределителей 10 совпа- Дыют, так как для их работы использумента И-ИЕ 16 1), то с формирователя 31 вырабатывается сигнал, по которому код запроса с регистра 2 записывается в блок 6 памяти по адресу со счетчика 5. По заднему фрон ту сигнала с формирователя 31 на фо мирователе 24 импульса вырабатывает ся сигнал, увеличивающий содержимое счетчика 5 на 1. При переполнении блока 6 памяти на выходе элемента И-НЕ 16 появляется О, блокирующий дальнейшее занесение запросов в бло 6 памяти этого канала. Сигнал с фор мирователя 31 канала, принявшего за

0

5

0

5

5

0

ется одинаковая частота синхронизации с входа 36. Если в триггере 8 К-го канапа 1 и счетчик 20 находится в К-м состоянии, при котором К-и выход дешифратора и соответственно выход распределителя 10 импульсов возбужден, то при нулевом состоянии триггера 9 с выхода элемента И 13 на формирователе 30 формируется сигнал, по которому через группу элементов И 4 код запроса регистра 1 К-го канала выдается на С общую магистраль 17.По сигналу ,на выходе элемента И 13 на формирователе 22 импульса вырабатывается сигнал сопровождения запроса,выдаваемый на общую линию 32, по которому код запроса с общей магистрали 17 записывается в регистр 2 всех каналов, в триггеры 9 всех каналов при этом записываются 1. По сигналу на выходе элемента И 13 производится на формирователе 30 формирование импульса установки в О триггера 8 К-го канала, выдавшего запрос на общую магистраль. При единичном состоянии триггера 9 блокируется формирование сигнала на выходе элемента И 13 и разрешается на выходе элемента И 14, при этом передача запросов через общую магистраль 17 блокируется.

При единичном состоянии триггеров 9 начинается поиск процессора, способного принять на обслуживание запрос, переданный через общую магистраль 17 и занесенный в регистры 2 всех каналов. При К-м состоянии счетчика 20 сигнал на выходе элемента И 14 не формируется, так как в триггере 7 К-го канала ,0. При К+1-м состоянии счетчика 20, если К+1-ч способен принять запрос (в триггере 7 1) и блок 6 памяти ка0

5

мента И-ИЕ 16 1), то с формирователя 31 вырабатывается сигнал, по которому код запроса с регистра 2 записывается в блок 6 памяти по адресу со счетчика 5. По заднему фронту сигнала с формирователя 31 на формирователе 24 импульса вырабатывается сигнал, увеличивающий содержимое , счетчика 5 на 1. При переполнении блока 6 памяти на выходе элемента И-НЕ 16 появляется О, блокирующий дальнейшее занесение запросов в блок 6 памяти этого канала. Сигнал с формирователя 31 канала, принявшего за5 16

прос, через элемент 18 развязки передается на линию 33, при этом триггеры 9 всех каналов устанавливаются в нулевое состояние, при котором разрешается распределение через общую магистраль 17 следующего запроса.

Процессоры через элемент И 15 по сигналу 41 опрашивают состояние блоков 6 памяти. Если в блоке 6 памяти есть запросы, т.е. на выходе элемента ИЛИ 23 1, то процессор считывает запрос, занесенный в блок 6 памяти с общей магистрали последним. Для этого процессор подает сигнал на вход 43. По сигналу на входе 43 после установки триггера 25 содержимое счетчика 5 уменьшается на 1, в результате формируется адрес ячейки, хранящей запрос, занесенный в блок 6 памяти последним. После формирования адреса в счетчике 5 по сигналу с выхода элемента 28 задержки производится через элементы И 26 считывание кода запроса с блока памяти 6. По следующему сигналу на входе 43 после уменьшения содержимого счетчика 5 на 1 по сигналу с выхода элемента 28 задержки производится считывание следующего запроса и т.д. При нулевом состоянии счетчика 5 (запросов нет) на выходе элемента ИЛИ 23 - О и считывание запроса не производится.

Для исключения одновременного появления импульсов на входах +1 и -1 счетчика 5 занесение- 1 в триггер 25 при 1 на входе 43 произво-. дится по заднему фронту импульса синхронизации с входа 36, задержанному на элементе 29. На вход -1 счетчика 5 поступает сигнал при 1 в триггере 25, с задержкой на элементе 28 по этому сигналу производится запись О в триггер 25. Описанная процедура осуществляется при отрицательном полупериоде синхронизации с входа 36. По переднему фронту синхроимпульса на входе 36 (положительный полупериод) производится увеличение на содержимого счетчика 20 и выдача сигнала с дешифратора 21 (вход разрешения дешифратора подключен к синхровходу 36), Так как по сигналу на выходе элемента И 14 производится переброска триггера 9 и формирование заднего фронта сигнала на выходе элемента И 14, то сигнал на вход -Н счетчика 5 поступает в положительный

92876

полупериод синхронизации (или не позднее, чем появляется сигнал на выходе элемента 29 задержки), чем обеспечивается разделение по времени работы входов -Н и -1 счетчика 5.

Для исключения рассогласования работы счетчиков 20 при достижении счетчиком 20 какого-либо канала мак- jg симального кода М на линию 34 выдает- , ся сигнал установки счетчиков 20 всех каналов в исходное нулевое состояние.

Формула изобретения

15

Многоканальное устройство для распределения заданий процессорам, содержащее в каждом канале первый и второй регистры, первую и вторую группы

элементов И, с первого по пятый элементы И, с первого по четвертый триггеры, элемент ИЛИ, первый и второй счетчики и дешифратор, информационный вход которого соединен с выходом первого счетчика, счетный вход которого соединен с синхровходом канала устройства, вход запроса которого соединен с первыми входами первого и второго элементов И и с синхровходом

первого регистра, информационный

вход которого соединен с входом кода запроса канала устройства, выходы первого регистра соединены с первыми входами элементов И первой и второй

групп, вторые входы элементов И вто- рой группы соединены с входом чтения кода запроса канала устройства,выходы элементов И второй группы соединены с выходами кода запроса канала устройст,ва, вход признака занятости процессора которого соединен с входом установки в О первого триггера, инверсный выход которого соединен с вторым входом второго элемента И, первый выход

дешифратора соединен с первыми входами третьего и четвертого элементов И, выход второго триггера соединен с вторым входом четвертого элемента И, прямой выход первого триггера соединен

с вторыми входами первого и третьего элементов И,вторые выходы дешифраторов всех каналов объединены через МОНТАЖНОЕ ИЛИ и соединены с входами установки в О первых счетчиков всех каналов устройства, выходы элементов И первой группы всех каналов устройства объединены через МОНТАЖНОЕ ИЛИ и соединены с информационными входямн вторых регистров всех каналов устройства выход второго триггера каждого канала устройства соединен с выходом признака перераспределения запроса каьа- ла устройства, вход начальной установ- ки которого соединен с входами установки в О первого счетчика, второго и третьего триггеров, отличающееся тем, что, с целью повышения производительности за счет кон-JQ вейерного распределения запросов че- рез общую магистраль при перегрузках отдельных процессоров, каждый канал устройства содержит третью группу элементов И, элемент И-НЕ, блок памя- (5 ти, с первого по третий элементы задержки, с первого по четвертый формирователи импульсов, элемент развязки, причем вход запроса канала устройства соединен с входом перво- JQ го элемента задержки и со стробиру- ющим входом первого триггера,вход установки в 1 которого соединен с входом признака освобождения процессора канала устройства, выход перво- 25 го элемента задержки соединен с третьими входами первого и второго элементов И, выходы которого соединены соответственно с выходом запроса канала устройства и с входом установ- JQ ки в 1 второго триггера, выход первого формирователя импульсов соединен с первыми входами элементов И первой группы и с синхровходом второго триггера, входы первого и второго формирователей импульсов соединены с выходом четвертого элемента И, третьи входы третьего и четвертого элементов И соединены соответственно с прямым и инверсным выходами третье- .Q го триггера, четвертый вход и выход третьего элемента И соединены соответственно с выходом элемента И-НЕ и с входом третьего формирователя импульса, синхровход канала устрой- ства соединен со стробирующим входом дешифратора и с входом второго элемента задержки, выход которого соединен

35

5 Q Q

5

с синхровходом четвертого триггера, выход которого соединен с вычитающим входом второго счетчика и входом третьего элемента задержки, выход которого соединен с входом установки в О четвертого триггера и с первыми входами элементов И третьей группы, вторые входы и выходы которых соединены соответственно с выходами блока памяти и с выходами кода запроса канала устройства, вход признака чтения перераспределенного запроса которого соединен с информационным входом четвертого триггера, информационный вход блока памяти соединен с выходом второго регистра, выход четвертого формирователя импульса соединен с суммирующим входом второго счетчика М (где М - разрядность счетчика) выходов которого соединены с М адресными входами блока памяти, с М входами элемента И-НЕ и с М входами элемента ИЛИ, выход которого соединен с первым входом пятого элемента И, второй вход и выход которого соединены соответственно с входом чтения признака наличия запросов и выходом признака наличия запросов канала устройства, вход начальной установки которого соединен с входом установки в 0 второго счетчика, выходы вторых формирователей импульсов всех каналов устройства объединены через МОНТАЖНОЕ ИЛИ и соединены с входами установки в 1 третьих триггеров и синхровхода- ми вторых регистров всех каналов устройства, выход третьего формирователя импульсов каждого канала устройства соединен с входом четвертого формирователя импульсов, с входом записи блока памяти и с входом элемента развязки, выходы элементов развязки всех каналов устройства объединены через МОНТАЖНОЕ ИЛИ и соединены с синхровхо- дами третьих триггеров всех каналов устройства.

fltfjjW

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для распределения заданий процессорам | 1988 |

|

SU1711171A2 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1471191A1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1427368A1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1545219A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1989 |

|

SU1730632A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для подключения источников информации к общей магистрали | 1989 |

|

SU1679498A1 |

| Многоканальное устройство приоритета | 1988 |

|

SU1501057A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1987 |

|

SU1439612A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1988 |

|

SU1580386A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных системах для распределения нагрузки между процессорами. Цель изобретения - повышение производительности путем конвейерного распределения запросов через общую магистраль при перегрузках отдельных процессоров. Устройство содержит два регистра, три группы элементов И, два счетчика, дешифратор, четыре триггера, пять элементов И, элемент ИЛИ, элемент И-НЕ, три элемента задержки,блок памяти, четыре формирователя импульса, элемент развязки. Цель изобретешь достигается благодаря распределению запроса от абонента (в случае перегрузки соответствующего абоненту процессора) к другому - незагруженному - процессору через общую магист-, раль. 1 ил. а S

| Устройство для распределения заданий процессорам | 1983 |

|

SU1124309A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1545219A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1988-03-17—Подача