1

Изобретение относится к вычислительной технике, в частности к устройствам распределения заданий меяэду процессорами, и может быть использовано в многомашинных вычислительных системах для распределения нагрузки между процессорами.

Цель изобретения - расширение области применения устройства путем обеспечения возможности перераспределения заданий процессорам б учетом их функциональных возможностей.

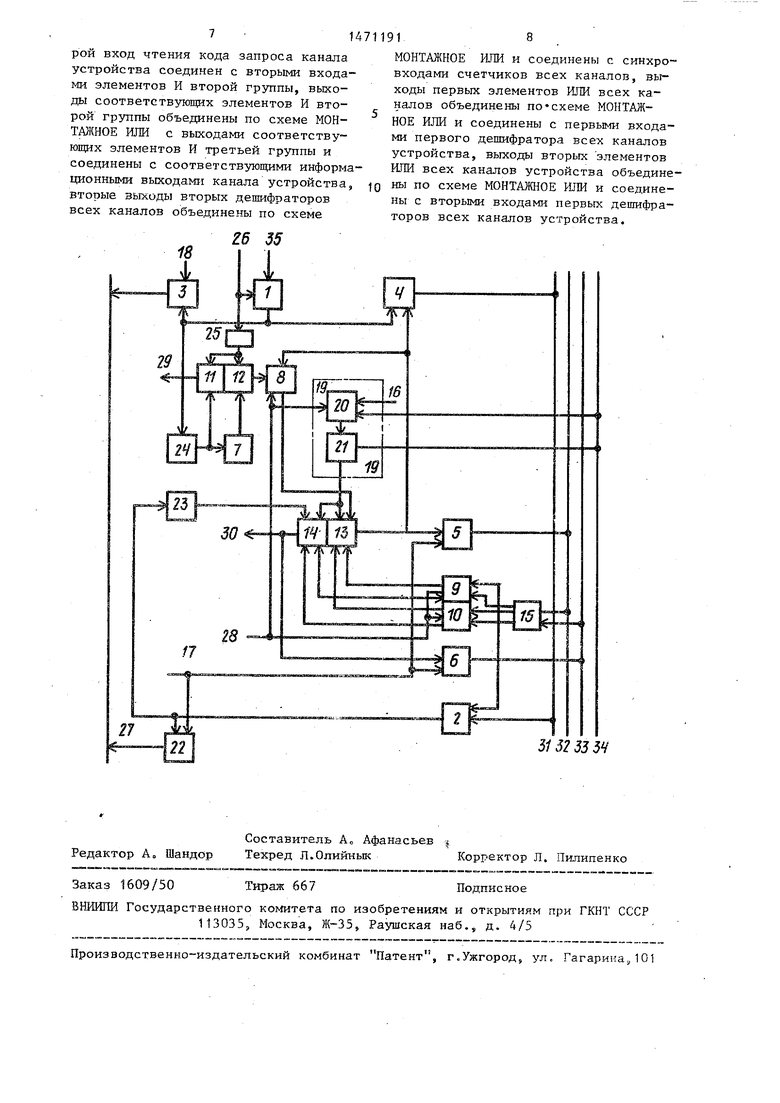

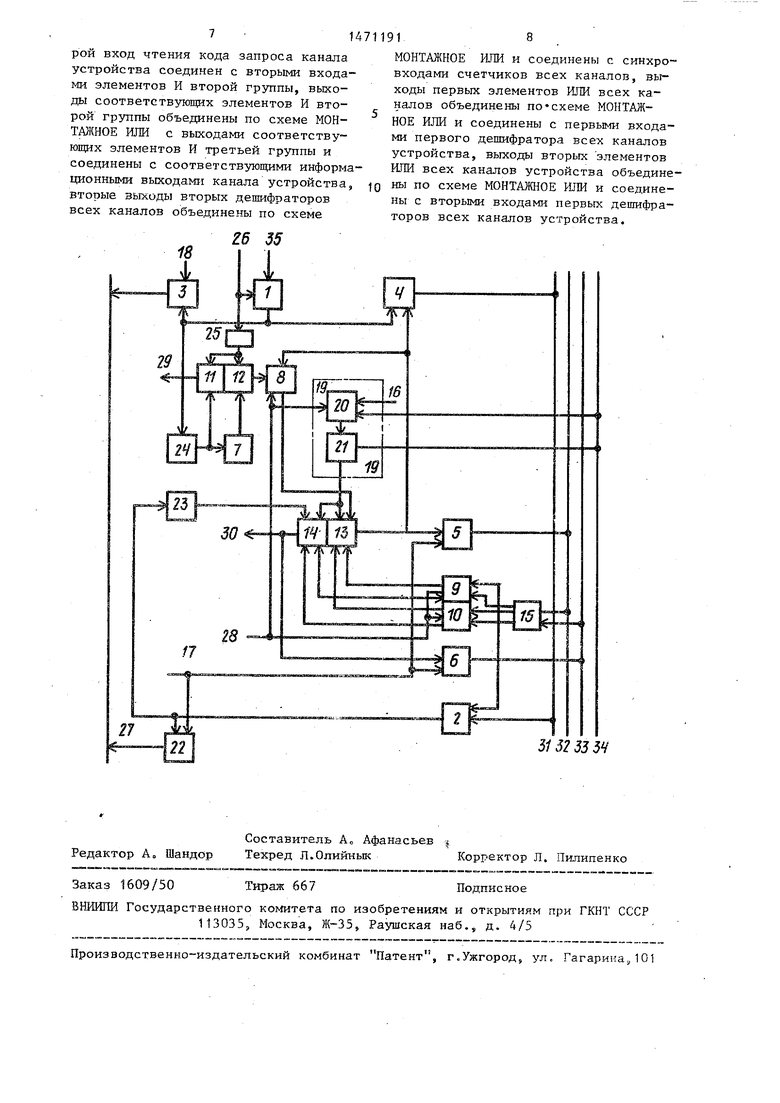

На чертеже приведена структзфная схема устройства (одного канала).

Канал устройства содержит регистры 1 и 2, группы элементов И 3 и 4, элементы ИЛИ 5 и 6, НЕ 7, триггеры 8-10, элементы И 11-14, дешифратор 15, тактовьй вход 16 канала, первьй 17 и второй 18 входы чтения кода запроса канала, распределитель 19 им-

пульсов, содержащий счетчик 20 и дешифратор 21, канал нмегт третью группу элементов И 22, блоки 23 и 24 памяти, элемент 25 задержки, вход 26 запроса, информационный выход 27 канала, вход 28 начальной установки, сигнальные выходы 29 и 30, общую магистраль 31, общие линии 32-34, кодовый вход 35 запроса канала.

Устройство работает следующем образом,

В блоке 24 памяти К-го канала отображается информация о способности К-го процессора вьшолнить запросы на выполнение функций f,, f, ..., f|. Цри этом, если К-й процессор способен выполнить запрос i-ro типа , по i-му адресу блока 24 памяти записывается 1, если нет - О.

В блоке 23 памяти отображается способность К-го процессора приниN{

мать запросы на выполнение функций

f , , перераспределяемых

через общую магистраль 31 от других процессоров. Если по i-i-iy адресу - 1, процессор первого канала способен принять запрос i-ro типа, перерас- пределяемьш через общую магистраль 31, если О - не способен. Обычно информация в блоках 23 и 24 памяти совпадает, но в ряде случаев для регулирования нагрузки процессоров в блоке 23 памяти возможно маскирование приема процессором К-го кана

каналов совпадают, так как для их работы используется одинаковая частота.

Если в триггере 8 К-го канала 1 и счетчик 20 находится в К-м состоянии, при котором на К-м выходе дешифратора 21 и выходе распределителя 19 К-го канала появляется 1, при О состоянии триггеров 9 и 10 на , выходе элемента И 13 формируется сигнал, по которому через группу элементов И 4 код запроса с регистра 1 К-го канала вьщается на общую магист-

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для распределения заданий процессорам | 1988 |

|

SU1619287A1 |

| Многоканальное устройство для распределения заданий процессорам | 1988 |

|

SU1711171A2 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1545219A1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1427368A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1508227A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения электронной вычислительной машины с общей магистралью | 1987 |

|

SU1411765A1 |

| Процессор для сопряжения цвм с каналами передачи данных | 1978 |

|

SU744541A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1986 |

|

SU1354199A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных системах для перераспределения нагрузки между процессорами. Цель изобретения - расширение области применения за счет возможности перераспределения запросов с учетом функциональных возможностей процессоров. Многоканальное устройство для распределения заданий процессорам содержит к (к-число процессоров) каналов, каждый из которых содержит счетчик, два дешифратора, два регистра, четыре элемента И, элемент НЕ, элемент задержки, два элемента ИЛИ, три триггера, три группы элементов ИЛИ, два блока памяти. 1 ил.

ла некоторых типов запросов, перерас- раль 31. По сигналу с выхода элеменпределяемых через общую магистраль 31 ,

Для начальной установки подается сигнал на вход 28, при этом в триггеры 8-10 записываются О, а счетчик 20 устанавливается в нулевое состояние.

Запрос от К-го источника запросов (абонента) заносится в регистр 1 с входа 35 по сигналу на входе 26, при О в триггере 8.

ЕСЛИ К-и процессор, закрепленный для обслужива:ния запросов от К-го абонента, способен выполнить запрашиваемую функцию, код которой зане-. сен в регистр 1 и подается на адресный вход блока 24 памяти, при считывании с блока 24 памяти 1 к моменту появления сигнала с входа 26 на выходе элемента 25 задержки (задержка равна времени записи, кода запроса в регистр 1 и чтения с блока 24 памяти по новому адресу. На выходе элемента И 11 появляется сигнал,;подаваемый на вход 29 прерьтания К-го процессора.

Код запроса процессор считывает с регистра 1 через группу элементов И 3 по сигналу 38. Если К-й процессор не способен выполнить запрос f, по сигналу с выхода элемента 25 задержки при О на выходе блока 24 памяти и 1 на выходе элемента НЕ 7 через элемент И 12 производится запись 1 в триггер 8.

Единичное состояние триггера 8 К-гЪ канала соответствует запросу от К-го канала устройства на перераспределение запроса от К-го абонента через общую магистраль 31. Распреде- лители 19 импульсов всех каналов по- (следовательно циклически перебирают числа от О до М (М - число каналов), причем состояния счетчиков 20 распределителей 19 импульсов различных

20

25

30

35

40

45

50

55

та И 13 через элемент ИЛИ 5 на линию 32 вьщается 1, на линии 33 в это время имеется О, так как при О на линии 33 возбуждается первый выход дешифратора 15 и в триггеры 9 и -10 записывается 1,, при этом состоянии триггеров 9 .и 10 блокируется формирование едини;ц 1 на выходе элеме та И 13 и передача запросов через общую магистраль 31. При состоянии триггеров 9 и 10 начинается поиск процессора, способного принять на обслуживание запрос, переданный через общую магистраль и занесенньй в регистры 2 всех .кангшов по сигналу на первом выходе дешифратора 15.

При (К+1)-м состоянии счетчика 20 если (К+1)-и процессор способен выполнить запрос, занесенный с магистрали 31 в регистр 2, на выходе блока. 23 памяти и на выходе элемента И 14 появляется сигнал, постзгпающий на выход 30 требованияс прерывания процессора соответств тощего канала. Если процессор (К+1)-го канала не способен выполнить запрос, распределенный через магистраль 31, при (К+1)-м состоянии счетчика 20 проверяется, способен ли процессор (К+1)-го канала принять запрос и т.,д. По сигналу на выходе элемента И 14, вырабатьша- емого при вьщелении процессора, загружаемого на выполнение запроса, переданного через магистраль 3 кроме вьэдачи этому процессору требования прерьшания на вход 30, производится вьщача 1 на линию 33 через элемент ИЛИ 6. Так как триггер 9 в состоянии, на выходе элемента И 13 и на линии 32 - О, в результате чего возбуждается второй выход дешифратора 15. По сигналу на втором выходе дешифратора 15 триггер 10 устанавливается в состояние, бло раль 31. По сигналу с выхода элемен0

5

0

5

0

5

0

5

та И 13 через элемент ИЛИ 5 на линию 32 вьщается 1, на линии 33 в это время имеется О, так как при О на линии 33 возбуждается первый выход дешифратора 15 и в триггеры 9 и -10 записывается 1,, при этом состоянии триггеров 9 .и 10 блокируется формирование едини;ц 1 на выходе элемента И 13 и передача запросов через общую магистраль 31. При состоянии триггеров 9 и 10 начинается поиск процессора, способного принять на обслуживание запрос, переданный через общую магистраль и занесенньй в регистры 2 всех .кангшов по сигналу на первом выходе дешифратора 15.

При (К+1)-м состоянии счетчика 20, если (К+1)-и процессор способен выполнить запрос, занесенный с магистрали 31 в регистр 2, на выходе блока. 23 памяти и на выходе элемента И 14 появляется сигнал, постзгпающий на выход 30 требованияс прерывания процессора соответств тощего канала. Если процессор (К+1)-го канала не способен выполнить запрос, распределенный через магистраль 31, при (К+1)-м состоянии счетчика 20 проверяется, способен ли процессор (К+1)-го канала принять запрос и т.,д. По сигналу на выходе элемента И 14, вырабатьша- емого при вьщелении процессора, загружаемого на выполнение запроса, переданного через магистраль 31, кроме вьэдачи этому процессору требования прерьшания на вход 30, производится вьщача 1 на линию 33 через элемент ИЛИ 6. Так как триггер 9 в состоянии, на выходе элемента И 13 и на линии 32 - О, в результате чего возбуждается второй выход дешифратора 15. По сигналу на втором выходе дешифратора 15 триггер 10 устанавливается в состояние, блокируклцее прохождение сигналов через элемент И 14 (прохождение сигналов через элемент И 13 блокируется сохра ненным состоянием триггера 9), Процессо|), получивший требование приема запроса, распределенного через общую магистраль 31, с входа 30 считывает код запроса с регистра 2 через элементы И 22 по сигналу с входа 17, при этом через элементы ИЛИ 5 и 6.на линиях 32 и 33 выставляются 1, в результате чего возбуждается третий выход дешифратора 15, устанавливающий триггеры 9 и 10 в исходное состояние 00, при котором разрешается распределение через общую магистраль 31 запросов от абонентов неисправных процессоров. Для исключения рассогласования работы счетчиков 20 (при достижении счетчиком 20 какого-либо канала максимального кода М) на линию 34 выдается сигнал установки счетчиков 20 всех каналов в исходное состояние.

Формула изобретения

М 1огоканальное устройство для распределения заданий процессорам, содержащее К каналов (К - число процессоров) , каждый из которых содер- . жит первый и второй, регистры, первую и вторую группы элементов И, с первого по четвертый элементы И, первый и второй триггеры, счетчик, первый и второй дешифраторы, первый и второй элементы ИЛИ,, причем в каждом канале вход кода запроса канала устройства соединен с информационным входом регистра, синхровход которого соединен с входом запроса канала устройства, выходы первого регистра соединены с первыми входами элементов И первой и второй групп, выходы первого и второго элементов И соединены соответственно с первым выходом признака обращения к процессору канала устройства и входом установки в 1 первого триггера, выходы одноименных элементов И первых групп всех каналов устройства объединены по схеме МОНТАЖНОЕ ИЛИ и соединены с соответствующими информационными входами вторых регистров кангшов устройства, отличающееся тем, что, с целью расширения области примене- йия устройства путем обеспечения возможности перераспределения заданий

0

0

5

с учетом функциональных возможностей процессоров, оно дополнительно содержит в каждом канале третий триггер, элемент НЕ, первый и второй блоки памяти, третью группу элементов И, элемент задержки, причем вход запроса канала устройства соединен с входом элемента задержки, выход которого соединен с первыми входами первого и второго элементов И, второй вход второго элемента И соединен с выходом элемента НЕ, вход которого соединен с вторым входом первого элемента И и с выхоg дом первого блока памяти, адресные входы., которого соединены с выходами первого регистра, выход первого триггера соединен с первым входом третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, с вторыми входами элементов И первой группы и с синхровходом первого триггера, вход начальной установки канала устройства соединен с входами установки в О счетчика и с первого по третий триггеров, первый выход первого дешифратора соединен с синхровходом второго регистра и с входами установки в 1 второго

Q и третьего триггеров, синхровходы , которых соединены соответственно с вторым и третьим выходами первого дешифратора, выходы второго регистра соединены с первыми входами элементов И третьей группы и с адресными, входами второго блока памяти, выход которого соединен с первым входом четвертого элемента И, вторые входы третьего и четвертого элементов И соединены с первым выходом второго дешифратора, вход которого соединен с выходом счетчика, синхровход которого соединен с тактовьм входом канала устройства, инверсные выходы второго и третьего триггеров соединены соответственно с третьим и четвертыми входами третьего элемента И, прямые выходы второго и третьего триггеров соединены соответственно с третьим и четвертым входами четвертого элемента И, выход которого соединен с вторым выходом признака обращения к процессору канала устройства и с первым входом второго элемента ИЛИ, вторые входы первого и второго элементов ИЛИ соединены с первым входом чтения кода запроса канала устройства и с вторыми входами элементов И третьей группы, вто-

5

0

5

0

5

рой вход чтения кода запроса канала устройства соединен с вторыми входами элементов И второй группы, выходы соответствующих элементов И второй группы объединены по схеме МОНТАЖНОЕ ИЛИ с выходами соответствующих элементов И третьей группы и соединены с соответствующими информационными выходами канала устройства, вторые выходы вторых дешифраторов всех каналов объединены по схеме

гб 55

25

30

riMH

ШЗЕК&аПБКЛСШВф

МОНТАЖНОЕ ИЛИ и соединены с синхро- входами счетчиков всех каналов, выходы первых элементов ИЛИ всех ка- налов объединены по«схеме МОНТАЖНОЕ ИЛИ и соединены с первыми входами первого дешифратора всех каналов устройства, выходы вторых элементов ШШ всех каналов устройства объедине- ны по схеме МОНТАЖНОЕ ИЛИ и соединены с вторыми входами первьгх дешифраторов всех каналов устройства.

3152335

| Устройство для распределения заданий процессорам | 1983 |

|

SU1124309A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-07—Публикация

1987-05-29—Подача