1

Изобретение относится к импульсной технике и может быть использовано в вычислительной и информационно-измерительной технике.

Целью изобретения является повышение быстродействия устройства.

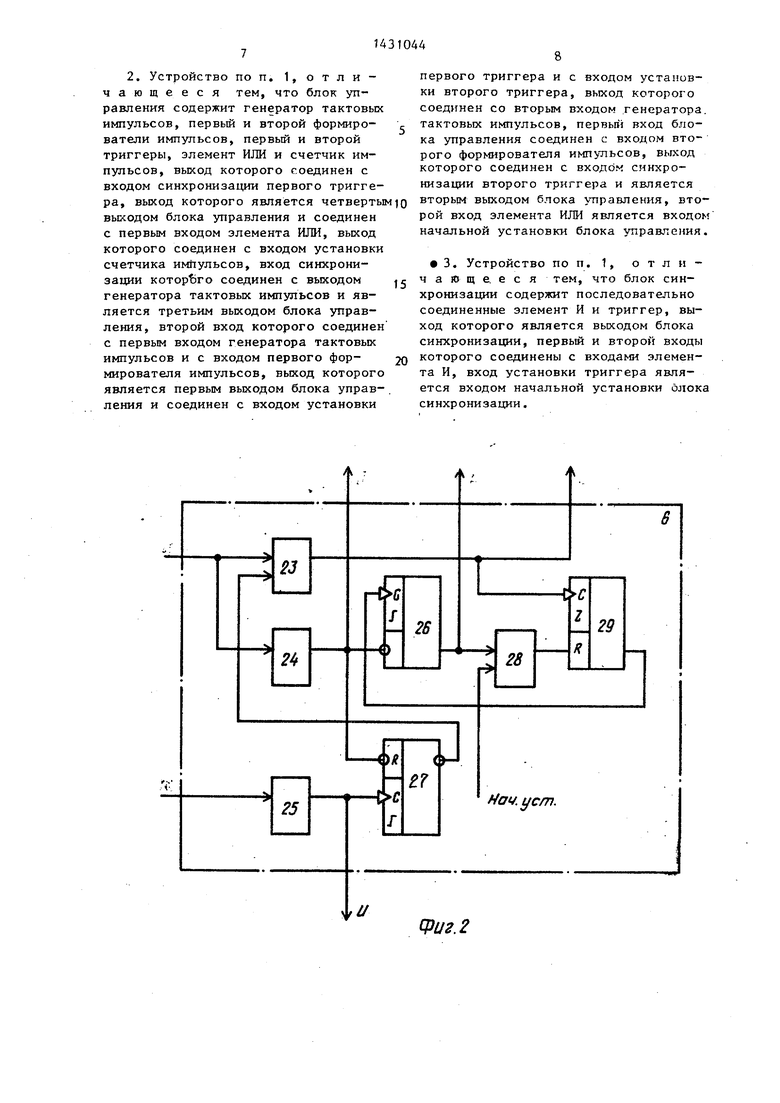

На фиг. 1 представлена структурная схема устройства для определения времени задержки последовательностей; на фиг, 2 и 3 - схемы примеров реализации блока управления и блока синхронизации соответственно

Устройство для определения времени задержки последовательностей (фиг. 1) содержит первый 1 и второй 2 регистры сдвига, первый 3 и второй 4 блоки сравнения, счетчик 5 импульсов, блок 6 управления, блок 7 регист рации, первый .8, второй 9 и третий 10 элементы И, первьй 11 и второй 12 элементы-ЗАПРЕТ, первьй 13, второй 14 и третий 15 элементы ИЛИS триггер 16, первый 17 и второй 18 сумматоры по модулю два, блок 19 синхронизации, первзто 20 и вторую 21 вхрдные шины, группу 22 кодовых шин, соединенных с соответствующими входами первой группы входов второго блока 4 сравнения и с соответствующими входами второй группы входов первого блока 3 сравнения, выход которого соединен с первым входом третьего элемента ИЛИ 15, вькод которого соединен с входом синхронизации триггера 16, выход,кото- рого соединен с первым входом блока 6 управления и с первым входом третьего элемента И 10, вькод которого соединен с входом синхронизации счетчика

0

5 5

0

5

0

., импульсов, выходы которого соединены с ргиформационными входами блока 7 регистрации, вход управления которого соединен с вторым выходом блока 6 управления, первый выход которого соединен с входами установки триггера 16 и счетчика 5 импульсов. Третий выход блока 6 управления соединен с вторым входом третьего элемента И 10,. с входом синхронизации второго регистра 2 сдвига и с входом синхронизации первого регистра 1 сдвига, соответствующие выходы которого соединены с первой группой входов первого блока 3 сравнения и с входами первого сумматора 17 по модулю два, выход которого соединен с первым входом первого элемента И 8, выход которого соединен с первым входом первого элемента ИЛИ 13, выход которого соединен с информационным входом первого регистра 1 сдвига о Второй вход третьего элемента ИЛИ 13s соединен с выходом второго блока 4 сравнения, вторая группа входов которого соединена с соответствующими выходами второго регистра 2 сдвига, соответствующие выходы которого соединены с входами второго сумматора 18 по модулю два, выход которого соединен с первым входом второго элемента И 9, выход которого соединен с первым входом второго элемента ИЛИ 14, выход которого соединен с информационным входом второго регистра 2 сдвига. Вторые входы первого 8 и второго 9 элементов И, инверсные входы первого и ,второго элементов ЗАПРЕТ Ли 12 соединены

между собой и с четвертым выходом блока 6 управле}П1я, второй вход которого соединен с выходом блока 19 синхронизации, первьй и второй входы которого соединены соответственно с первой 20 и второй 21 входными шинами и с прямыми входами первого 11 и второго 12 .элементов ЗАПРЕТ, выходы которых соединены с вторыми входаг-и первого 13 и второго 1А элементов ИЛИ.

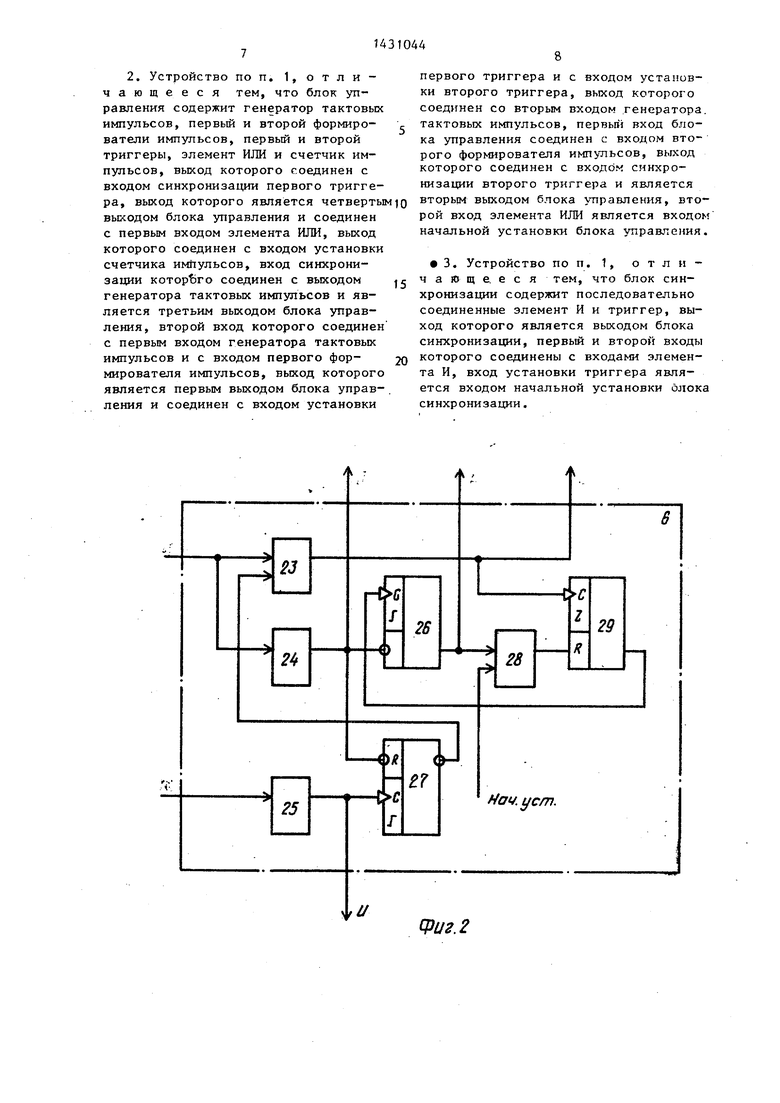

Блок 6 управления (фиг, 2) содержит генератор 23 тактовых импульсов, первый 24 и второй 25 формирователи импульсов, первый 26 и второй 27 триггеры, элемент ИЛИ 28 и счетчик 29 импульсов, выход которого соединен с входом синхронизации первого триггера 26, выход которого является четвертым выходом блока 6 управления и соединен с первым входом элемента ИЛИ 28, выход которого соединен с входом установки счетчика 29 импульсов, вход синхронизации которого соединен с выходом генератора 23 тактовых импульсов и является третьим выходом блока 6 управления, второй вход которого соединен с первым входом генератора 23 тактовых импульсов и с входом первого формирователя 24 импульсов, выход которого является первым выходом блока 6 управления и соединен с входом установки первого триггера 26 и с входом установки второго триггера 27, выход которого соединен с вторым входом генератора 23 тактовых импульсов. Первый вход блокд 6 управления соединен с входом второго формирователя 25 импульсов, выход которого соединен с входом синхронизации второго триггера 27 и является вторым выходом блока 6 управения . Второй вход элемента ИЛИ 28 является входом начальной установки блока 6 управления.

Блок 19 синхронизации (фиг. 3) содержит последовательно соединенные элемент И 30 и триггер 31, выход коорого является выходом блока 19 синронизации, первый и второй входы коорого соединены с входами элемента 30о Вход установки триггера 31 явяется входом начальной установки бло а 19 синхронизации.

Устройство работает следующим обазом.

Сдвинутые относительно друг друт а нализируемые последовательности (в

0

5

5

0

5

0

5

0

5

данном случае ггсевдослучаГшые) x(t) и y(t) подаются на первую 20 и иторую 21 входные 11П1ИЫ, т.е. на входы блока 19 синхронизации и прямые входы первого 11 и второго 12 элементов ЗАПРЕТ, которые закрьп-ы единичным логическим уровнем на их инверсных входах. При включении питания на выходе -блока 19 синхронизации устанавливается нулевой логический уровень и устанавливается в нулевое состояние счетчик 29 импульсов блока 6 управления. На первую группу входов второго блока 4 сравнения и вторую группу входов первого блока 3 сравнения подается с группы 22 кодовых шин параллельный код, соответствующий ключевому слову, образующему последовательности x(t) и y(t). Фронт первого БЫ ;од}1ого импульса блока 19 си гхронизации поступает на второй вход блока 6 управления и запускает его генератор 23 тактовых импульсов. Одновременно на выходе формирователя 24 иг-тульсов появляется сигнал, устанавливающий в ндчальные состояния триггер 16, счетчик 5 импульсов и триггеры 26 и 27 блока 6 управления. Импульсами с третьего выхода блока 6 управления информация с выходов первого 11 и второго 12 элементов ЗАПРЕТ через элементы ИЛИ 13 и 14 соответственно заносится в регистры 1 и 2 сдвига, так как уровень логического нуля с четвертого выхода блока 6 управления открывает (по инверсным входам) элементы ЗАПРЕТ 11 -и 12, .закрывая элементы И 8 и 9, т.е. разрывая обратную логическую связь регистров 1 и 2 сдвига. После заполнения регистров 1 и 2 сдвига (их разрядность равна разрядности регистров генераторов анализи- руемьк последовательностей) импульс с выхода счетчика 29 импульсов блока 6 управления устанавливает его триггер 26 в единичное состояние, т.е. на четвертом выходе блока 6 управления появляется единичный логический уровень, закрывающий элементы ЗАПРЕТ 11 и 12 и открывающий элементы И 8 и 9. В результате этого информационные входы регистров 1 и 2 сдвига подключаются к выходам сумматоров 17 и 18 по модулю два соответственно, т.е. замыкаются цепи логической обратной связи регистров 1 и 2 сдвига, после чего под действием импульсов с третьего выхода блока 6 управления регистры 1 и 2 сдвига с логическими обратными связями (идентичными связям в генераторах, формирующих последовательности x(t) и y(t) соответственно) начинают формировать псевдослучайные последовательности, которые сравниваются с ключевым кодовым словом с группы 22 кодовых шин При совпадении кодов, например, на блоке 3 сравнения на его выходе появляется сигнал 1, устанавливающий триггер 16 в единичное состояние. Единичный сигнал с выхода триггера 16 открывает элемент И 10, разрешая тем самым прохождение импульсов на вход синхронизации счетчика 5 импульсов. При последующем совпадении кодов на блоке 4 сравнения на его выходе формируется импульс, устанавливающий триггер 16 в нулевое состояние, т.е. запрещающий прохождение тактовых импульсов на вход счетчика 5 импульсов. Сигнал О с выхода триггера 16 поступает на первьш вход блока 6 управления, запускает формирователь 25 импульсов, сигнал с выхода которого устанавливает в единичное состояние триггер 27, сигнал с инверс ного (нулевой сигнал) выхода которого запрещает генерацию импульсов генератором 23 тактовых импульсов. Сигнал с выхода формирователя 25 импульсов, т.е. сигнал с второго выхода блока 6 управления, записывает код с выхода счетчика 5 импульсов в блок 7 регистрации. Работа устройства происходит аналогично при срабатьшании сначала (совпадении кодов) блока А сравнения. В последующих циклах измерения устройство работает аналогично

Формула изобретения

1. Устройство для. определения времени задержки последоват.ельностей, содержащее первый регистр сдвига, выходы которого соединены с первой группой входов первого блока сравнения, второй регистр сдвига, блок синхронизации, счетчик импульсов, выходы которого соединены с информационными входами блока регистрации, первую входную иину, отличаю щее- с я тем, что, с целью повьшеиия быстродействия, в него введены второй блок сравнения, блок управления, пер- вьй, второй и третий элементы И, первый и второй элементы ЗАПРЕТ, первьш.

второй и третий элементы ИШ1, первый и второй сумматоры по модулю два, триггер, вторая входная ишна, группа кодовых шин,, соединенных с соответствующими входами первой группы входов второго блока сравнения и с соответствующими вхог.., 1МИ второй rpyinibi входов первого блока сравнения, выQ ход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом синхронизации триггера, выход которого соединен с первым входом блока управления и с первым

5 входом третьего элемента И, выход которого соединен с входом синхронизации счетчика импульсов, вход установки которого соединен с входом установки триггера и с первым выходом блока

0 управления, вход управления блока регистрации соединен с вторым выходом блока управления, третий вькод кото- рого соединен с вторьм входом третьего элемен га И, с входом синхро5 низации второго регистра сдвига и с входом синхронизации первого регистра сдвига, соответствующие выходы которого соединены с входами первого сумматора по модулю два, выход котоQ рого соединен с первым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с информационным входом первого регис.тра сдвига, второй вход третьего элемента ИЛИ соединен с выходом второго блока сравнения, вторая группа входов которого соединена с соответствующими выходами второго регистра сдвига, со0 ответствующие выходы которого соединены с входами второго сумматора по модулю два, выход которого соединен с первым входом второго элемента И, вькод которого соединен с первым вхо5 дом второго элемента ИЛИ, выход которого соединен с информационным входом второго регистра сдвига, вторые входы первого и второго элементов И, инверсные входы первого и второго элементов ЗАПРЕТ соединены между собой и с четвертым выходом блока управления, второй вход которого соединен с выходом блока синхронизации, первый и второй входы которого соединены соответственно с первой и второй входными шинами и с прямыми входами первого и второго элементов ЗАПРЕТ, выходы которых соединены с вторыми входами первого и второго элементов И.ПИ.

5

0

5

2. Устройство по п, 1, отличающееся тем, что блок управления содержит генератор тактовых импульсов, первый и второй формиро- ватели импульсов, первый и второй триггеры, элемент ИЛИ и счетчик импульсов, выход которого соединен с входом синхронизации первого триггера, выход которого является четверты выходом блока управления и соединен с первым входом элемента ИЛИ, выход которого соединен с входом установки счетчика имйульсов, вход синхронизации которого соединен с выходом генератора тактовых импульсов и является третьим выходом блока управления, второй вход которого соединен с первым входом генератора тактовых импульсов и с входом первого фор- мирователя импульсов, выход которого является первым выходом блока управ- ления и соединен с входом установки

первого триггера и с входом установки второго триггера, выход которого соединен со вторым входом генератора, тактовых импульсов, первьи вход блока управления соединен с входом второго формирователя импульсов, выход которого соединен с входом синхронизации второго триггера и является вторьм выходом блока управления, второй вход элемента ИЛИ является входом начальной установки блока управления.

3. Устройство по п. 1, отличающееся тем, что блок синхронизации содержит последовательно соединенные элемент И и триггер, выход которого является выходом блока синхронизации, первый и второй входы которого соединены с входами элемента И, вход установки триггера является входом начальной установки олока синхронизации,

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных последовательностей | 1985 |

|

SU1298868A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| Устройство формирования модифицированных М-последовательностей | 2023 |

|

RU2801743C1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Генератор М-последовательностей | 1989 |

|

SU1676074A2 |

| Генератор псевдослучайных последовательностей | 1988 |

|

SU1636993A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

Изобретение относится к импульсной технике. Цель изобретения - повышение быстродействия. Анализируемые (например, псевдослучайные) последовательности подаются на входные шины 20 и 21, а на группу 22 кодовых шин подается ключевое слово (код) анализируемых последовательностей. Импульсами с блока 6 управления анализируемые последовательности заносятся в регистры 1 и 2 сдвига, после чего сигнал с блока 6 управления открывает элементы И 8 к 9. В результате этого регистры 1 и 2 сдвига подключаются к сумматорам 17 и 18 по модулю два соответственно, образуя генераторы псевдослучайных последовательностей с логическими обратными связями. Эти связи идентичны связям в генераторах, формирующих анализируе- мые последоват,ельности. Под действи- // ем импульсов с третьего выхода блока

и

иг.2

Г

Нач.усгл.

Редактор Т. Лазоренко

Составитель Ю, -Бурмистров

Техред Л Олийньгк Корректор Н.Король

Заказ 5351/55

Тираж 929

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 3035, Москва, Ж-35, Раушская наб., д. 4/5

19

Подписное

| Дифференциальный генератор псевдослучайных импульсов | 1984 |

|

SU1202039A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Алексеев А.Н | |||

| и др | |||

| Теория и применение псевдослучайных сигналов | |||

| М.: Наука, 1969, рис | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1988-10-15—Публикация

1987-02-12—Подача