Изобретение относится к импульсной технике и может быть использовано для диагностирования устройств автоматики и вычислительной техники.

Цель изобретения - повьшение достоверности генерируемых последовательностей.

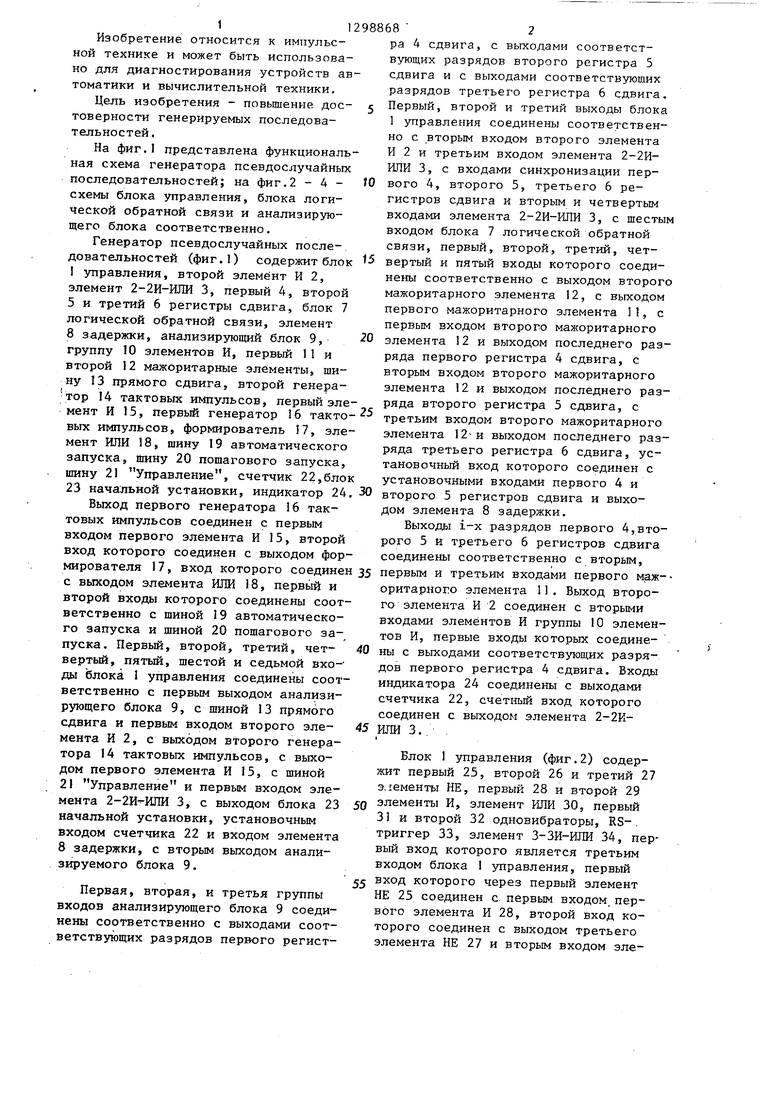

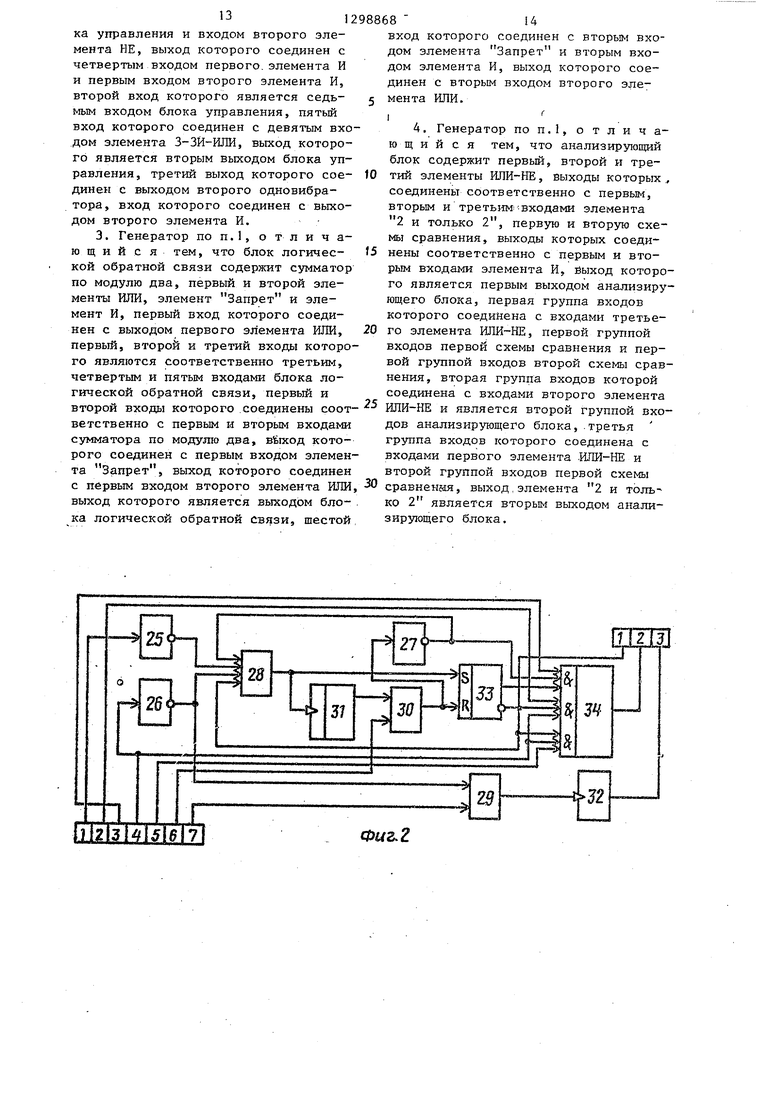

На фиг.1 представлена функциональная схема генератора псевдослучайных последовательностей; на фиг.2 - Д - схемы блока управления, блока логической обратной связи и анализирующего блока соответственно.

Генератор псевдослучайных послеfO

pa 4 сдвига, с выходами соответствующих разрядов второго регистра 5 сдвига и с выходами соответствуюших разрядов третьего регистра 6 сдвига. Первый, второй и третий выходы блока 1 управления соединены соответственно с вторым входом второго элемента И 2 и третьим входом элемента 2-2И- ИПИ 3, с входами синхронизации первого 4, второго 5, третьего 6 регистров сдвига и вторым и четвертым входами элемента 2-2И-ИЛИ 3, с шестым входом блока 7 логической обратной связи, первый, второй, третий, четдовательностей (фиг.1) содержит блок вертый и пятый входы которого соединены соответственно с выходом второго мажоритарного элемента 12, с выходом первого мажоритарного элемента II, с первым входом второго мажоритарного элемента 2 и выходом последнего разряда первого регистра 4 сдвига, с вторым входом второго мажоритарного элемента 12 и выходом последнего разряда второго регистра 5 сдвига, с

1 зшравления, второй элемент И 2, элемент 2-2И-ИЛИ 3, первый 4, второй 5 и третий 6 регистры сдвига, блок 7 логической обратной связи, элемент 8 задержки, анализирующий блок 9, группу 10 элементов И, первый 11 и второй 12 мажоритарные элементы, шину 13 прямого сдвига, второй генера тор 14 тактовых импульсов, первый эле- .. ., ,

мент И 15, первый генератор 16 такто- третьим входом второго мажоритарного вьгх импульсов, формирователь 57, эле- элемента 12 и выходом последнего раз- мент ИЛИ 18, шину 19 автоматического ряда третьего регистра 6 сдвига, ус- запуска, пшну 20 пошагового запуска, тановочный вход которого соединен с шину 21 Управление, счетчик 22,блок установочными входами первого 4 и 23 начальной установки, индикатор 24. ЗО второго 5 регистров сдвига и выхоВыход первого генератора 16 тактовых импульсов соединен с первым входом первого элемента И 15, второй вход которого соединен с выходом формирователя 17, вход которого соединен 35 первым и третьим входами первого маж- с выходом элемента ИЛИ 18, первый и оритарного элемента II. Выход второ- второй входы которого соединены соответственно с шиной 19 автоматического запуска и шиной 20 пошагового запуска. Первый, второй, третий, чет- 40 ны с выходами соответствующих разря- вертый, пятый, шестой и седьмой вхо- дов первого регистра 4 сдвига. Входы ды блока 1 управления соединены соответственно с первьи выходом анализидом элемента 8 задержки.

Выходы i-x разрядов первого 4,второго 5 и третьего 6 регистров сдвига соединены соответственно с вторым.

го элемента И 2 соединен с вторыми входами элементов И группы 10 элементов И, первые входы которых соединеиьщикатора 24 соединены с выходами счетчика 22, счетный вход которого соединен с выходом элемента 2-2И- 45 ИЛИ 3..

рующего блока 9, с шиной 13 прямого сдвига и первым входом второго элемента И 2, с выходом второго генератора 14 тактовых импульсов, с выходом первого элемента И 15, с шиной 21 Управление и первым входом элеиьщикатора 24 соединены с выходами счетчика 22, счетный вход которого соединен с выходом элемента 2-2И- 45 ИЛИ 3..

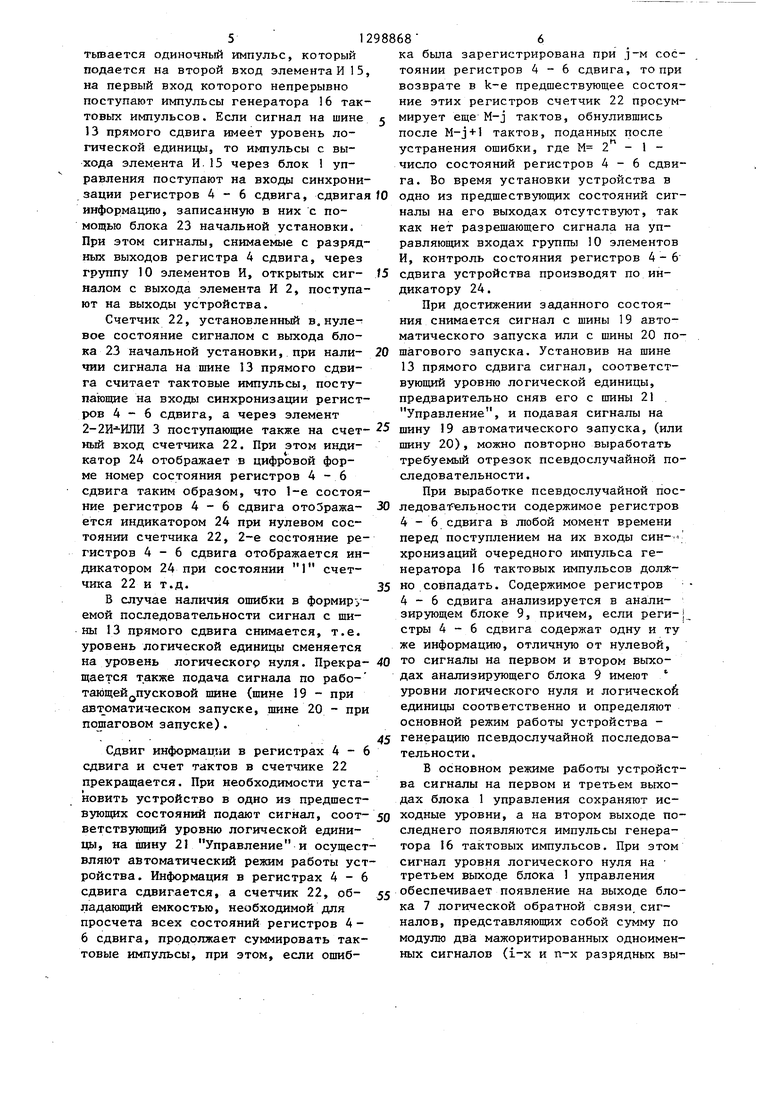

Блок 1 управления (фиг.2) содержит первый 25, второй 26 и третий 27 элементы НЕ, первый 28 и второй 29

мента 2-2И-ИЛИ 3, с выходом блока 23 50 элементы И, элемент ИЛИ 30, первый начальной установки, установочным 31 и второй 32 одновибраторы, RS-.

триггер 33, элемент 3-ЗИ-ИЛИ 34, пер- вьй вход которого является третьим входом блока 1 управления, первый вход которого через первый элемент НЕ 25 соединен с. первым входом, первого элемента И 28, второй вход которого соединен с выходом третьего элемента НЕ 27 и вторым входом злевходом счетчика 22 и входом элемента 8 задержки, с вторым выходом анализируемого блока 9.

Первая, вторая, и третья группы входов анализирующего блока 9 соединены соответственно с выходами соответствующих разрядов первого регист

pa 4 сдвига, с выходами соответствующих разрядов второго регистра 5 сдвига и с выходами соответствуюших разрядов третьего регистра 6 сдвига. Первый, второй и третий выходы блока 1 управления соединены соответственно с вторым входом второго элемента И 2 и третьим входом элемента 2-2И- ИПИ 3, с входами синхронизации первого 4, второго 5, третьего 6 регистров сдвига и вторым и четвертым входами элемента 2-2И-ИЛИ 3, с шестым входом блока 7 логической обратной связи, первый, второй, третий, четнены соответственно с мажоритарного элемент первого мажоритарного первым входом второго элемента 2 и выходом ряда первого регистра вторым входом второго элемента 12 и выходом ряда второго регистра

..

третьим входом второго мажоритарного элемента 12 и выходом последнего раз- ряда третьего регистра 6 сдвига, ус- тановочный вход которого соединен с установочными входами первого 4 и второго 5 регистров сдвига и выхопервым и третьим входами первого маж- оритарного элемента II. Выход второ- ны с выходами соответствующих разря- дов первого регистра 4 сдвига. Входы

дом элемента 8 задержки.

Выходы i-x разрядов первого 4,второго 5 и третьего 6 регистров сдвига соединены соответственно с вторым.

первым и третьим входами первого маж- оритарного элемента II. Выход второ- ны с выходами соответствующих разря- дов первого регистра 4 сдвига. Входы

го элемента И 2 соединен с вторыми входами элементов И группы 10 элементов И, первые входы которых соединепервым и третьим входами первого ма оритарного элемента II. Выход второ ны с выходами соответствующих разря дов первого регистра 4 сдвига. Вход

иьщикатора 24 соединены с выходами счетчика 22, счетный вход которого соединен с выходом элемента 2-2И- ИЛИ 3..

31298868

мента 3-ЗИ-ИЛИ 34, третий вход которого соединен с первым выходом RS- триггера 33, S-вход которого соединен с выходом первого элемента И 28, и входом первого одновибратора 31, Выход последнего соединен с первым входом элемента ИЛИ 30, второй вход которого является шестым входом блока 1 управления, второй вход которого соединен с четвертым входом эле- JO мента 3-ЗИ-ИЛИ 34, пятый вход которого является первым выходом блока 1 управления и соединен с шестьм входом элемента 3-ЗИ-ИЛИ 34, третьим

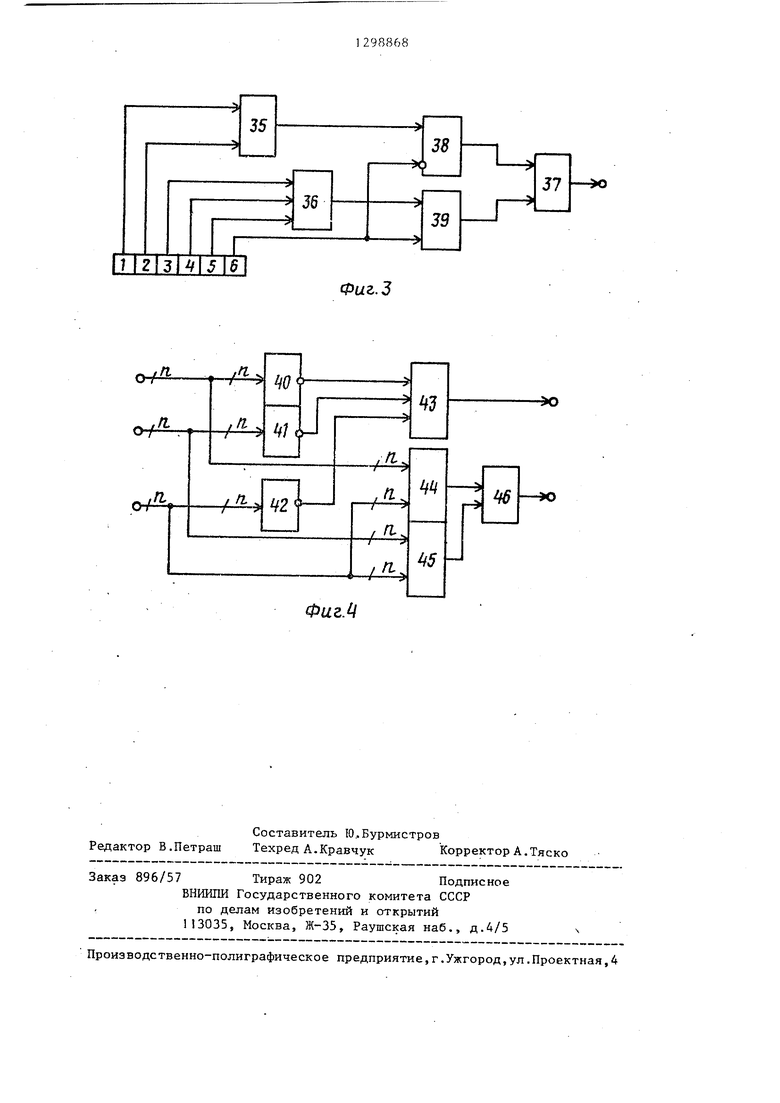

Анализирующий блок 9 (фи1 .4) содержит первый 40, второй 41 и третий 42 элементы ИЛИ-НЕ, выходы которых соединены соответственно с первым, вторым и третьим входами элемента 2 и только 2 43, первую 44 и вторую 45 схемы сравнения, выходы которых соединены соответственно с первым и вторым входами элемента И 46, выход которого является первым выходом анализирующего блока 9, первая группа входов которого соединена с входами третьего элемента ИЛИ-НЕ 42, первой группой входов первой схемы 44 сраввходом первого элемента И 28 и вторым 5 нения и первой группой входов рторой выходом RS-триггера 33, R-вход схемы 45 сравнения, вторая группа

входов которой соединена с входами второго элемента ИЛИ-НЕ 41 и является второй группой входов анализирую- 20

рого соединен с выходом элемента ИЛИ 30 и входом третьего элемента НЕ 27..

Седьмой вход элемента 3-ЗИ-ИЛИ 34 соединен с восьмым входом этого элемента, четвертым входом блока I управления и входом второго элемента НЕ 26, выход которого соединен с четвертым входом первого элемента И 28 -25 ляется вторым выходом анализируюп е- и первым входом второго элемента И 29, го блока 9. второй вход которого является седьмым входом блока 1 управления : пятый вход которого соединен с девятым входом элемента 3-ЗИ-ИПИ 34, выход кото-30 прямого сдвига, шине 19 автоматичес- рого является вторым выходом блока 1 кого запуска, шине 20 пошагового за- управления, третий выход которого соединен с выходом второго одновибратора 32, вход которого соединен с выходом второго элемента И 29.

щего блока 9. Третья группа входов блока 9 соединена с входами, первого элемента ИЛИ-НЕ 40 и второй группой входов первой схемы 44 сравнения. Выход элемента 2 и только 2 43 явГенератор работает следующим образом.

В исходном состоянии на шине 13

пуска и шине 21 Управление сигналы имеют уровень логического нуля сигналом с выхода блока 23 начальной 35 установки счетчик 22 установлен в нулевое состояние, регистры 4-6 сдвига установлены сигналом с выхода блока 23 начальной установки, подаваемым на их установочные входы через элемент 8 задержки, в одинаковые начальные состояния; сигналы на первом и втором выходах анализирующего блока 9 имеют уровни логических нуля и единицы соответственно, сигнал на

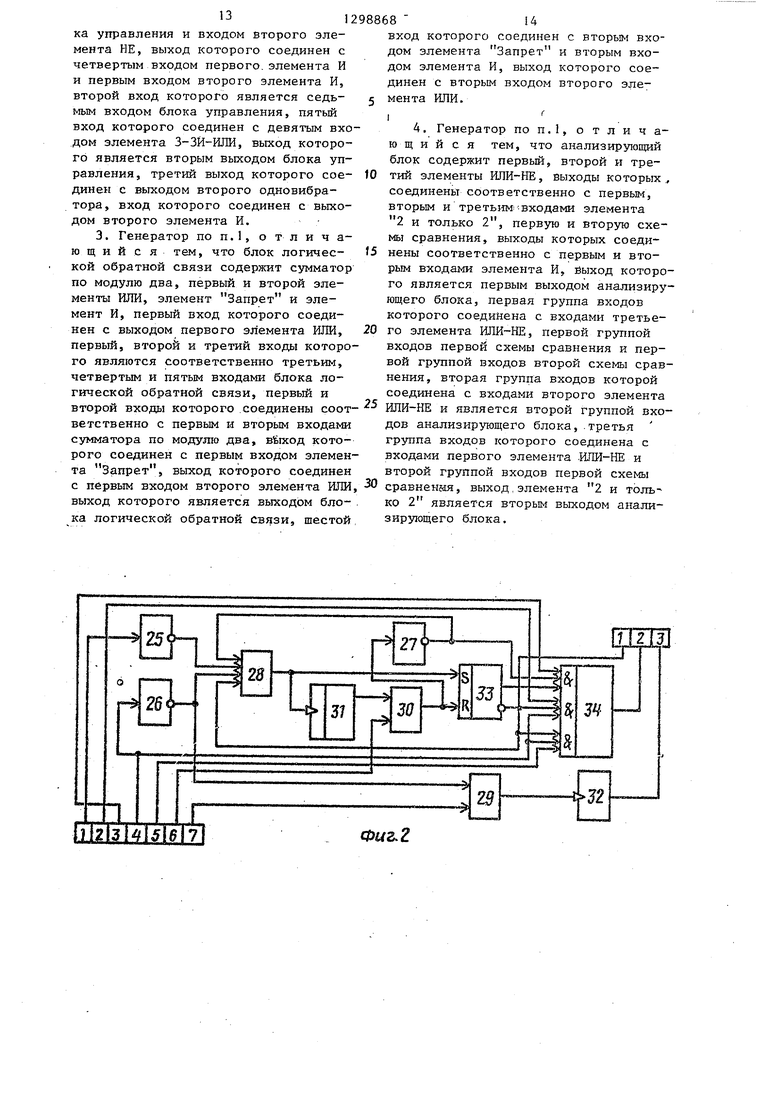

Блок 7 логической обратной связи (фиг.З) содержит сумматор 35 по модулю- два, первый 36 и второй 37 элементы ИЛИ, элемент 38 Запрет и мент И 39, первый вход которого соединен с выходом первого элемента ИЛИ 36. Первый, второй и третий входы

35

пуска и шине 21 Управление сигналы имеют уровень логического нуля сигналом с выхода блока 23 начальной 35 установки счетчик 22 установлен в ну левое состояние, регистры 4-6 сдви га установлены сигналом с выхода бло ка 23 начальной установки, подаваемым на их установочные входы через элемент 8 задержки, в одинаковые начальные состояния; сигналы на первом и втором выходах анализирующего блока 9 имеют уровни логических нуля и единицы соответственно, сигнал на

элемента ИЛИ 36 являются соответственно третьим, четвертым и пятым вхо-45 первом выходе блока 1 управления дами блока 7 логической обратной свя- имеет уровень логический единицы,на зи, первый и второй входы которого соединены соответственно с первым и вторым входами сумматора 35 по модулю два, выход которого соединен с 0 первым входом элемента 38 Запрет,

втором и третьем выходах - логического нуля, сигналы на выходах элемента И 15, элемента И 2, элементов И группы 10 элементов И и элемента 2-2И-ИЛИ 3 имеют уровень логического нуля.

I

При наличии сигнала логической

выход которого соединен с первым входам второго элемента ИЛИ 37, выход которого является выходом блока 7 логической обратной связи, шестой вход 55 единицы на шине 19 автоматического которого соединен с вторым входом эле- запуска или шине 20 пошагового за- мента 38 Запрет и вторым входом эле- пуска на выходе формирователя 17 со- меита И 39, выход которого соединен ответственно или устанавливается уро- с вторым входом второго элементаИПИ 37. вень логической единицы, или вырабаАнализирующий блок 9 (фи1 .4) содержит первый 40, второй 41 и третий 42 элементы ИЛИ-НЕ, выходы которых соединены соответственно с первым, вторым и третьим входами элемента 2 и только 2 43, первую 44 и вторую 45 схемы сравнения, выходы которых соединены соответственно с первым и вторым входами элемента И 46, выход которого является первым выходом анализирующего блока 9, первая группа входов которого соединена с входами третьего элемента ИЛИ-НЕ 42, первой группой входов первой схемы 44 сраввходов которой соединена с входами второго элемента ИЛИ-НЕ 41 и является второй группой входов анализирую-

ляется вторым выходом анализируюп е- го блока 9. прямого сдвига, шине 19 автоматичес- кого запуска, шине 20 пошагового за-

щего блока 9. Третья группа входов блока 9 соединена с входами, первого элемента ИЛИ-НЕ 40 и второй группой входов первой схемы 44 сравнения. Выход элемента 2 и только 2 43 является вторым выходом анализируюп е- го блока 9. прямого сдвига, шине 19 автоматичес- кого запуска, шине 20 пошагового за-

Генератор работает следующим образом.

В исходном состоянии на шине 13

ляется вторым выходом анализируюп е- го блока 9. прямого сдвига, шине 19 автоматичес- кого запуска, шине 20 пошагового за-

пуска и шине 21 Управление сигналы имеют уровень логического нуля сигналом с выхода блока 23 начальной установки счетчик 22 установлен в нулевое состояние, регистры 4-6 сдвига установлены сигналом с выхода блока 23 начальной установки, подаваемым на их установочные входы через элемент 8 задержки, в одинаковые начальные состояния; сигналы на первом и втором выходах анализирующего блока 9 имеют уровни логических нуля и единицы соответственно, сигнал на

первом выходе блока 1 управления имеет уровень логический единицы,на

первом выходе блока 1 управления имеет уровень логический единицы,на

втором и третьем выходах - логического нуля, сигналы на выходах элемента И 15, элемента И 2, элементов И группы 10 элементов И и элемента 2-2И-ИЛИ 3 имеют уровень логического нуля.

I

При наличии сигнала логической

единицы на шине 19 автоматического запуска или шине 20 пошагового за- пуска на выходе формирователя 17 с ответственно или устанавливается у вень логической единицы, или выраб

тьшается одиночный импульс, который подается на второй вход элемента И 15, на первый вход которого непрерывно поступают импульсы генератора 16 тактовых импульсов. Если сигнал на шине 13 прямого сдвига имеет уровень логической единицы, то импульсы с выхода элемента И.15 через блок 1 управления поступают на входы синхронизации регистров 4-6 сдвига, сдвигая W одно из предшествующих состояний сигинформацшо, записанную в них с помощью блока 23 начальной установки. При этом сигналы, снимаемые с разрядных выходов регистра 4 сдвига, через группу 10 элементов И, открытых сиг- налом с выхода элемента И 2, поступают на выходы устройства.

Счетчик 22, установленный в, нуле- вое состояние сигналом с выхода блока 23 начальной установки, при нали- чин сигнала на шине 13 прямого сдвига считает тактовые импульсы, поступающие на входы синхронизации регистров 4-6 сдвига, а через элемент 2-2И-°-Ш1И 3 поступающие также на счет- ный вход счетчика 22. При этом индикатор 24 отображает в цифровой форме номер состояния регистров 4-6 сдвига таким образом, что 1-е состояние регистров 4-6 сдвига отоЗража- ется индикатором 24 при нулевом состоянии счетчика 22, 2-е состояние регистров 4-6 сдвига отображается индикатором 24 при состоянии 1 счетчика 22 и т.д.

В случае наличия ошибки в формир - емой последовательности сигнал с шины 13 прямого сдвига снимается, т.е. уровень логической единицы сменяется

на уровень логического нуля. Прекра- 40 то сигналы на первом и втором выхо- щается также подача сигнала по рабо- Д анализирующего блока 9 имеют тающей пусковой щине (щине 19 - при автоматическом запуске, шине 20 - при

пошаговом запуске).

уровни логического нуля и логической единицы соответственно и определяют основной режим работы устройства - 45 генерацию псевдослучайной последова тельности.

уровни логического нуля и логической единицы соответственно и определяют основной режим работы устройства - 45 генерацию псевдослучайной последовательности.

В основном режиме работы устройства сигналы на первом и третьем выходах блока 1 управления сохраняют исСдвиг информации в регистрах 4-6 сдвига и счет тактов в счетчике 22 прекращается. При необходимости установить устройство в одно из предшествующих состояний подают сигнал, соот- 50 ходные уровни, а на втором выходе по- ветствующий уровню логической едини- следнего появляются импульсы генера- цы, на шину 21 Управление и осущест- тора 16 тактовых импульсов. При этом вляют автоматический режим работы устройства. Информация в регистрах 4-6 сдвига сдвигается, а счетчик 22, обладающий емкостью, необходимой для просчета всех состояний регистров 4 - 6 сдвига, продолжает суммировать таксигнал уровня логического нуля на третьем выходе блока 1 управления обеспечивает появление на выходе блока 7 логической обратной связи сигналов, представляющих собой сумму по модулю два мажоритированных одноименных сигналов (i-x и п-х разрядных вытовые импульсы, при этом, если ошибка была зарегистрирована при -м состоянии регистров 4-6 сдвига, то при возврате в k-e предшествзтощее состояние этих регистров счетчик 22 просуммирует еще M-J тактов, обнулившись после M-J+1 тактов, поданных после устранения ошибки, где М 2 - 1 - число состояний регистров 4-6 сдвига. Во время установки устройства в

налы на его выходах отсутствуют, так как нет разрешающего сигнала на управляющих входах группы 10 элементов И, контроль состояния регистров 4-6 сдвига устройства производят по индикатору 24.

При достижении заданного состояния снимается сигнал с шины 19 автоматического запуска или с шины 20 пошагового запуска. Установив на шине 13 прямого сдвига сигнал, соответствующий уровню логической единицы, предварительно сняв его с шины 21 . Управление, и подавая сигналы на шину 19 автоматического запуска, (или шину 20), можно повторно выработать требуемый отрезок псевдослучайной последовательности.

При выработке псевдослучайной пос- ледова Рельности содержимое регистров 4-6 сдвига в любой момент времени перед поступлением на их входы син- хронизаций очередного импульса генератора 16 тактовых импульсов должно совпадать. Содержимое регистров 4-6 сдвига анализируется в анализирующем блоке 9, причем, если регистры 4-6 сдвига содержат одну и ту же информацию, отличную от нулевой.

то сигналы на первом и втором выхо- Д анализирующего блока 9 имеют

уровни логического нуля и логической единицы соответственно и определяют основной режим работы устройства - генерацию псевдослучайной последовательности.

В основном режиме работы устройства сигналы на первом и третьем выходах блока 1 управления сохраняют исходные уровни, а на втором выходе по- следнего появляются импульсы генера- тора 16 тактовых импульсов. При этом

ходные уровни, а на втором выходе по- следнего появляются импульсы генера- тора 16 тактовых импульсов. При этом

сигнал уровня логического нуля на третьем выходе блока 1 управления обеспечивает появление на выходе блока 7 логической обратной связи сигналов, представляющих собой сумму по модулю два мажоритированных одноименных сигналов (i-x и п-х разрядных вы

ходов регистров 4-6 сдвига соответственно) , ВВОДИ1ЧЫХ в блок 7 логической обратной связи через первый и второй входы последнего с выходов мажоритарных элементов 11 и 12. Если из-за воздействия помехи регистры 4 - 6 сдвига не содержат одну и ту же информацию, отличную от нулевой, хотя бы в двух регистрах, то имеет местО искажение информации первого вида, которому на обоих выходах анализиру- юг;его блока 9 соответствуют сигналы уровня логического нуля. Если же из-за воздействия помехи два любых регистра сдвига обнулились, то имеет место искажение информации второго вида, которому на первом выходе анализирующего блока 9. соответствует уровень логической единицы, а на втором выходе последнего - уровень ло- гического нуля.

Устранение искажений информации осуществляется в режиме коррекции,в который устройство переводится блоком 1 управлен,ия при обнаружении искажений информации. Обнаружение искажений реализуется после поступления на входы синхронизации регистров 4 - 6 сдвига очередного импульса генератора 16 тактовых импульсов путем оп- роса в блоке 1 управления состояний выходов анализирующего блока 9.

В режиме коррекции независимо от вида искажения информации на втором выходе блока управления появляются импульсы генератора 14 тактовых импульсов , а на первом выходе блока 1 управления появляется сигнал, имеющий уровень логического нуля и блокирующий через элемент И 2 выходные сигналы устройства, а через третий вход элемента 3 блокирующий счетный вход счетчика 22 от импульсов генератора 14 тактовых импульсов.

Если блок I управления переводит генератор псевдослучайных последовательностей в режим коррекции при обнаружении искажения информации первого вида, то сигнал на третьем вы- ходе блока 1 управления сохраняет урвень логического нуля, при котором на выходе блока 7 логической обратной связи появляются сигналы, пред- ставляющие собой сумму по модулю два мажоритированных одноименных сигналов (i-x и п-х разрядных выходов регистров 4-6 сдвига соответственнэ)

5

O 0

5

О 5

вводимых в блок 7 логической обратной связи через первый и второй входы последнего с выходом мажоритарных элементов 11 и 12. Если же блок 1 управления переводит генератор псевдослучайных последовательностей в режим коррекции при обнаружении искажения информации второго вида, то сигнал на третьем выходе блока 1 управления имеет уровень логической единицы, при котором сигналы на выходе блока 7 логической обратной связи повторяют сигналы, поступающие на один из входов (третий, четвертый или пятый) последнего с п-го разрядного выхода необнуленного регистра сдвига, так как на два других входа блока 7 логической обратной связи поступают сигналы с п-х разрядных выходов обнуленных регистров сдвига.

Состояния выходов блока 1 управления, соответствующие режиму коррекции, должны сохраняться в течение времени, необходимого для п-кратного сдвига информации, содер,.сащейся в регистрах 4-6 сдвига в момент перевода устройства в режим коррекции, до поступления очередного импульса генератора 16 тактовых импульсов, что обеспечивает восстановление информации (устранение искажений) в регистрах 4-6 сдвига до полного совпадения их содержимого. После устранения искажений блок 1 управления автоматически переходит в исходное состояние и устройство готово к выдаче отрезка псевдослучайной последовательности, в котором бьти обнаружены искажения, и выработке последующих отрезков псевдослучайной последовательности .

Блок 1 управления работает следующим образом. В исходном состоянии RS-триггер 33 установлен в нулевое состояние, сигнал на третьем входе блока 1 управления представляет собой последовательность тактовых импульсов, сигналы на втором, четвертом, пятом, шестом и седьмом входах, втором и третьем выходах блока управления имеют уровень логического нуля, -сигналь: на первом входе и первом выходе блока 1 управления имеют уровень логической единицы, при этом прохождение сигналов с выходов элементов НЕ 26 и 27 и второго нулевого выхода RS-триггера 33, уровень логической единицы, через элемент И 28 блокируется сигналом с выхода элемента НЕ 25, имеющим уровень логического нуля, а сигналом с первого (единичного) выхода RS-триггера 33 заблокировано поступление тактовых импульсов через третий вход блока I управления и первый вход элемента З-ЗИ-ИЛИ 34 на второй выход блока 1 управления.

блока 1 управления имеет уровень логической единицы после запуска второго одновибратора 32, реализуемого через второй элемент И 29, когда сигналы на четвертом и седьмом входах блока 1 управления имеют уровни логического нуля и логической единицы соответственно,

Блок 7 логической обратной связи

Если на второй или пятый вход бло- Ш работает следующим образом. В исход- ка 1 управления подан сигнал, имею- ном состоянии сигналы на входах и вы- щий уровень логической единицы, и на ходе блока 7 логической обратной свячетвертый вход блока 1 управления поступают тактовые импульсы, то через седьмой вход элемента З-ЗИ-ИЛИ 34 тактовые импульсы поступают на второй выход блока 1 управления. С четвертого входа блока 1 управления тактовые импульсы поступают также на вход элемента НЕ 26, инвертирующего эти импульсы, что позволяет поддерживать уровень логической единицы на вьЬюде последнего между двумя ближайшими соседними тактовыми импульсами, поступающими на четвертый вход блока 1 управления. При этом на выходе элемента И 28 появляется сигнал, имеющий уровень логической единицы и переводящий RS-триггер 33 в единичное состояние, при котором блокируется прохождение тактовых импульсов с четвертого входа блока 1 управления на второй выход блока 1 управления, а сигнал на выходе элемента И 28 имеет уровень логического нуля.

В единичном состоянии RS-триггера 33 на втором выходе блока 1 управления появляются сигналы, поступающие через третий вход блока 1 управления на первый вход элемента З-ЗИ-ИЛИ 34., Сигнал, переводящий RS-триггер 33 в единичйое состояние, поступает на вход первого одновибратора 31 с задержкой на входе, что обеспечивает подачу на первый нход элемента ИЛИ 30 импульса, осуществляющего установку через элемент ИЛИ 30 RS-триггера 33 в нулевое состояние, при этом через элемент НЕ 27 блокируется элемент И 28, а по второму входу элемента З-ЗИ-ШШ 34 блокируется поступление сигналов через третий вход блока 1 управления и первый вход элемента З-ЗИ-ИЛИ 34 на второй выход блока 1 управления. RS-триггер 33 устанавливается в исходное состояние также сигналом с шестого входа блока 1 управления. Сигнал на третьем выходе

блока 1 управления имеет уровень логической единицы после запуска второго одновибратора 32, реализуемого через второй элемент И 29, когда сигналы на четвертом и седьмом входах блока 1 управления имеют уровни логического нуля и логической единицы соответственно,

Блок 7 логической обратной связи

5

5

0

зи имеют уровни логического нуля.

Если сигнал на шестом входе блока 7 логической обратной связи имеет уровень логической единицы, то на его выходе сигнал имеет уровень логической единицы, если хотя бы на один из его входов (третий, четвертый, пя- 0 тый) подан сигнал, имеющий уровень логической единицы. Если сигнал на шестом входе блока 7 логической обратной связи имеет уровень логического нуля, то на его выходе появляются сигналы, представляющие собой сумму по модулю два сигналов, поданных на его первый и второй входы.

Анализирующий блок 9 работает следующим образом. Если на входы первой, второй си третьей групп его входов по- атупает одноименная информация, то сигналы на его первом и втором выходах имеют уровни логической единицы и логического нуля соответственно. 5 Если на входы второй, третьей или первой, третьей или первой, второй групп входов анализирующего блока 9 поступает нулевая информация, то сигналы на его первом и втором выходах имеют уровни логического нуля и логической единицы соответственно. Если на входы первой, второй и третьей групп входов анализирующего блока 9 не поступает одноименная информация или последняя поступает лишь на входы второй, третьей или первой, третьей или первой, второй групп его входов, то сигналы на его первом и-втором выходах имеют уровни логического нуля.

Формула изобретения

0

5

0

1. Генератор псевдослучайных пос- ледовательностей, содержащий первый регистр сдвига, выходы разрядов которого соединены с первыми входами элементов И группы элементов И, бло начальной установки, выход которого

П1

соединен с уста}ювочным входом счетчика, выходы разрядов которого соединены с соответствующими входами индикатора, первый генератор тактовых импульсов, выход которого соединен с первым входом первого элемента И,второй вход которого соединен с выходом формирователя, вход которого соедине с выходом элемента ИЛИ, первый и второй входы которого соединены с шиной автоматического запуска и с шиной пошагового запуска соответственно, шину прямого сдвига, шину Управление отличающийся тем, что, с целью повьпиения достоверности генерируемых последовательностей, в него введены второй и третий регистры сдвига, второй элемент И, элемент 2- 2И-ИЛИ, блок управления, элемент задержки, анализирующий блок, второй генератор тактовых импульсов, блок логргческой обратной связи, первьй и второй мажоритарные элементы, выходы которых соединены с вторьм и первым входами соответственно блока логической обратной связи, выход которого соединен с информационными входами первого,второго и третьего ре9 истров сдвига, установочные входы которых соединены с выходом элемента задержки, вход которого соединен с выходом блока- начальной установки и шестым входом блока управления, первый, второй, третий, четвертый, пятый, шес

той и седьмой входы которого со един е--35 вход которого через первый элемент

ны соответственно с первым выходом анализирующего блока, щиной прямого сдвига и первым входом второго элемента И, выходом второго генератора тактовых импульсов, выходом первого элемента И, шиной Управление и первым входом элемента 2-2И-ИЛИ, вторым выходом анализирующего блока, первая группа входов которого соединена с соответствующими выходами разрядов первого регистра сдвига, вход синхронизации которого соединен с входами синхронизации второго и третьего регистров сдвига, вторьм и четвертым входами элемента 2-2И-Ш1И и вторым выходом блока управления, третий выход которого соединен с шестым входом блока логической обратной связи, третий,- четвертьй и пятьй входы которого соединены соответственно с вьгеодом последнего разряда первого регистра сдвига и первым входом второго мажоритарного элемента, с вы15

8868

5 О

0

5

)2

ходом последнего разряда второго регистра сдвига и вторым входом второго мажоритарного элемента, с выходом последнего разряда третьего регистра сдвига и третьим входом второго мажоритарного элемента, первый вход первого мажоритарного элемента соединен с выходом i-ro разряда второго регистра сдвига, выходы разрядов которого соединены с соответствующими входами второй группы входов анализирующего блока, входы третьей группы входов которого соединены с соответствующими выходами разрядов третьего регистра сдвига, выход, i-rc разряда которого соединен с третьим.входом первого мажоритарного элемента, второй вход которого соединен с выходом i-ro разряда первого регистра сдвига, счетный вход счетчика соединен с выходом элемента 2-2И-ИЛИ, третий вход которого соединен с первым выходом блока управления и вторым входом второго элемента И, выход которого соединен с вторыми входами элементов И группы элементов. И.

2. Генератор поп.1,отлича- ю щ и и с я тем, что блок управления содержит первый, второй и третий эле- менты НЕ, первый и второй элементы И, элемент ИЛИ, первый и второй одновиб- раторы, RS-триггер, элемент 3-ЗИ-ШШ, первый вход которого является третьим входом блока управления, первый

0

НЕ соединен с первым входом первого элемента И, второй вход которого соединен с выходом третьего, элемента НЕ и вторым входом элемента З-ЗИ-ИПИ, третий вход которого соединен с первым выходом RS-триггера, S-вход которого соединен с выходом первого элемента И и входом первого одновиб- ратора, выход которого соединен с пер- 5 вым входом элемента ИЛИ, второй вход которого является шестым входом блока управления, второй вход которого соединен с четвертым входом элемента З-ЗИ-ИПИ, пятый вход которого является первым выходом блока управления и соединен с шестым входом элемента 3-ЗИ-ИЛИ, третьим входом первого элемента И и вторым выходом RS-тригге- ра, R-вход которого соединен с выходом элемента liJlH и входом третьего элемента НЕ, седьмой вход элемента 3-ЗИ-ШТИ соединен с восьмым входом этого элемента, четвертым входом бло0

5

ка управления и входом второго элемента НЕ, выход которого соединен с четвертым входом первого.элемента И и первым входом второго элемента И, второй вход которого является седьмым входом блока управления, пятьй вход которого соединен с девятым входом элемента 3-ЗЙ-ИЛИ, выход которого является вторым выходом блока управления, третий выход которого соединен с выходом второго одновибра- тора, вход которого соединен с выходом второго элемента И.

3. Генератор по п.1, о т л и ч а- ю щ и и с я тем, что блок логической обратной связи содержит сумматор по модулю два, nepBbrti и второй элементы ИЛИ, элемент Запрет и элемент И, первый вход которого соединен с выходом первого элемента ШШ, первый, второй и третий входы которого являются соответственно третьим, четвертым и пятым входами блока логической обратной связи, первьй и второй входы которого соединены соот ветственно с первым и вторым входами сумматора по модулю два, в1ьгход которого соединен с первым входом элемента Запрет, выход которого соединен

вход которого соединен с вторым входом элемента Запрет и вторым входом элемента И, выход которого соединен с вторым входом второго эле- 5 мента ИЛИ,

1

4, Генератор по п., о т л и ч аю щ и и с я тем, что анализирующий блок содержит первый, второй и треtO тий элементы ИЛИ-НЕ, выходы которых., соединены соответственно с первым, вторым и третьигм--.входами элемента 2 и только 2, первую и вторую схемы сравнения, выходы которых соедиJ5 нены соответственно с первым и вторым входами элемента И, йыход которого является первым выходом анализирующего блока, первая группа входов которого соединена с входами третье20 го элемента ШШ-НЕ, первой группой входов первой схемы сравнения и первой группой входов второй схемы сравнения, вторая группа входов которой соединена с входами второго элемента - ИЛИ-НЕ и является второй группой входов анализирующего блока, .третья группа входов которого соединена с входами первого элемента .ИЛИ-НЕ и второй группой входов первой схемы

с первым входом второго элемента ИЛИ, - сравнения, выход, элемента 2 и толь- выход которого является выходом бло- . ко 2 является вторым выходом анали- ка логической обратной связи, шестой, зирузощего блока.

1ш1зМШШ

вход которого соединен с вторым входом элемента Запрет и вторым входом элемента И, выход которого соединен с вторым входом второго эле- 5 мента ИЛИ,

1

4, Генератор по п., о т л и ч аю щ и и с я тем, что анализирующий блок содержит первый, второй и треtO тий элементы ИЛИ-НЕ, выходы которых., соединены соответственно с первым, вторым и третьигм--.входами элемента 2 и только 2, первую и вторую схемы сравнения, выходы которых соедиJ5 нены соответственно с первым и вторым входами элемента И, йыход которого является первым выходом анализирующего блока, первая группа входов которого соединена с входами третье20 го элемента ШШ-НЕ, первой группой входов первой схемы сравнения и первой группой входов второй схемы сравнения, вторая группа входов которой соединена с входами второго элемента ИЛИ-НЕ и является второй группой входов анализирующего блока, .третья группа входов которого соединена с входами первого элемента .ИЛИ-НЕ и второй группой входов первой схемы

Фиг.г

M{2l3i l5|g

Фиг.З

ФигМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Преобразователь напряжение-код сКОНТРОлЕМ | 1979 |

|

SU822342A1 |

| Устройство для предварительной обработки изображений | 1989 |

|

SU1654849A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1990 |

|

SU1714607A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Система управления электрическим режимом дуговых электропечей при групповой работе в часы максимума активной нагрузки энергосистемы | 1988 |

|

SU1577083A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

Изобретение относится к импульсной технике и может быть использовано для диагносцирования устройств автоматики и вычислительной техники. Цель изобретения - повышение достоверности генерируемых последовательностей. Устройство содержит регистр 4 сдвига, группу 10 элементов И, элемент И 15, генератор 16 тактовых импульсов, формирователь 17, элемент ИЛИ 18, счетчик 22, блок 23 начальной установки, индикатор 24 и шины 13, 19,20 и 21 прямого сдвига,автоматического запуска,пошагового запуска и Управление соответственно. Для достижения поставленной цели в устрой ство введены блок 1 управления,элемент 2 И,элемент 2-2И-1 ШИ 3,регистры 5 и 6 сдвига,блок 7 логической обратной связи,элемент 8 задержки, анализирующий блок 9, мажоритарные элементы 11 и 12, генератор 14 тактовых импульсов и образованы новые связи между элементами устройства. В описании представлены примеры конкретного выполнения блока 1 управления, блока 7 логической обратной связи и анализиру-- ющего блока 9. 3 з.п. ф-лы, 4 ил. со

| Галкин А.П | |||

| Моделирование кана- лов систем связи | |||

| - М.: Связь, 1979, с.62,63 | |||

| Авторское свидетельство СССР № 756397, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-23—Публикация

1985-11-25—Подача