Изобретение относится к технике связи позволяет повысить достоверность инормации, передаваемой с использованием иклических кодов.

Известно устройство для мажоритарного декодирования циклических кодов при рехкратном повторении комбинации, соержащее последовательно соединенные буферный блок памяти, входы которого соеинены соответственно с третьим, четёерым и пятым выходами анализатора кодовых комбинаций, последовательнЬ соеиненные декодер, анализатор кодовых комбинаций и мажоритарный блок, второй вход которого подключен к второму выходу буферного блока памяти. К первому дополнительному входу мажоритарного блока подключен первый выход декодера, к синхронизирующему входу которого подключен первый выход анализатора кодовых комбинаций, к второму выходу которого подключен второй дополнительный вход мажоритарного элемента, а второй, третий, четвертый, пятый и шестой входы анализатора кодовых комбинаций подключены соответственно к первому выходу буферного блока памяти, дополнительному выходу мажоритарного элемента и выходам блока памяти кодовых, комбинаций результатов декодирования, вход которого подключен к дополнительному выходу декодера. Выходы блока памяти кодовых комбинаций результатов декодирования подключены к управляющим входам мажоритарного элемента, выход которого является выходом устройства.

Недостатком такого устройства Является низкое качество работы в случаях, когда в канале связи присутствуют образцы шума, имитирующие передаваемые кодовые слова, или образЦы шума, вызванные структурной помехой. Такие ситуации характерны для радиоканалов коротковолнового диапазона, когда последние пребывают в состоянии обрыва связи ; в тропосферных и ионосферных каналах за счет наличия отражения передаваемого сообщения от различных слоев атмосферы: в каналах случайного множественного доступа в периоды работы двух или более передатчиков, использующих один и тот же код, повышающий достоверность из-за на)1ичия стандартных унифицированных блоков в аппаратуре передачи.

Так, например, если при передаче по каналу связи одно из трех повторений принято с ошибкой ei, wt(ei) S (d-1)/2, где wt(ei) число единиц в двоичном векторе ei, а при передаче двух других повторений произошли ошибки вида ai Ф ei, где аг - кодовое

слово(n,k)-кoдa, используемого для передачи информации; ei двоичный вектор wt(ei) :S (d-1)/2, , тогда пол учателю выдают сообщение f, равное результату мажоритарной обработки трех сообщений: Со; Со ФСа; Со Ф Сз. где Со информационная часть передаваемого в действительности сообщений. Т.е. f в общем случае не совпадает с Со.

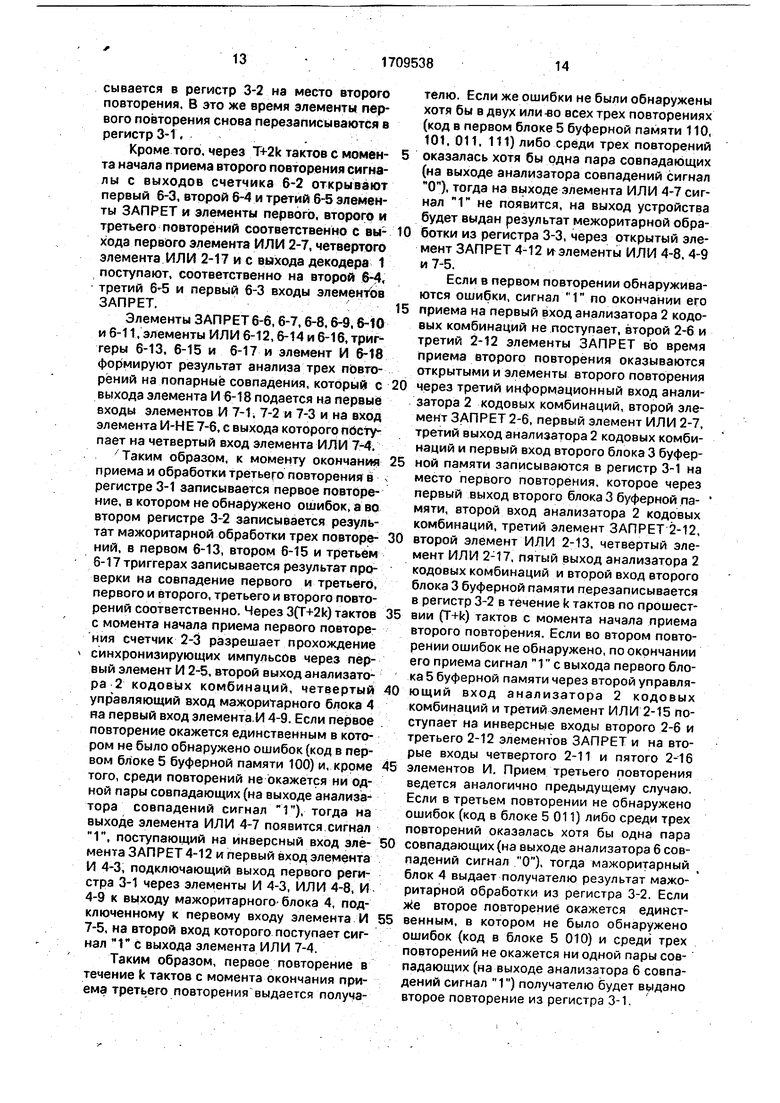

0 Наиболее полно случаи, приводящие к выдаче таким устройством получателю ложной информации, представлены в табл.1, где знаком + обозначены случаи, приводящие к необнаруженной ошибке, а знаком

5 - обозначены случаи верного приема сообщений.

Известно, что для обеспечения заданной гарантированной вероятности необнаруженной ошибки в произвольном канале

0 связи необходимо осуществить два независимых стох|астических преобразования: мультипликативное и аддитивное (универсальное кодирование). Однако для двоичных кодов, исправляющих независимые

5 ошибки, применение стохастического преобразования нецелесообразно, так как за счет выравнивания вероятностей векторов ошибок различных конфигураций на длине кодового слова п, которое происходит

0 вследствие . универсального кодирования, доля векторов с числом единиц t или меньше уменьшается. Это приводит к уменьшению доли исправляемых векторов ошибок кодами заданной длины в общем потоке

5 ошибок, так как корректирующий код гарантированно исправляет ошибки кратности t и меньше.

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому является устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации, содержащее последовательно соединенные декодер, анализатор кодовых

5 комбинаций, буферный блок памяти и Мажо ритарный блок, к первому дополнительному входу -которого подключен выход декодера, к синхронизирующем/ входу которого подключен соответствующий выход буферного

0 блока памяти, а второй, третий, четвертый и пятый выходы анализатора кодовых комбинаций подключены соответственно к второму дополнительному входу мажоритарного блока и первому, второму и третьему входам буферного блока памяти. Дополнительный выход мажоритарного блока и выходы блока памяти кодовых комбинаций результатов декодирования подключены соответственно к третьему, четвертому, пятому и шестому входам анализатора кодовых комбинаций, а вход блока памяти кодовых комбинаций результатов декодирования подключен к дополнительному выходу декодера, синхронизирующий вход анализатора совпадений кодовых комбинаций подключен к первому выходу анализатора кодовцх комбинаций, а первый, второй и третий входы соединены соответственно с первым выходом декодера и с соответствующими выходами анализатора кодовых комбинаций. Выход анализатора совпадений кодовых комбинаций подключен к первым входам первого, второго и третьего элементов И, вторые входы которых соединены с соответствующими выходами блока памяти кодовых комбинаций результатов декодирования. Кроме того, выходы блока памяти КОДОВ.ЫХ комбинаций результатов декодирования подключены к первым т0ем входам элемента ИЛИ. к четвертому входу которого подключен выход элемента ИИЛИ, входы которого подключены к выходу анализатора совпадений кодовых комбинаций. Выходы первого, второго и третьего злемента И подключены к соответствующим входам мажоритарного блока, выход которого подключен к первому входу четвертого злемента И, к второму входу которого подключен выход злемента ИЛИ, причем в.ыход четвертого элемента И является выходом устройства.

Однако такое устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации обладает низкой достоверностью принимаемой информации.

Как видно из табл.1, необнаружение .ошибки при приеме информации в известном устройстве появляется в целом ряде случаев.

Цель изобретения - повь1шение достоверности принимаемой информации.

Поставленная цель достигается за счет обеспечения возм(}жности использования при трехкратном повторении имитострйких преобразований циклического кода, не приводящих к выравниванию вероятностей векторов ошибок различных конфигураций на длине кодового слова п. Т.е.. если с (cof ci,...,ck) - информационная последовательность, предназначенная для передачи циклическим {п,k)-кoдoм при трехкратном, повторении комбинации, то осуществляются следующие преобразования;

АГ G;. А2- G; Ьз-с- Аз G,

где AI, А2. АЗ - двоичные обратимые матрицы (k х k), получаемые с помощью псевдослучайной последовательности (ПСП).

G - порождающая матрица циклическо5 го (п, k}кoдa.

На приемном конце системы передачи информации после осуществления декодирования bi, b2, Ьз и получения соответствующих qi, q2, qa информационных

0 последовательностей, необходимо осуществить обратное преобразование: gr Ai

,ii|Jcyw|j Ji uacJnnc. yi /лт ,

qa АЗ Возможность использования имитостойких преобразований кода позволяет существенно повысить совокупную

5 имитостойкость информации, передаваемой с использованием циклических кодов при трехкратном повторении комбинации (табл.1).

Псевдослучайные последовательности,

0 с помощью которых формируют на приемном и передающем концах системы передачи информации матрицы AI (1 1,3), согласованы одна относительно другой, например, с помощью системы единого вре5 мени,

Таким образом, для достижения поставленной цели в устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации, содержащее декодер, информационный, вход которого является информационным входом устройства, управляющий выход декодера соединен с информационным входом первого блока буферной памяти, первый выход которого соединен с первым управляющим йходом анализатора кодовых комбинаций и первыми входами первого элемента И и злемента ИЛИ, второй выход соединен с вторым управляющим входом

0 анализатора кодовых комбинаций, первым входом второго элемента И и вторым входом злемента ИЛИ, третий выход с третьим управляющим входом анализатора кодовых комбинаций, первым входом третьего

5 злемента И и третьим входом элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, выходы первого - третьего элементов И соединены соответственно с первым - третьим

0 управляющими входами мажоритарного блока, первый выход которого соединен с , первым информационным входом анализатора кодовых комбинаций, первый выход которого соединен с входами синхронизации декодера и анализатора совпадений, выход которого соединен непосредственно с вторыми входами первого - третьего элементов И и через элемент И-НЕ с четвертым входом злемента ИЛИ, установочные

входы анализатора кодовых совпадений являются установочными входами устройства, четвертый управляющий вход анализатора кодовых комбинаций - входом Пуск устройства, второй выход анализатора кодовых комбинаций соединен с четвертым управляющим входом межоритарного блоха, третий выход - с первыми информационными входами анализатора совпадений и второго блока буферной памяти, первый выход которого соединен с первым информационным входом мажоритарного блока и вторым информационным входом анализатора кодовых комбинаций, четвертый выход которого соединен с входом синхронизации второго блока буферной памяти, пятый выход - с вторыми информационными входами анализатора совпадений и второго блока буферной памяти, второй выход которого соединен с вторым информационным вхо. дом мажоритарного блока, второй выход которого соединен с вторым входом четвертого элемента И, выход которого является выходом устройства, введены блок постоянной памяти и арифметический блок, уст« новочные входы которого являются устан.;вочными входами устройства, вход синхронизации арифметического блока объединен с входом блока постоянной памяти и подключен к первому выходу анализатора кодовых комбинаций, выходы декодера и блока постоянной памяти соединены соответственно с первыми и одноименными вторыми информационными входами арифметического блока, выход которого соединен с третьими информационными входами анализатора кодовых комбинаций, анализатора совпадений и мажоритарного блока.

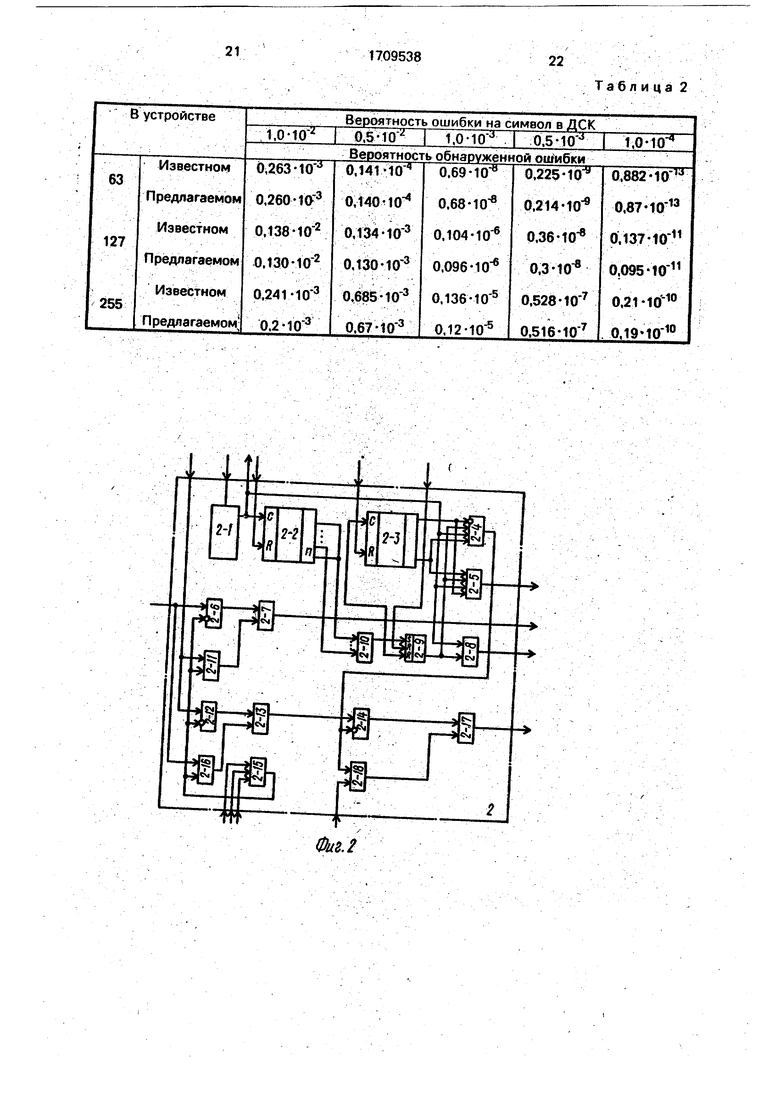

Арифметический блок содержит регистр, группу элементов И, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И, триггеры и счетчик, первые входы которого соединены с соответстеующими входами первого элемента И, выход которого соединен с входом установки в 1 первого триггера, выход которого соединен с первым входом второго элемента И, выход которого соединен с управляющим входом регистра и первыми входами элементов И группы, выходы которых соединены с одноименными информационными входами регистра, парал/ вльные выходы которого соединены с первыми входами одноименных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы которых соединены с вторыми входами одноименных элементов И группы, вторые выходы с«ввтчика соединены с соответствующими входами третьего элемент И, выход котефого соединен с первым входом установки О первого триггера и входом установки в 1 второго триггера, инверсный и прямой выходы которого соединены соответственно с Вторым входом второго элемента И и первым входом четвертого

элемента И, выход которого соединен с тактовым входом регистра, третий выход счетчика соединен с первым входом установки в О второго триггера, третьи входы элементов И группы объединены и являются

0 первым информационным входом арифметического блока, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - вторыми информационными входами арифметического блока, счетный вход счетчика объединен с

5 вторым входом четвертого элемента И и третьим входом второго элемента И и является входом синхронизации арифметического блока, входы установки в О регистра, счетчика и вторые входы установки в О

0 первого и второго триггеров являются установочными входами арифметического блока, последовательный выход регистра выходом арифметического блока.

Арифметический блок хорошо известен в системах передачи и обработки информации и представляет собой блок, выполняющий исключительно функцию перемножения. Выходная последовательность определяется выражением:

0. а с- Н,

где с - двоичная последовательность длины k,Н -двоичная обратная матрица размером k xk.

5 Введение в предлагаемое устройство арифметического блока и блока постоянной памяти позволяет повысить достоверность принимаемой информации,

В табл.1 приведены различия по выходному сигналу в известном и предлагаемом устройствах в зависимости от состояния канала.

Блок постоянной памяти функционально неразрывно связан с арифметическим

5 блоком, для работы которого необходимо использование стохастических матриц, хранящихся в блоке постоянной памяти. Таким образом, лишь пЪлная совокупность предлагаемых блоков обеспечивает повышение достоверности принимаемой информации.

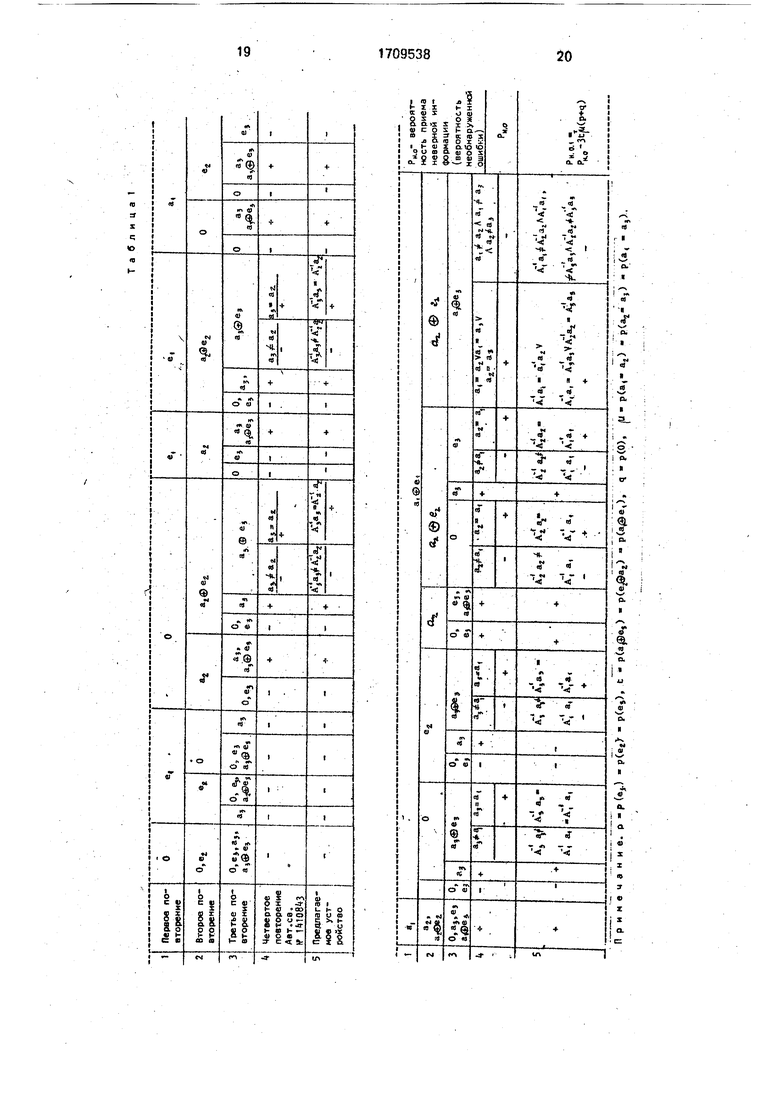

На фиг.1 представлена структурная схема предлагаемого устройства для мажоритарного декодирования имитозащищенных

5 циклических кодов при трехкратном повторении комбинации; на фиг.2 - структурная схема анализатора кодовых комбинаций; на фиг.З - структурная схема мажоритарного блока; на фиг. 4 - структурна я схема арифметического блока.

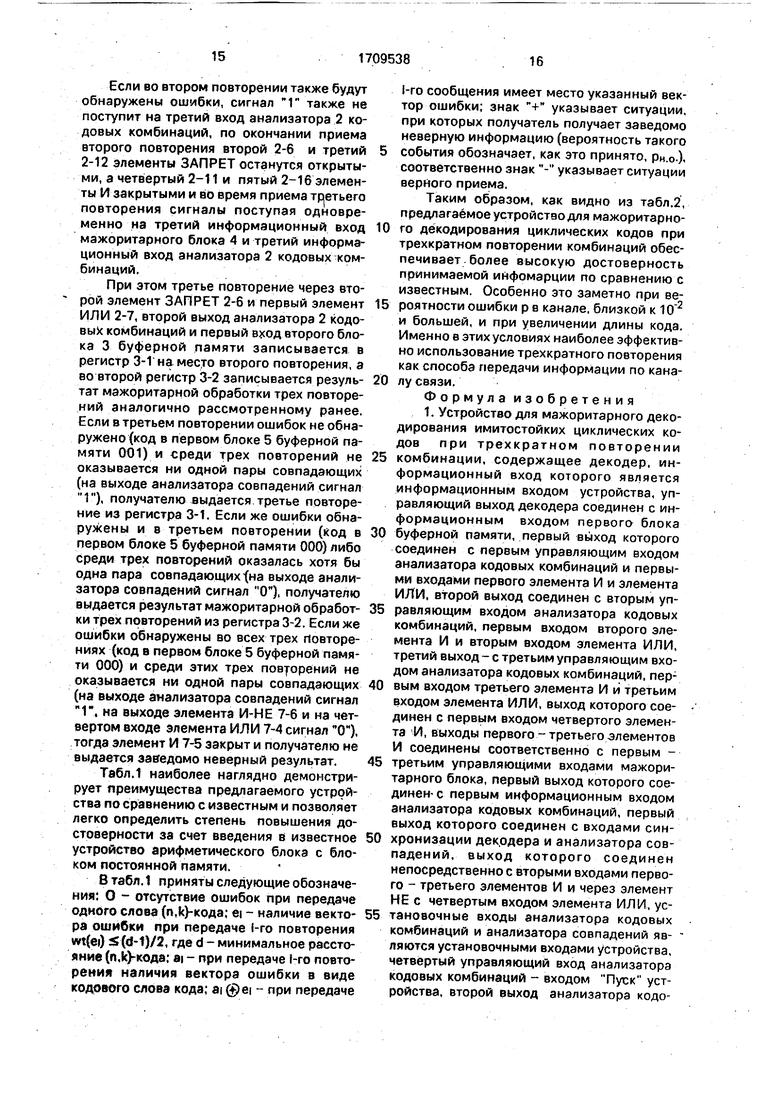

В табл.2 приведены результаты расчетов достоверности принимаемой информации для различных вероятностей ошибки в канале и различных длин кодов.

Предлагаемое устройство для мажори тлрного декодирования имитозащищенных циклических кодов при трехкратном повторении комбинации (фиг.1) содержит декодер 1, анализатор 2 кодовых комбинаций (фиг.2), содержащий генератор 2-1 синхроимпульсов, счетчики 2-2 и 2-3, первый элемент ЗАПРЕТ 24, второй элемент ЗАПРЕТ 2-6, первый элемент И 2-5, второй элемент И 2-8, триггер 2-9, третий 2-10 и четвертый 2-11 элементы И, третий элемент ЗАПРЕТ 2-12, первый элемент ИЛИ 2-7,второй элемент ИЛИ 2-13, четвертый элемент ЗАПРЕТ 2-14, третий элемент ИЛИ 2-15, пятый элемент И 2-16, четвертый элемент ИЛИ 2-17i шестой элемент И 2-18, второй блок 3 буферной памяти, содержащий регистры 3-1 и 3-2 (не показаны), мажоритарный блок 4 (фиг.З), содержащий первый элемент И 4-1, первый элемент ЗАПРЕТ 4-2, второй элемент И , третий элемент И 4-3, первый элемент ИЛИ 4-5, второй элемент ЗАПРЕТ 4-6, второй 4-7 и третий 4-8 элементы ИЛИ, четвертый 4-9 и пятый 4-10 элементы И, третий 4-11 и четвертый 4-12 элеме«ть1 ЗАПРЕТ, первый блок 5 буферной памяти , анализатор 6 совпадений, содержащий счетчики 6-1 и , первый 6-3, второй 6-4, третий 6-5. четвертый 6-6, пятый 6-10, шестой 6-7, седьмой 6-11, восьмой 6-8 и девятый 6-9 элементы ЗАПРЕТ, первый 6-12, второй 6-14 и третий 6-16 элементы ИЛИ, первый 6-13, второй 6-15 и третий 6-17 триггеры и элемент И 6-18 И (не показаны), первый 7-1, второй 7-2 и третий 7-3 элементы И, элемент ИЛИ 7-4, четвертый элемент И 7-5, элемент И-НЕ 7-6, арифметический блок 81, содержащий (фиг.4) регистр 8-1, первый 8-2 и второй 8-3 триггеры, счетчик 8-4, первый 8-5, второй 8-6 и третий 8-7, четвертый 8-8 элементы И, группу 8-9 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и группу 8-10 элементов И, блок 9 постоянной памяти.;

Счетчики, регистры и генераторы, используемые в схеме, являются стандартными элементами вычислительной техники.

Декодер 1, анализатор 2 кодовых комбинаций, второй блок 3 буферной памяти, мажоритарный блок 4, первый блок 5 буферной памяти и анализатор 6 совпадений выполнены идентично известному устройству. Синхронизирующий вход блока 5 соединен с синхронизирующим входом декодера 1. .

Устройство длямажоритарногоде кодирования циклических кодов при трехкратном повторении комбинации работает следующим образом.

В исходном состоянии триггер 2-9 устанавливается в нулевое состояние и сигнал 5 О с его выхода подается на вторые входы элемента ЗАПРЕТ 2-4 и элементов И 2-5 и 2-8, а счетчики 2-2 и 2-3 устанавливаются в нулевое состояние. Кроме того, триггеры 6-13, 6-15, 6-17 устанавливаются в нулевое

0 состояние и сигналы О с их выходов через схему И 6-18 подаются на первые входы элементов И 7-1,7-3,7-2 и на четвертый вход элемента ИЛИ 7-4 через элемент И-НЕ, счетчики 6-1 и 6-2 устанавливаются в нулевое

5 состояние, обнуляется регистр 8-1, счетчик 8-4 и триггеры 8-2 и 8-3 устанавливаются в нулевое состояние.Одновременно с началом приема первого повторения на вход генератора 2-1 синхроимпульсов поступает сигнал Пуск, по которому он начинает выдавать на частоте npVieMa синхронизирующие импульсы на синхронизирующий вход декодера 1, вход первого счетчика 2-2, и через элемент И 2-8

5 - на четвертый выход анализатора 2 кодовых комбинаций и первый синхронизирующий вход второго блока 3 буферной памяти, на синхронизирующие входы регистров 3-1 и 3-2, на счетный вход счетчика

0 8-4, а также на синхронизирующий вход блока 9 постоянной памяти. Емкость счетчика 8-4 равна T+2k, где Т - время (в числе тактов), необходимое декодеру 1 для осуществления декодирования принимаемой

5 кодовой комбинации, закодированной циклическим (п, k)-кoдoм. п - разрядные кодовые комбинации поступают на вход декодера 1, с выхода которого через Т тактов с момента начала приёма после декоди;

0 рования (обнаружения и, если возможно, исправления ошибок) k-разрядные кодовые комбинации а через вход арифметического распределителя блока поступают на вторые входы группы 8-10 элементов, на третьи входы которых поступают k-разрядные последовательности, хранящиеся в блоке 9 постоянной памяти, причем предварительно на элементах труппы ИСКЛЮЧАЮЩЕЕ ИЛИ осуществляется сложение по модулю

0 два прежнего содержимого каждого из разрядов регистра 8-1 с соответствующим разрядом очередной ПСП. При этом через Т тактов после начала приема сигналы с соответствующих выходов счетчика через первый элемент И 8-5 переводят триггер 8-2 в единичное состояние, разрешая тем самым прохождение синхронизирующих импульсов на второй синхронизирующий вход регистра 8-1, а также на первые входы группы 8-10 элементов И, Т.е. разрешается запись

информации в регистр 8-1. Таким образом, в течение /следующих k тактов в регистре 8-1 (арифметического блока) сформируется k-разрядная последовательность а АГ .

По окончании (T+k)-ro такта с моментов начала приема первого повторения сигналы с соответствующих выходов счетчика 8-4 через второй элемент И 8-6 переводят первый триггер 8-2 в нулевое состояние, запрещая тем самым прохождение синхронизирующих импульсов на второй синхронизирующий вход региста 8-1. Таким образом, в течение последующих k тактов запись информации в регистре 8-1 запрещена. Одновременно на первом выходе второго триггера 8-3 появляется единичный сигнал, разрешающий прохождение синхронизирующих импульсов на первый (сдвигающий) -синхронизирующий вход { регистра 8-1.

Кроме того, по окончании (T+k)-ro такта с момента начала приема первого повторения сигналы с соответствующих выходов счетчика 2-2 через третий элемент И 2-10 переводят триггер 2-9 в единичное состояние, разрешая тем самым прохождение синхронизирующих импульсов на синхронизирующие входы регистров 3-1 и 3-2. Таким образом, в течение следующих k тактов kфaзpяднaя кодовая комбинация из регистра 8-1 через первый вход анализатора кодовых комбинаций, элемент ЗАПРЕТ 2-6, элемент ИЛИ 2-7, третий-выход анализатора 2 кодовых комбинаций, первый вход второго блока 3 буферной памяти записывается в регистр 3-1.

По окончании (T+2k)-ro такта с момента начала приема первого повторения импульс переполнения со счетчика 2-2 через третий элемент И 2-10 переводит триггер 2-9 в нулевое состояние, запрещая тем самым прохождение синхронизирующих импульсов на синхронизирующие входы регистров 3-1 и 3-2 в течение первых (T+k) тактов с момента начала приема второго повторения. Таким образом, в течение последующих (T+k) тактов запись и сдвиг информации в регистрах 3-1 и 3-2 отсутствуют.

По истечении (T+2k) тактов с момента приема первого повторения с управляющего выхода декодера 1 на информационный вход первого блока 5 буферной-памятм поступает сигнал 1, если оно принято без обнаруженных ошибок. С выхода этого блока сигнал 1 поступает на третий вход анализатора 2 кодовых комбинаций и через элемент ИЛИ 2-15 - на инверсные входы второго 2-6 и третьего 2-12 элементов ЗАПРЕТ, а также на вторые входы элементов И 2-11 и 2-16, подготавливая анализатор 2

кодовых комбинаций к приему второго повторения.

По окончании приема и обработки первого повторения импульс переполнения со

счетчика 6-1 поступает на вход счетчика 6-2, в результате чего на первом выходе счетчика 6-2 появляется сигнал 1. Кроме того, по окончании (T+2k)-ro такта импульс переполнения со счетчика 8-4 переводит второй

0 триггер 8-3 в нулевое состояние, запрещая тем самым поступление синхронизирующих импульсов на первый синхронизирующий вход регистра 8-1. Элементы второго повторения через вход арифметического блока,

5 группу 8-10 элементов И, регистр 8-1, третий вход анализатора 2 кодовых комбинаций, пятый элемент И 2-16, второй элемент ИЛИ 2-17 и второй вход второго блока 3 буферной памяти записываются в регистр 3-2. В это

0 время элементы принятого без ошибок первогр повторения перезаписываются снова в регистр 3-1 через первый выход второго блока 3 буферной памяти, второй вход анализатора 2 кодовых комбинаций, четвертый

5 элемент И 2-11, первый элемент ИЛИ 2-7, третий выход анализатора 2 кодовых комбинаций, первый вход второго блока 3 буферной памяти. Через (T+2k) тактов с момента начала приема второго повторения

0 сигналы с выходов счетчика 2-3 открывают первый элемент ЗАПРЕТ 2-4 и синхронизирующие импульсы с генератора 2-1 синхроимпульсов в течение k тактов по прошествии T+k тактов с момента начала приема трёть5 его повторения поступают на инверсный вход четвертого элемента ЗАПРЕТ 2-14 и на первый вход шестого элемента И 2-18, запрещая запись третьего повторения в регистр 3-2 и подключая его вход через шестой

0 элемент И 2-18 и четвертый элемент ИЛИ 2-17 к первому выходу мажоритарного бло-, ка 4. Элементь третьего повторения с выхода декодера 1 через арифметический блок 8 поступают на третий информационный вход

5 мажоритарного блока 4 в течение k тактов по прошествии T+k тактов с момента начала его приема.

В это же время элементы первого и второго повторений поступают из регистров 30 1 и 3-2 через выходы второго блока 3 буферной памяти на входы мажоритарного блока 4. Элементы И 4-1,4-4,4-10 и элемент ИЛИ 4-5 формирует мажоритарный результат обработки трех повторений, который через первый выход мажоритарного блока 4, первый информационны.й вход анализатора 2 кодовых комбинаций, шестой элемент И 2-18, третий элемент ИЛИ 2-17, пятый выход анализатора 2 кодовых комбинаций,-третий вход второго блока 3 буферной памяти записывается в регистр 3-2 на место второго повторения. В это же время элементы первого повторения снова перезаписываются в регистр 3-Т.

Кроме того, через T+2k тактов с момеи- 5 та начала приема второго повторения сигналы с выходов счетчика 6-2 открывают первый 6-3, второй 6-4 и третий 6-5 элементы ЗАПРЕТ и элементы первого, второго и третьего повторений соответственно с вы 10 хода первого элемента ИЛ И 2-7, четвертого элемента ИЛИ 2-17 и с выхода декодера 1 поступают, соответственно на второй 6-4 третий и первый 6-3 входы элемент эв ЗАПРЕТ.;15

Элементы ЗАПРЕТ 6-6,6-7.6-8,6-9,6-10 и 6-11, элементы ИЛИ 6-12,6-14 и 6-16, триггеры 6-13, 6-15 и 6-17 и элемент И 6-18 формируют результат анализа трех повторений на попарные совпадения, который с 20 выхода элемента И 6-18 подается на первые входы элементов И 7-1; 7-2 и 7-3 и на вход элемента И-НЕ 7-6, с выхода которого поступает на четвертый вход элемента ИЛИ 7-4.

Таким образом, к моменту окончания 25 приема и обработки третьего повторения в ч регистре 3-1 записывается первое повторение, в котором не обнаружено ошибок, а во втором регистре 3-2 записывается результат мажоритарной обработки трех повторе- 30 НИИ, в первом 6-13, втором 6-15 и третьем 6-17 триггерах записывается результат проверки на совпадение первого и третьего, первого и второго, третьего и второго повторений соответственно. Через 3(T+2k) тактов( 35 с момента начала приема первого повторения счетчик 2-3 разрешает прохождение синхронизирующих импульсов через первый элемент И 2-5, второй выход анализатора 2 кодовых комбинаций, четвертый 40 управляющий вход мажоритарного блока 4 па первый вход элемента.И 4-9. Если первое повторение окажется единственным в котором не было обнаружено ошибок {код в первом блоке 5 буферной памяти 100) и, кроме 45 того, среди повторений не окажется ни одной пары совпадающих (на выходе анализатора совпадений сигнал 1), тогда на выходе элемента ИЛИ 4-7 появится сигнал 1, поступающий на инверсный вход эле- 50 мента ЗАПРЕТ 4-12 и первый вход элемента И 4-3, подключающий выход первого регистра 3-1 через элементы И 4-3, ИЛИ 4-8, И 4-9 к выходу мажоритарного- блока 4. подключенному к первому входу элемента И 55 7-5, на второй вход которого поступает сигнал Г с выхода элемента ИЛИ 7-4.

Таким образом, первое повторение в течение k тактов с момента окончания приема третьего повторения выдается получателю. Если же ошибки не были обнаружены хотя бы в двух или-во всех трех повторениях (код в первом блоке 5 буферной памяти 110, 101, 011, 111) либо среди трех повторений оказалась хотя бы одна пара совпадающих (на выходе анализатора совпадений сигнал О), тогда на выходе элемента ИЛИ 4-7 сигнал 1 не появится, на выход устройства будет выдан результат межоритарной обработки из регистра 3-3, через открытый элемент ЗАПРЕТ 4-12 И элементы ИЛИ 4-8, 4-9 и 7-5.

Если в первом повторении обнаруживаются ошибки, сигнал 1 по окончании его приема на первый вход анализатора 2 кодовых комбинаций не поступает, второй 2-6 и третий 2-12 элементы ЗАПРЕТ во время приема второго повторения оказываются открытыми и элементы второго повторения через третий информационный вход анализатора 2 кодовых комбинаций, второй элемент ЗАПРЕТ 2-6, первый элемент ИЛИ 2-7, третий выход анализатора 2 кодовых комбинаций и первый вход второго блока 3 буферной памяти записываются в регистр 3-1 на место первого повторения, которое через первый выход второго блока 3 буферной памяти, второй вход анализатора 2 кодовых комбинаций, третий элемент ЗАПРЕТ 2-12, второй элемент ИЛИ 2-13, четвертый элемент ИЛИ 2-17, пятый выход анализатора 2 кодовых комбинаций и второй вход второго блока 3 буферной памяти перезаписывается в регистр 3-2 в течение k тактов по прошествии (T+k) тактов с момента начала приема второго повторения. Если во втором повторении ошибок не обнаружено, по окончании его приема сигнал 1 с выхода первого блока 5 буферной памяти через второй управляющий вход анализатора 2 кодовых комбинаций и третийэлемент ИЛИ 2-15 поступает на инверсные входы второго 2-6 и третьего 2-12 элементов ЗАПРЕТ и на вторые входы четвертого 2-11 и пятого 2-16 элементов И. Прием третьего повторения ведется аналогично предыдущему случаю. Если в третьем повторении не обнаружено ошибок (код в блоке 5011) либо среди трех повторений оказалась хотя бы одна пара совпадающих (на выходе анализатора 6 совпадений сигнал О), тогда мажоритарный блок 4 выдает получателю результат мажоритарной обработки из регистра 3-2. Если )tie второе повторение окажется единственным, в котором не было обнаружено ошибок (код в блоке 5 010) и среди трех повторений не окажется ни одной пары совпадающих (на выходе анализатора 6 совпадений сигнал 1) получателю будет вьщано второе повторение из регистра 3-1.

Если во втором повторении также будут обнаружены ошибки, сигнал Г также не поступит на третий вход анализатора 2 кодовых комбинаций, по окончании приема второго повторения второй 2-6 и третий 2-12 элементы ЗАПРЕТ останутся открытыми, а четвертый 2-11 и пятый 2-16 элементы И закрытыми и во время приема третьего повторения сигналы поступая одновременно на третий информационный вход мажоритарного блока 4 и третий информационный вход анализатора 2 кодовых комбинаций.

При этом третье повторение через второй элемент ЗАПРЕТ 2-6 и первый элемент ИЛИ 2-7, второй выход анализатора 2 кодовых комбинаций и первый вход второго блока 3 буферной памяти записывается в регистр 3-1 наместо второго повторения, а во второй регистр 3-2 записывается результат мажоритарной обработки трех повторений аналогично рассмотренному ранее, Если в третьем повторении ошибок не обнаружено (код в первом блоке 5 буферной памяти 001) и среди трех повторений не оказывается ни одной пары совпадающих (на выходе анализатора совпадений сигнал 1), получателю выдается третье повторение из регистра 3-1. Если же ошибки обнаружены и в третьем повторении (код в первом блоке 5 буферной памяти 000} либо среди трех повторений оказалась хотя бы одна пара совпадающих на выходе анализатора совпадений сигнал О), получателю выдается результат мажоритарной обработки трех повторений из регистра 3-2. Если же ошибки обнаружены во всех трех Повторениях (код в первом блоке 5 буферной памяти 000) и среди этих трех повторений не оказывается ни одной пары совпадающих (на выходе анализатора совпадений сигнал Г, на выходе элемента И-НЕ 7-6 и на четвертом входе элемента ИЛИ 7-4 сигнал О), тогда элемент И 7-5 закрыт и получателю не выдается завгедомо неверный результат,

Табл,1 наиболее наглядно демонстрирует преимущества предлагаемого устройства по сравнению с известным и позволяет легко определить степень повышения достоверности за счет введения GI известное устройство арифметического блока с блоком постоянной памяти.

В табл. 1 приняты следующие обозначения: О - отсутствие ошибок при передаче одного слова (n,k)-кoдa; ei - наличие вектора ошибки при передаче i-ro повторения wt(ei) S(d-1)/2, где d - минимальное расстояние (п,1с)-кода; ai - при передаче f-ro повторения наличия вектора ошибки в виде кодового слова кода; ai (ei - при передаче

1-го сообщения имеет место указанный вектор ошибки; знак + указывает ситуации, при которых получатель получает заведомо неверную информацию (вероятность такого

события обозначает, как это принято, рн.о.), соответственно указывает ситуации верного приема.

Таким образом, как видно из табл.2, предлагаемое устройство ,аля мажоритарного декодирования циклических кодов при трехкратном повторении комбинаций обеспечивает более высокую достоверность принимаемой инфомарции по сравнению с известным. Особенно это заметно при вероятности ошибки р в канале, близкой к 10 и большей, и при увеличении длины кода. Именно в этих условиях наиболее эффективно использование трехкратного повторения как способа передачи информации по кана0 лу связи.

Формула изобретения 1. Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении

5 комбинации, содержащее декодер, информационный вход которого является информационным входом устройства, управляющий выход декодера соединен с информационным входом первого блока

0 буферной памяти, первый выход которого соединен с первым управляющим входом анализатора кодовых комбинаций и первыми входами первого элемента И и элемента ИЛИ, второй выход соединен с вторым управляющим входом анализатора кодовых комбинаций, первым входом второго элемента И и вторым входом элемента ИЛИ, третий выход-с третьим управляющим входом анализатора кодовых комбинаций, первым входом третьего элемента И и третьим входом элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, выходы первого - третьего элементов И соединены соответственно с первым 5 третьим управляющими входами мажоритарного блока, первый выход которого соединен- с первым информационным входом анализатора кодовых комбинаций, первый выход которого соединен с входами синхронизации дек.одера и анализатора совпадений, выход которого соединен непосредственно с вторыми входами первого - третьего элементов И и через элемент НЕ с четвертым входом элемента ИЛИ, установочные входы анализатора кодовых комбинаций и анализатора совпадений являются установочными входами устройства, четвёртый управляющий вход анализатора кодовых комбинаций - входом Пуск устройства, второй выход анализатора кодовых комбинаций соединен с четвертым управляющим входом мажоритарного блока, третий выход-с первыми информационными входами анализатора совпадений и второго блока буферной памяти, первый выход которого соединен с первым информационным входом мажоритарного блока и вторым информационным входом анализатора кодовых комбинаций, четвертый выход которого соединен с входом синхронизации второго блока буферной памяти, пятый выход г с вторыми информационными входами анализатора совпадений и второго блока буферной памяти, второй выход которого соединен с вторым информационным входом мажоритарного блока, второй выход которого соединен с вторым входом четвертого элемент1а И, выход которого является выходом устройства, отличающееся тем, что, с целью повышения достоверности информации на выходе устройства, в него введены блок постоянной памяти и арифметический блок, установочные входы которого являются установочными входами устройства, вход синхронизации арифметического блока объединен с входом блока постоянной памяти и подключен к первому выходу анализатора кодовых комбинаций, выходы декодера и блока постоянной памяти соединены соответственно с первым и одноименными вторыми информационными входами арифметического блока, выход которого соединен с третьими информационными входами анализатора кодовых, комбинаций, анализатора совпадений и мажоритарного блока.

2. Устройство по п, 1, о т л и ч а ю щ е ёт с я тем, что арифметический блок содержит регистр, группу элементов И, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И, триггеры и счетчик, первые выходы которого соединены с соответствующими входами первого элемента И, выход которого соединен с входом установки в 1 первого триггера, выход которого соединен с первым входом второго элемента И, выход которого соединен с управляющим входом регистра и первыми входами элементов И группы, выходы которых соединены с одноименными информационными входами регистра, параллельные выходы которого соединены с первыми входами одноименных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы которых соединены с вторыми входами одноименных элементов И группы, вторые выходы счетчика соединены с соответствующими входами третьего элемента И, выход которого соединен с первым- входом установки в О первого триггера и входом установки в 1 второго триггера, инверсный и прямой выходы которого соединены соответственно с вторым входом второго элемента И и первым входом четЁертого элемента И, выход которого соединен с тактовым входом регистра, третий выход счетчика соединен с первым входом установки в О второго триггера, третьи входы элементов И группы объединены и являются первым информационным входом арифметического блока, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ - вторыми информационными входами арифметического блока, счетный вход счетчика объединен с вторым входом четвертого элемента И и третьим входом второго элемента И и является входом синхронизации арифм тического блока, входы установки в О регистра, счетчика и вторые входы установки в О первого и второго триггеров являются установочными входами ариф/летического блока, последовательный выход регистра выходом арифметического блока.

n

я s с; ю n

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации | 1983 |

|

SU1141577A2 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Декодер линейного кода | 1986 |

|

SU1432786A1 |

| Устройство для приема трехкратно повторяемых команд управления | 1979 |

|

SU873436A1 |

| ДЕКОДЕР С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК | 2008 |

|

RU2370887C1 |

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи информации. С помощью введенных арифметического блока 8 и блока 9 постоянной памяти псевдослучайной последовательности осуществляются имитостойкие преобразования кода, что повышает достоверность информации на выходе устройства. Устройство содержит декодер 1. анализатор 2 кодовых комбинаций, блоки 3 и 5 буферной памяти, мажоритарный блок 4, анализатор 6 совпадений кодовых комбинаций, элементы И 7, арифметический блок 8, блок 9 постоянной памяти. 1 з.п. ф-лы, 4 ил., 2 табл."Чо >&оСПы оа

;1

Фиг. J

| Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации | 1983 |

|

SU1141577A2 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Авторское свидетельство СССР № 1410843, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-01-30—Публикация

1990-01-22—Подача