Изобретение относится к системам телекоммуникаций и вычислительной технике и может найти применение в устройствах приема информации из канала передачи или воспроизведения информации с высоким уровнем ошибок.

В настоящее время на практике применяются устройства декодирования кодов Рида-Соломона (PC-кодов), реализующие классические алгоритмы декодирования (Питерсона-Горенстейна-Цирлера, Берлекэмпа-Месси, Евклида), позволяющие исправлять не более t ошибочных символов в кодовом слове (t=(d-1)/2, d - минимальное кодовое расстояние).

Известно устройство списочного декодирования кодов Рида-Соломона, исправляющее ошибки за границей половины минимального кодового расстояния t, [1], содержащее: входной блок, блок декодирования и выходной блок. Используемый метод декодирования основывается на нахождении ненулевого элемента в ядре структурированной матрицы.

Недостатком данного устройства является сложность его реализации.

Известно устройство декодирования, реализующее алгебраический алгоритм декодирования кодов Рида-Соломона, используя мягкие решения [2], содержащее: блок повторного кодирования, блок интерполяции, блок факторизации, блок выборки точек интерполяции и селектор.

Алгоритм работы устройства состоит в следующем: используя оценки надежностей символов принятого кодового слова, вычисляется матрица М, которая определяет интерполяционные точки и их кратность; выполняется процедура интерполяции для нахождения полинома QM(X,Y); в полиноме QM(X,Y) выделяются сомножители вида Y-f(X); из полиномов f(X) реконструируются кодовые слова; наиболее вероятное из них выбирается как результат работы алгоритма.

Недостатком данного устройства является его сложность, обусловленная сложностью реализации процедур интерполяции и факторизации многочленов больших степеней.

Наиболее близким по технической сущности к заявляемому изобретению является выбранное в качестве прототипа устройство декодирования кодов Рида-Соломона [3], позволяющее исправить одну дополнительную ошибку за границей половины минимального кодового расстояния. Устройство-прототип содержит: буферную память данных, блок вычисления синдромов, процессор Галуа, блок дискретного преобразования Фурье, блок поиска позиций ошибок веса t+1 и блок вычисления значений ошибок.

Устройство-прототип осуществляет поиск позиций ошибок за границей половины минимального кодового расстояния путем вычисления последовательностей возможных значений неизвестных невязок аналитического продолжения алгоритма Берлекэмпа-Месси и подсчета значений невязок в этих последовательностях.

Недостатком прототипа является относительно низкое быстродействие, обусловленное переборным характером поиска неизвестных невязок при исправлении t+1 ошибок. Количество вычислений возможных значений неизвестной невязки равняется nS=(n-1+t)(n-t)/2, где n - длина кодового слова кода Рида-Соломона.

Быстродействие декодера [3] может быть увеличено за счет усреднения времени декодирования кодовых слов с различным числом ошибок. Однако при этом для обеспечения постоянной пропускной способности необходимо ввести дополнительный буфер для хранения кодовых слов, что одновременно увеличит задержку данных в декодере.

Технической задачей изобретения является повышение быстродействия исправления ошибок за границей половины минимального расстояния путем использования информации о надежности принятых из канала символов.

Поставленная техническая задача решается тем, что в устройство декодирования кодов Рида-Соломона, содержащее буферную память данных, блок вычисления синдромов, процессор Галуа, блок дискретного преобразования Фурье, блок поиска позиций ошибок, блок вычисления значений ошибок, первый сумматор элементов поля Галуа, причем входы буферной памяти данных и входы блока вычисления синдромов являются входами символов данных устройства декодирования кодов Рида-Соломона, выходы буферной памяти данных соединены с первыми входами первого сумматора элементов поля Галуа, выходы блока вычисления синдромов соединены с первыми входами процессора Галуа, первые выходы процессора Галуа соединены с первыми входами блока дискретного преобразования Фурье, вторые выходы процессора Галуа соединены со вторыми входами блока дискретного преобразования Фурье, третьи выходы процессора Галуа соединены с третьими входами блока дискретного преобразования Фурье, четвертые выходы процессора Галуа соединены с четвертыми входами блока поиска позиций ошибок, пятые выходы процессора Галуа соединены с первыми входами блока вычисления значений ошибок, шестые выходы процессора Галуа соединены со вторыми входами блока вычисления значений ошибок, седьмые выходы процессора Галуа соединены с третьими входами блока вычисления значений ошибок, вторые выходы блока дискретного преобразования Фурье соединены с третьими входами процессора Галуа, третьи выходы блока дискретного преобразования Фурье соединены с четвертыми входами процессора Галуа, четвертые выходы блока дискретного преобразования Фурье соединены с первыми входами блока поиска позиций ошибок, пятый выход блока дискретного преобразования Фурье соединен со вторым входом блока поиска позиций ошибок, шестые выходы блока дискретного преобразования Фурье соединены с третьими входами блока поиска позиций ошибок, первые выходы блока поиска позиций ошибок соединены с пятыми входами процессора Галуа, вторые выходы блока поиска позиций ошибок соединены с шестыми входами процессора Галуа, третьи выходы блока поиска позиций ошибок соединены с седьмыми входами процессора Галуа, четвертые выходы блока поиска позиций ошибок соединены с восьмыми входами процессора Галуа, выходы блока вычисления значений ошибок соединены со вторыми входами первого сумматора элементов поля Галуа, выходы первого сумматора элементов поля Галуа являются выходами данных устройства декодирования кодов Рида-Соломона, введен блок сортировки позиций символов, причем первые входы блока сортировки позиций символов являются входами оценок надежности символов данных устройства декодирования кодов Рида-Соломона, пятые выходы блока поиска позиций ошибок соединены со вторыми входами блока сортировки позиций символов, первые выходы блока дискретного преобразования Фурье соединены с третьими входами блока сортировки позиций символов, первые выходы блока сортировки позиций символов соединены со вторыми входами процессора Галуа, вторые выходы блока сортировки позиций символов соединены с пятыми входами блока поиска позиций ошибок, причем блок сортировки позиций символов содержит первую схему сравнения кодов, первый блок памяти отсортированных позиций, второй блок памяти отсортированных позиций, третий блок памяти отсортированных позиций, четвертый блок памяти отсортированных позиций, пятый блок памяти отсортированных позиций, первый коммутатор, второй коммутатор, третий коммутатор, четвертый коммутатор, пятый коммутатор, шестой коммутатор, седьмой коммутатор, первый счетчик, второй счетчик, третий счетчик, первый дешифратор, второй дешифратор, причем первые входы первой схемы сравнения кодов являются первыми входами блока сортировки позиций символов, вторые входы первой схемы сравнения кодов соединены с шиной константы Thres, выход первой схемы сравнения кодов соединен со вторым входом первого блока памяти отсортированных позиций, со вторым входом второго блока памяти отсортированных позиций, со вторым входом третьего блока памяти отсортированных позиций, со вторым входом четвертого блока памяти отсортированных позиций и со вторым входом пятого блока памяти отсортированных позиций, первые выходы первого счетчика соединены с первыми входами первого блока памяти отсортированных позиций, с первыми входами второго блока памяти отсортированных позиций, с первыми входами третьего блока памяти отсортированных позиций, с первыми входами четвертого блока памяти отсортированных позиций и с первыми входами пятого блока памяти отсортированных позиций, второй выход первого счетчика соединен с входом второго счетчика, выходы второго счетчика соединены со входами первого дешифратора, первый выход первого дешифратора соединен с третьим входом первого блока памяти отсортированных позиций, второй выход первого дешифратора соединен с третьим входом второго блока памяти отсортированных позиций, третий выход первого дешифратора соединен с третьим входом третьего блока памяти отсортированных позиций, четвертый выход первого дешифратора соединен с третьим входом четвертого блока памяти отсортированных позиций, пятый выход первого дешифратора соединен с третьим входом пятого блока памяти отсортированных позиций, выходы первого блока памяти отсортированных позиций соединены со вторыми входами первого коммутатора и четвертыми входами второго коммутатора, выходы второго блока памяти отсортированных позиций соединены с третьими входами первого коммутатора и пятыми входами второго коммутатора, выходы третьего блока памяти отсортированных позиций соединены с четвертыми входами первого коммутатора и первыми входами второго коммутатора, выходы четвертого блока памяти отсортированных позиций соединены с пятыми входами первого коммутатора и вторыми входами второго коммутатора, выходы пятого блока памяти отсортированных позиций соединены с первыми входами первого коммутатора и третьими входами второго коммутатора, выходы третьего счетчика соединены с шестыми входами первого коммутатора, с шестыми входами второго коммутатора и входами второго дешифратора, первый выход второго дешифратора соединен с третьим входом седьмого коммутатора, второй выход второго дешифратора соединен с третьим входом третьего коммутатора, третий выход второго дешифратора соединен с третьим входом четвертого коммутатора, четвертый выход второго дешифратора соединен с третьим входом пятого коммутатора, пятый выход второго дешифратора соединен с третьим входом шестого коммутатора, первые входы третьего, четвертого, пятого, шестого и седьмого коммутаторов являются третьими входами блока сортировки позиций символов, вторые входы третьего, четвертого, пятого, шестого и седьмого коммутаторов являются вторыми входами блока сортировки позиций символов, выходы третьего коммутатора соединены с четвертыми входами первого блока памяти отсортированных позиций, выходы четвертого коммутатора соединены с четвертыми входами второго блока памяти отсортированных позиций, выходы пятого коммутатора соединены с четвертыми входами третьего блока памяти отсортированных позиций, выходы шестого коммутатора соединены с четвертыми входами четвертого блока памяти отсортированных позиций, выходы седьмого коммутатора соединены с четвертыми входами пятого блока памяти отсортированных позиций, выходы первого коммутатора являются вторыми выходами блока сортировки позиций символов, выходы второго коммутатора являются первыми выходами блока сортировки позиций символов, причем блок памяти отсортированных позиций содержит первый блок памяти с произвольным доступом, второй блок памяти с произвольным доступом, первый логический элемент И-НЕ, второй логический элемент И-НЕ, четвертый счетчик, пятый счетчик, восьмой коммутатор, девятый коммутатор, десятый коммутатор, одиннадцатый коммутатор и вычитатель, причем первые входы первого блока памяти с произвольным доступом, первые входы второго блока памяти с произвольным доступом являются первыми входами блока памяти отсортированных позиций, первый вход первого логического элемента И-НЕ, первый вход второго логического элемента И-НЕ, третий вход восьмого коммутатора, третий вход девятого коммутатора являются третьим входом блока памяти отсортированных позиций, второй вход первого логического элемента И-НЕ, второй вход второго логического элемента И-НЕ являются вторым входом блока памяти отсортированных позиций, выход первого логического элемента И-НЕ соединен со вторым входом первого блока памяти с произвольным доступом и входом четвертого счетчика, выходы четвертого счетчика соединены с первыми входами восьмого коммутатора, вторыми входами одиннадцатого коммутатора и первыми входами вычитателя, выходы восьмого коммутатора соединены с третьими входами первого блока памяти с произвольным доступом, выходы первого блока памяти с произвольным доступом соединены с первыми входами десятого коммутатора, выход второго логического элемента И-НЕ соединен со вторым входом второго блока памяти с произвольным доступом и входом пятого счетчика, выходы пятого счетчика соединены с первыми входами девятого коммутатора, выходы девятого коммутатора соединены с третьими входами второго блока памяти с произвольным доступом, выходы второго блока памяти с произвольным доступом соединены со вторыми входами десятого коммутатора, вторые входы вычитателя и вторые входы восьмого коммутатора являются четвертыми входами блока памяти отсортированных позиций, а старший разряд четвертых входов блока памяти отсортированных позиций соединен с третьим входом одиннадцатого коммутатора, первые выходы вычитателя соединены со вторыми входами девятого коммутатора, второй выход вычитателя соединен с третьим входом десятого коммутатора, выходы десятого коммутатора соединены с первыми входами одиннадцатого коммутатора, выходы одиннадцатого коммутатора являются выходами блока памяти отсортированных позиций, причем блок поиска позиций ошибок содержит первый блок вычисления невязок, второй блок вычисления невязок, первый блок подсчета невязок, второй блок подсчета невязок, двенадцатый коммутатор, первый регистр-защелку, блок памяти коэффициентов, первое местное устройство управления, причем первые входы первого местного устройства управления являются четвертыми входами блока поиска позиций ошибок, вторые входы первого местного устройства управления и первые входы блока памяти коэффициентов являются пятыми входами блока поиска позиций ошибок, третьи входы блока поиска позиций ошибок являются младшими разрядами вторых входов блока памяти коэффициентов, первые входы блока поиска позиций ошибок являются средними разрядами вторых входов блока памяти коэффициентов, второй вход блока поиска позиций ошибок является старшим разрядом вторых входов блока памяти коэффициентов, младшие разряды первых выходов блока памяти коэффициентов соединены с первыми входами первого блока вычисления невязок и с первыми входами второго блока вычисления невязок, средние разряды первых выходов блока памяти коэффициентов соединены с третьими входами первого блока вычисления невязок и с третьими входами второго блока вычисления невязок, старший разряд первых выходов блока памяти коэффициентов соединен с пятым входом первого блока вычисления невязок и с пятым входом второго блока вычисления невязок, младшие разряды вторых выходов блока памяти коэффициентов соединены со вторыми входами первого блока вычисления невязок и со вторыми входами второго блока вычисления невязок, средние разряды вторых выходов блока памяти коэффициентов соединены с четвертыми входами первого блока вычисления невязок и с четвертыми входами второго блока вычисления невязок, старший разряд вторых выходов блока памяти коэффициентов соединен с шестым входом первого блока вычисления невязок и с шестым входом второго блока вычисления невязок, первые выходы первого блока вычисления невязок соединены с шестыми входами двенадцатого коммутатора, вторые выходы первого блока вычисления невязок соединены с пятыми входами двенадцатого коммутатора, третий выход первого блока вычисления невязок соединен с четвертым входом первого блока подсчета невязок, четвертые выходы первого блока вычисления невязок соединены с третьими входами первого блока подсчета невязок, пятый выход первого блока вычисления невязок соединен с третьим входом первого местного устройства управления, первый выход первого блока подсчета невязок соединен с пятым входом первого местного устройства управления, вторые выходы первого блока подсчета невязок соединены с четвертыми входами двенадцатого коммутатора, первые выходы второго блока вычисления невязок соединены с первыми входами двенадцатого коммутатора, вторые выходы второго блока вычисления невязок соединены со вторыми входами двенадцатого коммутатора, пятый выход второго блока вычисления невязок соединен с четвертым входом первого местного устройства управления, четвертые выходы второго блока вычисления невязок соединены с третьими входами второго блока подсчета невязок, третий выход второго блока вычисления невязок соединен с четвертым входом второго блока подсчета невязок, вторые выходы второго блока подсчета невязок соединены с третьими входами двенадцатого коммутатора, первый выход второго блока подсчета невязок соединен с шестым входом первого местного устройства управления, третий выход первого местного устройства управления соединен с седьмым входом первого блока вычисления невязок, четвертый выход первого местного устройства управления соединен с восьмым входом первого блока вычисления невязок, пятый выход первого местного устройства управления соединен с девятым входом первого блока вычисления невязок, шестые выходы первого местного устройства управления соединены с четвертыми входами блока памяти коэффициентов, седьмые выходы первого местного устройства управления соединены с третьими входами блока памяти коэффициентов, восьмые выходы первого местного устройства управления соединены со вторыми входами первого блока подсчета невязок, девятый выход первого местного устройства управления соединен с первым входом первого блока подсчета невязок, десятый выход первого местного устройства управления соединен с пятым входом второго блока подсчета невязок, одиннадцатый выход первого местного устройства управления соединен с четвертым входом первого регистра-защелки, двенадцатые выходы первого местного устройства управления соединены с седьмыми входами двенадцатого коммутатора, тринадцатый выход первого местного устройства управления соединен с пятым входом второго блока подсчета невязок, четырнадцатый выход первого местного устройства управления соединен с первым входом второго блока подсчета невязок, пятнадцатые выходы первого местного устройства управления соединены со вторыми входами второго блока подсчета невязок, шестнадцатый выход первого местного устройства управления соединен с девятым входом второго блока вычисления невязок семнадцатый выход первого местного устройства управления соединен с восьмым входом второго блока вычисления невязок, восемнадцатый выход первого местного устройства управления соединен с седьмым входом второго блока вычисления невязок, первые выходы первого местного устройства управления являются пятыми выходами блока поиска позиций ошибок, вторые выходы первого местного устройства управления являются первыми выходами блока поиска позиций ошибок, первые выходы двенадцатого коммутатора соединены с первыми входами первого регистра-защелки, вторые выходы двенадцатого коммутатора соединены со вторыми входами первого регистра-защелки, третьи выходы двенадцатого коммутатора соединены с третьими входами первого регистра-защелки, вторые выходы первого регистра-защелки соединены с десятыми входами первого блока вычисления невязок, десятыми входами второго блока вычисления невязок и являются вторыми выходами блока поиска позиций ошибок, первые выходы первого регистра-защелки являются третьими выходами блока поиска позиций ошибок, третьи выходы первого регистра-защелки являются четвертыми выходами блока поиска позиций ошибок, причем блок вычисления невязок содержит тринадцатый, четырнадцатый и пятнадцатый коммутаторы, второй регистр-защелку, третий регистр-защелку, второй сумматор элементов поля Галуа, третий сумматор элементов поля Галуа, первый инвертор элементов поля Галуа, первый перемножитель элементов поля Галуа, вторую схему сравнения кодов, первый селектор нулевого элементов поля Галуа, первый логический элемент И, второй логический элемент И, логический элемент ИЛИ-НЕ, D-триггер, причем первые входы тринадцатого коммутатора являются первыми входами блока вычисления невязок, вторые входы тринадцатого коммутатора являются вторыми входами блока вычисления невязок, первые входы четырнадцатого коммутатора являются третьими входами блока вычисления невязок, вторые входы четырнадцатого коммутатора являются четвертыми входами блока вычисления невязок, первый вход пятнадцатого коммутатора является пятым входом блока вычисления невязок, второй вход пятнадцатого коммутатора является шестым входом блока вычисления невязок, третий вход тринадцатого коммутатора, третий вход четырнадцатого коммутатора, третий вход пятнадцатого коммутатора являются седьмым входом блока вычисления невязок, выходы тринадцатого коммутатора соединены с первыми входами второго регистра-защелки и вторыми входами второго сумматора элементов поля Галуа, второй вход второго регистра-защелки, второй вход третьего регистра-защелки, второй вход D-триггера являются восьмым входом блока вычисления невязок, выходы второго регистра-защелки соединены с первыми входами второго сумматора элементов поля Галуа и являются вторыми выходами блока вычисления невязок, выходы второго сумматора элементов поля Галуа соединены со входами первого инвертора элементов поля Галуа, выходы первого инвертора элементов поля Галуа соединены с первыми входами первого перемножителя элементов поля Галуа, выходы первого перемножителя элементов поля Галуа соединены со вторыми входами второй схемы сравнения кодов и являются четвертыми выходами блока вычисления невязок, первые входы второй схемы сравнения кодов являются десятыми входами блока вычисления невязок, выход второй схемы сравнения кодов соединен с первым входом первого логического элемента И, выход первого логического элемента И является пятым выходом блока вычисления невязок, выходы четырнадцатого коммутатора соединены с первыми входами третьего регистра-защелки и вторыми входами третьего сумматора элементов поля Галуа, выходы третьего регистра-защелки соединены с первыми входами третьего сумматора элементов поля Галуа и являются первыми выходами блока вычисления невязок, выходы третьего сумматора элементов поля Галуа соединены со входами первого селектора нулевого элемента поля Галуа и вторыми входами перемножителя элементов поля Галуа, выход первого селектора нулевого элемента поля Галуа соединен с первым входом второго логического элемента И, второй вход второго логического элемента И является девятым входом блока вычисления невязок, выход второго логического элемента И соединен с первым входом логического элемента ИЛИ-НЕ, выход пятнадцатого коммутатора соединен со вторым входом логического элемента ИЛИ-НЕ и первым входом D-триггера, выход D-триггера соединен с третьим входом логического элемента ИЛИ-НЕ, выход логического элемента ИЛИ-НЕ соединен со вторым входом первого логического элемента И и является третьим выходом блока вычисления невязок, причем блок подсчета невязок содержит первый блок вентилей, третий блок памяти с произвольным доступом, схему инкремента, третью схему сравнения кодов, шестнадцатый коммутатор, четвертый регистр-защелку, третий логический элемент И, четвертый логический элемент И, причем второй вход первого блока вентилей и третий вход шестнадцатого коммутатора являются первым входом блока подсчета невязок, выходы первого блока вентилей соединены с первыми входами третьего блока памяти с произвольным доступом, выходы третьего блока памяти с произвольным доступом соединены с первыми входами схемы инкремента, выходы схемы инкремента соединены с первыми входами первого блока вентилей и первыми входами третьей схемы сравнения кодов, вторые входы третьей схемы сравнения кодов соединены с шиной константы 't', выход третьей схемы сравнения кодов соединен с первым входом третьего логического элемента И, выход третьего элемента логическое И является первым выходом блока подсчета невязок, первые входы шестнадцатого коммутатора являются вторыми входами блока подсчета невязок, выходы шестнадцатого коммутатора соединены со вторыми входами третьего блока памяти с произвольным доступом, входы четвертого регистра-защелки являются третьими входами блока подсчета невязок, выходы четвертого регистра-защелки соединены со вторыми входами шестнадцатого коммутатора и являются вторыми выходами блока подсчета невязок, первый вход четвертого логического элемента И является четвертым входом блока подсчета невязок, второй вход четвертого логического элемента И является пятым входом блока подсчета невязок, выход четвертого логического элемента И соединен со вторым входом схемы инкремента и вторым входом третьего логического элемента И.

Введение в устройство блока сортировки позиций символов позволяет организовать в блоке поиска позиций ошибок поиск позиций ошибочных символов, управляемый надежностью символов кодового слова, обеспечивая тем самым быстрое нахождение позиций ошибок

Сущность изобретения состоит в том, что в процесс поиска ошибочных символов за границей половины минимального кодового расстояния вводится управление информацией о надежности принятых из канала символов. Для этого используется таблица перестановок позиций символов кодового слова, полученная в результате сортировки символов по надежности.

Для каждого кодового слова таблица перестановок формируется блоком сортировки позиций символов, в котором она хранится необходимое время. Эта таблица используется для формирования адресов памяти при записи результатов работы блока дискретного преобразования Фурье в блок поиска позиций ошибок веса t+1. Последовательное чтение данных из памяти в блоке поиска позиций ошибок формирует поток данных, упорядоченный в соответствии с надежностью символов кодового слова. В результате достаточно обработать небольшую часть этого потока, чтобы найти позиции ошибочных символов. Это значительно ускоряет работу заявляемого устройства декодирования.

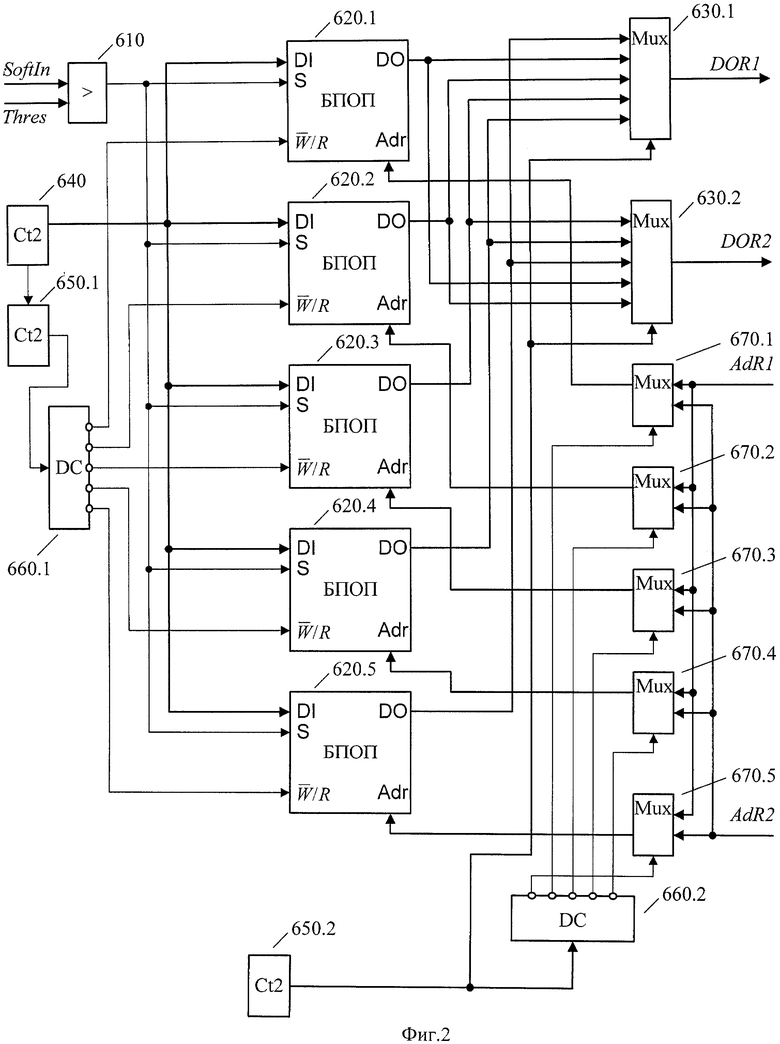

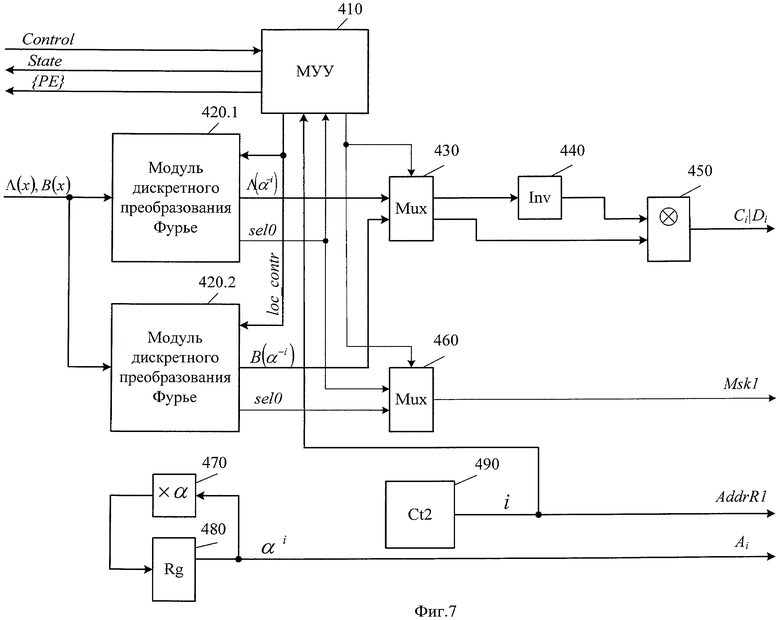

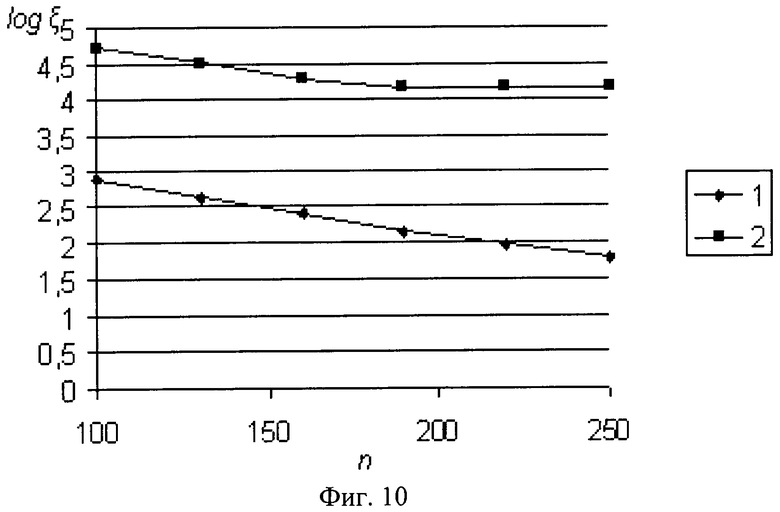

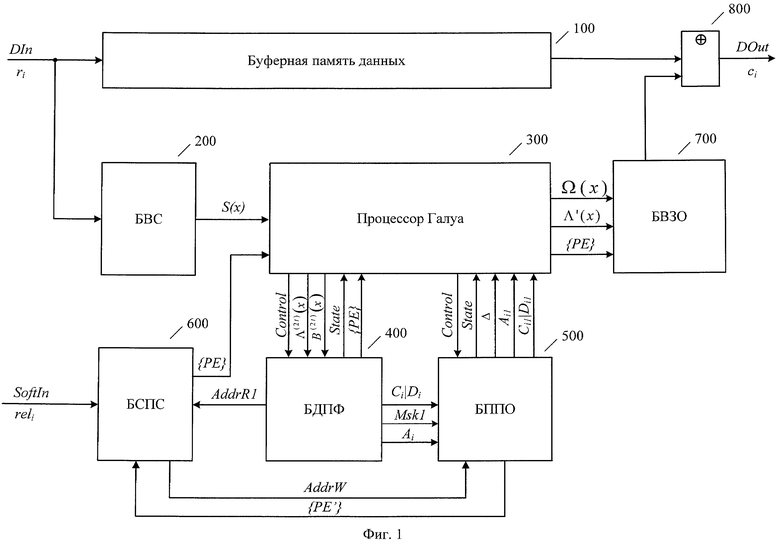

На фиг.1 приведена функциональная схема предлагаемого устройства декодирования PC-кода. На фиг.2 изображена функциональная схема блока сортировки позиций символов; на следующей фиг.3 - функциональная схема одного из его основных блоков: блока памяти отсортированных позиций. На фиг.4 приведена функциональная схема блока поиска позиций ошибок, на следующих фиг.5-6 - функциональные схемы его основных блоков: блока вычисления невязок (фиг.5), блока подсчета невязок (фиг.6). На фиг.7 показана функциональная схема блока дискретного преобразования Фурье, на следующей фиг.8 - функциональная схема одного из его основных блоков: модуля дискретного преобразования Фурье многочлена Λ(2t)(х). На фиг.9 изображена временная диаграмма обработки кодовых слов предлагаемым устройством декодирования PC-кода. На фиг.10 приведен график с результатами исследований быстродействия заявляемого устройства в канале с аддитивным белым гауссовским шумом (AWGN) и модуляцией BPSK.

В описании устройства и на чертежах используются следующие обозначения:

БВС - блок вычисления синдромов;

БСПС - блок сортировки позиций символов;

БДПФ - блок дискретного преобразования Фурье;

БППО - блок поиска позиций ошибок;

БВЗО - блок вычисления значений ошибок;

БПОП - блок памяти отсортированных позиций;

Ct2 - двоичный счетчик;

DC - дешифратор;

Mux - мультиплексор (коммутатор);

RAM - память с произвольным доступом;

Sub - вычитатель;

МУУ - местное устройство управления;

Inv - инвертор в конечном поле;

Rg - регистр;

БВ - блок вентилей;

БВН - блок вычисления невязок;

БПН - блок подсчета невязок;

БПК - блок памяти коэффициентов;

m - разрядность элемента расширенного поля Галуа GF(2m);

n - количество символов в кодовом слове PC-кода;

k - количество информационных символов в кодовом слове;

d - минимальное кодовое расстояние PC-кода, d=r+1;

t - число гарантированно исправляемых ошибок в кодовом слове  ;

;

α - примитивный элемент поля Галуа GF(2m);

r(x)=rn-1xn-1+rn-2xn-2+…+r1x+r0 - многочлен принятого из канала кодового слова;

с(х)=cn-1xn-1+сп-2xn-2+…+с1х+с0 - многочлен исправленного кодового слова;

S(x) - многочлен синдрома;

Λ(2t)(х) - многочлен локаторов ошибок после 2t итераций алгоритма Берлекэмпа-Месси;

B(2t)(x) - вспомогательный многочлен после 2t итераций алгоритма Берлекэмпа-Месси;

L2t - формальная степень многочлена локаторов ошибок Λ(2t)(х);

Λ(2t+2)(x) - многочлен локаторов ошибок, полученный аналитическим продолжением алгоритма Берлекэмпа-Месси еще на 2 итерации;

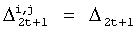

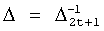

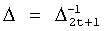

Δ2t+1 и Δ2t+2 - невязки аналитического продолжения алгоритма Берлекэмпа-Месси на 2 итерации;

Λ'(х) - формальная производная многочлена локаторов ошибок;

Ω(x) - многочлен значений ошибок;

{РЕ} - множество позиций ошибок в кодовом слове.

Устройство декодирования PC-кода (фиг.1) содержит: буферную память данных 100, блок вычисления синдромов 200, процессор Галуа 300, блок дискретного преобразования Фурье 400, блок поиска позиций ошибок веса t+1 500, блок сортировки позиций символов 600, блок вычисления значений ошибок 700, первый сумматор элементов поля Галуа 800.

На вход буферной памяти данных 100, вход блока вычисления синдромов 200 поступают символы ri кодового слова, принятого из канала (сигналы DIn). Выходы буферной памяти данных 100 соединены с первыми входами первого сумматора элементов поля Галуа 800. Выходы блока вычисления синдромов 200 соединены с первыми входами процессора Галуа 300. Первые выходы процессора Галуа 300 (сигналы Control) соединены с первыми входами блока дискретного преобразования Фурье 400. Вторые выходы процессора Галуа 300 (Λ(2t)(x)) соединены со вторыми входами блока дискретного преобразования Фурье 400. Третьи выходы процессора Галуа 300 (B(2t)(x)) соединены с третьими входами блока дискретного преобразования Фурье 400. Четвертые выходы процессора Галуа 300 (сигналы Control) соединены с четвертыми входами блока поиска позиций ошибок 500. Пятые выходы процессора Галуа 300 (Ω(х)) соединены с первыми входами блока вычисления значений ошибок 700. Шестые выходы процессора Галуа 300 (Λ'(х)) соединены со вторыми входами блока вычисления значений ошибок 700. Седьмые выходы процессора Галуа 300 ({РЕ}) соединены с третьими входами блока вычисления значений ошибок 700.

Вторые выходы блока дискретного преобразования Фурье 400 (сигналы State) соединены с третьими входами процессора Галуа 300. Третьи выходы блока дискретного преобразования Фурье 400 ({РЕ}) соединены с четвертыми входами процессора Галуа 300. Четвертые выходы блока дискретного преобразования Фурье 400 (Ci|Di) соединены с первыми входами блока поиска позиций ошибок 500. Пятый выход блока дискретного преобразования Фурье 400 (Mskl) соединен со вторым входом блока поиска позиций ошибок 500. Шестые выходы блока дискретного преобразования Фурье 400 (Ai) соединены с третьими входами блока поиска позиций ошибок 500.

Первые выходы блока поиска позиций ошибок 500 (сигналы State) соединены с пятыми входами процессора Галуа 300. Вторые выходы блока поиска позиций ошибок 500 (Δ) соединены с шестыми входами процессора Галуа 300. Третьи выходы блока поиска позиций ошибок 500 (Ai1) соединены с седьмыми входами процессора Галуа 300. Четвертые выходы блока поиска позиций ошибок 500 (Ci1|Di1) соединены с восьмыми входами процессора Галуа 300.

Первые входы блока сортировки позиций символов 600 (сигналы SoftIn) являются входами оценок надежности символов данных устройства декодирования кодов Рида-Соломона. Оценка надежности представляется двоичным числом без знака с фиксированной точкой. Большее значение числа соответствует большей надежности символов кодового слова.

Пятые выходы блока поиска позиций ошибок 500 ({РЕ'}) соединены со вторыми входами блока сортировки позиций символов 600. Первые выходы блока дискретного преобразования Фурье 400 (AddrR1) соединены с третьими входами блока сортировки позиций символов 600. Первые выходы блока сортировки позиций символов 600 ({РЕ}) соединены со вторыми входами процессора Галуа 300. Вторые выходы блока сортировки позиций символов 600 (AddrW) соединены с пятыми входами блока поиска позиций ошибок 500.

Выходы блока вычисления значений ошибок 700 соединены со вторыми входами первого сумматора элементов поля Галуа 800. Выходы первого сумматора элементов поля Галуа 800 являются выходами данных устройства декодирования кодов Рида-Соломона (сигналы DOut).

Блок сортировки позиций символов 600 (фиг.2) содержит первую схему сравнения кодов 610, первый блок памяти отсортированных позиций 620.1, второй блок памяти отсортированных позиций 620.2, третий блок памяти отсортированных позиций 620.3, четвертый блок памяти отсортированных позиций 620.4, пятый блок памяти отсортированных позиций 620.5, первый коммутатор 630.1, второй коммутатор 630.2, третий коммутатор 670.1, четвертый коммутатор 670.2, пятый коммутатор 670.3, шестой коммутатор 670.4, седьмой коммутатор 670.5, первый счетчик 640, второй счетчик 650.1, третий счетчик 650.2, первый дешифратор 660.1, второй дешифратор 660.2.

Первые входы первой схемы сравнения кодов 610 (сигналы SoftIn) являются первыми входами блока сортировки позиций символов, а вторые входы первой схемы сравнения кодов соединены с шиной константы Thres. Выход первой схемы сравнения кодов 610 соединен со вторым входом первого блока памяти отсортированных позиций 620.1, со вторым входом второго блока памяти отсортированных позиций 620.2, со вторым входом третьего блока памяти отсортированных позиций 620.3, со вторым входом четвертого блока памяти отсортированных позиций 620.4 и со вторым входом пятого блока памяти отсортированных позиций 620.5. Первые выходы первого счетчика 640 соединены с первыми входами первого блока памяти отсортированных позиций 620.1, с первыми входами второго блока памяти отсортированных позиций 620.2, с первыми входами третьего блока памяти отсортированных позиций 620.3, с первыми входами четвертого блока памяти отсортированных позиций 620.4 и с первыми входами пятого блока памяти отсортированных позиций 620.5. Второй выход первого счетчика 640 соединен со входом второго счетчика 650.1. Выходы второго счетчика 650.1 соединены со входами первого дешифратора 660.1. Первый выход первого дешифратора 660.1 соединен с третьим входом  первого блока памяти отсортированных позиций 620.1. Второй выход первого дешифратора 660.1 соединен с третьим входом

первого блока памяти отсортированных позиций 620.1. Второй выход первого дешифратора 660.1 соединен с третьим входом  второго блока памяти отсортированных позиций 620.2. Третий выход первого дешифратора 660.1 соединен с третьим входом

второго блока памяти отсортированных позиций 620.2. Третий выход первого дешифратора 660.1 соединен с третьим входом  третьего блока памяти отсортированных позиций 620.3. Четвертый выход первого дешифратора 660.1 соединен с третьим входом

третьего блока памяти отсортированных позиций 620.3. Четвертый выход первого дешифратора 660.1 соединен с третьим входом  четвертого блока памяти отсортированных позиций 620.4. Пятый выход первого дешифратора 660.1 соединен с третьим входом

четвертого блока памяти отсортированных позиций 620.4. Пятый выход первого дешифратора 660.1 соединен с третьим входом  пятого блока памяти отсортированных позиций 620.5. Выходы первого блока памяти отсортированных позиций 620.1 соединены со вторыми входами первого коммутатора 630.1 и четвертыми входами второго коммутатора 630.2. Выходы второго блока памяти отсортированных позиций 620.2 соединены с третьими входами первого коммутатора 630.1 и пятыми входами второго коммутатора 630.2. Выходы третьего блока памяти отсортированных позиций 620.3 соединены с четвертыми входами первого коммутатора 630.1 и первыми входами второго коммутатора 630.2. Выходы четвертого блока памяти отсортированных позиций 620.4 соединены с пятыми входами первого коммутатора 630.1 и вторыми входами второго коммутатора 630.2. Выходы пятого блока памяти отсортированных позиций 620.5 соединены с первыми входами первого коммутатора 630.1 и третьими входами второго коммутатора 630.2. Выходы третьего счетчика 650.2 соединены с шестыми входами первого коммутатора 630.1, с шестыми входами второго коммутатора 630.2 и входами второго дешифратора 660.2. Первый выход второго дешифратора 660.2 соединен с третьим входом седьмого коммутатора 670.5, второй выход второго дешифратора 660.2 соединен с третьим входом третьего коммутатора 670.1. Третий выход второго дешифратора 660.2 соединен с третьим входом четвертого коммутатора 670.2. Четвертый выход второго дешифратора 660.2 соединен с третьим входом пятого коммутатора 670.3. Пятый выход второго дешифратора 660.2 соединен с третьим входом шестого коммутатора 670.4. Первые входы третьего 670.1, четвертого 670.2, пятого 670.3, шестого 670.4 и седьмого 670.5 коммутаторов (сигналы AdR1) являются третьими входами блока сортировки позиций символов 600. Вторые входы третьего 670.1, четвертого 670.2, пятого 670.3, шестого 670.4 и седьмого 670.5 коммутаторов (сигналы AdR2) являются вторыми входами блока сортировки позиций символов 600. Выходы третьего коммутатора 670.1 соединены с четвертыми входами Adr первого блока памяти отсортированных позиций 620.1. Выходы четвертого коммутатора 670.2 соединены с четвертыми входами Adr второго блока памяти отсортированных позиций 620.2. Выходы пятого коммутатора 670.3 соединены с четвертыми входами Adr третьего блока памяти отсортированных позиций 620.3. Выходы шестого коммутатора 670.4 соединены с четвертыми входами Adr четвертого блока памяти отсортированных позиций 620.4. Выходы седьмого коммутатора 670.5 соединены с четвертыми входами Adr пятого блока памяти отсортированных позиций 620.5. Выходы первого коммутатора 630.1 (сигналы DOR1) являются вторыми выходами блока сортировки позиций символов. Выходы второго коммутатора 630.2 (сигналы DOR2) являются первыми выходами блока сортировки позиций символов.

пятого блока памяти отсортированных позиций 620.5. Выходы первого блока памяти отсортированных позиций 620.1 соединены со вторыми входами первого коммутатора 630.1 и четвертыми входами второго коммутатора 630.2. Выходы второго блока памяти отсортированных позиций 620.2 соединены с третьими входами первого коммутатора 630.1 и пятыми входами второго коммутатора 630.2. Выходы третьего блока памяти отсортированных позиций 620.3 соединены с четвертыми входами первого коммутатора 630.1 и первыми входами второго коммутатора 630.2. Выходы четвертого блока памяти отсортированных позиций 620.4 соединены с пятыми входами первого коммутатора 630.1 и вторыми входами второго коммутатора 630.2. Выходы пятого блока памяти отсортированных позиций 620.5 соединены с первыми входами первого коммутатора 630.1 и третьими входами второго коммутатора 630.2. Выходы третьего счетчика 650.2 соединены с шестыми входами первого коммутатора 630.1, с шестыми входами второго коммутатора 630.2 и входами второго дешифратора 660.2. Первый выход второго дешифратора 660.2 соединен с третьим входом седьмого коммутатора 670.5, второй выход второго дешифратора 660.2 соединен с третьим входом третьего коммутатора 670.1. Третий выход второго дешифратора 660.2 соединен с третьим входом четвертого коммутатора 670.2. Четвертый выход второго дешифратора 660.2 соединен с третьим входом пятого коммутатора 670.3. Пятый выход второго дешифратора 660.2 соединен с третьим входом шестого коммутатора 670.4. Первые входы третьего 670.1, четвертого 670.2, пятого 670.3, шестого 670.4 и седьмого 670.5 коммутаторов (сигналы AdR1) являются третьими входами блока сортировки позиций символов 600. Вторые входы третьего 670.1, четвертого 670.2, пятого 670.3, шестого 670.4 и седьмого 670.5 коммутаторов (сигналы AdR2) являются вторыми входами блока сортировки позиций символов 600. Выходы третьего коммутатора 670.1 соединены с четвертыми входами Adr первого блока памяти отсортированных позиций 620.1. Выходы четвертого коммутатора 670.2 соединены с четвертыми входами Adr второго блока памяти отсортированных позиций 620.2. Выходы пятого коммутатора 670.3 соединены с четвертыми входами Adr третьего блока памяти отсортированных позиций 620.3. Выходы шестого коммутатора 670.4 соединены с четвертыми входами Adr четвертого блока памяти отсортированных позиций 620.4. Выходы седьмого коммутатора 670.5 соединены с четвертыми входами Adr пятого блока памяти отсортированных позиций 620.5. Выходы первого коммутатора 630.1 (сигналы DOR1) являются вторыми выходами блока сортировки позиций символов. Выходы второго коммутатора 630.2 (сигналы DOR2) являются первыми выходами блока сортировки позиций символов.

Все используемые в блоке 600 счетчики - двоичные: счетчик 640 работает с коэффициентом пересчета n, счетчики 650 работают с коэффициентом перечета 5.

Дешифраторы 660 имеют инверсные выходы. На i-х выходах дешифраторов (i=1,…,5) появляются значения логического ноля (активный уровень), когда на их входы подаются значения «i-1».

Все коммутаторы в блоке 600-m-разрядные. На выходы коммутаторов 630 подаются значения их «i-х» входов (i=1,…,5), если на их шестые входы подаются значения «i-1». На выходы коммутаторов 670 подаются значения их первых входов, если на их третьи входы подаются значения логического ноля.

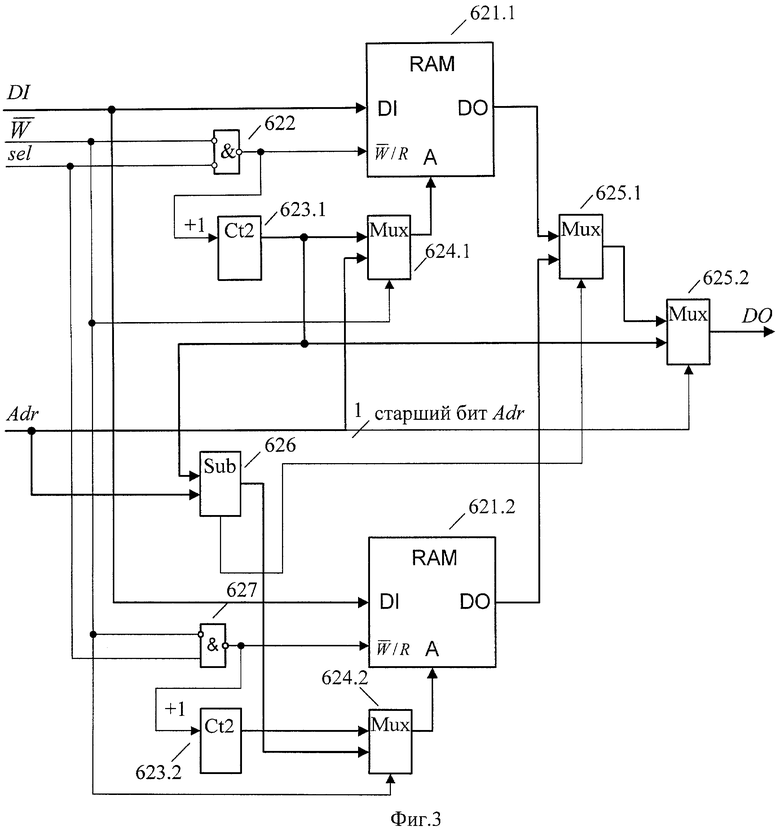

Блок памяти отсортированных позиций (фиг.3) содержит первый блок памяти с произвольным доступом 621.1, второй блок памяти с произвольным доступом 621.2, первый логический элемент И-НЕ 622, второй логический элемент И-НЕ 627, четвертый счетчик 623.1, пятый счетчик 623.2, восьмой коммутатор 624.1, девятый коммутатор 624.2, десятый коммутатор 625.1, одиннадцатый коммутатор 625.2 и вычитатель 626.

Первые входы первого блока памяти с произвольным доступом 621.1, первые входы второго блока памяти с произвольным доступом 621.2 являются первыми входами DI блока памяти отсортированных позиций. Первый вход первого логического элемента И-НЕ 622, первый вход второго логического элемента И-НЕ 627, третий вход восьмого коммутатора 624.1, третий вход девятого коммутатора 624.2 являются третьим входом  блока памяти отсортированных позиций. Второй вход первого логического элемента И-НЕ 622, второй вход второго логического элемента И-НЕ 627 являются вторым входом S блока памяти отсортированных позиций. Выход первого логического элемента И-НЕ 622 соединен со вторым входом

блока памяти отсортированных позиций. Второй вход первого логического элемента И-НЕ 622, второй вход второго логического элемента И-НЕ 627 являются вторым входом S блока памяти отсортированных позиций. Выход первого логического элемента И-НЕ 622 соединен со вторым входом  первого блока памяти с произвольным доступом 621.1 и входом четвертого счетчика 623.1. Выходы четвертого счетчика 623.1 соединены с первыми входами восьмого коммутатора 624.1, вторыми входами одиннадцатого коммутатора 625.2 и первыми входами вычитателя 626. Выходы восьмого коммутатора 624.1 соединены с третьими входами А первого блока памяти с произвольным доступом 621.1. Выходы первого блока памяти с произвольным доступом 621.1 соединены с первыми входами десятого коммутатора 625.1. Выход второго логического элемента И-НЕ 627 соединен со вторым входом

первого блока памяти с произвольным доступом 621.1 и входом четвертого счетчика 623.1. Выходы четвертого счетчика 623.1 соединены с первыми входами восьмого коммутатора 624.1, вторыми входами одиннадцатого коммутатора 625.2 и первыми входами вычитателя 626. Выходы восьмого коммутатора 624.1 соединены с третьими входами А первого блока памяти с произвольным доступом 621.1. Выходы первого блока памяти с произвольным доступом 621.1 соединены с первыми входами десятого коммутатора 625.1. Выход второго логического элемента И-НЕ 627 соединен со вторым входом  второго блока памяти с произвольным доступом 621.2 и входом пятого счетчика 623.2. Выходы пятого счетчика 623.2 соединены с первыми входами девятого коммутатора 624.2. Выходы девятого коммутатора 624.2 соединены с третьими входами А второго блока памяти с произвольным доступом 621.2. Выходы второго блока памяти с произвольным доступом 621.2 соединены со вторыми входами десятого коммутатора 625.1. Вторые входы вычитателя 626 и вторые входы восьмого коммутатора 624.1 (сигналы Adr) являются четвертыми входами блока памяти отсортированных позиций, а старший разряд четвертых входов блока памяти отсортированных позиций соединен с третьим входом одиннадцатого коммутатора 625.2. Первые выходы вычитателя 626 соединены со вторыми входами девятого коммутатора 624.2. Второй выход вычитателя 626 соединен с третьим входом десятого коммутатора 625.1. Выходы десятого коммутатора 625.1 соединены с первыми входами одиннадцатого коммутатора 625.2. Выходы одиннадцатого коммутатора 625.2 являются выходами блока памяти отсортированных позиций.

второго блока памяти с произвольным доступом 621.2 и входом пятого счетчика 623.2. Выходы пятого счетчика 623.2 соединены с первыми входами девятого коммутатора 624.2. Выходы девятого коммутатора 624.2 соединены с третьими входами А второго блока памяти с произвольным доступом 621.2. Выходы второго блока памяти с произвольным доступом 621.2 соединены со вторыми входами десятого коммутатора 625.1. Вторые входы вычитателя 626 и вторые входы восьмого коммутатора 624.1 (сигналы Adr) являются четвертыми входами блока памяти отсортированных позиций, а старший разряд четвертых входов блока памяти отсортированных позиций соединен с третьим входом одиннадцатого коммутатора 625.2. Первые выходы вычитателя 626 соединены со вторыми входами девятого коммутатора 624.2. Второй выход вычитателя 626 соединен с третьим входом десятого коммутатора 625.1. Выходы десятого коммутатора 625.1 соединены с первыми входами одиннадцатого коммутатора 625.2. Выходы одиннадцатого коммутатора 625.2 являются выходами блока памяти отсортированных позиций.

Блоки памяти с произвольным доступом 621 содержат n log2n-разрядных ячеек. Счетчики 623 - двоичные log2n-разрядные. Такую же разрядность имеют коммутаторы 624 и 625. Они осуществляют коммутацию с двух направлений, передавая значения своих первых входов на выходы, когда на их третьи входы подается значение логического ноля.

Вычитатель 626 осуществляет вычитание содержимого счетчика 623.1 из значения, поданного на четвертые входы блока 620 (сигналы Adr). На втором выходе вычитателя формируется сигнал заема.

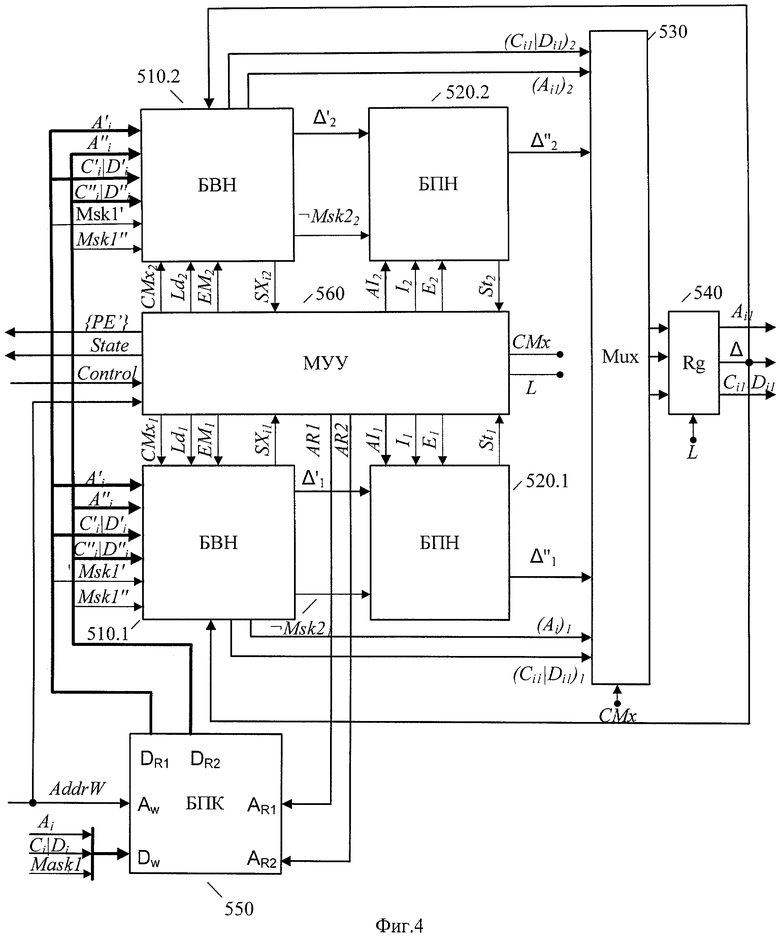

Блок поиска позиций ошибок (фиг.4) содержит первый блок вычисления невязок 510.1, второй блок вычисления невязок 510.2, первый блок подсчета невязок 520.1, второй блок подсчета невязок 520.2, двенадцатый коммутатор 530, первый регистр-защелку 540, блок памяти коэффициентов 550, первое местное устройство управления 560.

Первые входы первого местного устройства управления 560 (сигналы Control) являются четвертыми входами блока поиска позиций ошибок 500. Вторые входы первого местного устройства управления 560 и первые входы блока памяти коэффициентов 550 (сигналы AddrW) являются пятыми входами блока поиска позиций ошибок. Третьи входы блока поиска позиций ошибок 500 (сигналы Ai) являются младшими разрядами вторых входов блока памяти коэффициентов 550. Первые входы блока поиска позиций ошибок 500 являются средними разрядами вторых входов блока памяти коэффициентов 550 (Ci|Di). Второй вход блока поиска позиций ошибок 500 (Msk1) является старшим разрядом вторых входов блока памяти коэффициентов 550 (Mask1). Младшие разряды первых выходов DR1 блока памяти коэффициентов 550 (сигналы A'i) соединены с первыми входами первого блока вычисления невязок 510.1 и с первыми входами второго блока вычисления невязок 510.2. Средние разряды первых выходов DR1 блока памяти коэффициентов 550 (C'i|D'i) соединены с третьими входами первого блока вычисления невязок 510.1 и с третьими входами второго блока вычисления невязок 510.2. Старший разряд первых выходов DR1 блока памяти коэффициентов 550 (Msk1') соединен с пятым входом первого блока вычисления невязок 510.1 и с пятым входом второго блока вычисления невязок 510.2. Младшие разряды вторых выходов DR2 блока памяти коэффициентов 550 (А''i) соединены со вторыми входами первого блока вычисления невязок 510.1 и со вторыми входами второго блока вычисления невязок 510.2. Средние разряды вторых выходов DR2 блока памяти коэффициентов 550 (С''i|D''i) соединены с четвертыми входами первого блока вычисления невязок 510.1 и с четвертыми входами второго блока вычисления невязок 510.2. Старший разряд вторых выходов DR2 блока памяти коэффициентов 550 (Msk1'') соединен с шестым входом первого блока вычисления невязок 510.1 и с шестым входом второго блока вычисления невязок 510.2.

Первые выходы первого блока вычисления невязок 510.1 (сигналы (Ci1|Di1)1) соединены с шестыми входами двенадцатого коммутатора 530. Вторые выходы первого блока вычисления невязок 510.1 ((Ai1)1) соединены с пятыми входами двенадцатого коммутатора 530. Третий выход первого блока вычисления невязок 510.1 (¬Msk21) соединен с четвертым входом первого блока подсчета невязок 520.1. Четвертые выходы первого блока вычисления невязок 510.1 (Δ'1) соединены с третьими входами первого блока подсчета невязок 520.1. Пятый выход первого блока вычисления невязок 510.1 (SXi1) соединен с третьим входом местного устройства управления 560. Первый выход первого блока подсчета невязок 520.1 (St1) соединен с пятым входом первого местного устройства управления 560. Вторые выходы первого блока подсчета невязок 520.1 (Δ''1) соединены с четвертыми входами двенадцатого коммутатора 530.

Первые выходы второго блока вычисления невязок 510.1 (сигналы (Ci1|Di1)2) соединены с первыми входами двенадцатого коммутатора 530. Вторые выходы второго блока вычисления невязок 510.2 ((Ai1)2) соединены со вторыми входами двенадцатого коммутатора 530. Пятый выход второго блока вычисления невязок 510.2 (SXi2) соединен с четвертым входом первого местного устройства управления 560. Четвертые выходы второго блока вычисления невязок 510.2 (Δ'2) соединены с третьими входами второго блока подсчета невязок 520.2. Третий выход второго блока вычисления невязок 510.2 (¬Msk22) соединен с четвертым входом второго блока подсчета невязок 520.2. Вторые выходы второго блока подсчета невязок 520.2 (Δ''2) соединены с третьими входами двенадцатого коммутатора 530. Первый выход второго блока подсчета невязок 520.2 (St2) соединен с шестым входом первого местного устройства управления 560. Третий выход первого местного устройства управления 560 (CMx1) соединен с седьмым входом первого блока вычисления невязок 510.1. Четвертый выход первого местного устройства управления 560 (Ld1) соединен с восьмым входом первого блока вычисления невязок 510.1. Пятый выход первого местного устройства управления 560 (EM1) соединен с девятым входом первого блока вычисления невязок 510.1. Шестые выходы первого местного устройства управления 560 (AR1) соединены с четвертыми входами AR1 блока памяти коэффициентов 550. Седьмые выходы первого местного устройства управления 560 (AR2) соединены с третьими входами AR2 блока памяти коэффициентов 550. Восьмые выходы первого местного устройства управления 560 (AI1) соединены со вторыми входами первого блока подсчета невязок 520.1. Девятый выход первого местного устройства управления 560 (I1) соединен с первым входом первого блока подсчета невязок 520.1. Десятый выход местного первого устройства управления 560 (E1) соединен с пятым входом первого блока подсчета невязок 520.1. Одиннадцатый выход первого местного устройства управления 560 (L) соединен с четвертым входом первого регистра-защелки 540. Двенадцатые выходы первого местного устройства управления 560 (СМх) соединены с седьмыми входами двенадцатого коммутатора 530. Тринадцатый выход первого местного устройства управления 560 (Е2) соединен с пятым входом второго блока подсчета невязок 520.2. Четырнадцатый выход первого местного устройства управления 560 (I2) соединен с первым входом второго блока подсчета невязок 520.2. Пятнадцатые выходы первого местного устройства управления 560 (AI2) соединены со вторыми входами второго блока подсчета невязок 520.2. Шестнадцатый выход первого местного устройства управления 560 (ЕМ2) соединен с девятым входом второго блока вычисления невязок 510.2. Семнадцатый выход первого местного устройства управления 560 (Ld2) соединен с восьмым входом второго блока вычисления невязок 510.2. Восемнадцатый выход первого местного устройства управления 560 (СМх2) соединен с седьмым входом второго блока вычисления невязок 510.2. Первые выходы первого местного устройства управления 560 ({РЕ'}) являются пятыми выходами блока поиска позиций ошибок 500. Вторые выходы первого местного устройства управления 560 (State) являются первыми выходами блока поиска позиций ошибок 500. Первые выходы двенадцатого коммутатора 530 соединены с первыми входами первого регистра-защелки 540. Вторые выходы двенадцатого коммутатора 530 соединены со вторыми входами первого регистра-защелки 540. Третьи выходы двенадцатого коммутатора 530 соединены с третьими входами первого регистра-защелки 540. Вторые выходы первого регистра-защелки 540 (Δ) соединены с десятыми входами первого блока вычисления невязок 510.1, десятыми входами второго блока вычисления невязок 510.2 и являются вторыми выходами блока поиска позиций ошибок 500. Первые выходы первого регистра-защелки 540 (Ai1) являются третьими выходами блока поиска позиций ошибок 500. Третьи выходы первого регистра-защелки 540 (Ci1|Di1) являются четвертыми выходами блока поиска позиций ошибок 500.

Коммутатор 530 - трехсекционный двунаправленный. Первый и шестой входы коммутатора являются входами первой секции, второй и пятый входы - входами второй секции, третий и четвертый входы - входами третьей секции.

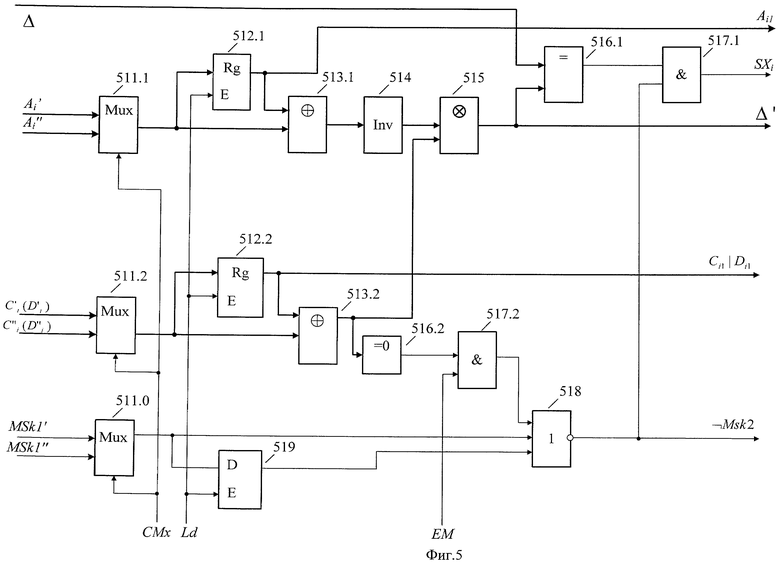

Блок вычисления невязок (фиг.5) содержит тринадцатый 511.1, четырнадцатый 511.2 и пятнадцатый коммутаторы 511.0, второй регистр-защелку 512.1, третий регистр-защелку 512.2, второй сумматор элементов поля Галуа 513.1, третий сумматор элементов поля Галуа 513.2, первый инвертор элементов поля Галуа 514, первый перемножитель элементов поля Галуа 515, вторую схему сравнения кодов 516.1, первый селектор нулевого элемента поля Галуа 516.2, первый логический элемент И 517.2, второй логический элемент И 517.1, логический элемент ИЛИ-НЕ 518, D-триггер 519.

Первые входы тринадцатого коммутатора 511.1 (сигнал Ai ') являются первыми входами блока вычисления невязок. Вторые входы тринадцатого коммутатора 511.1 (Ai'') являются вторыми входами блока вычисления невязок. Первые входы четырнадцатого коммутатора 511.2 (C'i(D'i)) являются третьими входами блока вычисления невязок. Вторые входы четырнадцатого коммутатора 511.2 (С''i(D''i)) являются четвертыми входами блока вычисления невязок. Первый вход пятнадцатого коммутатора 511.0 (Msk1') является пятым входом блока вычисления невязок. Второй вход пятнадцатого коммутатора 511.0 (MSk1'') является шестым входом блока вычисления невязок.

Третий вход тринадцатого коммутатора 511.1, третий вход четырнадцатого коммутатора 511.2, третий вход пятнадцатого коммутатора 511.0 являются седьмым входом блока вычисления невязок, на который подается сигнал СМх. Выходы тринадцатого коммутатора 511.1 соединены с первыми входами второго регистра-защелки 512.1 и вторыми входами второго сумматора элементов поля Галуа 513.1. Второй вход второго регистра-защелки 512.1, второй вход третьего регистра-защелки 512.2, второй вход D-триггера 519 являются восьмым входом блока вычисления невязок, на который подается сигнал Ld. Выходы второго регистра-защелки 512.1 (сигналы Ai1) соединены с первыми входами второго сумматора элементов поля Галуа 513.1 и являются вторыми выходами блока вычисления невязок. Выходы второго сумматора элементов поля Галуа 513.1 соединены со входами первого инвертора элементов поля Галуа 514. Выходы первого инвертора элементов поля Галуа 514 соединены с первыми входами первого перемножителя элементов поля Галуа 515. Выходы первого перемножителя элементов поля Галуа 515 (сигналы Δ') соединены со вторыми входами второй схемы сравнения кодов 516.1 и являются четвертыми выходами блока вычисления невязок. Первые входы второй схемы сравнения кодов 516.1 являются десятыми входами блока вычисления невязок, на которые подаются сигналы Δ. Выход второй схемы сравнения кодов 516.1 соединен с первым входом первого логического элемента И 517.1. Выход первого логического элемента И 517.1 (сигнал SXi) является пятым выходом блока вычисления невязок. Выходы четырнадцатого коммутатора 511.2 соединены с первыми входами третьего регистра-защелки 512.2 и вторыми входами третьего сумматора элементов поля Галуа 513.3. Выходы третьего регистра-защелки 512.2 (Ci1|Di1) соединены с первыми входами третьего сумматора элементов поля Галуа 513.2 и являются первыми выходами блока вычисления невязок. Выходы третьего сумматора элементов поля Галуа 513.2 соединены со входами первого селектора нулевого элемента поля Галуа 516.2 и вторыми входами первого перемножителя элементов поля Галуа 515. Выход первого селектора нулевого элемента поля Галуа 516.2 соединен с первым входом второго логического элемента И 517.2. Второй вход второго логического элемента И 517.2 является девятым входом блока вычисления невязок, на который подается сигнал ЕМ. Выход второго логического элемента И 517.2 соединен с первым входом логического элемента ИЛИ-НЕ 518. Выход пятнадцатого коммутатора 511.0 соединен со вторым входом логического элемента ИЛИ-НЕ 518 и первым входом D-триггера 519. Выход D-триггера 519 соединен с третьим входом логического элемента ИЛИ-НЕ 518. Выход логического элемента ИЛИ-НЕ 518 (¬Msk2) соединен со вторым входом первого логического элемента И 517.1 и является третьим выходом блока вычисления невязок.

Регистры-защелки 512 и D-триггер 519 принимают информацию при активном сигнале Ld, который подается на их вторые входы.

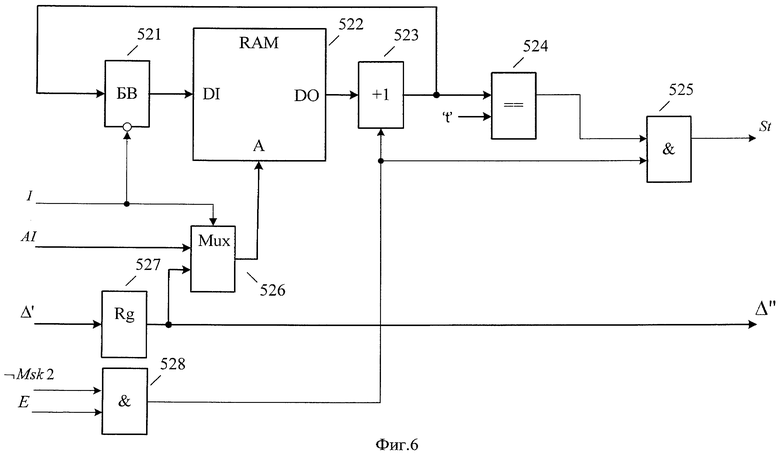

Блок подсчета невязок (фиг.6) содержит первый блок вентилей 521, третий блок памяти с произвольным доступом 522, схему инкремента 523, третью схему сравнения кодов 524, третий логический элемент И 525, шестнадцатый коммутатор 526, четвертый регистр-защелку 527, четвертый логический элемент И 528.

Второй вход первого блока вентилей и третий вход шестнадцатого коммутатора являются первым входом блока подсчета невязок, на который подается сигнал I. Выходы первого блока вентилей соединены с первыми входами DI третьего блока памяти с произвольным доступом 522. Выходы третьего блока памяти с произвольным доступом 522 соединены с первыми входами схемы инкремента 523. Выходы схемы инкремента 523 соединены с первыми входами первого блока вентилей 521 и первыми входами третьей схемы сравнения кодов 524. Вторые входы третьей схемы сравнения кодов 524 соединены с шиной константы 't'. Выход третьей схемы сравнения кодов 524 соединен с первым входом третьего логического элемента И 525. Выход третьего элемента логическое И 525 является первым выходом блока подсчета невязок, на котором формируется сигнал St. Первые входы шестнадцатого коммутатора 526 являются вторыми входами блока подсчета невязок, на который подаются сигналы AI. Выходы шестнадцатого коммутатора 526 соединены со вторыми входами А третьего блока памяти с произвольным доступом 522. Входы четвертого регистра-защелки 527 являются третьими входами блока подсчета невязок, на который подаются сигналы Δ'. Выходы четвертого регистра-защелки 527 (сигналы Δ''n) соединены со вторыми входами шестнадцатого коммутатора 526 и являются вторыми выходами блока подсчета невязок. Первый вход четвертого логического элемента И 528 является четвертым входом блока подсчета невязок, на который подается сигнал ¬Msk2. Второй вход четвертого логического элемента И 528 является пятым входом блока подсчета невязок, на который подается сигнал Е. Выход четвертого логического элемента И 528 соединен со вторым входом схемы инкремента 523 и вторым входом третьего логического элемента И 525.

Блок вентилей 521 передает информацию с первых входов на выходы, когда на второй его вход подается логический ноль, в противном случае на его выходах формируются нули.

Блок дискретного преобразования Фурье (фиг.7) содержит второе местное устройство управления 410, первый модуль дискретного преобразования Фурье многочлена Λ(2t)(х) 420.1, второй модуль дискретного преобразования Фурье многочлена В(2t)(х) 420.2, семнадцатый коммутатор 430, второй инвертор элементов поля Галуа 440, второй перемножитель двух элементов поля Галуа 450, восемнадцатый двухвходовый коммутатор 460, умножитель на α 470, пятый регистр-защелку 480, работающую по фронту тактового сигнала; шестой двоичный счетчик номеров позиций принятого слова 490 с коэффициентом пересчета n.

Первые входы второго местного устройства управления 410 являются первыми входами блока дискретного преобразования Фурье 400, на которые подаются сигналы Control. Первые выходы второго местного устройства управления 400 являются вторыми выходами блока дискретного преобразования Фурье 400, на которые выдаются сигналы State. Вторые выходы второго местного устройства управления 410 являются третьими выходами блока дискретного преобразования Фурье 400, на которые выдаются сигналы {РЕ}. Третьи выходы второго местного устройства управления 410 соединены со вторыми входами первого модуля дискретного преобразования Фурье 420.1 и со вторыми входами второго модуля дискретного преобразования Фурье 420.2. Четвертый выход второго местного устройства управления 410 соединен с третьим входом семнадцатого коммутатора 430 и с третьим входом восемнадцатого коммутатора 460. Первые входы первого модуля дискретного преобразования Фурье 420.1 и второго модуля дискретного преобразования Фурье 420.2 являются вторыми и третьими входами блока дискретного преобразования Фурье 400, на которые подаются сигналы Λ(х), В(х). Первые выходы первого модуля дискретного преобразования Фурье 420.1 (сигналы Λ(α-1)) соединены с первыми входами семнадцатого коммутатора 430. Второй выход первого модуля дискретного преобразования Фурье 420.1 (sel0) соединен с третьим входом второго местного устройства управления 410 и первым входом восемнадцатого коммутатора 460. Первые выходы второго модуля дискретного преобразования Фурье 420.2 (В(α-1)) соединены со вторыми входами семнадцатого коммутатора 430. Второй выход второго модуля дискретного преобразования Фурье 420.2 (sel0) соединен со вторым входом восемнадцатого коммутатора 460. Первые выходы семнадцатого коммутатора 430 соединены со входами второго инвертора элементов поля Галуа 440. Вторые выходы семнадцатого коммутатора соединены со вторыми входами второго перемножителя элементов поля Галуа 450. Выходы второго инвертора элементов поля Галуа 440 соединены с первыми входами второго перемножителя элементов поля Галуа 450. Выходы второго перемножителя элементов поля Галуа являются четвертыми выходами блока дискретного преобразования Фурье 400, на которые выдаются сигналы (Ci|Di). Выход восемнадцатого коммутатора 460 является пятым выходом блока дискретного преобразования Фурье 400, на который выдается сигнал Msk1. Выходы шестого двоичного счетчика 490 соединены со вторыми входами второго местного устройства управления 410 и являются первыми выходами блока дискретного преобразования Фурье 400, на которые выдаются сигналы AddrR1. Выходы умножителя на α 470 соединены со входами пятого регистра-защелки 480. Выходы пятого регистра-защелки 480 соединены со входами умножителя на α 470 и являются шестыми выходами блока дискретного преобразования Фурье 400, на которые выдаются сигналы Ai.

Семнадцатый коммутатор 430 - перекресный. Когда сигнал на третьем входе - активный, коммутатор работает в режиме перекрестной передачи: значения его первых входов подаются на вторые выходы, значения его вторых входов подаются на первые выходы. При неактивном сигнале на третьем входе коммутатор работает в режиме прямой передачи.

Модуль дискретного преобразования Фурье (фиг.8) содержит второй блок вентилей 421, шестой, седьмой, восьмой, …, t+7 регистры-защелки, работающие по фронту тактового импульса, 422.0 - 422.t+1, четвертый сумматор элементов поля Галуа на t+2 входа 423, второй селектор нулевого элемента поля Галуа 424, первый, второй, …, t+1 умножители на постоянные коэффициенты в поле Галуа 425.1 - 425.t+1, первый, второй, …, t+1 блоки логических элементов ИЛИ 426.1-426.t+1.

Первые входы второго блока вентилей 421 являются первыми входами модуля дискретного преобразования Фурье, на которые подаются сигналы Λ(х). Второй вход второго блока вентилей 421 (сигнал enable) подключен к шине loc_contr, представляющей вторые входы БДПФ 400. Выходы второго блока вентилей 421 соединены с первыми входами шестого регистра-защелки 422.0, вторыми входами первого, второго, …, t+1 блоков логических элементов ИЛИ 426.1, …, 426.t+1. Вторые входы шестого, седьмого, восьмого, …, t+7 регистров-защелок подключены к шине loc_contr (сигналы c0…ct+1). Третьи входы шестого, седьмого, восьмого, …, t+7 регистров-защелок подключены к шине loc_contr (сигнал clear). Выходы первого, второго, …, t+1 блоков логических элементов ИЛИ 426.1,…, 426.t+1 соединены с первыми входами седьмого, восьмого, …, t+7 регистров-защелок 422.1, …, 425.t+1 соответственно. Выходы шестого регистра-защелки 422.0 соединены с первыми входами четвертого сумматора элементов поля Галуа 423. Выходы седьмого, восьмого, …, t+7 регистров-защелок 422.1, …, 425.t+1 соединены соответственно со вторыми, третьими, …, t+2 входами четвертого сумматора элементов поля Галуа 423 и входами первого, второго, …, t+1 умножителя на постоянные коэффициенты в поле Галуа 425.1, …, 425.t+1, соответственно. Выходы первого, второго, …, t+1 умножителя на постоянные коэффициенты в поле Галуа 425.1…425.t+1 соединены с первыми входами первого, второго, …, t+1 блоков логических элементов ИЛИ 426.1, …, 426.t+1 соответственно. Выходы четвертого сумматора элементов поля Галуа 423 соединены со входами второго селектора нулевого элемента поля Галуа 424 и являются первыми выходами модуля дискретного преобразования Фурье, на которые выдаются сигналы Λ(w). Выход второго селектора нулевого элемента поля Галуа 424 является вторым выходом модуля дискретного преобразования Фурье, на который выдается сигнал sel0.

Все линии связи, соединяющие блоки на фиг.1-8, по которым передаются данные в виде элементов поля Галуа, являются m-разрядными.

Все используемые триггеры, регистры и счетчики работают по переднему фронту тактового сигнала, который на фиг.1-7 не показан, но подразумевается.

Сумматоры элементов поля, умножители на постоянные коэффициенты и блоки нахождения обратного элемента поля могут быть реализованы известным образом, в частности, сумматоры могут быть реализованы на m двухвходовых элементах ИСКЛЮЧАЮЩЕЕ-ИЛИ (сумматорах по модулю 2), умножители на постоянные коэффициенты могут быть реализованы на многовходовых элементах ИСКЛЮЧАЮЩЕЕ-ИЛИ, блоки нахождения обратного элемента могут быть реализованы табличным способом.

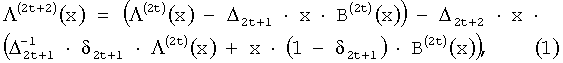

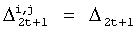

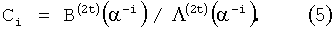

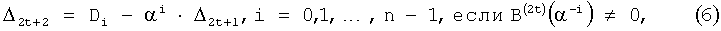

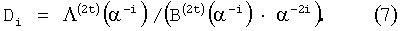

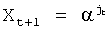

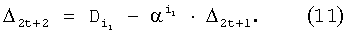

Процедура декодирования, выполняемая заявляемым устройством, обеспечивает исправление t+1 ошибки в кодовом PC-кода с минимальным кодовым расстоянием d=2t+1 путем аналитического продолжения алгоритма Берлекэмпа-Месси еще на две итерации. Это продолжение дает:

где δk=1, если Δk≠0 и 2Lk-1≤k-1, или δk=0 в противном случае. Lk - формальная степень многочлена локаторов ошибок Λ(k)(х), В(k)(х) - вспомогательный многочлен.

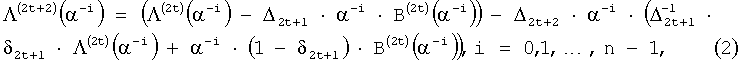

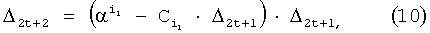

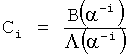

Каждой паре неизвестных невязок Δ2+t1 и Δ2t+2. соответствует многочлен Λ(2t+2)(х). По определению многочлен локаторов ошибок Λ(х) обращается в нуль, когда х принимает значения, обратные к локаторам ошибочных символов. Представляют интерес такие многочлены Λ(2t+2)(х), которые имеют степень t+1 и имеют точно t+1 корень в GF(q). Множество допустимых корней многочлена Λ(2t+2)(x) составляет {α0, α-1, α-2, …, α-(n-2), α-(n-1)} (α - примитивный элемент поля GF(q)). Подставляя это множество в уравнение (1), можно получить следующее:

где Λ(2t)(α-i) и В(2t)(α-i) - компоненты дискретного преобразования Фурье многочленов Λ(2t)(х) и В(2t)(х).

В случае наличия в кодовом слове конфигурации ошибок веса t+1 ровно t+1 правых частей уравнений системы (2) для некоторого значения пары невязок Δ2t+1 и Δ2t+2 обращаются в 0. Для определения позиций этих ошибочных символов необходимо найти соответствующую пару невязок и зафиксировать номера i уравнений системы (2) с правыми частями, обратившимися в нуль.

Приравняв левые части уравнений системы (2) нулю, можно получить следующую систему уравнений от двух неизвестных Δ2t+1 и Δ2t+2:

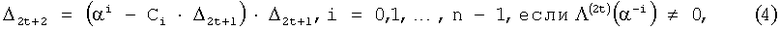

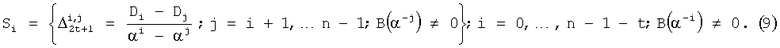

Подмножества из ровно t+1 совместных уравнений системы (3) будут соответствовать искомым комбинациям ошибок веса t+1, значения номеров уравнений i дадут позиции ошибок в кодовом слове.

Эти подмножества могут быть найдены следующим образом [3, 4]. Фиксируется одно из уравнений системы (3) (обозначим его номер i). К нему присоединяется одно из оставшихся уравнений (пусть его номер будет j). Для этих двух уравнений с двумя неизвестными находится возможное значение невязки  . Затем к первому уравнению последовательно присоединяются другие оставшиеся уравнения. Для всех таких пар уравнений также вычисляются возможные значения невязки

. Затем к первому уравнению последовательно присоединяются другие оставшиеся уравнения. Для всех таких пар уравнений также вычисляются возможные значения невязки  . Если среди всех полученных значений невязки есть t одинаковых, равных Δ2t+1, это говорит о том, что зафиксированное уравнение с номером i входит в искомое подмножество уравнений (и определяет позицию первой ошибки). Значения j, соответствующие условию

. Если среди всех полученных значений невязки есть t одинаковых, равных Δ2t+1, это говорит о том, что зафиксированное уравнение с номером i входит в искомое подмножество уравнений (и определяет позицию первой ошибки). Значения j, соответствующие условию  , дадут позиции еще t ошибок. В процессе поиска перебираются все возможные значения i.

, дадут позиции еще t ошибок. В процессе поиска перебираются все возможные значения i.

Формальное описание процедуры декодирования основывается на нижеприведенных Теореме, Следствии и Утверждении [3, 4], приведенных ниже без доказательств.

Теорема: Пусть Λ(2t)(х), В(2t)(х) и L2t получены после 2t итераций алгоритма Берлекэмпа-Месси. Если L2t<t или L2t>t+1, то тогда в принятом слове не может быть t+1 ошибок.

Если L2t=t, то тогда неизвестные невязки, соответствующие t+1 ошибкам, могут быть найдены из следующей системы уравнений:

где

Если L2t=t+1, то тогда невязки могут быть найдены из системы:

где

Следствие: Если L2t=t, то последовательности значений Δ2t+1, полученные для всех пар i и j уравнений системы (4), будут иметь следующий вид:

Если L2t=t+1, то последовательности значений Δ2t+1, полученные из системы (6), будут иметь следующий вид:

Обозначим через Cnt(S) оператор подсчета различных значений элементов последовательности S в поле GF(q). Этот оператор формирует вектор W размерности q: i-ая компонента вектора (i=0 …, q-2) соответствует элементу поля αi∈GF(q), последняя компонента (i=q-1) соответствует нулевому элементу поля GF(q). Тогда справедливо следующее утверждение.

Утверждение: Пусть Δ - множество значений Δ2t+1 такое, что полином Λ(2t+2)(x) имеет точно t+1 допустимых корней в поле GF(q). Пусть Wi=Cnt(Si); i=0, …, n-1-t; Р(α-i)≠0. Тогда множество Δ состоит из всех значений αi, удовлетворяющих условию wi,j=t для всех i=0, …, n-1-t, Р(α-i)≠0 и l=0, …, q-2.

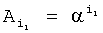

Значение i для найденной невязки Δ2t+1 дает позицию (i1=i) первой ошибки. Значения j, удовлетворяющие условию  дают позиции (j1, j2, …, jt) остальных ошибок. Тогда локатор первой ошибки будет

дают позиции (j1, j2, …, jt) остальных ошибок. Тогда локатор первой ошибки будет  , и локаторы остальных ошибок будут

, и локаторы остальных ошибок будут  ,

,  …,

…,  .

.

После нахождения невязки Δ2t+1 невязку Δ2t+2 можно легко вычислить, используя (4)

или (6)

Отличительной чертой процедуры декодирования, используемой в заявляемом устройстве, является управление процессом поиска позиций t+1 ошибки информацией о надежности символов. Процедура декодирования состоит из следующих этапов:

1) Вычисление полинома синдромов S(x).

2) Получение полинома локаторов Λ(2t)(х), вспомогательного полинома В(2t)(х) и формальной степени полинома локаторов L2t с использованием алгоритма Берлекэмпа-Месси.

3) Вычисление преобразования Фурье полиномов Λ(2t)(x) и В(2t)(х), когда L2t=t или L2t=t+1.

4а) Вычисление коэффициентов Ci=В(2t)(α-i)/Λ(2t)(α-i), когда L2t=t, или Di=Λ(2t)(α-i)/(В(2t)(α-i)·α-2i), когда L2t=t+1.

4b) Вычисление последовательностей Si возможных значений  невязки Δ2t+1 для каждого значения i∈{0,…,n-1-t} (j=i+1,…,n-1), подсчет значений Wi для каждой последовательности и фиксация значения Δ2t+1, которое встречается точно t раз в какой-то из этих последовательностей (wi,l=t), где

невязки Δ2t+1 для каждого значения i∈{0,…,n-1-t} (j=i+1,…,n-1), подсчет значений Wi для каждой последовательности и фиксация значения Δ2t+1, которое встречается точно t раз в какой-то из этих последовательностей (wi,l=t), где

когда L2t=t, или

когда L2t=t+1 (L - массив номеров позиций символов принятого кодового слова, упорядоченных (может быть частично) по возрастанию надежности символов, nc≤n-1-t).

4с) Повторное вычисление последовательностей Si для найденного значения i и фиксация позиций ошибок в моменты времени равенства невязки Δ2t+1 значениям  .

.

5) Получение полинома Λ(2t+2)(x), вычисление значений ошибок и их исправление.

При такой организации перебора (12, 13) неизвестная невязка  находится при малых значениях i.

находится при малых значениях i.

Предлагаемая процедура декодирования одновременно с повышением быстродействия позволяет решить задачу выбора наиболее вероятного вектора ошибок из списка. В большинстве случаев невязка  , соответствующая этому вектору находится первой.

, соответствующая этому вектору находится первой.

Заявляемое устройство декодирования PC-кодов содержит: буферную память данных 100, блок вычисления синдромов 200, процессор Галуа 300, блок дискретного преобразования Фурье 400, блок поиска позиций ошибок веса t+1 500, блок сортировки позиций символов 600, блок вычисления значений ошибок 700, первый сумматор элементов поля Галуа 800.

Устройство обрабатывает входные данные, представляющие собой последовательность n m-разрядных символов кодового слова {ri}, принятого из канала, которые сопровождаются значениями их надежности {reli}. При этом оно выполняет описанную выше процедуру декодирования. На выход устройства выдается последовательность n m-разрядных символов кодового слова с исправленными ошибками {ci}.

Буферная память данных 100 (фиг.1) предназначена для временного хранения принятых из канала символов исправляемых кодовых слов. Может быть реализована известным образом на основе двухпортовой RAM.

Блок вычисления синдромов 200 выполняет 1-й этап процедуры декодирования, заключающийся в вычислении многочлена синдрома S(x) принятого кодового слова, может быть реализован известным образом по схеме Горнера [4, 5].

Блок сортировки позиций символов 600 осуществляет сортировку позиций символов принимаемого из канала кодового слова в соответствии с их надежностью, формируя тем самым таблицу перестановок L.

Процессор Галуа 300 - специализированный процессор, выполняющий операции в конечном поле Галуа, может быть реализован известным образом на основе RISC-архитектуры.

Процессор Галуа 300 реализует алгоритм Берлекэмпа-Месси [4, 5], вычисляя в соответствии с ним многочлены Λ(2t)(x) и В(2t)(х) за 2t итераций (2-ой этап процедуры декодирования).

Кроме того, на основе информации, полученной от блока поиска позиций ошибок веса t+1 500 (i1∈{РЕ}, Δ ( или Δ=Δ2t+1),

или Δ=Δ2t+1),

или

или  он вычисляет значение Δ2t+2 по формуле (10) или (11) и затем Λ(2t+2)(x) (выполнив еще две итерации алгоритма Берлекэмпа-Месси с невязками Δ2t+1 и Δ2t+2). Используя многочлены Λ(х)=Λ(2t+2)(х) и S(x), процессор Галуа 300 вычисляет многочлен значений ошибок Ω(х)=Λ(x)·S(x)modxd-1 и формальную производную Λ'(х) многочлена локаторов Λ(х) с последующей загрузкой полученных многочленов вместе с найденными позициями ошибок {РЕ} в блок вычисления значений ошибок 700. Таким образом, выполняется начало 5-го этапа процедуры декодирования.

он вычисляет значение Δ2t+2 по формуле (10) или (11) и затем Λ(2t+2)(x) (выполнив еще две итерации алгоритма Берлекэмпа-Месси с невязками Δ2t+1 и Δ2t+2). Используя многочлены Λ(х)=Λ(2t+2)(х) и S(x), процессор Галуа 300 вычисляет многочлен значений ошибок Ω(х)=Λ(x)·S(x)modxd-1 и формальную производную Λ'(х) многочлена локаторов Λ(х) с последующей загрузкой полученных многочленов вместе с найденными позициями ошибок {РЕ} в блок вычисления значений ошибок 700. Таким образом, выполняется начало 5-го этапа процедуры декодирования.

Кроме этого, процессор Галуа 300 управляет БДПФ 400 и БППО 500 (с использованием сигналов управления Control). Процессор Галуа устанавливает режим работы БДПФ 400, он же загружает в него коэффициенты многочленов Λ(2t)(x) и В(2t)(х). Процессор Галуа контролирует состояние БДПФ (сигналы состояния State) и выгружает из него значения позиций ошибок веса меньшего или равного t. Также процессор Галуа контролирует состояние БППО (сигналы состояния State) и выгружает из него значения позиций ошибок веса t+1 (пропуская их предварительно через таблицу перестановок L блока БСПС 600).

Блок ДПФ 400 вычисляет преобразование Фурье многочленов Λ(2t)(х) и В(2t)(х) (3-ий этап процедуры декодирования). Кроме того, в зависимости от режима работы он вычисляет коэффициенты Ci или Di, а также коэффициенты Ai=αi (этап 4а процедуры декодирования). Эти коэффициенты загружаются в память блока БППО 500, адресуемую с помощью таблицы перестановок L блока БСПС 600. Блок ДПФ также вычисляет величины, обратные к корням полинома Λ(2t)(х), и контролирует их число, если L2t≤t.

Блок поиска позиций ошибок веса t+1 500 в зависимости от режима работы анализирует систему (4) с коэффициентами Ci или систему (6) с коэффициентами Di. Он находит позиции ошибок веса t+1 и соответствующие им значения Δ,  ,

,  или

или  . Таким образом выполняются этапы 4b и 4с процедуры декодирования.

. Таким образом выполняются этапы 4b и 4с процедуры декодирования.

Блок вычисления значений ошибок 700, используя многочлены Ω(х) и Λ'(х), вычисляет значения ошибок в найденных позициях ошибок {РЕ}. Он может быть реализован известным образом с использованием формулы Форни [4, 5]. Значения ошибок суммируются с помощью сумматора 800 с соответствующими символами кодового слова, считываемого из буферной памяти данных. Тем самым исправляются ошибочные символы кодового слова. Таким образом выполняется основная часть 5-го этапа процедуры декодирования.

Представленный декодер работает по конвейерному принципу: все основные его модули работают параллельно, обрабатывая последовательно принятые из канала различные кодовые слова. Конвейерный принцип работы декодера иллюстрируется фиг.9.

Рассмотрим для примера обработку декодером k-го кодового слова, в котором произошло t+1 ошибок.

Сначала в 1-ом кадре (кадр соответствует времени поступления одного кодового слова) k-oe слово записывается в буфер данных 100 и одновременно в темпе поступления в декодер обрабатывается блоком вычисления синдромов 200 и блоком сортировки позиций символов 600.

Затем в первой половине 2-го кадра процессор Галуа 300 реализует алгоритм Берлекэмпа-Месси для вычисленного синдрома, анализирует L2t и в начале второй половины 2-го кадра загружает коэффициенты многочленов Λ(2t)(х) и В(2t)(х) в блок ДПФ 400 (Низкий уровень на строке "БДПФ" фиг.9).

В течение второй половины 2-го кадра и первой половины 3-го кадра блок ДПФ 400 выполняет преобразование Фурье многочленов Λ(2t)(x) и В(2t)(х) k-го кодового слова (высокий уровень на строке 'БДПФ'). Кроме того, в зависимости от режима работы он вычисляет коэффициенты Ci или Di и Ai, которые загружаются в память БППО, адресуемую с помощью таблицы перестановок L блока БСПС. Если L2t≤t блок ДПФ 400 также вычисляет величины, обратные к корням полинома Λ(2t)(х), и контролирует их число.