Изобретение относится к автомаике и вычислительной технике и моет найти применение в различных устройствсях в качестве базового узла при построении, например, электрических фильтров.

Целью изобретения является повышение точности интегратора.

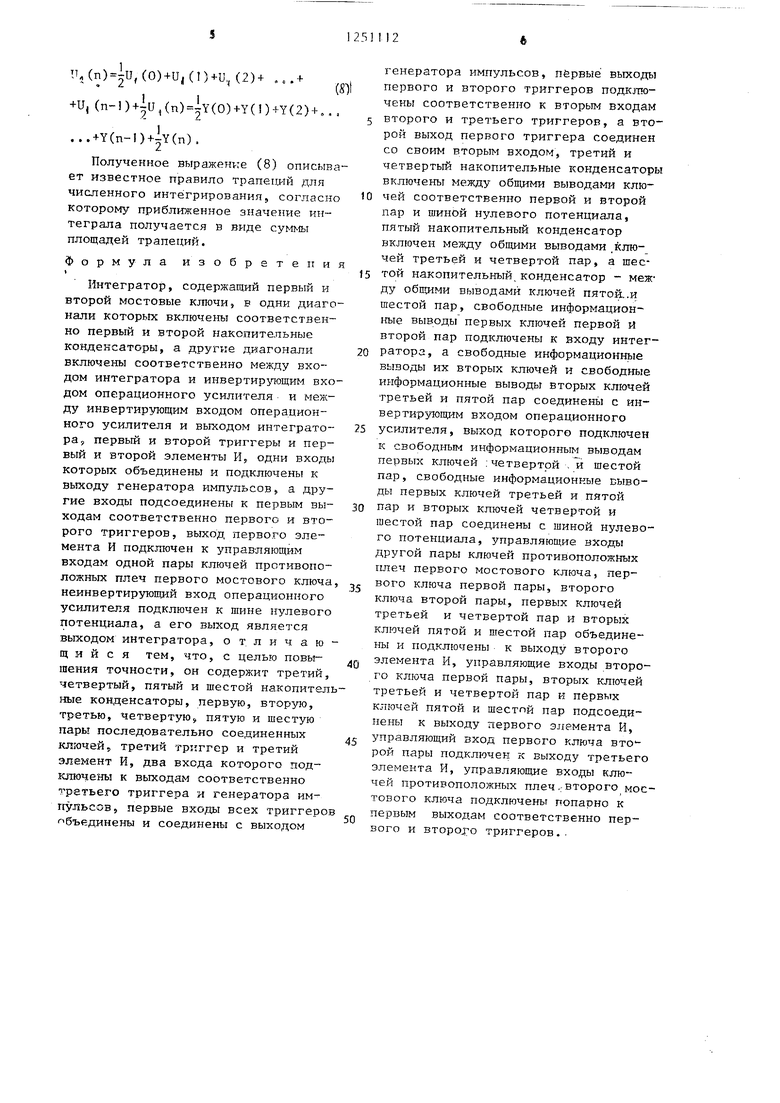

На чертеже приведена схема интегратора.

Интегратор содержит генератор 1 импульсов, первый мостовой ключ 2 с первым накопительным конденсатором 3 в диагонали и ключами 4 - 7 в плечах, операционный усилитель 8, ключи 9 - 12, входящие в состав второго мостового ключа 13 с вторым накопительным конденсатором 14 в диагонали, первую и вторую пары ключей 15 и 6, к общим вызодам которых подключены третий и четвертый накопительные конденсаторы соответственно 17 и 18, первые ключи 9 и 20 и вторые ключи 21 и 22 соответственно пар ключей 15 и 16, третью и четвертую пары ключей 23, пятую и шестую пары ключей 24, между общими выводами которых включены пятый и шестой накопительные конденсаторы соответственно 25 и 26, первые ключи 27,, 27 и 281, 28 и вторые ключи 29( , 29 и 30, 30 соответственно пар ключей 23 и 24; схему 31 управления интегратором с выходами 32 36, выполненной на первом, втором и третьем триггерах 37-39 и элементах И 40 - 42, соединенных по приведенной схеме; кроме того, интегратор имеет вход 43 и выход 44.

Интегратор работает следующим образом.

На вход 43 интегратора подается сигнал, подлежащий интегрированию. Схема 31 управления представляет собой регистр сдвига на тактируемых фронтом триггерах 37,38 и 39,, которые изменяют свое первоначальное состояние при изменении переднего фронта тактового импульса, поступающего на их первые входы, в соответствии с уровнем потенциала, находящимся на их вторых входах. Пусть все триггеры находятся в состоянии О, В момент времени первый импульс с выхода генератора 1 тактовых импульсов поступает на первые входы первого, второго и третьего триггеров 37 - 39. В это время сигнал I

10

15

20

25

30

35

40

45

50

122

со второго выхода ггервого триггера

37 поступает на его второй вход, в результате чего по переднему фронту первого тактового импульса триггер 37 переключается и на его первом выходе появляется высокий потенциал, который поступает на вход первого элемента И 40. При этом первый тактовый импульс с генератора 1 поступает на другой вход элемента И 40, на выходе которого формируется управляющий сигнал В результате длительность импульсов на выходе 32 схег-1ы 31 управления равна длительности тактовых импульсов с выхода генератора 1 импульсов, а длительность импульсов на выходе 35 равна периоду импульсов 1 генератора.

Таким образом, в момент t.0 импульс с выхода 32 схемы 31 управления поступает на ключи 4 и 7 мостового ключа 2, ключ 21 пары ключей 15, ключи 29(, 29 пар ключей 23 и ключи 28( , 28 пар ключей 24, В этот же момент времени () с выхода 35 схемы 3 управления подается сигнал на управляющие, входы ключей 9 и 12 мостового ключа 13, в результате чего последние открываются. При этом накопительный конденсатор 3 заряжается до входного напряжения (напряжения на входе 43 в момент времени ), т.е.

и (0) (,)

где и - напряжение; С - емкость; Q - заряд.

В тот же момент времени () накопительный конденсатор 14 и накопительный конденсатор 26 заряжаются до выходного напряжения (напряжения на выходе 44 интегратора). Поэтому для этого момента времени можно записать зарядное уравнение

C,U,(0)(0),,(0), (2) где и(0) - напряжение на входе

43;

UjCO) - напряжение на выходе интегратора.

30

Однако, в силу того, что ключи

j , 30/J пар ключей 24 в момент закрыты, заряд, образующийся на конденсаторе 26, запоминается и не оказывает влияния на выходной сигнал, В ургавнение (2) не входит член .., так как конденсатор I7 в зтот момент не заряжается (т.е..его заряд равен

3125

нулю). Таким образом, для момента остается справедливьм уравнение

С,и, (0)С,иг(0),

откуда напряжение на выходе 44 интегратора5

ило) 2-u,(o).

(3)

н

Полагая, что ,, получим

UJO) и((0)ф(0).

В следующий момент времени с приходом второго тактового импульса с выхода генератора 1 импульсов первый триггер 37 вновь переключается в состояние О, а второй триг- гер 38 переключается в .состояние 1, третий триггер 39 при этом остается в состоянии О. Сигнал 1 с выхода триггера 38, который одновременно является и пятым выходом 36 схемы 31 управления, поступает на вход элемента И 41, на другой вход которого поступает второй тактовый импульс с генератора 1 , в результа- те чего на выходе элемента И 41 присутствует импульс, который включает ключи 5 и 6 мостового ключа 2, ключ 19, ключ 22, ключи 27, , 27 и 30,, 30, а с выхода 36 подается сигнал, по длительности равный пери- оду следования тактовых импульсов с генератора 1, в результате чего включаются ключи 10 и 11 мостового ключа 13.

Накопительный конденсатор 3 пере- заряжается до нового напряжения, присутствующего на входе 43 интегратора в момент времени . Заряд на конденсаторе 3 в этот момент равенQc,(l)C3U(l).

В этот же момент времени происходит заряд третьего накопительного конденсатора 17 пары 15 до входного напряжения. При этом заряд конденсатора 17 равен

Qc,,(l)q7U«.(I).

. V Однако в силу того, что ключ 21 в момент закрыт, заряд, образу- ющийся на конденсаторе 17, запоминается и не оказывает влияния на выходное напряжение, как и заряд Qc2/l)

(1) , образовавшийся на конденсаторе 25. Поэтому для момента времени справедливо следующее зарядное уравнение:

Qcj(l)+Qc2e(0)QcK(). (4)

124

Знак + у слагаемого Qf,(0) обусловлен инвертирующими свойствами,пар ключей 24, В уравнение (4) не входит член QI;,,,, так как конденсатор 18 через вторую пару ключей 16 не заряжается, т.е. он пока не вступал в работу.

Из выражения (4) выходное напряжение на выходе 44 для этого момента времени составляет

С%

С26,

) и,(1)+ (0)., (5)

Ь, С,4

С учетом выражения (3) выражение (5

примет

г.. Г(6)

u,,(i)p-Ui(,(o)

L,|4 U,4 Ь,4

Считая, что 2С,.С,4 лучими,(1)ф,(о)+1иД1)у(о)+1у(1).

в следующий момент времени первый триггер 37 вновь оказывается в состоянии 1, второй триггер 38 в состоянии О, а третий триггер 39 переходит в состояние 1. Поскольку выход триггера 39 соединен с одним из входов третьего элемента И 42, на другой вход которого поступает тактовый импульс с выхода генератора 1 импульсов, на выходе элемента И 42 присутствует импульс. Таким образом, в момент времени управляющие импульсы присутствуют на первом 32, третьем 34 и четверто 35 выходах схемы 31 управления. Управляющие импульсы на выходах 32 и 35 схемы 31 управления включают все ключи, которые были включены в момент йремени . В этот же момент времени () импульсом с третьего выхода 34 схемы 31 управления вклю- . чается ключ 20 второй пары ключей 16 и конденсатор 1Й заряжается до значения Qc,g(2)C,gU, (2). С учетом зарядов Q(.(l) и Qc s - b запомненных в предыдущем интервале времени, зарядное уравнение примет вид

С5и,(2)+С„и,()+С,иг(1) С„и(2).(7)

Учитывая, что , окончательно с учетом (6) получим

U2(2)iu,(2)+lu, (, (1) +

,(о)1у(о)+у(1)+1у(2).

Далее процесс повторяется, поэ- тоьгу для п-го момента выходное напряжение составляет

(n)iu, (0)+U, (1)+U,,(2) +

(S)t

+U,(n-),(n)Y(0)+Y()4Y(2)+,.,

...+Y(n-l)(n).

Полученное выражение (8) описывает известное правило трапеций для численного интегрирования, согласно которому приближенное значение интеграла получается в виде площадей трапеций.

Формула изобретепи

1

Интегратор, содержащий первый и второй мостовые ключи, в одни диагонали которых включены соответственно первый и второй накопительные конденсаторы, а другие диагонали включены соответственно между входом интегратора и инвертир пощим входом операционного усилителя и между инвертирующим входом операционного усилителя и выходом интеграто- ра, первый и второй триггеры и первый и второй элементы И, одни входы которых объединены и подключены к выходу генератора импульсов а другие входы подсоединеньг к первым вы- ходам соответственно первого и второго триггеров, выход первого элемента И подключен к управляющим входам одной пары ключей противоположных плеч первого мостового ключа,

неинвертирующий вход операционного усилителя подключен к шине нулевого потенциала, а его выход является выходом интегратора, отличающийся тем, что, с целью повьг- шения точности, он содержит третий, четвертый, пятый и шестой накопительные конденсаторы, первую, вторую, третью, четвертую, пятую и шестую пары последовательно соединенных ключей, третий триггер и третий элемент И, два входа которого подключены к выходам соответственно третьего триггера и генератора им- ггульсов, первые входы всех триггеров

бъединены и соединены с выходом

О

5

0 5 о

5

..

генератора импульсов, первые выходы первого и второго триггеров подключены соответственно к вторым входам второго и третьего триггеров, а второй выход первого триггера соединен со своим вторым входом, третий и четвертый накопительные конденсаторы включены между обпуями выводами ключей соответственно первой и второй пар и шиной нулевого потенциала, пятый накопительный конденсатор включен между общими выводами .клю- чей третьей и четвертой пар, а шестой накопительный.конденсатор - между общими выводами ключей пятой:..и шестой пар, свободные информацион ные выводы первых ключей первой и второй пар подключены к входу интегратора, а свободные информационнь1е выводы их вторых ключей и свободные информационные выводы вторых ключей третьей и пятой пар соединены с инвертирующим входом операционного усилителя, выход которого подключен к свободным информационным выводам первых ключей :четвертой , и шестой пар, свободные информационные выводы первых ключей третьей и пятой пар и вторых ключей четвертой и шестой пар соединены с шиной нулевого потенциала, управляющие входы другой пары ключей противоположных плеч первого мостового ключа, первого ключа первой пары, второго ключа второй пары, первых ключей третьей и четвертой пар и вторых ключей пятой и шестой пар объединены и подключены к выходу второго элемента И, управляющие входы второго ключа первой пары, вторых ключей третьей и четвертой пар и первых ключей пятой и шестой пар подсоединены к выходу первого элемента И, управляющий вход первого ключа вто - рой пары подключен к выходу третьего элемента И, управляющие входы ключей противоположных плеч ,: второго мостового ключа подключены попарно к первым выходам соответственно первого и BTOpoj; o триггеров..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения приращений аналогового сигнала | 1985 |

|

SU1288722A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Интегратор | 1986 |

|

SU1376107A1 |

| Устройство для считывания информации из доменной памяти | 1988 |

|

SU1558226A1 |

| Компаратор напряжения | 1989 |

|

SU1653149A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1200421A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| КОРРЕКТОР КОЭФФИЦИЕНТА МОЩНОСТИ | 2011 |

|

RU2473109C1 |

| Интегрирующий преобразователь тока в код | 1989 |

|

SU1741264A1 |

Изобретение относится к области автоматики и вычислительной техники и может Найти применение в различных устройствах в качестве базового узла при построении, например, .электрических фильтров. Цель изобретения - повышение точности интегратора. Интегратор содержит.генератор импульсов, первый мостовой ключ с первым накопительным конденсатором в диагонали, операционный усилитель, второй мостовой ключ с вторым накопительным конденсатором в диагонали, первую и вторую пары ключей, к общим выводам которых подключены третий и четвертый накопительные конденсаторы, две пары-ключей, между общими выводами которых включены пятый и шестой накопительные конденсаторы, и схему управления, выполненную на трех триггерах и трех элементах И. Достижение поставленной цели обеспечено за счет схемной реализации алгоритма численного интегрирования по правилу трапеций путем введения в прототип дополнительных накопительных конденсаторов и спаренных ключей и благодаря особенностям связей между логическими элементами схемы управления и элементами схемы интегратора. 1 ил. Q 49

| Марше Ж | |||

| Операционные усилители и их применение | |||

| Энергия, 1974, с | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Решающий усилитель | 1983 |

|

SU1144122A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1985-02-12—Подача