114380022

Изобретение относится к электро-лов, Первые п и последние п циклов

измерительной технике и может бытьидентичны: в течение заданного иниспользовано для повышения быстродей-тервала времени Т, интегрируется

ствия прецизионных цифровых средств, опорное напряжение Е, далее значение

измерения.накопленного интеграла приводится к

Цель изобретения - повышение быст-нулю интегрированием образцового

родействия. .напряжения Uo. В основном (п+1)-м

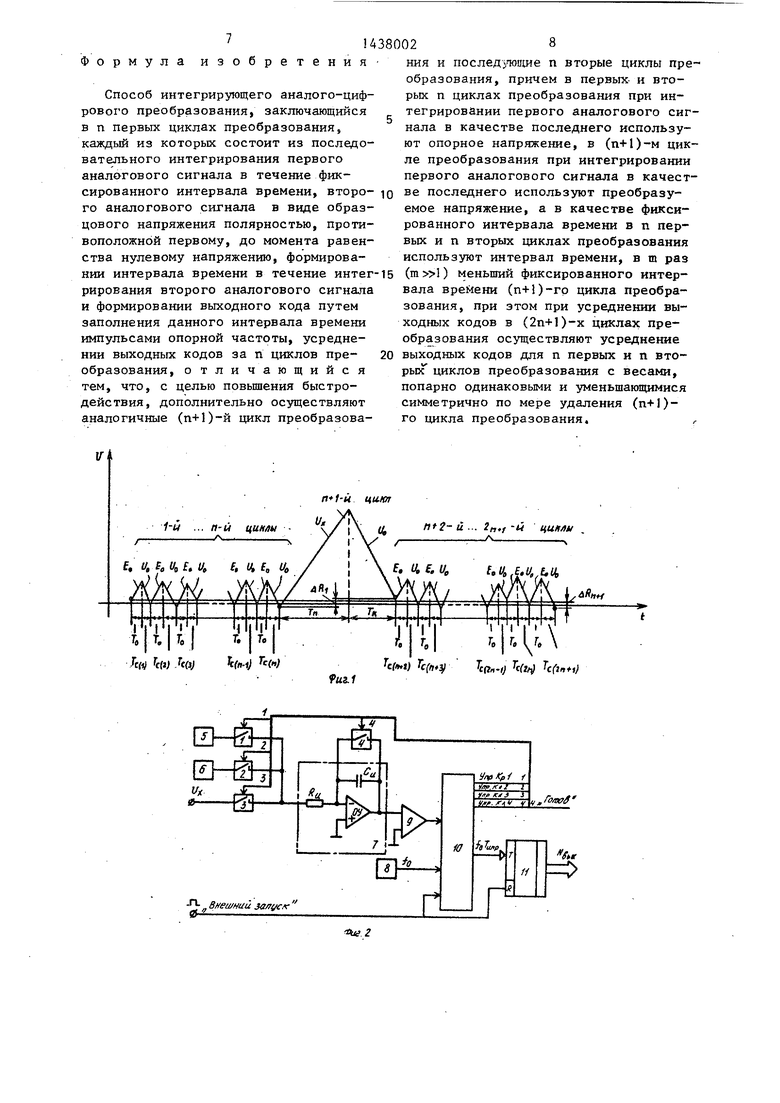

На фиг,1 представлена временнаяцикле в течение фиксированного интердиаграмма, поясняющая способ| вала времени Ту,тТд(т ) интегриру- фиг,2 - схема устройст ва для реали-ется преобразуемое напряжение Ujt, зации предлагаемого способа; надалее накопленный интеграл списыва- фиг.З - схема устройства управленияjется до нуля образцовым напряжением, на фиг.4 - временные диаграммы, поясняющие работу устройства управле-)5 Предполагая, что Ux const, для ния.рассматриваемого процесса преобразоПроцесс преобразования (фиг.1)вания согласно временной диаграмме

осуществляется непрерывно во време нмможно составить следующую систему

за 2п+1 (п. - целое) примыкающ.их цик-уравнений:

Л гр тт гр

% (п,),() &R,;

9 УхТпЕоТо Uo Xoinj (,iJ

. tлгТ- .™™™«..

(,,,,t, iR2;

3. .nta.l-IjCi i.LiIjS il iuiiL+Tc(

U Ск(143)- Un tv.iM,,, 6 R ;

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1314458A1 |

| Резонансный интегратор со сбросом | 1990 |

|

SU1774355A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012132C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Способ измерения частоты и устройство для его осуществления | 1986 |

|

SU1467519A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИЗМЕРИТЕЛЬНЫХ СИГНАЛОВ | 2009 |

|

RU2444125C2 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1728968A1 |

Изобретение относится к области электроизмерительной техники и может быть использовано для повьппения быстродействия прецизионных цифровых Средств измерения. Цель изобретения - повышение быстродействия аналого-цифрового преобразователя. Поставленная цель достигается тем, что согласно способу интегрирующего аналого-цифрового преобразования, заключающемуся в п первых циклах преобразования, каждый из которых состоит из последовательного интегрирования первого аналогового сигнала в течение фиксированного интервала времени, второго аналогового сигнала в виде образцового напряжения полярностью, противоположной первому, до момента равенства нулевому напряжению, формировании интервала времени в течение интегрирования второго аналогового сигнала и формировании выходного кода путем заполнения данного интервала времени импульсами опорной частоты, усреднении выходных кодов за п циклов преобразования, дополнительно осуществляют аналогичные (п+О-й цикл преобразования и последущие п вторые циклы преобразования . Причем в первых и вторых п циклах преобразования при интегрировании первого аналогового сигнала в качестве последнего используют опор- ное напряжение, а в (п+1)-м цикле пре-Ш образования при интегрировании первого аналогового сигнала в качестве последнего используют преобразуемое напряжение, а в качестве фиксированного интервала времени и в п первых и п вторых циклах преобразования используют интервал Времени, в m раз () меньший фиксированного интервала времени (п+1)-го цикла преобразования, при этом при усреднении выходных кодов в (2п+1)-х циклах преобразования осуществляют усреднение выходных кодов для п первЕзК и п вторых циклов Преобразования с весами, попарно одинаковыми и уменьшающимися симметрично по мере удаления относительно (п+1)-го цикла преобразования. 4 ил. 4;i САЭ 00 Ю

MiliL + 2(i-i) Ыз. y ll iu- L 2iibiiiiL j J.iiiiJ:T ia} i

.1:I: ±Tj L j.±.LLi±±iiTci i4.JiiL±Iiiiiill (..n -Unrt(,j..,J uR,-;

n. (п-1) S-gTo- yoj:T c,,.,.

-t6

± IiL41 ±iii±Tj,.ml+iii+T c la.i.;.0 +Tciln.Q,

Uy, t (гм -Un tn(z)l UR,;

ЕдТо Uo. +Te(a) +...+Tc(n +Tv + Т

i±iiIiLa iL ii.-Li±Ici.a rti +T u+it i „ r

n + i)

Ufl t i{lll ARn41 .

в данной системе TC(,, ...Тсщ) информативный временной интерTC(H+Z) (2M4i1 интервалы вре-вал; параметр i l ; n+lj соответстмени, в течение которых интегрирует-вует порядковому номеру уравнения. ся Ug, являются информативными; ин- Если разрешить каждое из уравнедексы 1...2П+1 указывают номер цикланий системы относительно информативпреобразования, в котором был полу-ных интервалов времени, то

-Ь 4-9 il - г .

+2 -у ц о ,

cCn -ri+Tcin (п+г) Тс()

Т На +4 . Uo Uo и„ -

(n-Ur) + эТ (t (;(

-Тс(„.ио (п..2(1-0 ;

о

cdi+Tc. +...(„ („ + 2)(аи4.,))

Т -1 +2 fn-1) ---- - --- С

% Uo и Uo

cCt Tc(ai +...+Тс(п5 +ТУ+ТС.(„ +. .. .+Т(,„ +

J.T Т Hi j.7r, uRtn-l /V

(„, Т„ у -Ь2п ц - -f-- .

Если сложить соответственно левые на п+1, то получим ,и правые части уравнений и разделить

(п1 - п+Т (п-. +Тс(„.,, + W Теи„) -|j Т,„ Те(,,,„

тт , ,, т 1 tcn-f( -

T..-i Z: 2(1-,, л, .

или

TX - nil 2- Тс(п.г-;)+Т,„,, i i

п« 1 р т 1 HL + 1 V 7Ci-n а-2- 5 ЛЯ -- .

Uo %+1 2(1 1) , &R, у

Заполнив информативные интервалы функцию преобразования способа времени опорной частотой f , получим . и-и р

Z;(n+2-i) N,.,,+N,,,,.

Tlir1 IT т

5: S;T Z - SIT г, -1.

где N,(,Nj. - результаты преобразованияпримыкающих интервалов времени, то

в код временных интерва- с целью исключения накопления погрешлов Т, Тр соответствен-ности квантования необходимо синхроно.низировать опорной частотой fg моменТак как промежуточные результатыты времени, в которые происходит

преобразования получены в виде не-отключение образцового напряжения U.

о

К

раз

Предлагаемьй способ в сравнении с известным способом позволяет при одинаковом уменьшении случайной погрешности увеличить быстродействие в

S-Isiii

m+2n где п - целое; m 1,

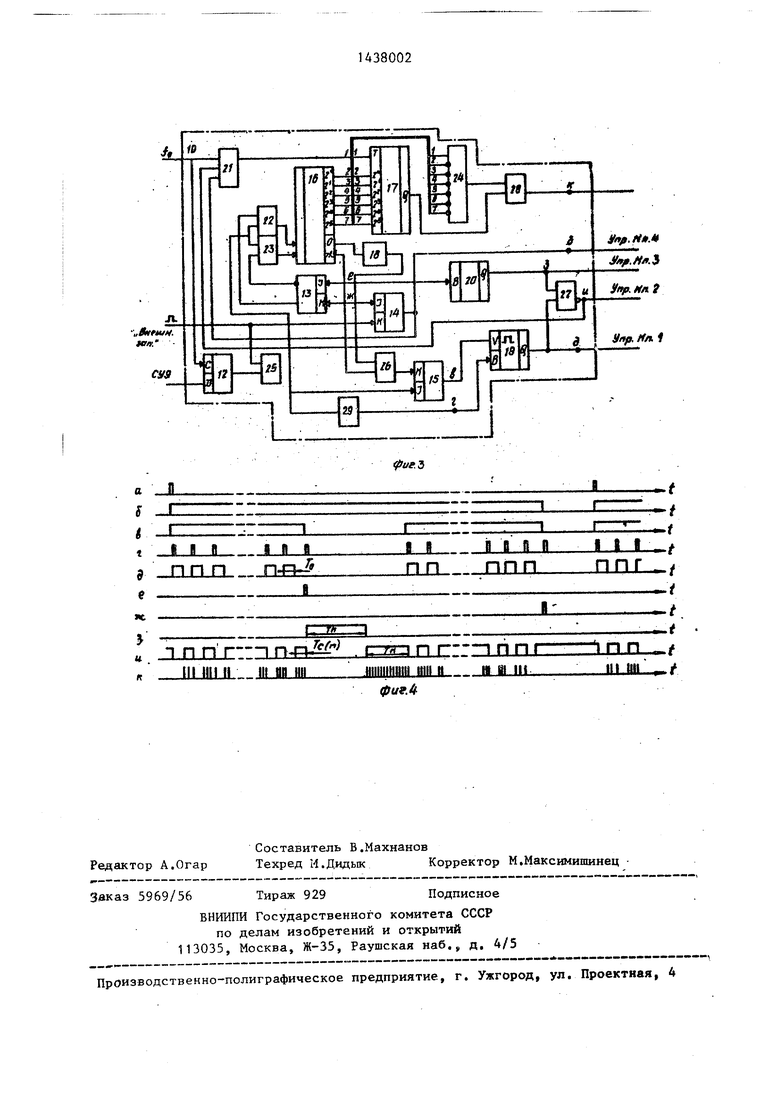

На фиг.2 показана схема устройства для осу1дествления предлагаемого способа. Устройство содержит ключи 1-4, источник 5 опорного напряжения, источ:ник 6 образцового напряжения, интегратор 7, генератор 8 опорной частоты, сравнивающее устройство 9, устройство 10 управления и счетчик 11 импульсов,

Временные диаграммы, представленные на фиг.1, полностью отражают процесс изменения напряжения на выходе интегратора 7, Сигналы Е, U и U подключаются к входу интегратора 7 первым, вторым и третьим ключами 1 - 3 соответственно. Четвертый.ключ 4 осуществляет сброс интегратора 7 по завершении полного цикла преобразования и поддержание нулевого потенциала на его выходе до прихода импульса Внешний запуск. Сравнивающе устройство 9 вьщеляет моменты равенства нулю значения накопленного интеграла. Устройство 10 управления управляет работой ключей I - 4, а также осуществляет заполнение информативных интервалов времени Т„.. опории р

ной частотой f с последующим умножением полученных результатов на соответствующие весовые коэффициенты q. Счетчик 11 импульсов преобразует информативные импульсные последовательности в выходной код.

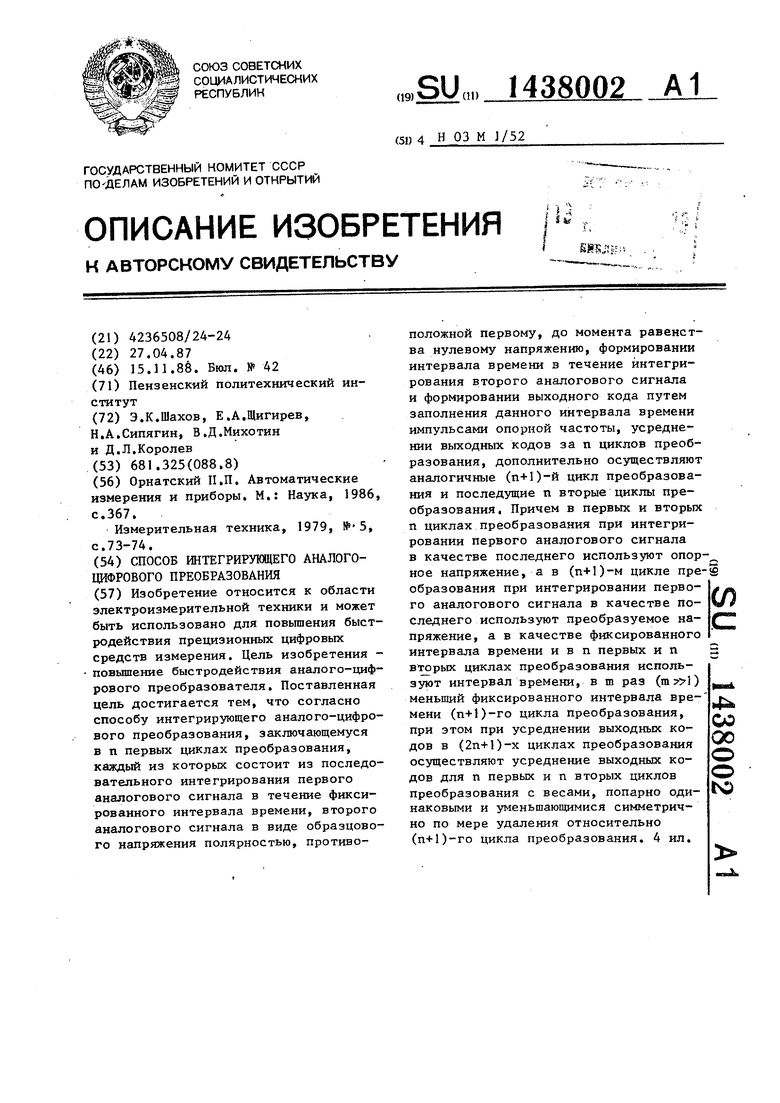

Функциональная схема устройства 10 управления приведена на фиг,3,

Устройство 10 управления содержит D-триггер 12, JK-триггеры 13 - 15, реверсивный двоичный счетчик 16 импульсов, делитель 17 частоты с переменным коэффициентом деления, делитель 18 частоты на два, одновибрато- ры 19 и 20, элементы И 21 - 24, элементы ИЛИ 25 - 27, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 28 и элемент 29 эадерж си.

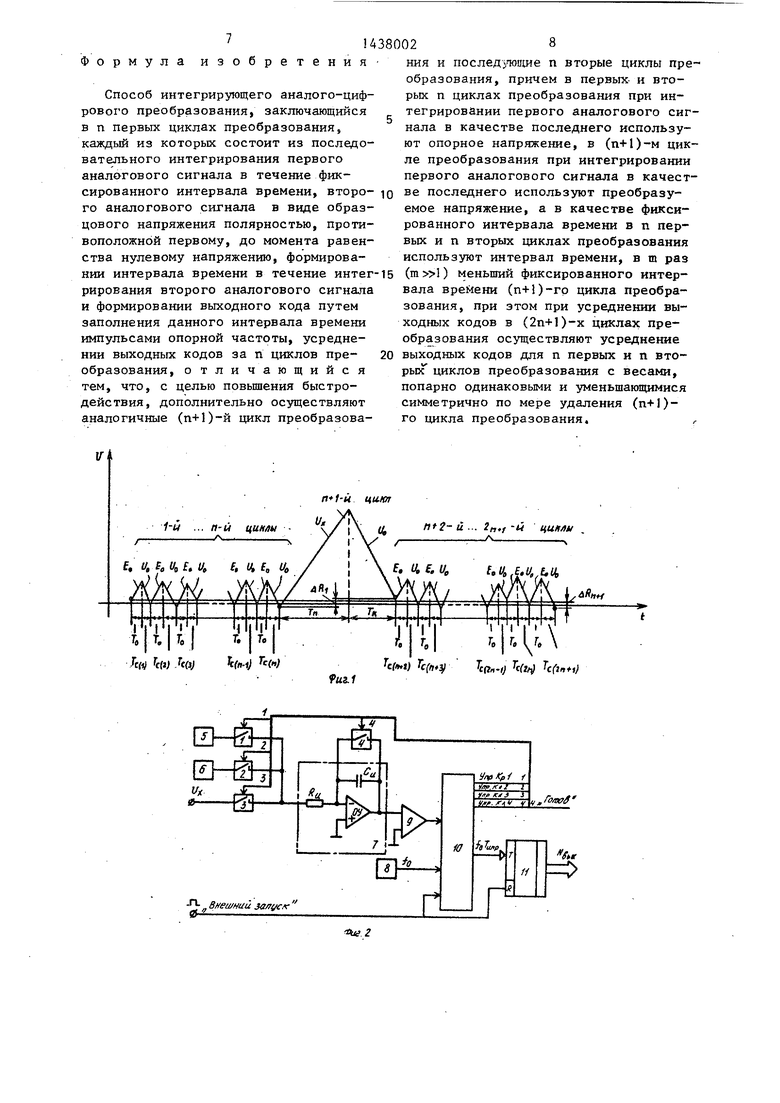

Временные диаграммы, поясняющие i работу схему, приведены на фиг.4.

Первый заданный интервал времени Те формируется на выходе одновибра- тора 19 по сигналу Внешний запуск, последующие 2п-1 заданных временных интервалов - по сигналу срабатьшания

сравнивающего устройства 9. Управление разрешением приема информации на вход. Запуск одновибратора 19 осуществляется с выхода JK-триггера 15. Элемент 29 задержки введен для устранения логических состязаний между сигналами, поступающими на вход резрешения и вход Запуск одновибратора 19,

Фиксированный интервал времени Т формируется на выходе одновибратора 20 по переднему фронту импульса с выхода Перенос реверсивного, двоичного счетчика 16 импульсов. Управление режимом работы счетчика 16 осуществляется с помощью JK-триггера 13 и элементов И 22 к 23, Первые п циклов преобразования счетчик 16 работает в режиме сложения, последние п+1 циклов - в режиме вычитания, Двоич- ньй код с выхода этого счетчика служит для задания коэффициента деления (т,е, весового коэффициента q) делителя 17 частоты в соответствии с номером цикла преобразования. Делитель 18 частоты ,на два предназначен для игнорирования импульса, неизбежно появляющегося на выходе Заем счетчика 16 по завершении основного п+1- го цикла преобразования.

Заполнение информативных интервалов времени опорной частотой ff, осуществляется с помощью элемента И 21,

Для квантования информативных интервалов времени импульсами опорной час тоты используется D-триггер 12,

Элемент И 24 позволяет получить в n+1-M цикле преобразования значение весового коэффициента q, равное единице,

На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 28 формируются пачки импульсов,-пред45 ставляющие собой умноженные на соответствующие весовые коэффициенты q результаты заполнения информативных интервалов времени Т„цо, опорной частотой fg. Далее количество этих

50 импульсов-фиксируется счетчиком П импульсов. Появление уровня логической единицы на выходе JK-триггера 14 сигнализирует о конце преобразования и разрешении считывания информа55 ции с выхода счетчика 11,

Начало нового преобразования возможно только по приходу импульса Внешний запуск.

Формула изобретения

ния и последутопдае п вторые циклы пре образования, причем в первых, и вторых п циклах преобразования при интегрировании первого аналогового сиг нала в качестве последнего используют опорное напряжение, в (п+1)-м цик ле преобразования при интегрировании первого аналогового сигнала в качест

Способ интегрирующего аналого-цифрового преобразования, заключающийся в п первых циклах преобразования, каждый из которых состоит из последовательного интегрирования первого аналогового сигнала в течение фиксированного интервала времени, второ- ю последнего используют преобразу- го аналогового сигнала в виде образ- емое напряжение, а в качестве фикси- цового напряжения полярностью, проти- рованного интервала времени в п пер- воположной первому, до момента равен- вых и п вторых циклах преобразования ства нулевому напряжению, формирова- используют интервал времени, в m раз НИИ интервала времени в течение интег-15 (т 1) меньший фиксированного интер- рирования второго аналогового сигнала вала времени ( цикла преобра- и формировании выходного кода путем зования, при зтом при усреднении выходных кодов в (2п+1)-х циклах преобразования осуществляют усреднение 20 выходных кодов для п первых и п вто- рызГ циклов преобразования с весами, попарно одинаковыми и уменьшающимися симметрично по мере удаления (п+1)- го цикла преобразования.

заполнения данного интервала времени импульсами опорной частоты, усреднении выходных кодов за п циклов преобразования, отличающийся тем, что, с целью повьш1ения быстродействия, дополнительно осуществляют аналогичные (п+1)-й цикл преобразова1-й ... п-и цинаы

f, и,,и,Е. и, е, ц , Uo

ния и последутопдае п вторые циклы преобразования, причем в первых, и вторых п циклах преобразования при интегрировании первого аналогового сигнала в качестве последнего используют опорное напряжение, в (п+1)-м цикле преобразования при интегрировании первого аналогового сигнала в качест последнего используют преобразу- емое напряжение, а в качестве фикси- рованного интервала времени в п пер- вых и п вторых циклах преобразования используют интервал времени, в m раз (т 1) меньший фиксированного интер- вала времени ( цикла преобра- зования, при зтом при усреднении выходных кодов в (2п+1)-х циклах преобразования осуществляют усреднение выходных кодов для п первых и п вто- рызГ циклов преобразования с весами, попарно одинаковыми и уменьшающимися симметрично по мере удаления (п+1)- го цикла преобразования.

nt2- и . 2n.f -н nun/lit

л.

f. Ч.и,f.i/, ,f/ bit

| Орнатский II ,П | |||

| Автоматические измерения и приборы | |||

| М.: Наука, 1986, с.367 | |||

| Измерительная техника, 1979, №-5, с.73-74. |

Авторы

Даты

1988-11-15—Публикация

1987-04-27—Подача