Изобретение относится к электроизмерительной технике и может быть использовано для создания аналоге- цифровых преобразователер и вольтметров среднеквадратического (СКЗ), средневыпрямленного (СВЗ) и среднего (СЗ) значений напряжений произвольной формьи

Целью изобретения является повышение точности

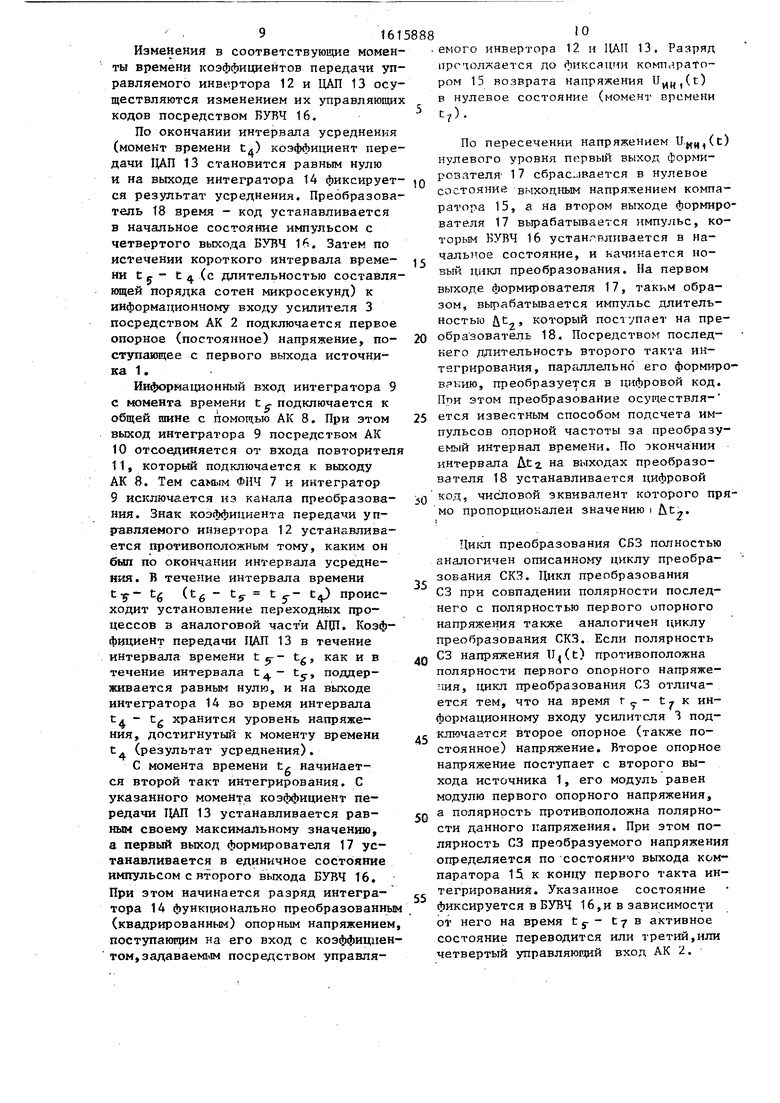

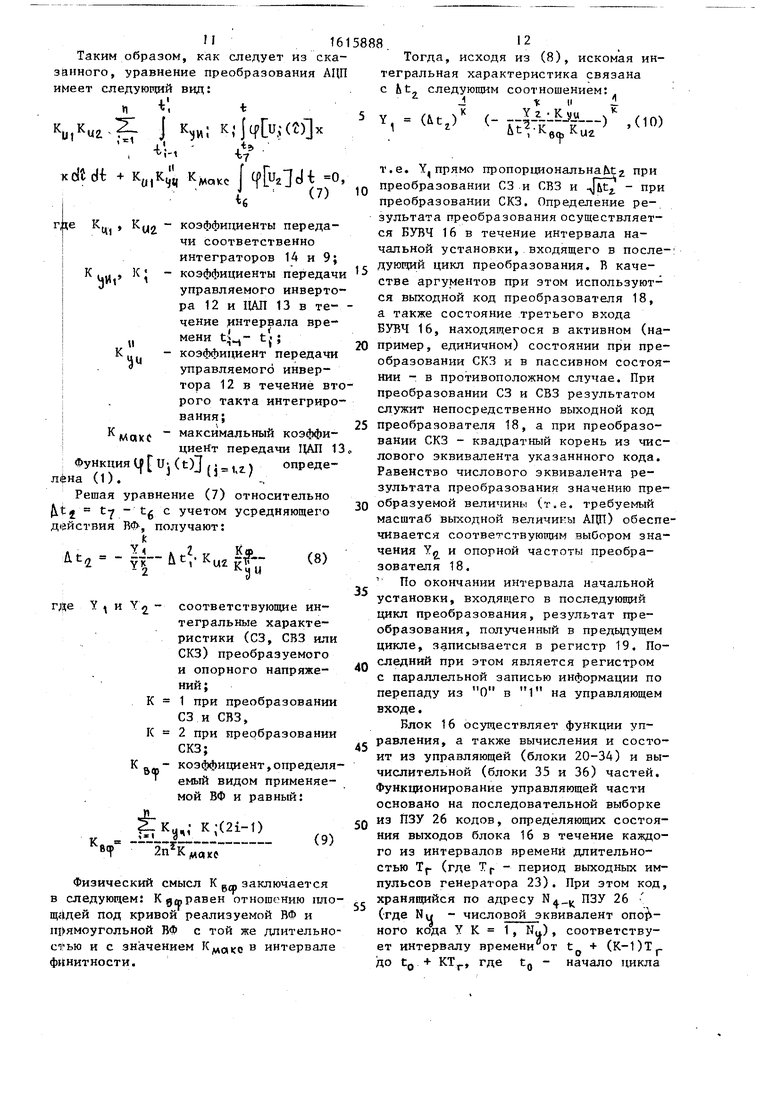

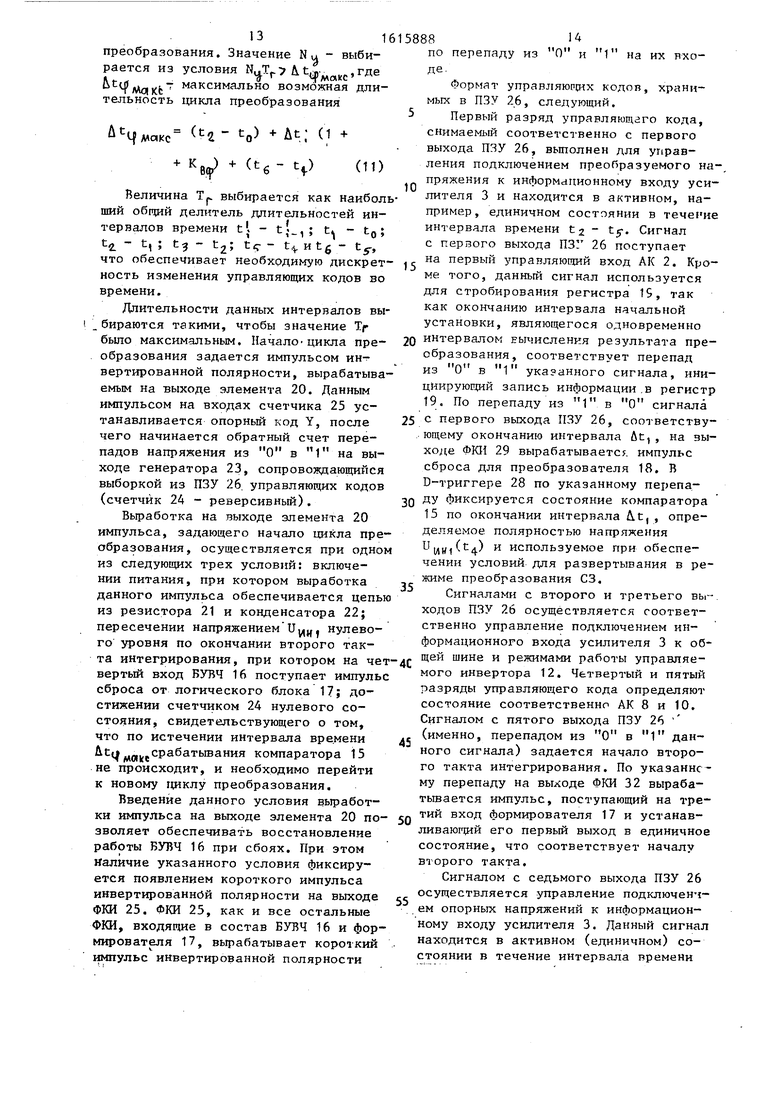

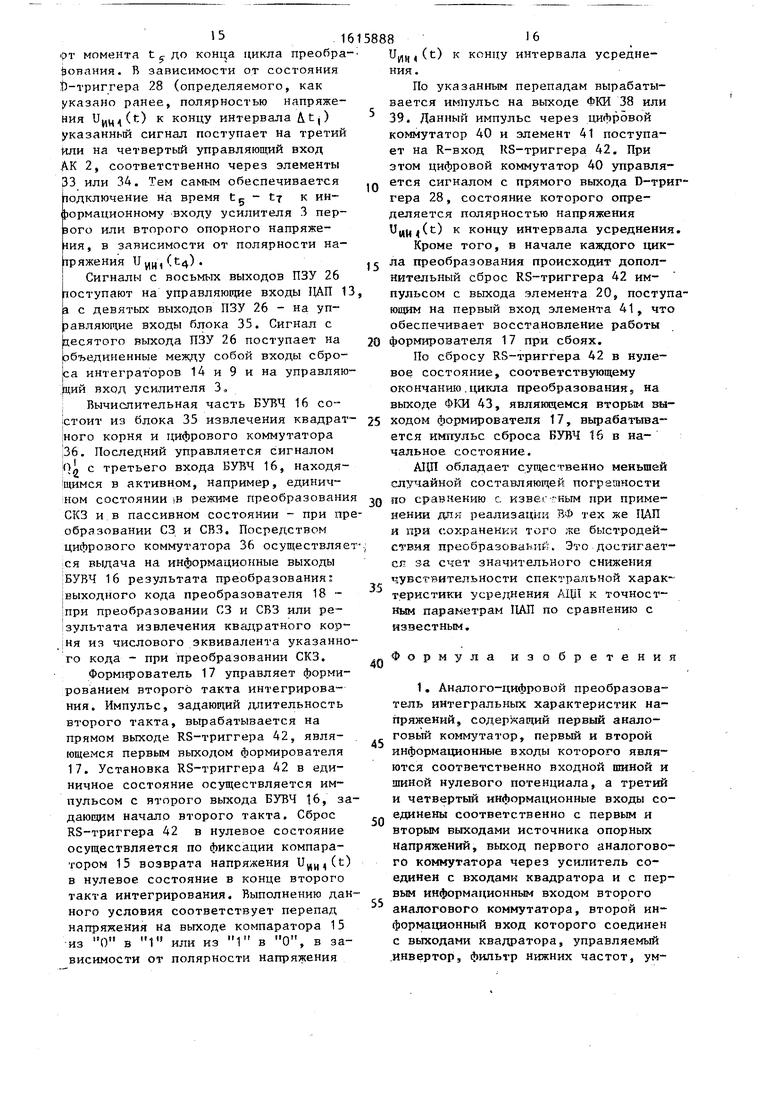

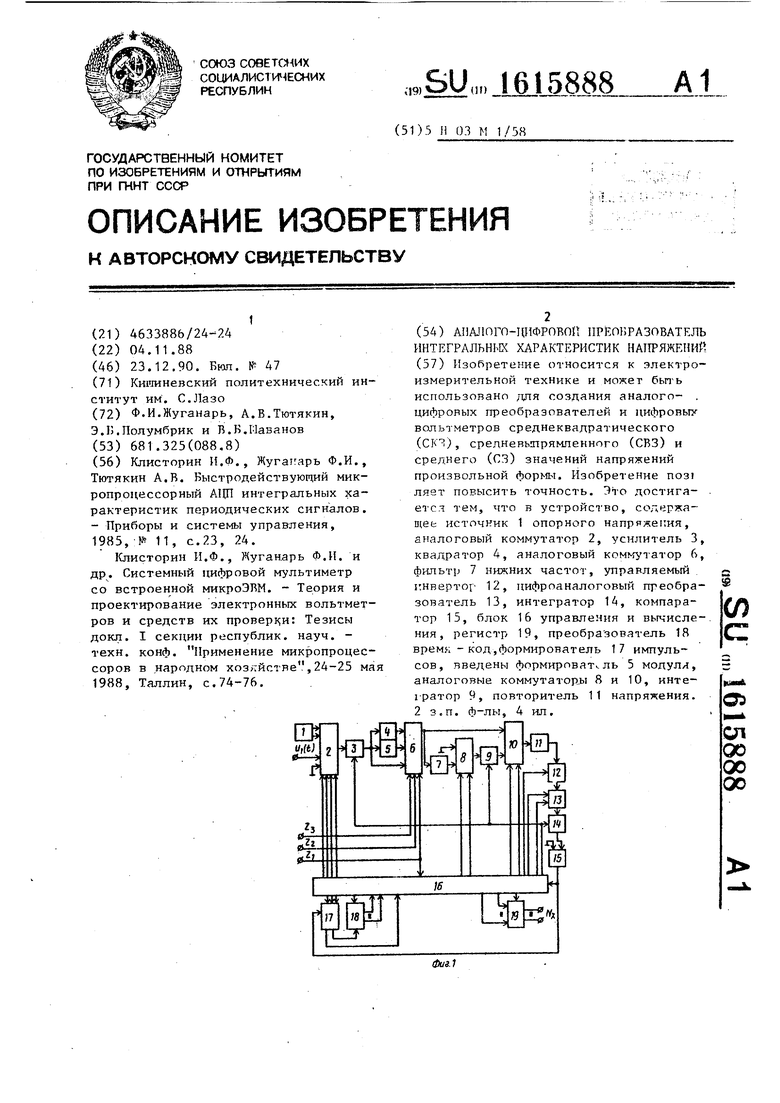

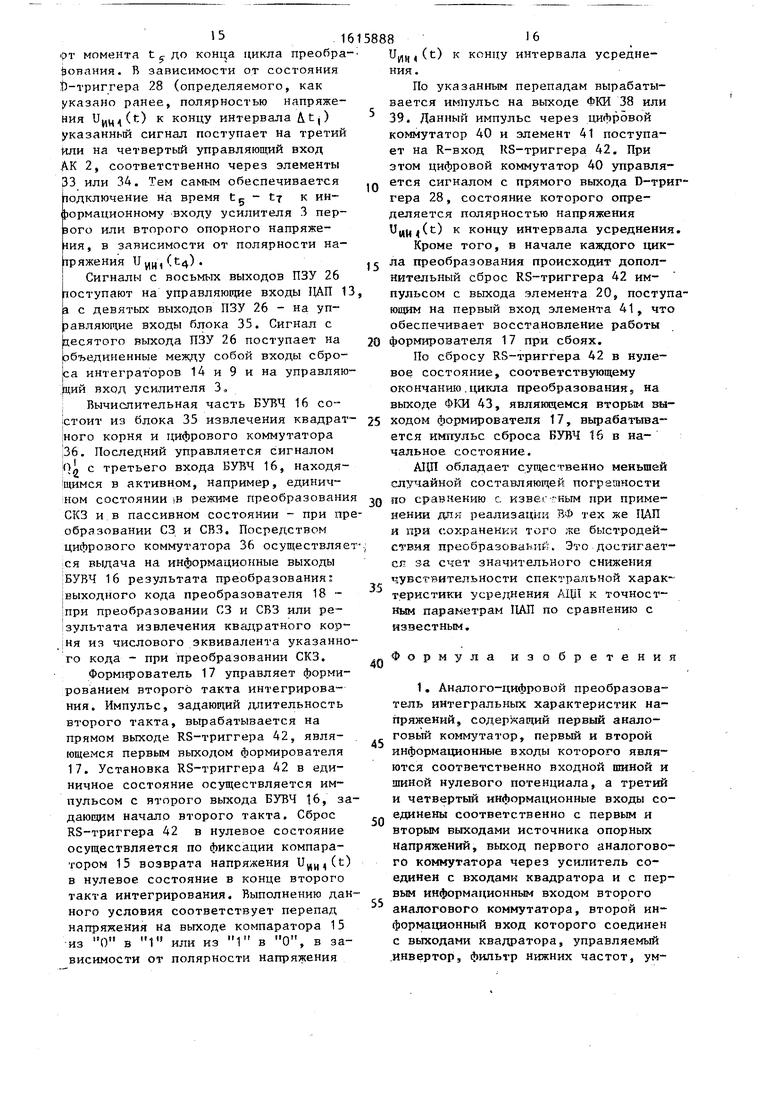

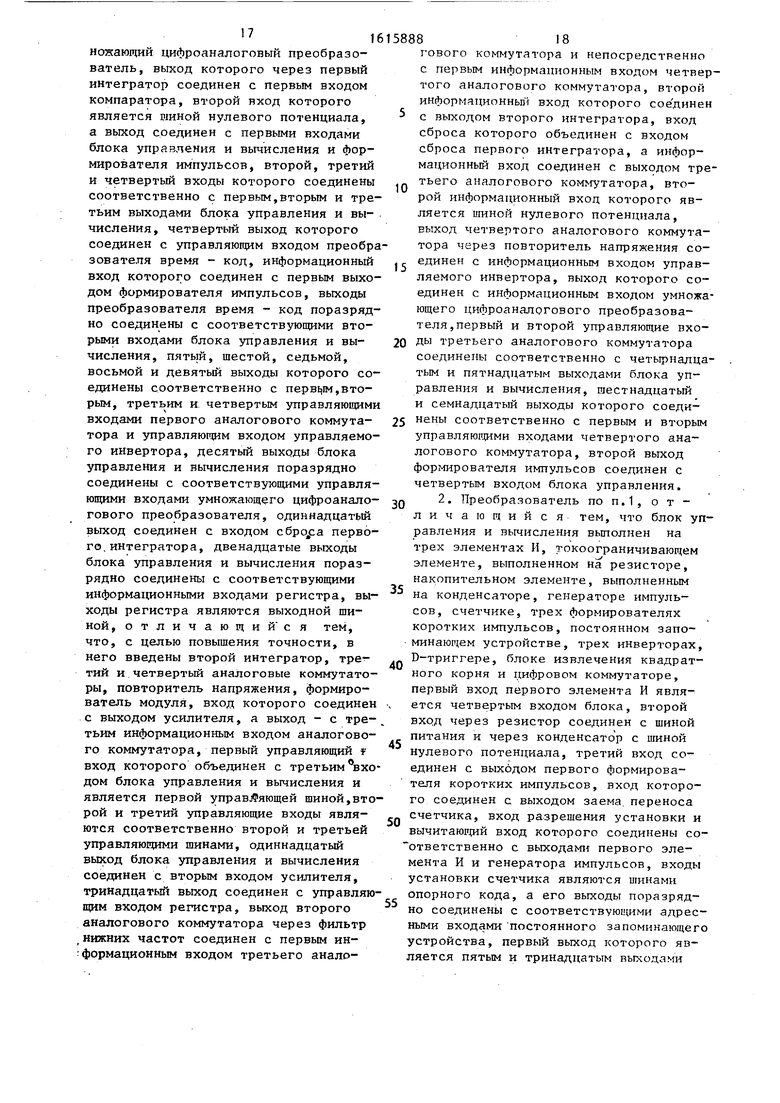

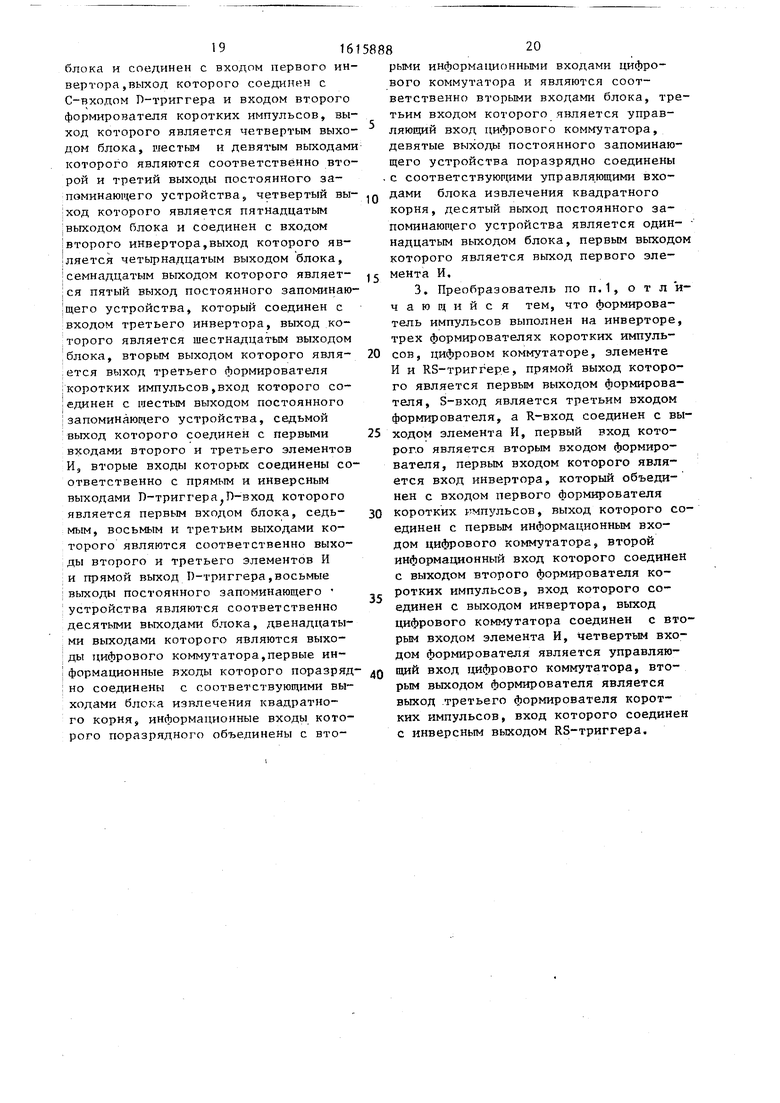

На фиг,1 Ьредставлена функциональ- 1ая схема преобразователя;на фиг.2 - |ункциональная схема блока управления я вычисления (БУВЧ); на, фиг.З функциональная схема формирователя им- Пульсов J на фиг в4 -- временные диаг- - 1раммы напряжений в преобразователе,, Например, при преобразовании СКЗ.

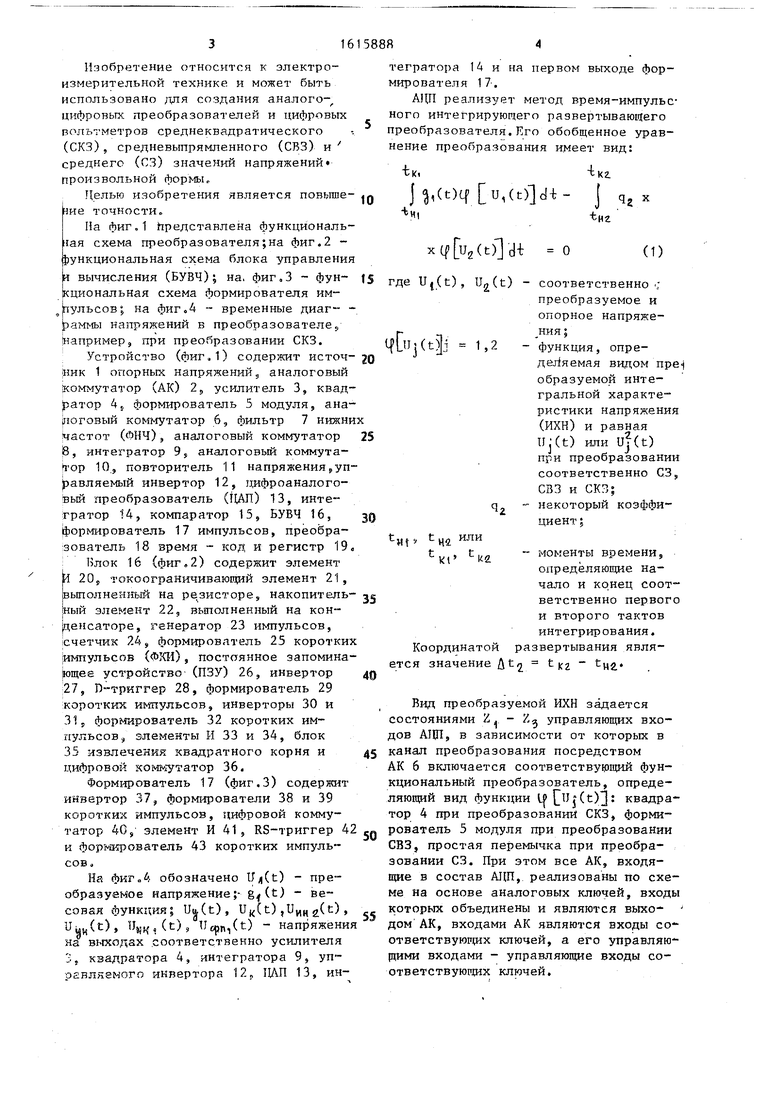

Устройство (фиг,1) содержит источ- |шк 1 ог орных напряжений, аналоговый коммутатор (АК) 2 усилитель 3, квадратор 4j формирователь 5 модуля, ана- ЬЮГОБЫЙ коммутатор 6, фильтр 7 нижни частот (ФНЧ), аналоговый коммутатор 8, интегратор 9, аналоговый коммута- fi op 10., повторитель 11 напряжения,уп- завляемый инвертор 12, цифроаналого- вьш преобразователь () 13, интегратор 14, компаратор 15, БУБЧ 16, формирователь 17 импульсов, преобразователь 18 время - код и регистр 19.

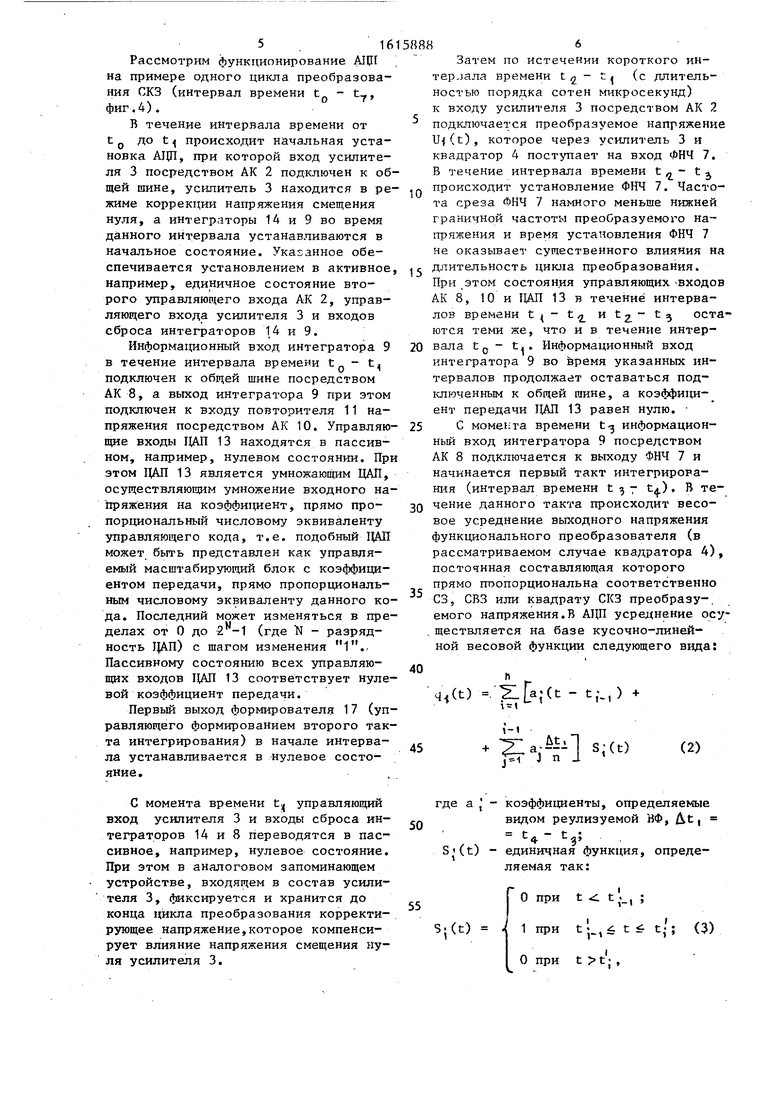

Блок 16 (фиг.2) содержит элемент И 205 токоограничивающий элемент 21 , вьтолненньй на ре зисторе, накопитель- |ный элемент 22, выполненный на кон- ценсаторе, генератор 23 импульсов, Ьчетчик 24, формирователь 25 коротких импульсов (ФХИ), постоянное запомина- щее устройство (ПЗУ) 26, инвертор ;27, П-триггер 28, формирователь 29 коротких импульсов, инверторы 30 и 31, формирователь 32 коротких импульсов, элементы И 33 и 34, блок 35 извлечения квадратного корня и цифровой коммутатор 36.

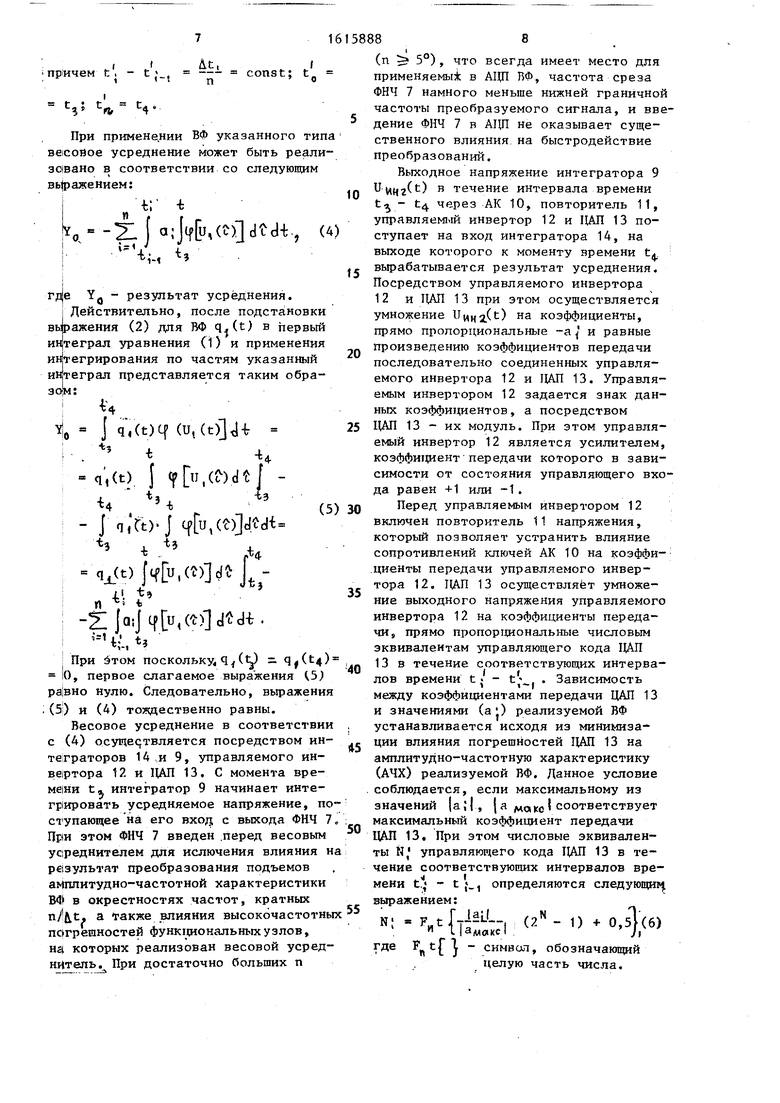

Формирователь 17 (фиг.З) содержит инвертор 37, формирователи 38 и 39 коротких импульсов, цифровой коммутатор 40, элемент И 41, RS-триггер 42 и формирователь 43 коротких импульсов.

На фиг,4 обозначено tl;)(t) - преобразуемое напряжение;- g| (t) - ве- -овал функция; Utt(t), U((t) ,UI,H t), cpn/t) - напряжения

и

на выходах .соответственно усилителя 3. квадратора 4, интегратора 9, уп огвляемого инвертора 12„ ПДП 13, ин

тегратора 14 и на первом выходе формирователя 17.

АЦП реализует метод время-импульсного интегрирующего развертывающего преобразователя.Его обобщенное уравнение преобразования имеет вид:

.

J,(t)q U,(t)di- j qg tHi

X

(t) di 0

(1)

где U((t), q(.t) - соответственно ,:

преобразуемое и опорное напряже- Г -1,

fUJj(t)|j 1,2 - функция, опреде11яемая видом пре образуемой интегральной характеристики напряжения (ИХН) и равная IJj(t) или Uj(t) при преобразовании соответственно СЗ, СВЗ и СКЗ;

q некоторый коэффициент ;

-Mt

tц или t,,

моменты времени, определяющие начало и ко,нец соот ветственно первого и второго тактов интегрирования.

Координатой развертывания является значение ДС2 Ьц.

Вид преобразуемой ИХН задается состояниями управляющих входов АЦП, в зависимости от которых в канал преобразования посредством АК 6 включается соответствующий функциональный преобразователь, определяющий вид функции U DjKt) квадратор 4 при преобразований СКЗ, формирователь 5 модуля при преобразовании СВЗ, простая перемычка при преобразовании СЗ, При этом все АК, входящие в состав А1Щ, реализованы по схеме на основе аналоговых ключей, входы которых объединены и являются выходом АК, входами АК являются входы со ответствуюрщх ключей, а его управляю- щими входами - управляющие входы соответствующих ключей.

Рассмотрим функционирование А1ЦГ на примере одного цикла преобразования СКЗ (интервал времени t - t, фиг.4).

В течение интервала времени от t р до t происходит начальная установка А1Щ, при которой вход усилителя 3 посредством АК 2 подключен к общей шине, усилитель 3 находится в режиме коррекции напряжения смещения нуля, а интеграторы 14 и 9 во время данного интервала устанавливаются в начальное состояние. Указанное обеспечивается установлением в активное например, единичное состояние второго управляюр1его входа АК 2, управляющего входа усилителя 3 и входов сброса интеграторов 14 и 9.

Информационный вход интегратора 9 в течение интервала времени t - t, подключен к общей шине посредством АК 8, а выход интегратора 9 при этом подключен к входу повторителя 11 напряжения посредством АК 10. Управляющие входы НАЛ 13 находятся в пассивном, например, нулевом состоянии. При этом ЦАП 13 является умножающим ЦАП, осуществляющим умножение входного напряжения на коэффициент, прямо пропорциональный числовому эквиваленту управляющего кода, т.е. подобныйЦАП может быть представлен как управляемый масштабирующий блок с коэффициентом передачи, прямо пропорциональным числовому эквиваленту данного кода. Последний может изменяться в пределах от О до 2-1 (где N - разрядность 1{АП) с шагом изменения 1,- Пассивному состоянию всех управляющих входов ЦАП 13 соответствует нулевой коэффициент передачи.

Первый выход формирователя 17 (управляющего формированием второго такта интегрирования) в начале интервала устанавливается в нулевое состояние ,

5

0

5

0

5

Затем по истечении короткого интервала времени t - t (с длительностью порядка сотен микросекунд) к входу усилителя 3 посредством АК 2 подключается преобразуемое напряжение Uj(t), которое через усилитель 3 и квадратор 4 поступает на вход ФНЧ 7. В течение интервала времени t /г. - 3 происходит установление ФНЧ 7. Частота среза ФНЧ 7 намного меньше нижней граничной частоты преобразуемого напряжения и время установления ФНЧ 7 не оказывает существенного влияния на длительность цикла преобразования. При этом состояния управляющих -входов АК 8, 10 и ЦАП 13 в течение интервалов времени t и t остаются теми же, что и в течение интервала tjj- t. . Информационный вход интегратора 9 во время указанных интервалов продолжает оставаться подключенным к общей шине, а коэффициент передачи ЦАП 13 равен нулю.

С момента времени t-j информацион- ньй вход интегратора 9 посредством АК 8 подключается к выходу ФНЧ 7 и начинается первый такт интегрирования (интервал времени t з 7 t). В течение данного такта происходит весовое усреднение выходного напряжения функционального преобразователя (в рассматриваемом случае квадратора 4), постоянная составляющая которого прямо поопорциональна соответственно СЗ, СВЗ или квадрату СКЗ преобразу-. емого напряжения.В АЦП усреднение осу- , ществляется на базе кусочно-линейной весовой функции следующего В1ада:

п q;(t) . ,(t - t,-,) н |; г г ; «

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ преобразования скоростей вращения двух валов для измерения соотношения скоростей и устройство для его осуществления | 1989 |

|

SU1636774A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478332A1 |

| Блок управления нагревателями аппаратуры космического аппарата | 2017 |

|

RU2660098C1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1314458A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1280698A1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1594695A1 |

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

Изобретение относится к электроизмерительной технике и может быть использовано для создания аналого-цифровых преобразователей и цифровых вольтметров среднеквадратического (СКЗ), средневыпрямленного (СВЗ) и среднего (СЗ) значений напряжений произвольной формы. Изобретение позволяет повысить точность. Это достигается тем, что в устройство, содержащее источник 1 опорного напряжения, аналоговый коммутатор 2, усилитель 3, квадратор 4, аналоговый коммутатор 6, фильтр 7 нижних частот, управляемый инвертор 12, цифроаналоговый преобразователь 13, интегратор 14, компаратор 15, блок 16 управления и вычисления, регистр 19, преобразователь 18 время-код, формирователь 17 импульсов, введены формирователь 5 модуля, аналоговые коммутаторы 8, 10, интегратор 9, повторитель 11 напряжения. 2 з.п. ф-лы, 4 ил.

с момента времени t управляющий вход усилителя 3 и входы сброса интеграторов 14 и 8 переводятся в пассивное, например, нулевое состояние. При этом в аналоговом запоминающем устройстве, входящем в состав усилителя 3, фиксируется и хранится до конца цикла преобразования корректирующее напряжение,которое компенсирует влияние напряжения смещения нуля усилителя 3.

t

где а j - коэффициенты, определяемые видом реулизуемой ВФ, At,

4-45

единичная функция, определяемая так:

S (t)

55

О при t -с. t

S;(t)

1 при t|, t tj О при t t - ,

(3)

г iit,/

причем t, - const; t

t.

4 4«

При применении ВФ указанного типа ве сойое усреднение может быть реализовано в соответствии со следующим вы|раяением:

чг

, -Z. I a;K,(), )

Ч.. ь .

гр,

le YQ - результат усреднения.

Действительно, после подстановки вь ражения (2) дпя ВФ q.(t) в первый иН|теграл уравнения (1) и применения ин1тегрирования по частям указанный интеграл представляется таким обра Ч

0 J qi(t)cf (u,(t)j

16158888

(n 5°), что всегда имеет место для применяемы в А1Щ ВФ, частота среза

ФНЧ 7 намного меньше нижней граничной частоты преобразуемого сигнала, и вве дение ФНЧ 7 в АЦП не оказывает существенного влияния на быстродействие преобразований.

Выходное напряжение интегратора 9

10 Миг течение интервала времени t - t. через АК 10, повторитель 11, управляем1л1й инвертор 12 и ЦАП 13 поступает на вход интегратора 14, на выходе которого к моменту времени t

.f вырабатывается результат усреднения. Посредством управляемого инвертора 12 и 11АП 13 при этом осуществляется умножение ) на коэффициенты, прямо пропорциональные -а и равные

20

произведению коэффициентов передачи

последовательно соединенных управляемого инвертора 12 и ЦАП 13. Управляемым инвертором 12 задается знак данных коэффициентов, а посредством

25 ЦАП 13 - их модуль. При этом управля- е1Ф1й инвертор 12 является усилителем, коэффи щент передачи которого в зависимости от состояния управляющего входа равен +1 или -1.

(,t) j ,()dtf

4

I lirt)- ,(e)d.di

ta , t

(5)

-21 . 4л

: При Й1ТОМ поскольку, q (О - Ч|(Ь4) К), первое слагаемое выражения 5) pajBHo нулю. Следовательно, выражения : (5) И (4) тождественно равны.

Весовое усреднение в соответствии с (4) осуществляется посредством ин- те граторов 14,и 9, управляемого ин- BeipTOpa 12 и ЦАП 13. С момента вре- ме|ни t. интегратор 9 начинает инте- гр1ировать усредняемое напряжение, поступающее на его вход с выхода ФНЧ 7, При этом ФНЧ 7 введен .перед весовым усреднителем для ислючения влияния на результат преобразования подъемов амплитудно-частотной характеристики ВФ в окрестностях частот, кратных , а также влияния высокочастотных погрешностей функциональных узлов, Hst которых реализован весовой усреднитель. При достаточно больших n

произведению коэффициентов передачи

последовательно соединенных управляемого инвертора 12 и ЦАП 13. Управляемым инвертором 12 задается знак данных коэффициентов, а посредством

ЦАП 13 - их модуль. При этом управля- е1Ф1й инвертор 12 является усилителем, коэффи щент передачи которого в зависимости от состояния управляющего входа равен +1 или -1.

Перед управляемым инвертором 12 включен повторитель 11 напряжения, который позволяет устранить влияние сопротивлений ключей АК 10 на коэффи-- .циенты передачи управляемого инвертора 12, ЦАП 13 осуществляет умножение выходного напряжения управляемого инвертора 12 на коэффициенты передачи, прямо пропоргдаональные числовым эквивалентам управляющего кода ПАП

13 в течение соответствующих интервалов времени tj - t - . Зависимость между коэффициентами передачи 13 и значениями (ai) реализуемой ВФ

устанавливается исходя из минииизации влияния погрещностей ЦАП 13 на амплитудно-частотную характеристику (АЧХ) реализуемой ВФ. Данное условие соблюдается, если максимальному из значений |а, |, |а акс °°тветствует максимальный коэффициент передачи

ЦАП 13, При этом числовые эквиваленты N, управляющего кода ЦАП 13 в течение соответствующих интервалов времени t.; - t f-1 определяются следующиг выражением:

N; - F tr-r Si- --, ( 1) ч- 0,5Т(6) L |аддо1кс1Jf

где Р t - символ, обозначающий . целую часть числа.

Изменения в соответствующие моменты времени коэффициентов передачи управляемого инвертора 12 и ЦАП 13 осуществляются изменением их управляющих кодов посредством БУВЧ 16,

По окончании интервала усреднения (момент времени t) коэффициент передачи ЦАП 13 становится равным нулю И на выходе интегратора 14 фиксируется результат усреднения. Преобразователь 18 время - код устанавливается в начальное состояние импульсом с четвертого выхода БУВЧ 1 fi. Затем по истечении короткого интервала времени t у - t (с длительностью составляющей порядка сотен микросекунд) к информационному входу усилителя 3 посредством АК 2 подключается первое опорное (постоянное) напряжение, по- стзтающее с первого выхода источника 1 .

Информационный вход интегратора 9 с момента времени t подключается к общей шине с помощью АК 8. При этом выход интегратора 9 посредством АК 10 отсоединяется от входа повторителя 11, которЕлй подключается к выходу АК 8. Тем ФНЧ 7 и интегратор 9 исключается из канапа преобразования. Знак коэффициента передачи управляемого инвертора 12 устанавливается противоположным тому, каким он бып по окончании интервшта усреднения. В течение интервала времени

Ч (Чt.r

t г- происходит установление переходных процессов в аналоговой части А1Щ. Коэффициент передачи ЦАП 13 в течение интервала времени tg, как и в течение интервала ty, поддерживается равным нулю, и на выходе интегратора 14 во время интервала

tg хранится уровень напряжеЧния, достигнутый к моменту времени t (результат усреднения).

С момента времени t, начинается второй такт интегрирования. С указанного момента коэффициент передачи ЦАП 13 устанавливается равным своему максимальному значению, а первый выход формирователя 17 устанавливается в единичное состояние импульсом с второго выхода БУВЧ 16. При этом начинается разряд интегратора 14 функционально преобразованным (квадрированным) опорным напряжением, поступающим на его вход с коэффициентом, задаваемым посредством управля

5

0

5

0

-емого инвертора 12 н ЦАП 13. Разряд прстолжается до фиксации KOMnapato- ром 15 возврата напряжения Uj,(t) в нулевое состояние (момент времени t,).

По пересечении напряжением U.jf(c) нулевого уровня первый выход формирователя 17 сбрас- 1вается в нулевое состояние выходным напряжением компаратора 15, а на втором выходе формирователя 17 вырабатывается импульс, которым НУВЧ 16 устанавливается в начальное состояние, и начинается новый цикл преобразования. На первом выходе формирователя 17, таким образом, вьфабатьшается импульс длительностью ut, который поступает на пре- обра зователь 18. Посредством последнего длительность второго такта интегрирования, параллельно его формированию, преобразуется в цифровой код. При этом преобразование осуществля- ется известным способом подсчета импульсов опорной частоты за преобразуемый интервал времени. По окончании интервала At г на выходах преобразователя 18 устанавливается цифровой код, числовой эквивалент которого прямо пропорционален значению ut.

5

Цикл преобразования СБЗ полностью аналогичен onHcaHHOhry циклу преобразования СКЗ. Цикл преобразования СЗ при совпадении полярности последнего с полярностью первого опорного напряжения также аналогичен циклу преобразования СКЗ. Если полярность п СЗ напряжения U(t) противоположна полярности первого опорного напряже- :1ия, 1дакл преобразования СЗ отличается тем, что на время г - t к информационному входу усилителя 3 подключается второе опорное (также постоянное) напряжение. Второе опорное напряжение поступает с второго выхода источника 1, его модуль равен модулю первого опорного напряжения, а полярность противоположна полярности данного напряжения. При этом полярность СЗ преобразуемого напряжения определяется по состоянию выхода компаратора 15 к концу первого такта интегрирования. Указанное состояние фиксируется в БУВЧ 16,и в зависимости от него на время t j- - 17 в активное состояние переводится или третий,или четвертый управляющей вход АК 2.

0

5

уравнение преобразования АЦП дующий вид:

.V,

j К„

; i n

к к

и

K, j((t)x

J.

к

Макс I иЛ 6

0, (7) 10

де К

(А1

К

U2

К коэффициенты передачи соответственно интеграторов 14 и 9; коэффициенты передачи управляемого инвертора 12 и ПАП 13 в те- - чение интервала времени t:;

К

К

Макс

коэффициент передачи управляемого инвертора 12 в течение второго такта интегрирования;

максимальный коэффи- циейт передачи ЦАП 13 Функция(. (t),. ,-ч опредеыа (1). - И- -2 ;

Решая уравнение (7) относительно tj t-7 - tg с учетом усредняющего (гйствия ВФ, получают:

ч - uiKl i;

(8)

де Y , и Y К

К

t

соответствующие интегральные характеристики (СЗ, СВЗ или СКЗ) преобразуемого и опорного напряжений ;

1при преобразовании СЗ и СВЗ,

2при преобразовании СКЗ;

коэффициент,определяемый видом применяемой ВФ и равный:

К.

К,; K;(2i-1)

(9)

махе

Физический смысл К цд, заключается

стью Т(- (где Тр - период выходных импульсов генератора 23). При этом код, следующем: Кд равен отношению пло- , хранящийся по адресу , ПЗУ 26

кода Y

щадей под кривой реализуемой ВФ и щ ямоугольной ВФ с той же длительно(тде N, ного

- числовой эквивалент , 1Чи

К 1, NU), соответствусп ью и с значением фкнитности.

К

в интервале

ьная

следующим 1

(it,)

характеристика связана соотношением:

1C II 1

& иг

-) ,(10)

0

0

0

5

0

5

т.е. Y прямо пpoпopциoнaльнa t2 при преобразовании СЗ и СВЗ и -Jbt - при преобразовании СКЗ. Определение результата преобразования осуществляется БУВЧ 16 в течение интервала начальной установки, входящего в после-;

г дующий цикл преобразования. В качестве аргументов при этом используются выходной код преобразователя 18, а также состояние третьего входа БУВЧ 16, находящегося в активном (например, единичном) состоянии при преобразовании СКЗ и в пассивном состоянии - в противоположном случае. При преобразовании СЗ и СВЗ результатом служит непосредственно выходной код

5 преобразователя 18, а при преобразовании СКЗ - квадратный корень из числового эквивалента указаннного кода. Равенство числового эквивалента результата преобразования значению преобразуемой величины (т.е. требуемый масштаб выходной величины А1Щ) обеспечивается соответствующим выбором значения J. и опорной частоты преобразователя 18.

По окончании интервала начальной установки, входящего в последующий цикл преобразования, результат преобразования, полученный в предьщущем цикле, записывается в регистр 19. Последний при этом является регистром с параллельной записью информации по перепаду из О в 1 на управляющем входе.

Блок 16 осуществляет функции управления, а также вычисления и состоит из управляющей (блоки 20-34) и вычислительной (блоки 35 и 36) частей. Функционирование управляющей части основано на последовательной выборке

ft из ПЗУ 26 кодов, определяющих состояния выходов блока 16 в течение каждого из интервалов времени длительностью Т(- (где Тр - период выходных импульсов генератора 23). При этом код, хранящийся по адресу , ПЗУ 26

пульсов генератора 23). При этом код хранящийся по адресу , ПЗУ 26

кода Y

(тде N, ного

- числовой эквивалент , 1Чи

ет интервалу времени от

К 1, NU), соответствуtg + (К-1)Тр

до tf. + КТг, где t- - начало цикла

131

преобразования. Значение Nu - выбирается из условия ,j)( Ч мсюсЬ максимально возможная длительность цикла преобразования

,кс Ч- to) + At; (1 +

ъо Ч- Ч 0

Величина Т выбирается как наибол ший обпщй делитель лпительностей интервалов времени tl - t .; ti - tf,;

Ч - t, ; t - tc - t, Htg - t., что обеспечивает необходимую дискретность изменения управляющих кодов во времени.

Длительности данных интервалов вы бираются такими, чтобы значение Тг бьшо максимальным. Начало-цикла преобразования задается импульсом ин- вертированной полярности, вырабатываемым на выходе элемента 20. Данным импульсом на входах счетчика 25 устанавливается опорный код Y, после чего начинается обратный счет перепадов напряжения из О в 1 на выходе генератора 23, сопровождающийся выборкой из ПЗУ 26. управляющих кодов (счетчик 24 - реверсивный).

Выработка на выходе элемента 20 импульса, задающего начало цикла преобразования, осуществляется при одном из следующих трех условий: включении питания, при котором выработка данного импульса обеспечивается цепью из резистора 21 и конденсатора 22; пересечении напряжением Uy,jj. нулевого уровня по окончании второго такта интегрирования, при котором на чет вертый вход БУВЧ 16 поступает импульс сброса от логического блока 17; достижении счетчиком 24 нулевого состояния, свидетельствующего о том, что по истечении интервала времени йС(| д1 срабатьтания компаратора 15 не происходит, и необходимо перейти к новому циклу преобразования.

Введение данного условия выработки импульса на выходе элемента 20 позволяет обеспечивать восстановление работы ВУВЧ 16 при сбоях. При этом Наличие указанного условия фиксируется появлением короткого импульса инвертированной полярности на выходе ФКИ 25. ФКИ 25, как и все остальные ФКИ, входящие в состав ВУВЧ 16 и формирователя 17, вырабатывает короткий импульс инвертированной полярности

15

588814

по перепаду из О и 1 на их яхо- де,

Формят управляюп(их кодов, хранимых в ПЗУ 26, следующий.

Первый разряд управляющгго кода, снимаемый соответственно с первого выхода ПЯУ 26, выполнен для управления подключением преобразуемого на- пряжения к информационному входу усилителя 3 и находится в активном, например, единичном состоянии в течение интервала времени tj - tj-. Сигнал с первого выхода ИЗ 26 поступает на первый з правляющий вход АК 2. Кроме того, данный сигнал используется для стробирования регистра 1S, так как окончанию интервала начальной установки, являющегося одновременно

20 интервалом вычисления результата преобразования, соответствует перепад из О в 1 указанного сигнала, ини- цйируюсдай запись информации ,в регистр 19. По перепаду из 1 в О сигнала

25 с первого выхода ПЗУ 26, соответствующему окончанию интервала ut,, на выходе ФКИ 29 вырабатываете;, импульс сброса для преобразователя 18. В D-триггере 28 по указанному перепа30 ДУ фиксируется состояние компаратора 15 по окончании интернала At,, определяемое полярностью напряжения

и

МИ1

(t) и используемое при обеспе35

4С

45

чении условий для развертывания в режиме преобразования СЗ.

Сигналами с второго и третьего выходов ПЗУ 26 осуществляется соответственно управление подключением информационного входа усилителя 3 к общей шине и режимами работы управляемого инвертора 12. Четвертый и пятый разряды управляюрдего кода определяют состояние соответственно АК 8 и 10. Сигналом с пятого выхода ПЗУ 26 (именно, перепадом из О в 1 дан50

ного сигнала) задается начало второго такта интегрирования. По указанному перепаду на выходе ФКИ 32 выраба- тьшается импульс, поступающий на третий вход формирователя 17 и устанав- ливаюг-щй его первый выход в единичное состояние, что соответствует началу второго такта.

Сигналом с седьмого выхода ПЗУ 26 осуществляется управление подключен- - .ем опорных напряжений к информационному входу усилителя 3. Данный сигнал находится в активном (единичном) состоянии в течение интервала времени

516

от момента t до конца цикла преобра оваиия. В зависимости от состояния л)-триггера 28 (определяемого, как указано ранее, полярностью напряжения и,ц(г.) к концу интервала itj) указанный сигнал поступает на третий Мли на четвертый управляющий вход АК 2, соответственно через элементы 33 или 34. Тем самым обеспечивается юдключение на время tg - t/ к информационному входу усилителя 3 первого или второго опорного напряжения, в зависимости от полярности напряжения , (4).

Сигналы с восьмых выходов ПЗУ 26 поступают на управляющие входы 11ДП 13 а с девятых выходов ПЗУ 26 - на управляющие входы блока 35. Сигнал с |цесятого выхода ПЗУ 26 поступает на Объединенные между собой входы сбро- ta интеграторов 14 и 9 и на управляю- |щий вход усилителя 3, : Вычислительная часть БУВЧ 16 со-- Ьтоит из блока 35 извлечения квадрат- JHoro корня и цифрового коммутатора |36. Последний управляется сигналом ioi с третьего входа ВУВЧ 16, находя- Зщимся в активном, например, единич- ном состоянии iB режиме преобразования СКЗ и в пассивном состоянии - при преобразовании СЗ и СВЗ. Посредством цифрового коммутатора 36 осуществляе ;ся выдача на информационные выходы ;БУВЧ 16 результата преобразования: выходного кода преобразователя 18 - |при преобразовании СЗ и СВЗ или ре- 1зультата извлечения квадратного кор™ Ня из числового эквивалента указанно го кода - при преобразовании СКЗ.

Формирователь 17 управляет формированием второго такта интегрирования. Импульс, задающий длительность второго такта, вырабатывается на прямом выходе RS-триггера 42, являющемся первым выходом формирователя 17. Установка RS-триггера 42 в единичное состояние осуществляется импульсом с второго выхода БУВЧ 16, задающим начало второго такта. Сброс RS-триггера 42 в нулевое состояние осуществляется по фиксации компаратором 15 возврата напряжения (t) в нулевое состояние в конце второго такта интегрирования. Выполнению данного условия соответствует перепад напряжения ка выходе компаратора 15 из О в 1 или из 1 в О, в зависимости от полярности напряжения

j,(t) к концу интервала усредне88816

и,

ния.

По указанным перепадам вырабатывается импульс на выходе ФКИ 38 или 39. Данный импульс через цифровой коммутатор 40 и элемент 41 поступает на R-вход RS-триггера 42. При этом цифровой коммутатор 40 управля- Q ется сигналом с прямого выхода В-триг- гера 28, состояние которого определяется полярностью напряжения (t) к концу интервала усреднения.

Кроме того, в начале каждого цик- C ла преобразования происходит дополнительный сброс RS-триггера 42 импульсом с выхода элемента 20, поступающим на первый вход элемента 41, что обеспечивает восстановление работы 0 формирователя 17 при сбоях.

По сбросу RS-триггера 42 в нулевое состояние, соответствующему окончанию.цикла преобразования, на выходе 43, являнядемся вторым вы- 5 ходом формирователя 17, вырабатьгеа- ется импульс сброса ВУВЧ 1 б в начальное состояние.

А1Щ обладает существенно меньшей сп /чайной составляющей погрешности 0 о сравнению с извесгным при применении для реализации ВФ тех же ЦАП и при сохраненкк того же быстродей- c-S BHH преобразований. Это достигается за счет значительного снижения чувствительности спектральной характеристики усреднения АЩ1 к точностным параметрам ПАЛ по сравнению с известным.

5

ормула изобретения

ногсающий цифроаналоговый преобразователь, выход которого через первый интегратор соединен с первым входом компаратора, второй нход которого является шиной нулевого потенциала, а выход соединен с первыми входами блока управления и вычисления и формирователя импульсов, второй, третий и четвертый входы которого соединены соответственно с первьт,вторым и третьим выходами блока управления и вы- числения, четвертый выход которого соединен с управляющим входом преобразователя время - код, информационньй вход которого соединен с первым выходом формирователя импульсов, выходы преобразователя время - код поразрядно соединены с соответствующими вторыми входами блока управления и вычисления, пятый, шестой, седьмой, восьмой и девятый выходы которого соединены соответственно с nepatiiM,вторым, треть им и четвертым управляющими входами первого аналогового коммутатора и управляющим входом управляемого инвертора, десятый выходы блока управления и вычисления поразрядно соединены с соответствуюпщми управляющими входами умножающего цифроанало- гового преобразователя, одиннадцатый выход соединен с входом сбро.са первого, интегратора, двенадцатые выходы блока управления и вычисления поразрядно соединены с соответствующими информационными входами регистра, выходы регистра являются выходной шиной, отличающий с я тем, что, с целью повышения точности, в него введены второй интегратор, тре тий и четвертый аналоговые коммутаторы, повторитель напряжения, формирователь модуля, вход которого соединен с выходом усилителя, а выход - с тре- , тьим информационным входом аналогового коммутатора, первый управляющий f вход которого объединен с третьим входом блока управления и вычисления и является первой управофяющей шиной,второй и третий управляющие входы являтся соответственно второй и третьей управляющими шинами, одиннадцатый выход блока управления и вычисления соединен с вторым входом усилителя, тринадцать выход соединен с управляюим входом регистра, выход второго налогового коммутатора через фильтр ижних частот соединен с первым ин- ормационным входом третьего анало588818

гового коммутатора и непосредственно с первым информационным входом четвертого аналогового коммутатора, второй информационньпЧ вход которого соединен 5 с выходом второго интегратора, вход сброса которого объединен с входом сброса первого интегратора, а инфор- мационньй вход соединен с выходом тре- тьего аналогового KOMNryTaTopa, второй информационный вход которого является шиной нулевого потенциала, выход четвертого аналогового коммутатора через повторитель напряжения со- J, единен с информационным входом управляемого инвертора, выход которого соединен с информационным входом умножающего цифроанапогового преобразователя, первый и второй управляющие вхо- 20 ды третьего аналогового коммутатора соединены соответственно с четырнадцатым и пятнадцатым выходами блока управления и вычисления, шестнадцатый и семнадцатый выходы которого соеди- 25 нены соответственно с первым и вторым управляю1цими входами четвертого аналогового коммутатора, второй выход формирователя импульсов соединен с четвертым входом блока управления, 2Q 2. Преобразователь по п.1, отличающийся тем, что блок управления и вычисления вьтолнен на трех элементах И, токоограничивающем элементе, выполненном на резисторе, накопительном элементе, выполненным на конденсаторе, генераторе импульсов, счетчике, трех формирователях коротких импульсов, постоянном запоминающем устройстве, трех инверторах, D-триггере, блоке извлечения квадратного корня и цифровом коммутаторе, первый вход первого элемента И является четвертым входом блока, второй вход через резистор соединен с шиной питания и через конденсатор с шиной нулевого потенциала, третий вход соединен с выходом первого формирователя коротких импульсов, вход которого соединен с выходом заема. переноса счетчика, вход разрешения установки и вычитаюпд1й вход которого соединены со- ответственно с выходам первого элемента И и генератора импульсов, входы установки счетчика являются шинами опорного кода, а его выходы поразрядно соединены с соответствующими адресными входами постоянного запоминающего устройства, первый выход которого является пятым и тринадцатым выходами

5

0

5

0

5

1916

блока и соединен с входом первого инвертора , выход которого соединин с С-входом D-триггера и входом второго формирователя коротких импульсов, выход которого является четвертым выходом блока, шестым и девятым выходами которого являются соответственно второй и третий выходы постоянного запоминающего устройства5 четвертый выход которого является пятнадцатым выходом блока и соединен с входом второго инвертора,выход которого является четырнадцатым выходом блока, семнадцатым выходом которого является пятый выход постоянного запоминающего устройства, который соединен с входом третьего инвертора, выход которого является шестнадцатым выходом блока, вторым выходом которого является выход третьего формирователя коротких импульсов,вход которого соединен с шестым выходом постоянного запоминающего устройства, седьмой выход которого соединен с первыми входами второго и третьего элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами П-триггера П-вход которого является первым входом блока, седьмым, восьмым и третьим выходами которого являются соответственно выходы второго и третьего элементов И и прямой выход 1)-триггера,восьмые выходы постоянного запоминающего устройства являются соответственно десятыми выходами блока, двенадцатыми выходами которого являются выходы цифрового коммутатора,первые информационные входы которого поразрядно соединены с соответствующими выходами блока извлечения квадратного корня, информационные входы которого поразрядного объединены с вто88820

рыьш информационными входами цифрового коммутатора и являются соответственно вторыми входами блока, третьим входом которого является управ- лягощий вход цифрового коммутатора, девятые выходы постоянного запоминающего устройства поразрядно соединены .с соответствующими управляющими вхо- fj дами блока извлечения квадратного корня, десятый выход постоянного запоминающего устройства является одиннадцатым выходом блока, первым выходом которого является выход первого эле- 5 мента И,

35

Фиг.

t,

ЩигМ

Ws

tf i

| Клисторин И.Ф | |||

| , Жугат арь Ф.И., Тютякин А.В, Быстродействующий микропроцессорный АЦП интегральных характеристик периодических сигналов | |||

| - Приборы и системы управления, 1985, :fR 11, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Клисторин И.Ф., Жуганарь Ф.И | |||

| и др | |||

| Системный цифровой мультиметр со встроенной микроЭВМ | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| I секции республик, науч | |||

| - техн | |||

| конф | |||

| Применение микропроцессоров в народном хозя-йстве,24-25 мая 1988, Таллин, с.74-76. | |||

Авторы

Даты

1990-12-23—Публикация

1988-11-04—Подача