4

Од СО О5 О 00

Изобретение относится к ;и,- -;ислг.-- телыюй технике и может м;- имепяться fifin приема инфор с и. о ly-iqjpGXJз ю числительную 1. по нескопьктпи информационным каи;ии;м.,

Целью изобретения яв.гьче г.я повышение достоБврностн приема 1-п1фс;рмацпи

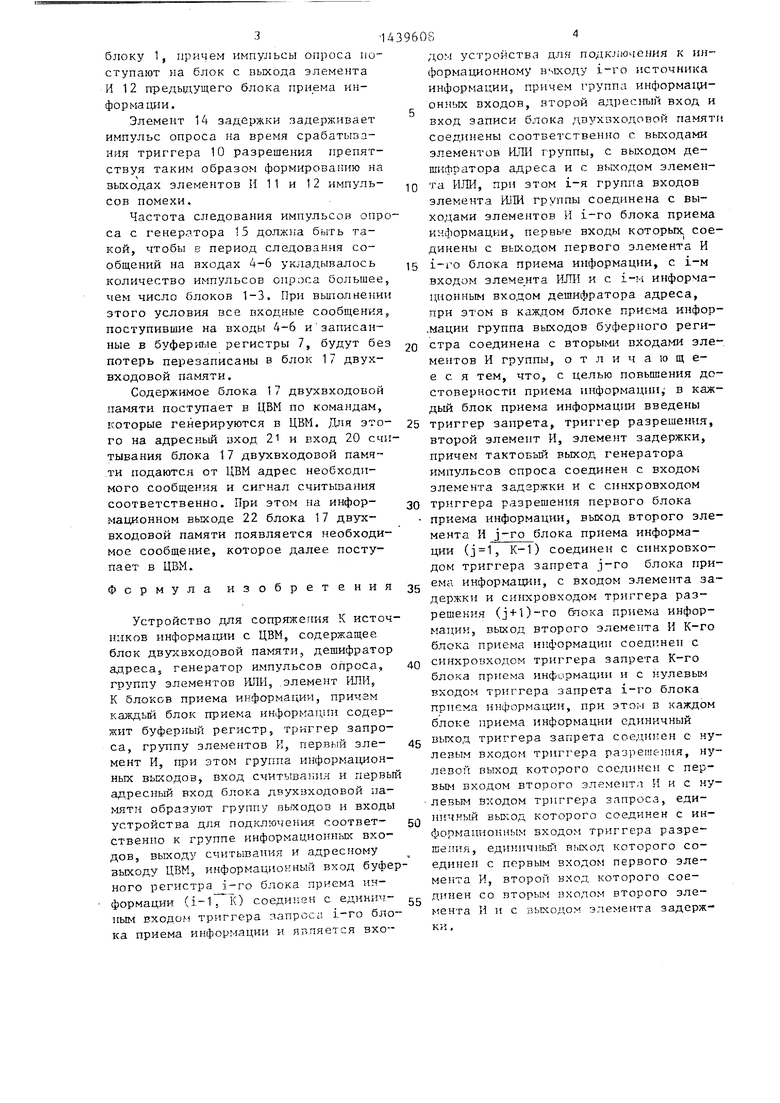

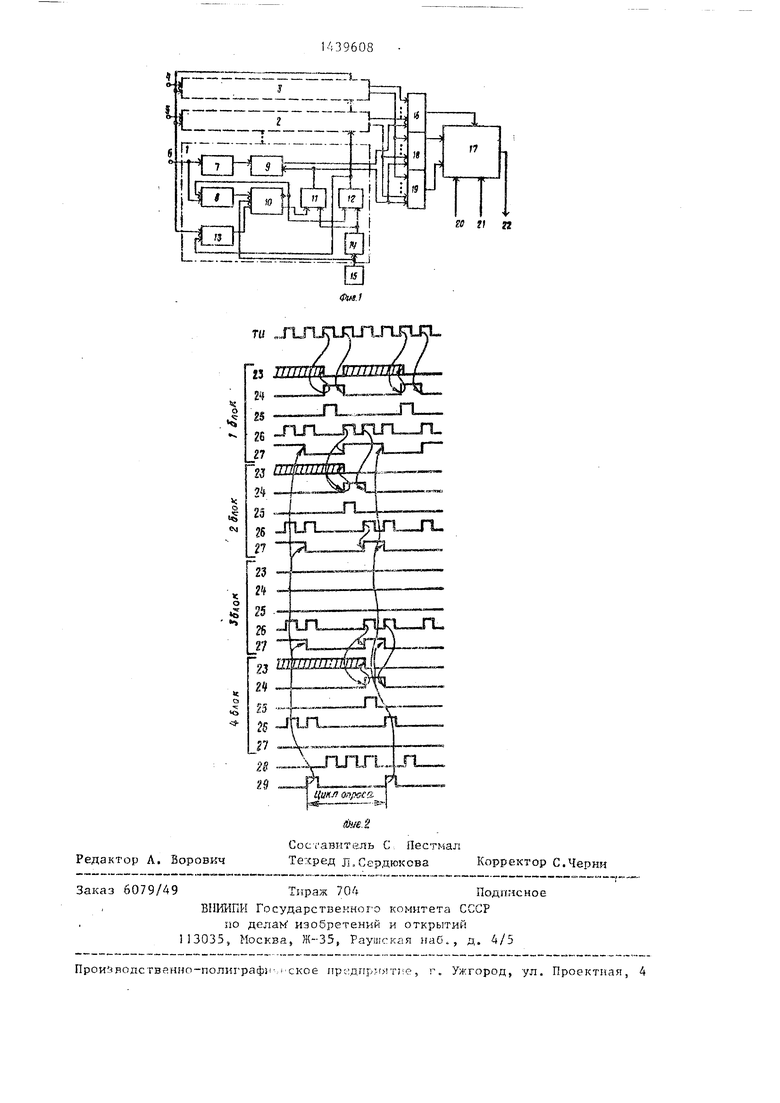

На фиг. 1 представлена структурная схема ycTpotlcfEaj на фиг, 2 - BpeMeuнал диаграмма работы устройства.

Устройство содержит (фиг„1) блоки 1-3 прие.л.а ин;} ормацни,, информационные входы 4-6, KaiKju iH блок г/ри- ена информации содержит буферный ре- гистр 7, триггер 8 запроса, группу элементов И 9, триггер 10 разреи1ения, элементы И II и 12, триггер 13 запрета, элемент 14 задержки. Кроме того, устройство содержит генератор 15 им- пульсов опроса, г руттпу злементоз ИЛИ 16, блок i7 двухвходовой памяти, дешифратор 18 адреса, длемонт ИЛИ 19, входы 20 и 21 и выход .пя подключения к цифровой Бычислительной мапшне (ЦВМ).

На фиг. 2 обозначены выход 23 триггера 8 запросов, выход 24 триггера 10 разрешения, выход 25 злемеита И 11, 26 элемента И 12„ выход 27 триг гера 13 запрета, выход 28 элемента ИЛИ 19j выход 29 элемег та 11 12 K-i o блока приема информации.

На фиг. 2 также представлена лре- менная диаграмма работы устройства для случая, когда нмеготся 4 блока приема сообщений, причем сооб;дения

поступили в 1,2 и Ч блЮКН. в 3-м

блоке сообщения нет.

Устройство работает следующим об-

разом.

При поступлении сообш, на какой либо ВХОД; например вход. ; DJi.jKa 1 (фиг.1), оно записывается в буфе тпый регистр 7, одновременно происходит установка триггера 8 запроса (фиг,2). Сигнал Запрос с едини-гмого яьк.ода триггера 8 запроса поступает на информационный вход тр.нггера 10 разрешения. Цикл опроса канаУгоБ начинается

с импульса сбросг;,, который 1оступает

на пулевой вход григгера 13 запрета всех блоков, далее с npnxojiciM .:еред- него фронта (переход из низкого уров- -. ня в.вьгсокий) импульса оггроса с еиератора 15 HMiiynbcnr :;а силхровход триггер; ТО р.,ачещенил последний устанапписае т ся в ЙДИПРГ-ЧЮС состояние - (фиг. 2). с од11мич

Q

5 0 5

0

.„.

f j

р

5

лого 1-;ькода риггера 10 разрешения разрешает работу элементу И i1, сиг- na.fi с мулеаого выхода триггера 10 разрешения сбрасьгоает триггер 8 запроса (фиг,2) и запрещает работу элемента И 12,, По сигналу с выхода элемента И 11 сообщение из буферного регистра 7 передается через группу элементов И 9 на вход т руппы элементов ШТИ 16, с выхода которых - на информационный вход блока 17 двухвходо- вой памяти, Одновреь енно TaKjKe по сигналу с выхода элемента К 11 дешифратора 18 адреса Г1Ор {ирует адрес, который поступает -ui .-щресный вход блока 17 двухвходовой памяти, а элемент ШИ 19 формирует на своет; сигнал записи (фиг,2)5 при этом информация из первого блока приема информации записывается в блок 17 двухвходо- Еой памяти. С приходом с:тедую1цего импульса опроса с i eHcpfxTopa 15 импульсов опроса триггеру 10 раз;;: ешеш1к устанавпивается з нулевое состояние с еди.пнчногс ныходы., запрещая работу элемента И 11; ас нулевого выхода разрешая работу элемента И 12, слгна. с выхода элемеь та И 12 поступает на след- лсш.ий блок в качестве иьигульса опроса и устанавливает триггер 13 запрета в единичное состояние. Сиг- кал с единичного выхода триггера 13 запрета поступает па нулезой вход триггера 10 разрешения, в результате чего т эиггер 10 аазреи ения фикСиру- ется в состоянии разрешен гя передачи имлульсоЕ опроса ч ергз элемент F 12 на следующий блох 2 приема информации. Триггер 13 запрета сбрасглза- ется в KoiiiTe ци сла опроса блоков сигналом с элемента И 12 последнего . блока 3 приема информадии

Если при приходе очередного импульса опроса триггер 8 запроса в блоке не установлен (фиг„2s блок 3), то триггер 10 разрешения ;е изменяет скоего состояния и импульсы опроса поступают через элемент Н 12 на опрос следующего блока ,При достшкении импульсов опроса последнего блока приема информации на выходе его элемента И 12 формиру- f-TCfi сигнал окончания цикла опроса, который сбрасывает трип-еры запретгг яо всех блоках, п начинается новый ;,икл дпроса каналов.

Работа остальнызс блоков нрчема информации проис ;:одит анй.логичнс

блоку 1, причем импульсы опроса поступают на блок с выхода элемента И 12 предыдущего блока приема ин- формадяи.

Элемент 14 задержки задерживает импульс опроса на время срабатывания триггера 10 разрешения препятствуя таким образом формированию на выходах элементов И 11 и 12 импульсов помехи.

Частота следования импульсов опрса с генератора 15 должна быть такой, чтобы в период следования сообщений на входах 4-6 укладывалось количество импульсов опроса большее чем число блоков 1-3. При выполнени этого условия все входные сообщения поступившие на входы 4-6 и записанные в буферHfjie регистры 7, будут бе потерь перезаписаны в блок 17 двух- входовой памяти.

Содержимое блока 17 двухвходовой памяти поступает в ЦВМ по командам, которые генерируются в ЦВМ. Для этого на адресный вход, 21 и вход 20 счтывания блока 17 двухвходовой памя- .ти подаются от ЦВМ адрес необходимого сообщения и сигнал считывания соответственно. При этом на. информационном выходе 22 блока 17 двухвходовой памяти появляется необходимое сообщение, которое далее поступает в ЦВМ.

Формула изобретения

Устройство для сопряжения К источников информации с ЦВМ, содержащее блок двухвходовой , дешифратор адреса, генератор импульсов опроса, группу элементов ИЛИ, .элемент ИЛИ, К блоков приема информации, причем каждьм блок приема информации содержит буферный регистр, триггер запроса, группу элементов И, первый элемент И, при этом группа информационных выходов, вход считывагшл и первьй адресный вход блока двухвходовой памяти образуют группу вь/ходоз и входы устройства для подключения соответственно к группе информационных вхо дов, выходу считывания и адресному выходу ЦВМ, информационный вход буфер22 ема информации, с входом элемента з держки и синхровходом триггера разрешения (j-H)ro &1ока приема инфор мации, выход второго элемента И К-г блока приема информации соединен с синхровходом триггера запрета К-го блока приема информации и с нулевым входом триггера запрета i-ro блока приема информации, при этом в каждо блоке приема информации единичный выход триггера запрета соединен с н левым входом триггера разре111е1 ня, н левой выход которого соединен с пер вым входом второго элемент И и с н левым входом триггера запроса, единичный вькод которого соединен с ин фop 5aпиoнным входом триггера разрешения, еди}П1чньш выход которого соединен с первым входом первого элемента И, второй вход которого соеного регистра i-ro блока приема VIHформации () соеди :ен с единич- gg динен со вторым входом второго эле- ным входом триггера запроса i-ro блока приема информации и является вхомента И и с выходом элемента задержки.

0

0

дом устройства для подключения к информационному выходу i-ro источника информации, причем группа информагщ- онных входов, второй адресный вход и вход записи блока двухвходовой памяти соединены соответственно с выходами элементов ИЛИ группы, с выходом дешифратора адреса и с выходом элемента ИЛИ, при этом i-я группа входов элемента ИЛИ группы соединена с выходами элементов И i-ro блока приема информации, первые входы которых соединены с выходом первого элемента И

5 iro блока приема информации, с 1-м входом элеме нта IlfTIi и с i-м информационным входом дешифратора адреса, при этом в каж,цом блоке приема инфор- .мации группа выходов буферного регистра соединена с вторыми входами элементов И группы, о т л и ч а ю щ е- е с я тем, что, с целью повьш ения достоверности при.ема информации в каждый блок приема информации введены

5 триггер запрета, триггер разрешения, второй элемент И, элемент задержки, причем тактоБьш выход генератора импульсов опроса соединен с входом элемента задержки и с синхровходом

0 триггера разрешения первого блока - приема информации, выход второго элемента И j-ro блока приема информации (, К-1) соединен с синхровходом триггера запрета j-го блока при2 ема информации, с входом элемента задержки и синхровходом триггера разрешения (j-H)ro &1ока приема информации, выход второго элемента И К-го блока приема информации соединен с синхровходом триггера запрета К-го блока приема информации и с нулевым входом триггера запрета i-ro блока приема информации, при этом в каждом блоке приема информации единичный выход триггера запрета соединен с нулевым входом триггера разре111е1 ня, нулевой выход которого соединен с первым входом второго элемент И и с нулевым входом триггера запроса, единичный вькод которого соединен с ин- фop 5aпиoнным входом триггера разрешения, еди}П1чньш выход которого соединен с первым входом первого элемента И, второй вход которого сое0

5

0

динен со вторым входом второго эле-

мента И и с выходом элемента задержки.

|rL,.LJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сопряжения каналов связи с ЭВМ | 1985 |

|

SU1278873A1 |

| Многоканальное устройство для сопряжения абонентов с цифровой вычислительной машиной | 1986 |

|

SU1310831A2 |

| Многоканальное устройство сопряжения абонентов с цифровой вычислительной машиной | 1984 |

|

SU1234842A1 |

| Устройство для управления обменом информации | 1982 |

|

SU1081638A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| Устройство для сопряжения в многотерминальной вычислительной системе | 1984 |

|

SU1166124A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство для сопряжения цифровой вычислительной машины | 1987 |

|

SU1444793A1 |

Изобретение относится к вычислительной технике и может применяться для приема информации в ЦВМ по нескольким инфopмaцк нны каналам. Целью изобретения является повышение достоверности приема информации. Устройство содержит блок двухвходовой памяти, дешифратор адреса, группу элементов ИЛИ, элекент ШШ, генератор импульсов опроса К блоков приема информации. 2 ил.

TU

20

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1980 |

|

SU941979A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство сопряжения абонентов с цифровой вычислительной машиной | 1984 |

|

SU1234842A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1987-04-22—Подача