Изобретение относится к запоминающим устройствам и может найти применение в вычислительной технике для наладки, записи и контроля блоков программируемого постоянного запоминающего устройства (ППЗУ).

Целью изобретения является повышение надежности устройства.

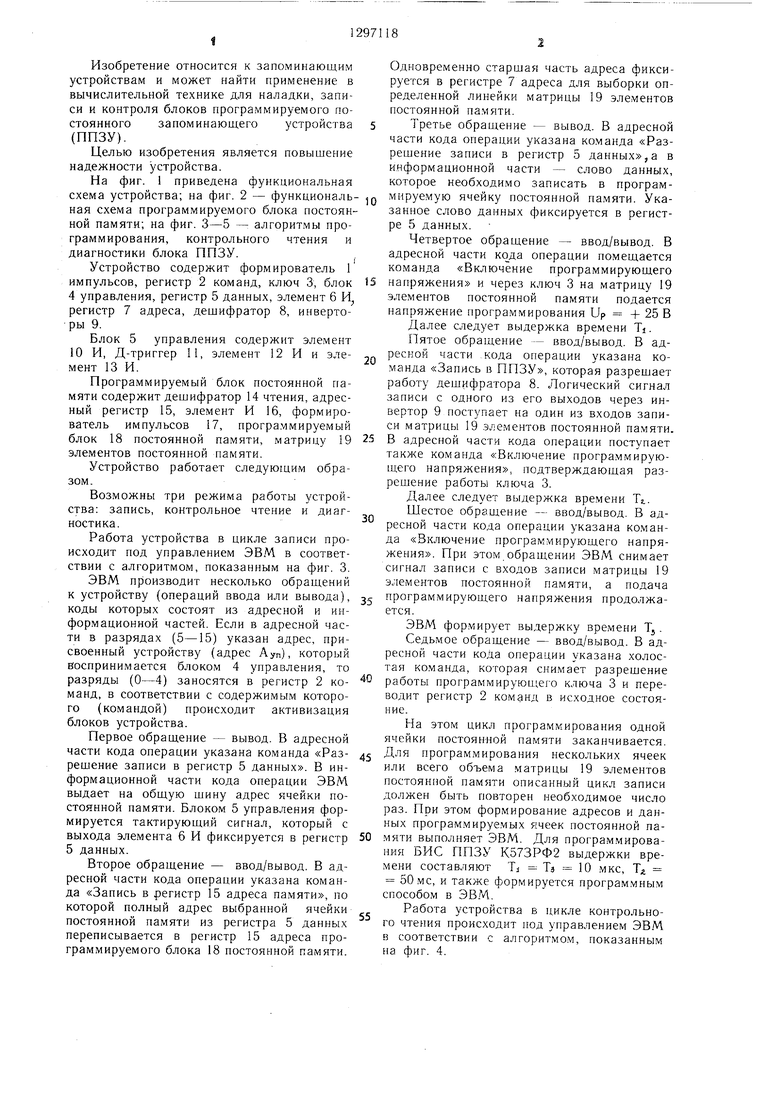

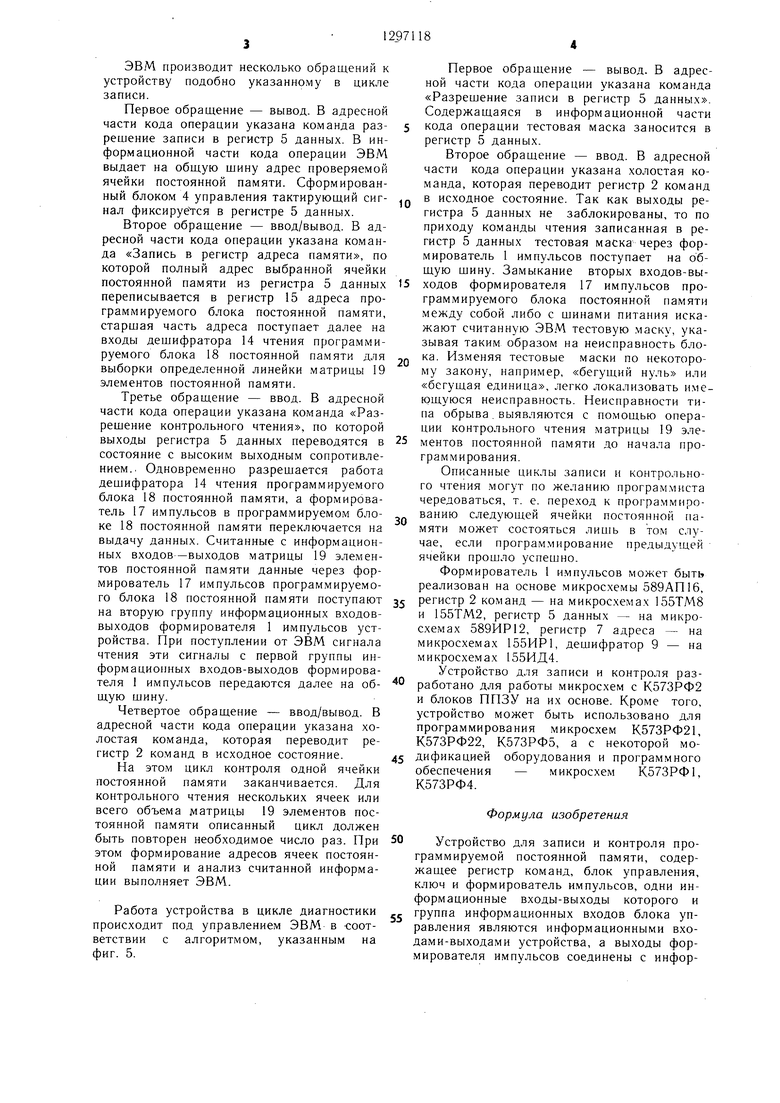

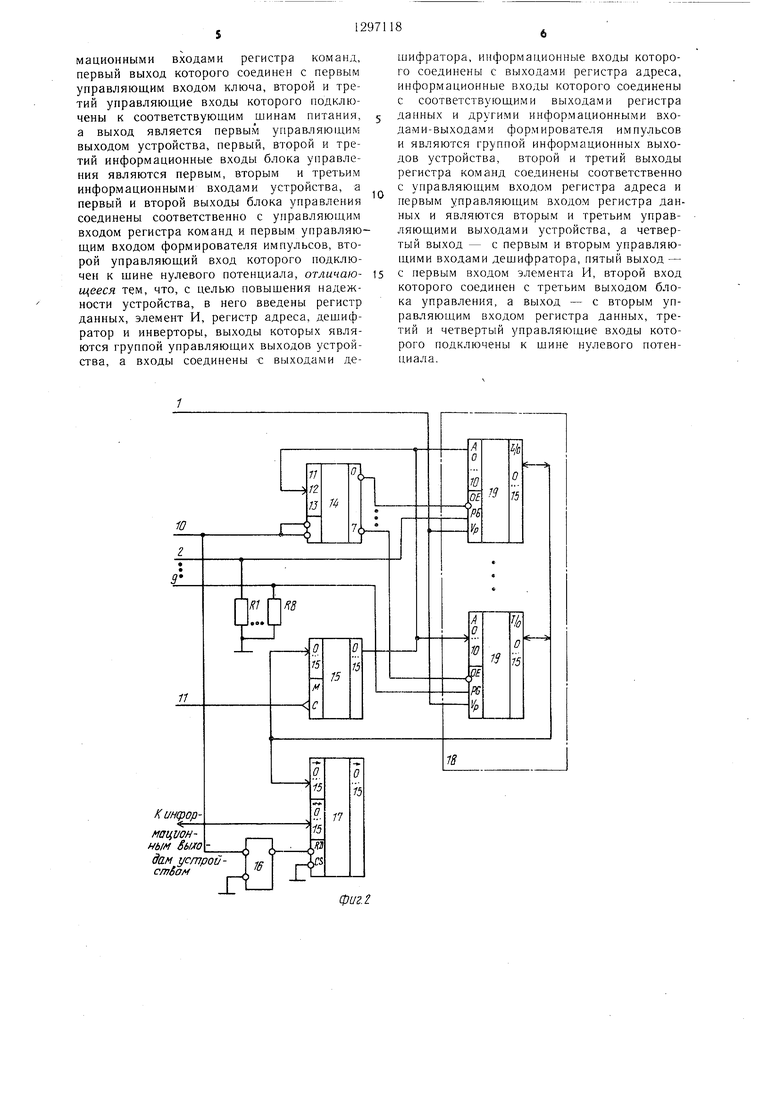

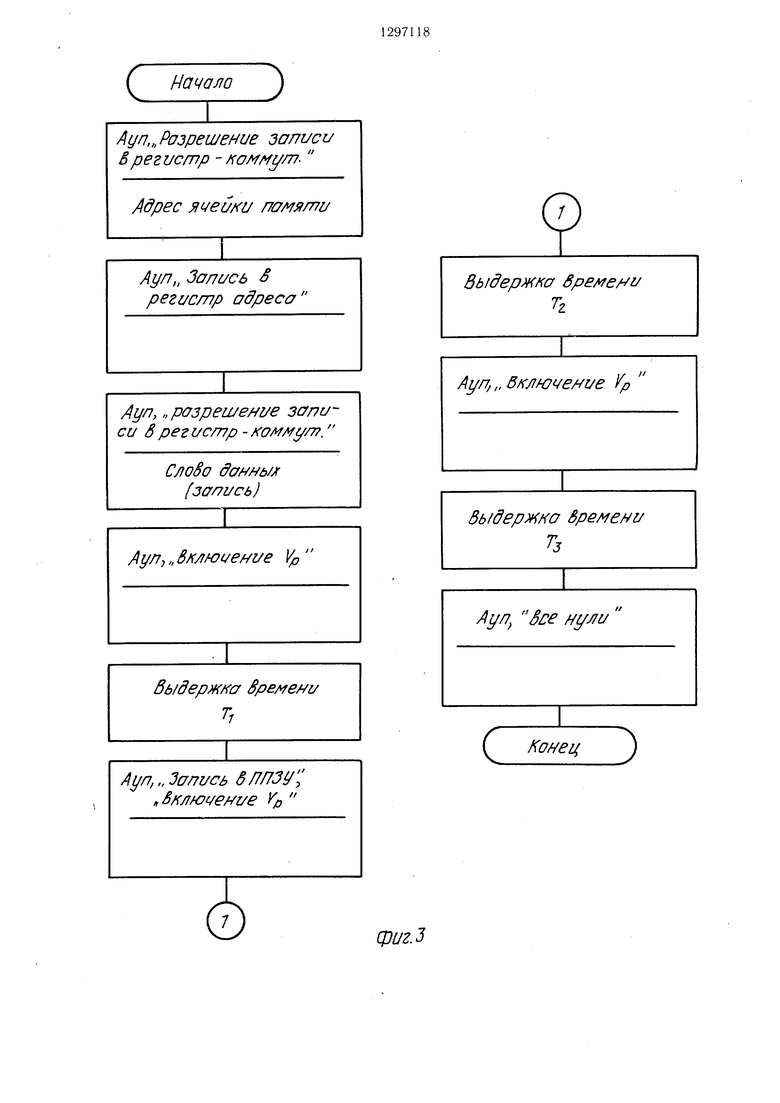

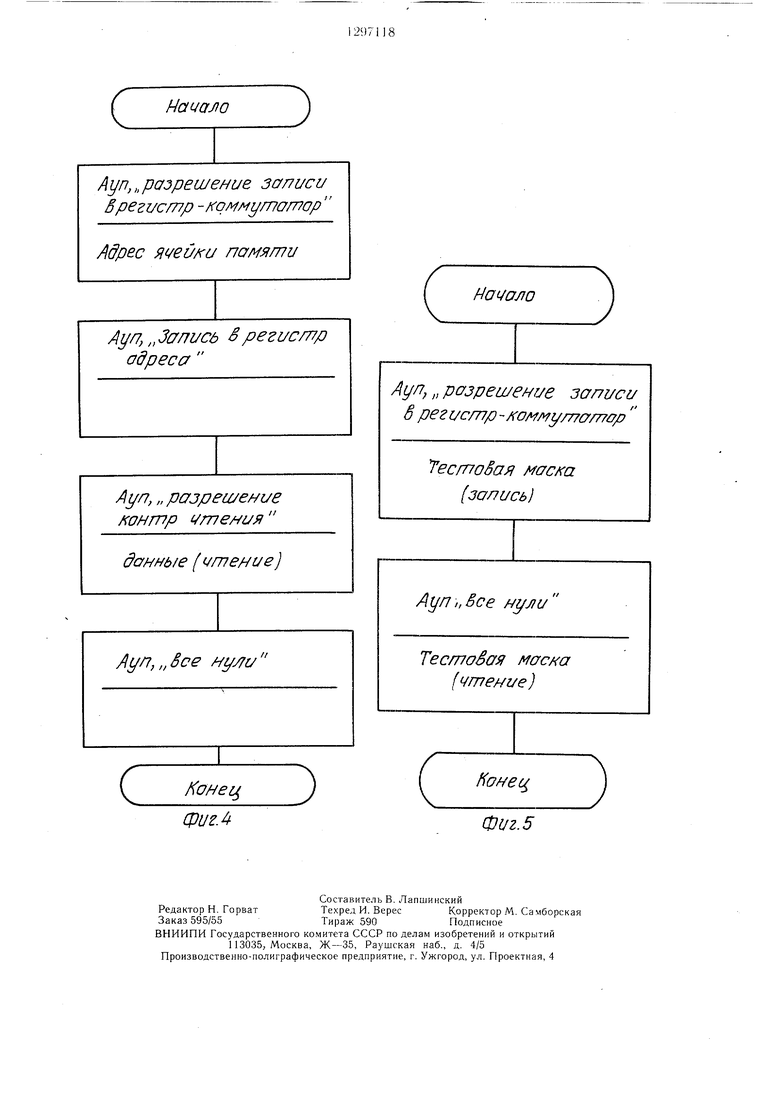

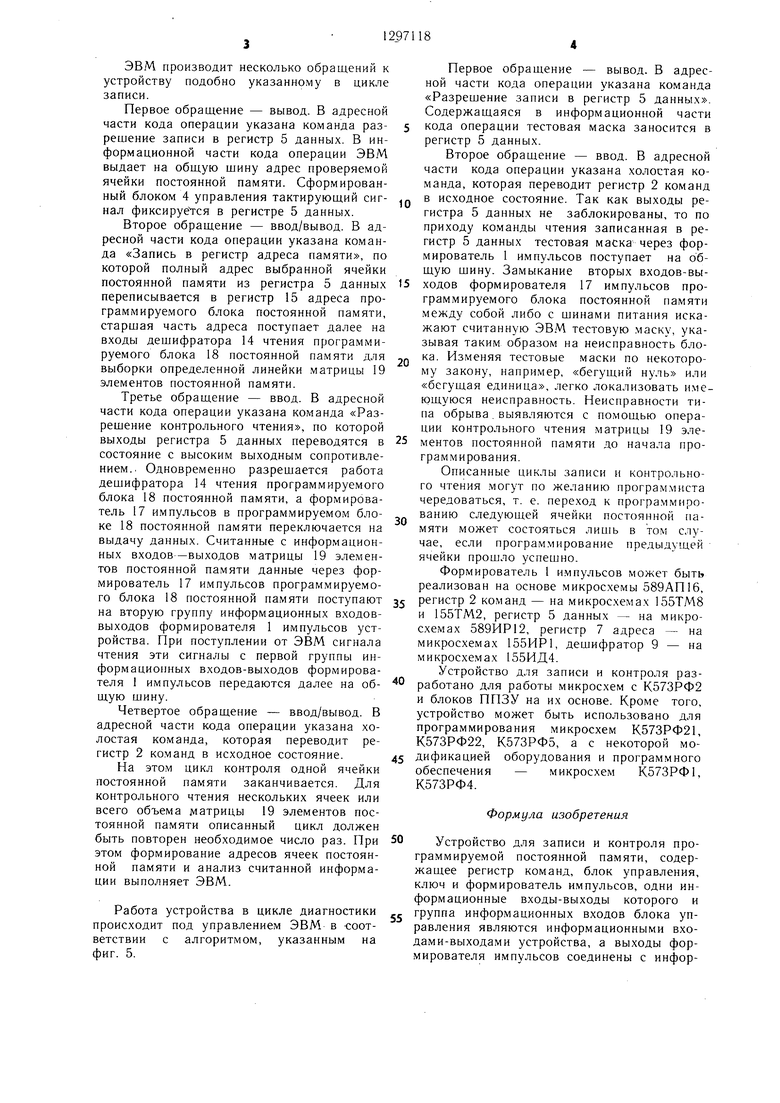

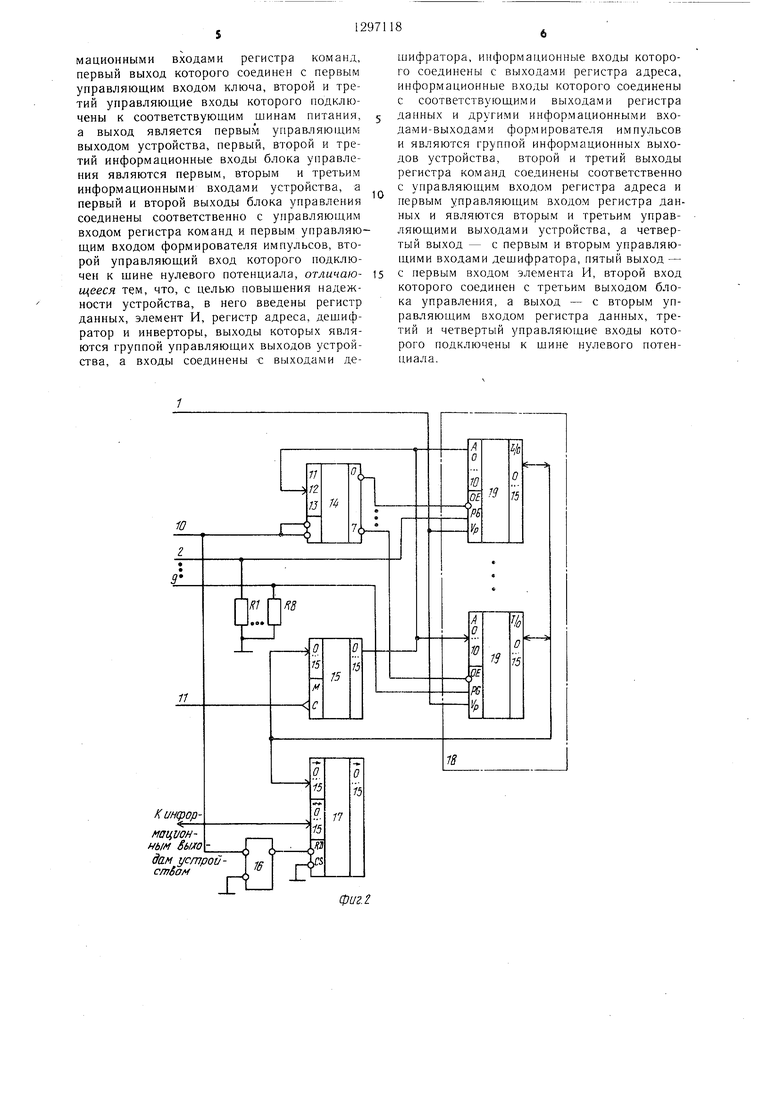

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональ- ная схема программируемого блока постоянной памяти; на фиг. 3-5 -: алгоритмы программирования, контрольного чтения и диагностики блока ППЗУ.

Устройство содержит формирователь 1 импульсов, регистр 2 команд, ключ 3, блок

4управления, регистр 5 данных, элемент 6 И., регистр 7 адреса, дешифратор 8, инверторы 9.

Блок 5 управления содержит элемент 10 И, Д-триггер И, элемент 12 И и эле- мент 13 И.

Программируемый блок постоянной памяти содержит дешифратор 14 чтения, адресный регистр 15, элемент И 16, формирователь импульсов 17, программируемый блок 18 постоянной памяти, матрицу 19 элементов постоянной памяти.

Устройство работает следующим образом.

Возможны три режима работы устройства: запись, контрольное чтение и диаг- ностика.

Работа устройства в цикле записи происходит под управлением ЭВМ в соответствии с алгоритмом, показанным на фиг. 3.

ЭВМ производит несколько обращений к устройству {операций ввода или вывода), коды которых состоят из адресной и информационной частей. Если в адресной части в разрядах (5-15) указан адрес, присвоенный устройству (адрес Ауп), который Воспринимается блоко.м 4 управления, то разряды (О-4) заносятся в регистр 2 ко- манд, в соответствии с содержимым которого (командой) происходит активизация блоков устройства.

Первое обращение - вывод. В адресной части кода операции указана команда «Раз- решение записи в регистр 5 данных. В информационной части кода операции ЭВМ выдает на общую шину адрес ячейки постоянной памяти. Блоком 5 управления формируется тактирующий сигнал, который с выхода элемента 6 И фиксируется в регистр

5данных.

Второе обращение - ввод/вывод. В адресной части кода операции указана команда «Запись в регистр 15 адреса памяти, по которой полный адрес выбранной ячейки постоянной памяти из регистра 5 данных переписывается в регистр 15 адреса программируемого блока 18 постоянной памяти.

Одновременно старшая часть адреса фиксируется в регистре 7 адреса для выборки определенной линейки матрицы 19 элементов постоянной памяти.

Третье обращение - вывод. В адресной части кода операции указана ко.манда «Разрешение записи в регистр 5 данных,а в информационной части - слово данных, которое необходимо записать в програм- мируе.мую ячейку постоянной памяти. Указанное слово данных фиксируется в регистре 5 данных.

Четвертое обращение - ввод/вывод. В адресной части кода операции помещается команда «Включение программирующего напряжения и через ключ 3 на матрицу 19 элементов постоянной памяти подается напряжение программирования Up + 25 В

Далее следует выдержка времени Tj.

Пятое обращение - ввод/вывод. В адресной части кода операции указана команда «Запись в ППЗУ, которая разрешает работу дешифратора 8. Логический сигнал записи с одного из его выходов через инвертор 9 поступает на один из входов записи матрицы 19 элементов постоянной памяти. В адресной части кода операции поступает также команда «Включение програ.ммирую- щего напряжения, подтверждающая разрешение работы ключа 3.

Цалее следует выдержка времени Тг,.

Шестое обращение - ввод/вывод. В адресной части кода операции указана команда «Включение программирующего напряжения. При этом обращении ЭВМ снимает сигнал записи с входов записи матрицы 19 элементов постоянной памяти, а подача программирующего напряжения продолжается.

ЭВМ формирует выдержку времени Т,.

Седьмое обращение - ввод/вывод. В адресной части коДа операции указана холостая команда, которая снимает разрешение работы программирующего ключа 3 и переводит регистр 2 команд в исходное состояние.

На этом цикл программирования одной ячейки постоянной памяти заканчивается. Для программирования нескольких ячеек или всего объема матрицы 19 элементов постоянной памяти описанный цикл записи должен быть повторен необходимое число раз. При этом формирование адресов и данных программируемых ячеек постоянной памяти выполняет ЭВМ. Для програм.мирова- ния БИС ППЗУ К573РФ2 выдержки времени составляют Ъ Тз 10 мкс, Тд 50 мс, и также формируется програм.мным способом в ЭВ. Л,

Работа устройства в цикле контрольного чтения происходит под управлением ЭВМ в соответствии с алгоритмом, показанным на фиг. 4.

ЭВМ производит несколько обращений к устройству подобно указанному в цикле записи.

Первое обращение - вывод. В адресной части кода операции указана команда раз- рещение записи в регистр 5 данных. В информационной части кода операции ЭВМ выдает на общую щину адрес проверяемой ячейки постоянной памяти. Сформированный блоком 4 управления тактирующий сиг- нал фиксируемся в регистре 5 данных.

Второе обращение - ввод/вывод. В адресной части кода операции указана команда «Запись в регистр адреса памяти, по которой полный адрес выбранной ячейки постоянной памяти из регистра 5 данных переписывается в регистр 15 адреса программируемого блока постоянной памяти, старщая часть адреса поступает далее на входы дещифратора 14 чтения программируемого блока 18 постоянной памяти для выборки определенной линейки матрицы 19 элементов постоянной памяти.

Третье обращение - ввод. В адресной части кода операции указана команда «Раз- рещение контрольного чтения, по которой выходы регистра 5 данных переводятся в состояние с высоким выходным сопротивлением.. Одновременно разрещается работа дещифратора 14 чтения программируемого блока 18 постоянной памяти, а формирователь 17 импульсов в программируемом блоке 18 постоянной памяти переключается на выдачу данных. Считанные с информационных входов -выходов матрицы 19 элементов постоянной памяти данные через формирователь 17 импульсов программируемого блока 18 постоянной памяти поступают на вторую группу информационных входов- выходов формирователя 1 импульсов устройства. При поступлении от ЭВМ сигнала чтения эти сигналы с первой группы информационных входов-выходов формирователя 1 импульсов передаются далее на об- щую щину.

Четвертое обращение - ввод/вывод. В адресной части кода операции указана холостая команда, которая переводит регистр 2 команд в исходное состояние.

На этом цикл контроля одной ячейки постоянной памяти заканчивается. Для контрольного чтения нескольких ячеек или всего объема матрицы 19 элементов постоянной памяти описанный цикл должен быть повторен необходимое число раз. При этом формирование адресов ячеек постоянной памяти и анализ считанной информации выполняет ЭВМ.

Работа устройства в цикле диагностики происходит под управлением ЭВМ в -соответствии с алгоритмом, указанным на фиг. 5.

Первое обращение - вывод. В адресной части кода операции указана команда «Разрещение записи в регистр 5 данных. Содержащаяся в информационной части кода операции тестовая маска заносится в регистр 5 данных.

Второе обращение - ввод. В адресной части кода операции указана холостая команда, которая переводит регистр 2 команд в исходное состояние. Так как выходы регистра 5 данных не заблокированы, то по приходу команды чтения записанная в регистр 5 данных тестовая маска через формирователь 1 импульсов поступает на общую щину. Замыкание вторых входов-выходов формирователя 17 импульсов программируемого блока постоянной памяти между собой либо с щинами питания искажают считанную ЭВМ тестовую маску, указывая таким образом на неисправность блока. Изменяя тестовые маски по некоторому закону, например, «бегущий нуль или «бегущая единица, легко локализовать и.ме- ющуюся неисправность. Неисправности типа обрыва. выявляются с помощью операции контрольного чтения матрицы 19 элементов постоянной памяти до начала программирования.

Описанные циклы записи и контрольного чтения .могут по желанию программиста чередоваться, т. е. переход к программированию следующей ячейки постоянной памяти может состояться лишь в том случае, если программирование предыдущей ячейки прощло успещно.

Формирователь 1 и.мпульсов может быть реализован на основе микросхемы 589АП16, регистр 2 команд - на микросхемах 155ТМ8 и 155ТМ2, регистр 5 данных - на микросхемах 589ИР12, регистр 7 адреса - на микросхемах 155ИР1, дещифратор 9 - на микросхемах 155ИД4.

Устройство для записи и контроля разработано для работы микросхем с К573РФ2 и блоков ППЗУ на их основе. Кроме того, устройство может быть использовано для программирования микросхем К573РФ21, К573РФ22, К573РФ5, а с некоторой модификацией оборудования и программного обеспечения - микросхем К573РФ1, К573РФ4.

Формула изобретения

Устройство для записи и контроля программируемой постоянной памяти, содержащее регистр команд, блок управления, ключ и формирователь импульсов, одни информационные входы-выходы которого и группа информационных входов блока управления являются информационными входами-выходами устройства, а выходы формирователя импульсов соединены с инфор

мационными входами регистра команд, первый выход которого соединен с первым управляющим входом ключа, второй и третий управляющие входы которого подключены к соответствующим шинам питания, а выход является первы и управляющим выходом устройства, первый, второй и третий информационные входы блока управления являются первым, вторым и третьим информационными входами устройства, а первый и второй выходы блока управления соединены соответственно с управляющим входом регистра команд и первым управляющим входом формирователя импульсов, второй управляющий вход которого подключен к шине нулевого потенциала, отличаю- щееся тем, что, с целью повышения надежности устройства, в него введены регистр данных, элемент И, регистр адреса, дешифратор и инверторы, выходы которых являются группой управляющих выходов устройства, а входы соединены -с выходами де

шифратора, информационные входы которого соединены с выходами регистра адреса, информационные входы которого соединены с соответствующими выходами регистра данных и другими информационными входами-выходами формирователя импульсов и являются группой информационных выходов устройства, второй и третий выходы регистра команд соединены соответственно с управляющим входом регистра адреса и первым управляющим входом регистра Данных и являются вторым и третьим управляющими выходами устройства, а четвертый выход - с первым и вторым управляющими входами дешифратора, пятый выход - с первым входом элемента И, второй вход которого соединен с третьим выходом блока управления, а выход - с вторым управляющим входом регистра данных, третий и четвертый управляющие входы которого подключены к шине нулевого потенциала.

фи2.2

Г Начало J

Ai/n,„Разрешение записи В регистр - .

Адрес пс7мя/77и

Ауп„ Запись регистр адреса

Аул, „разрешение записи в рег исл7р - f(OMAfi//7.

Сло8о запись)

Аул „Вмю1/ен1/е Ур

Вь/держ/ а Времена/ TI

Ai/n, „ дапись бЛЛЗУ ,ё/ лю /ен1/е jo

Выдержка TZ

Ауп, „ 5ff H}i ejHue Ур

6b/dep) бремени Тз

Ауп See

(конец

Устройство относится к вычислительной технике и может найти применение при наладке и программировании блоков ППЗУ. Цель изобретения - повышение надежности устройства. Изобретение позволяет выявлять и локализовать неисправности в блоках ППЗУ, за счет чего совмещаются операции наладки и программирования в одном устройстве. Устройство содержит формирователь I импульсов, регистр 2 команд, ключ 3, блок 4 управления, регистр 5 данных, элемент И 6, регистр 7 адреса, дешифратор 8. Ил. 5. Общая шина & (Л Ю со 00 Информациан- ные выходы

фиг.З

с

HauajJo

Ауп,„разрешение записи В регистр -/ омму/77(

Адрес Я( памяти

Ауп, „Запись ё/}ezLfc/77/} адреса

At//7, „ разрешение

доннь/е тение

С

KoHei

фиг. 4

Редактор Н. Горват Заказ 595/55

Составитель В. Лапшинскнй

Техред И. ВересКорректор М. Са мборская

Тираж 590Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Но(оло

Ауп, „ разрешение записи 6 peef/c/77/} -/fo/ Mi/fnamffp

естобая золись

Ауп,,ёсе Hf/Mu

Тестовая (чтение

Фиг. 5

| Патент США № 4093998, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-04—Подача