оо 00

ел

;о 1C

Изобретение относится к вычислительной технике, а именно к управляющим устройствам программирования, и может быть использовано при программировании интегральных микросхем типа программируемых логических матриц (ПЛМ).

Цель изобретения - расширение об- ластн применения за счет возможности программирования ПЛМ и повышения быстродействия устройства.

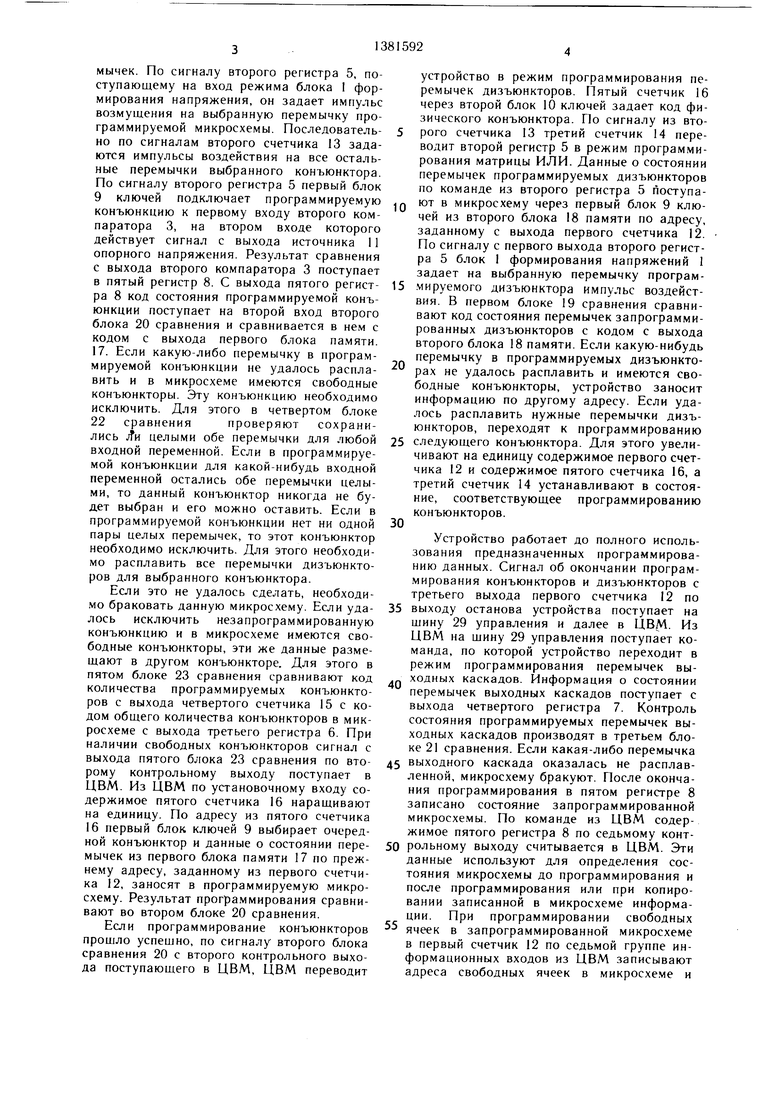

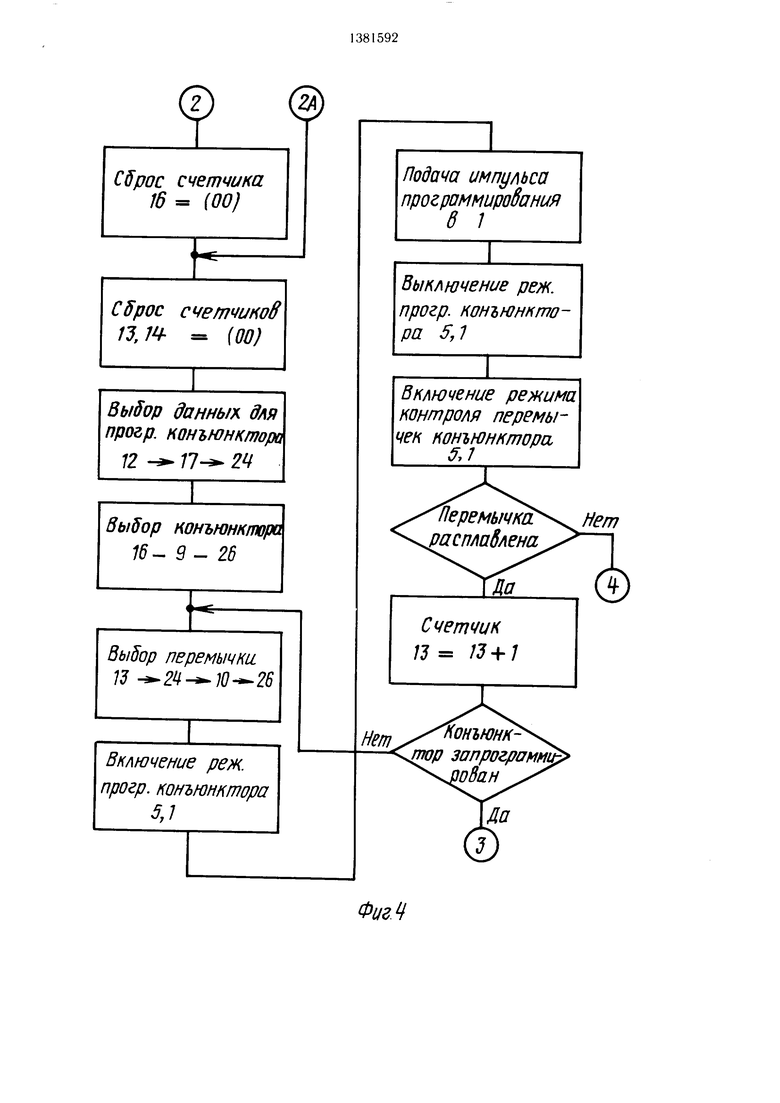

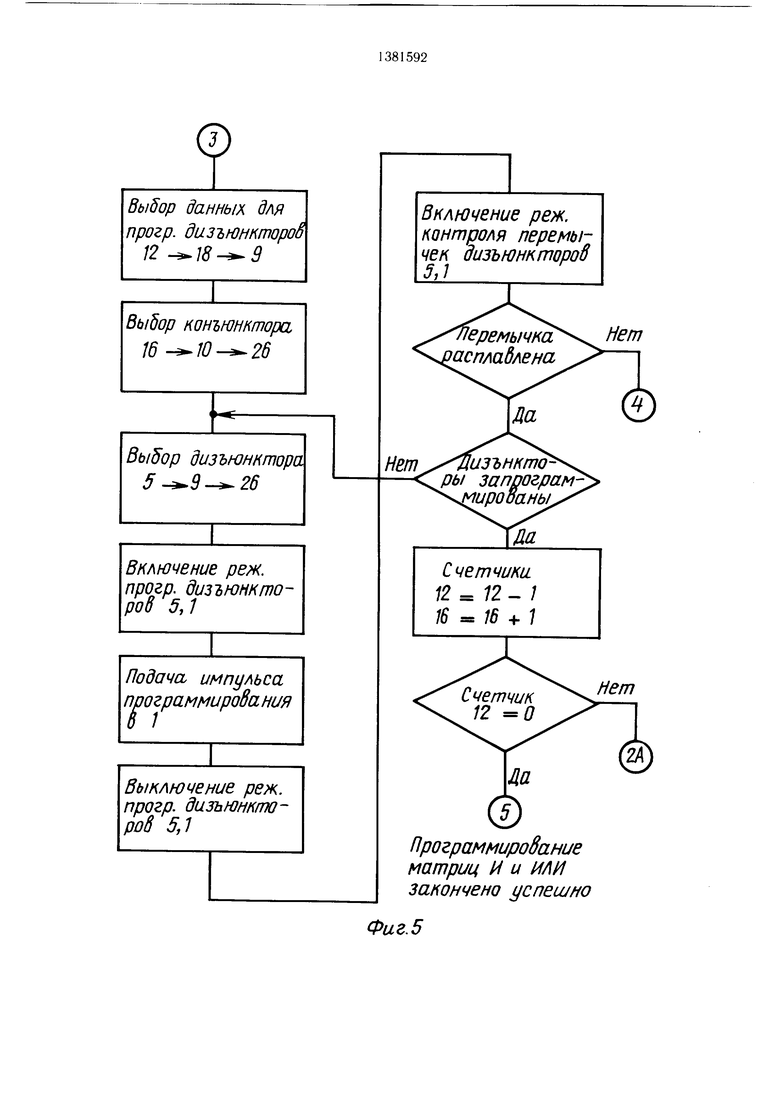

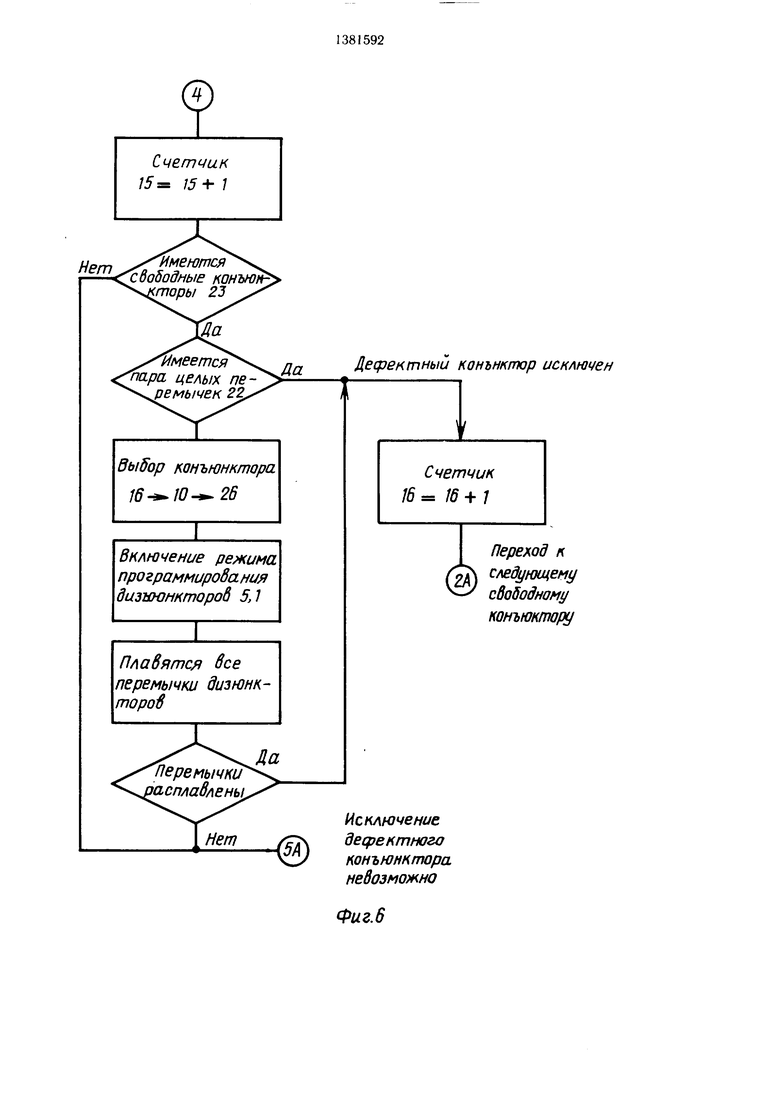

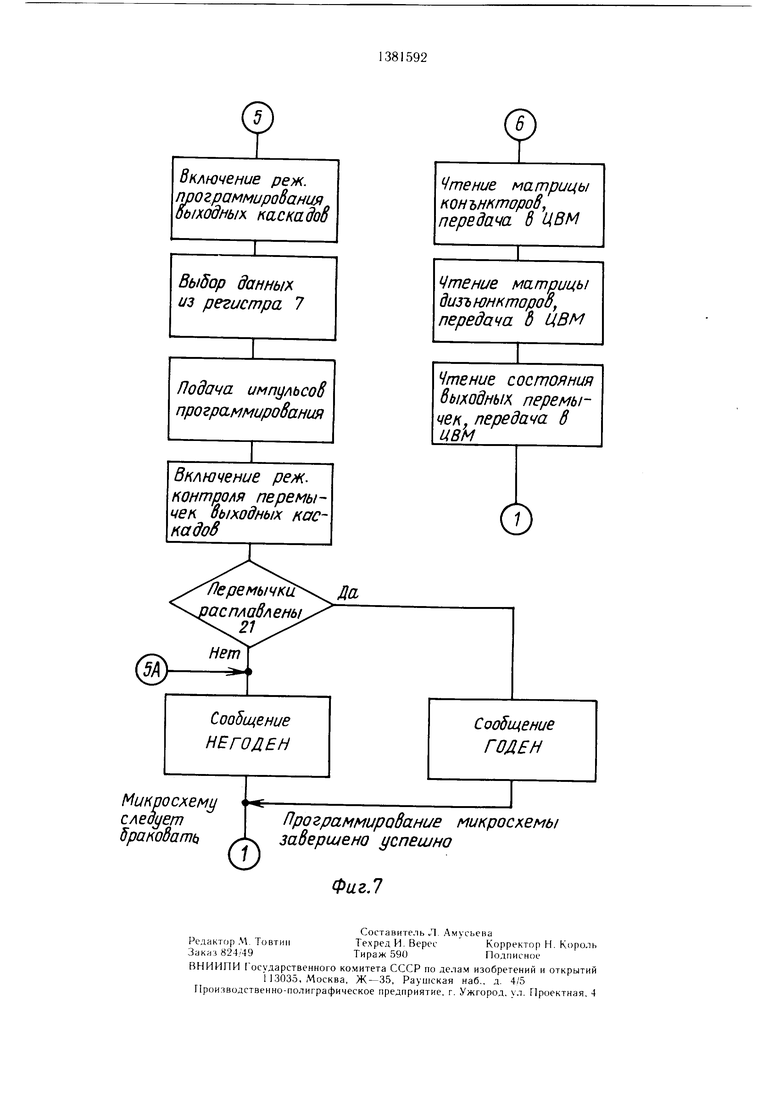

На фиг. 1 дана структурная схема устройства; на фиг. 2 - то же, схема блока формирования напряжений; на фиг. 3-7 - алгоритм работы устройства.

Устройство содержит блок 1 формирования напряжения, первый 2 и второй 3 компараторы, первый 4, второй 5, третий 6, четвертый 7 и пятый 8 регистры, первый 9 и второй 10 блоки ключей, источник 11 опорного напряжения, первый 12, второй 13, третий 14, четвертый 15 и пятый 16 счетчики, первый 17 и второй 18 блоки памяти, первый 19, второй 20, третий 21, четвертый 22 и пятый 23 блоки сравнения, мультиплексор 24, дешифратор 25, контактный разъем 26, цифроаналоговый преобразователь 27, шину 28 данных и шину 29 управления.

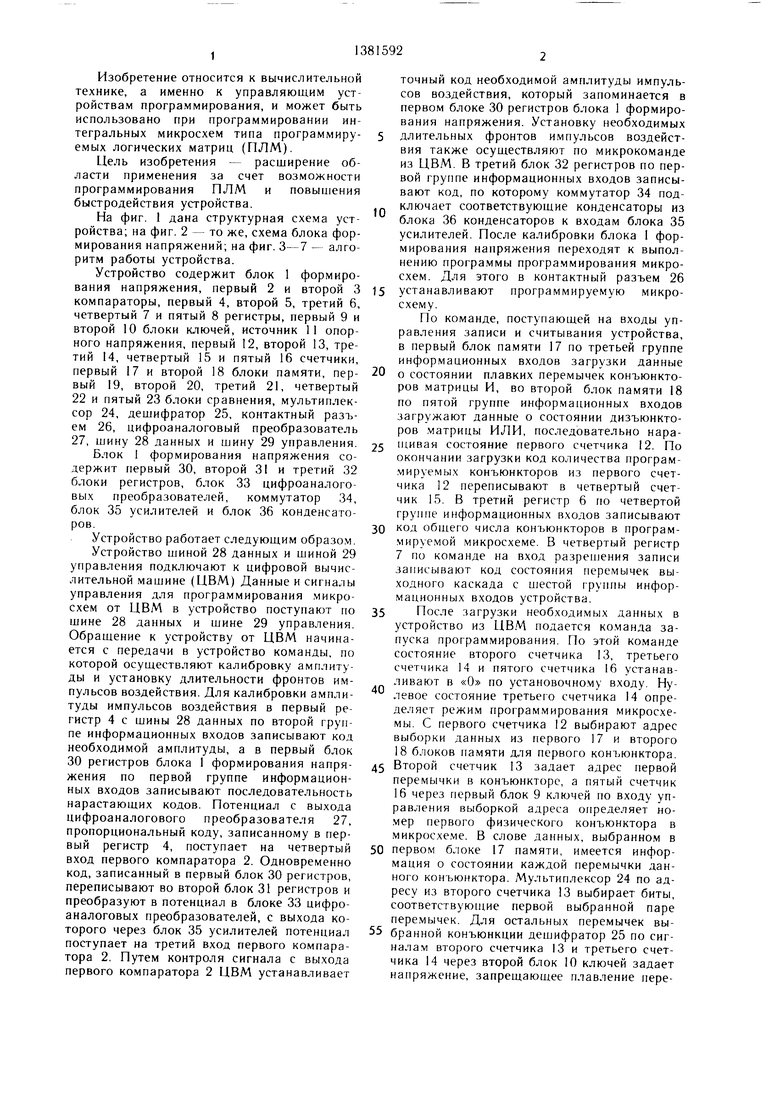

Блок 1 формирования напряжения содержит первый 30, второй 31 и третий 32 блоки регистров, блок 33 цифроаналого- вых преобразователей, коммутатор 34, блок 35 усилителей и блок 36 конденсаторов.

Устройство работает следующим образом.

Устройство шиной 28 данных и шиной 29 управления подключают к цифровой вычислительной машине (ЦВМ) Данные и сигналы управления для программирования микросхем от ЦВМ в устройство поступают по шине 28 данных и шине 29 управления. Обращение к устройству от ЦВМ начинается с передачи в устройство команды, по которой осуществляют калибровку амплитуды и установку длительности фронтов импульсов воздействия. Для калибровки амплитуды импульсов воздействия в первый регистр 4 с шины 28 данных по второй группе информационных входов записывают код необходимой амплитуды, а в первый блок 30 регистров блока 1 формирования напряжения по первой группе информационных входов записывают последовательность нарастающих кодов. Потенциал с выхода цифроаналогового преобразователя 27, пропорциональный коду, записанному в первый регистр 4, поступает на четвертый вход первого компаратора 2. Одновременно код, записанный в первый блок 30 регистров, переписывают во второй блок 31 регистров и преобразуют в потенциал в блоке 33 цифро- аналоговых преобразователей, с выхода которого через блок 35 усилителей потенциал поступает на третий вход первого компаратора 2. Путем контроля сигнала с выхода первого компаратора 2 ЦВМ устанавливает

точный код необходимой амплитуды импульсов воздействия, который запоминается в первом блоке 30 регистров блока 1 формирования напряжения. Установку необходимых

длительных фронтов импульсов воздействия также осуществляют по микрокоманде из ЦВМ. В третий блок 32 регистров по первой группе информационных входов записывают код, по которому коммутатор 34 подключает соответствующие конденсаторы из блока 36 конденсаторов к входам блока 35 усилителей. После калибровки блока 1 формирования напряжения переходят к выполнению программы программирования микросхем. Для этого в контактный разъем 26

устанавливают программируемую микросхему.

По команде, поступающей на входы управления записи и считывания устройства, в первый блок памяти 17 по третьей группе информационных входов загрузки данные

0 о состоянии плавких перемычек конъюнкто- ров матрицы И, во второй блок памяти 18 по пятой группе информационных входов загружают данные о состоянии дизъюнкто- ров матрицы ИЛИ, последовательно нара5 пшвая состояние первого счетчика 12. По окончании загрузки код количества програм- мируемы.х конъюнкторов из первого счетчика 12 переписывают в четвертый счетчик 15. В третий регистр 6 по четвертой группе информационных входов записывают

0 код общего числа конъюнкторов в програм- .мируемой микросхеме. В четвертый регистр 7 по команде на вход разрешения записи записывают код состояния перемычек выходного каскада с шестой группы информационных входов устройства.

5 После загрузки необходимых данных в устройство из ЦВМ подается ко.манда запуска программирования. По этой команде состояние второго счетчика 13, третьего счетчика 14 и пятого счетчика 16 устанавливают в «О по установочному входу. Нулевое состояние третьего счетчика 14 определяет режим программирования микросхемы. С первого счетчика 12 выбирают адрес выборки данных из первого 17 и второго 18 блоков памяти для первого конъюнктора.

5 Второй счетчик 13 задает адрес первой перемычки в конъюнкторе, а пятый счетчик 16 через первый блок 9 ключей по входу управления выборкой адреса определяет но- .мер первого физического конъюнктора в микросхе.ме. В слове данных, выбранном в

0 первом блоке 17 памяти, имеется информация о состоянии каждой перемычки данного конъюнктора. Мультиплексор 24 по адресу из второго счетчика 13 выбирает биты, соответствующие первой выбранной паре перемычек. Для остальных перемычек вы5 бранной конъюнкции дешифратор 25 по сигналам второго счетчика 13 и третьего счетчика 14 через второй блок 10 ключей задает напряжение, запрещающее плавление пере0

мычек. По сигналу второго регистра 5, поступающему на вход режима блока 1 формирования напряжения, он задает импульс возмущения на выбранную перемычку программируемой микросхемы. Последовательно по сигналам второго счетчика 13 задаются импульсы воздействия на все остальные перемычки выбранного конъюнктора. По сигналу второго регистра 5 первый блок 9 ключей подключает программируемую конъюнкцию к первому входу второго компаратора 3, на втором входе которого действует сигнал с выхода источника 11 опорного напряжения. Результат сравнения с выхода второго компаратора 3 поступает в пятый регистр 8. С выхода пятого регистра 8 код состояния программируемой конъюнкции поступает на второй вход второго блока 20 сравнения и сравнивается в нем с кодом с выхода первого блока памяти. 17. Если какую-либо перемычку в программируемой конъюнкции не удалось расплавить и в микросхеме имеются свободные конъюнкторы. Эту конъюнкцию необходимо исключить. Для этого в четвертом блоке 22 сравненияпроверяют сохранились Ли целыми обе перемычки для любой входной переменной. Если в программируемой конъюнкции для какой-нибудь входной переменной остались обе перемычки целыми, то данный конъюнктор никогда не будет выбран и его можно оставить. Если в программируемой конъюнкции нет ни одной пары целых перемычек, то этот конъюнктор необходимо исключить. Для этого необходимо расплавить все перемычки дизъюнкто- ров для выбранного конъюнктора.

Если это не удалось сделать, необходимо браковать данную микросхему. Если удалось исключить незапрограммированную конъюнкцию и в микросхеме имеются свободные конъюнкторы, эти же данные размещают в другом конъюнкторе. Для этого в пятом блоке 23 сравнения сравнивают код количества программируемых конъюнкто- ров с выхода четвертого счетчика 15 с кодом общего количества конъюнкторов в микросхеме с выхода третьего регистра 6. При наличии свободных конъюнкторов сигнал с выхода пятого блока 23 сравнения по второму контрольному выходу поступает в ЦВМ. Из ЦВМ по установочному входу содержимое пятого счетчика 16 наращивают на единицу. По адресу из пятого счетчика 16 первый блок ключей 9 выбирает очередной конъюнктор и данные о состоянии перемычек из первого блока памяти 17 по прежнему адресу, заданному из первого счетчика 12, заносят в программируемую микросхему. Результат программирования сравнивают во втором блоке 20 сравнения.

Если программирование конъюнкторов прощло успещно, по сигналу второго блока сравнения 20 с второго контрольного выхода поступающего в ЦВМ, ЦВМ переводит

0

устройство в режим программирования перемычек дизъюнкторов. Пятый счетчик 16 через второй блок 10 ключей задает код физического конъюнктора. По сигналу из второго счетчика 13 третий счетчик 14 переводит второй регистр 5 в режим программирования матрицы ИЛИ. Данные о состоянии перемычек программируемых дизъюнкторов по команде из второго регистра 5 поступа0 ют в микросхему через первый блок 9 ключей из второго блока 18 памяти по адресу, заданному с выхода первого счетчика 12. По сигналу с первого выхода второго регистра 5 блок I формирования напряжений 1 задает на выбранную перемычку програм.мируемого дизъюнктора импульс воздействия. В первом блоке 19 сравнения сравнивают код состояния перемычек запрограммированных дизъюнкторов с кодом с выхода второго блока 18 памяти. Если какую-нибудь перемычку в программируемых дизъюнкто- рах не удалось расплавить и имеются свободные конъюнкторы, устройство заносит информацию по другому адресу. Если удалось расплавить нужные перемычки дизъюнкторов, переходят к программированию

5 следующего конъюнктора. Для этого увеличивают на единицу содержимое первого счетчика 12 и содержимое пятого счетчика 16, а третий счетчик 14 устанавливают в состояние, соответствующее программированию конъюнкторов.

0

Устройство работает до полного использования предназначенных программированию данных. Сигнал об окончании программирования конъюнкторов и дизъюнкторов с третьего выхода первого счетчика 12 по

5 выходу останова устройства поступает на щину 29 управления и далее в ЦВМ. Из ЦВМ на шину 29 управления поступает команда, по которой устройство переходит в режим программирования перемычек вы ходных каскадов. Информация о состоянии перемычек выходных каскадов поступает с выхода четвертого регистра 7. Контроль состояния программируемых перемычек выходных каскадов производят в третьем блоке 21 сравнения. Если какая-либо перемычка

5 выходного каскада оказалась не расплавленной, микросхему бракуют. После окончания программирования в пятом регистре 8 записано состояние запрограммированной микросхемы. По команде из ЦВМ содержимое пятого регистра 8 по седьмому конт0 рольному выходу считывается в ЦВМ. Эти данные используют для определения состояния микросхемы до программирования и после программирования или при копировании записанной в микросхеме информации. При программировании свободных

5

ячеек в запрограммированной микросхеме в первый счетчик 12 по седьмой группе информационных входов из ЦВМ записывают адреса свободных ячеек в микросхеме и

далее устройство работает как было описано выше.

Использование предлагаемого изобретения позволяет расширить область применения и повысить производительность при массовом программировании или копировании ПЛМ.

Формула изобретения

Устройство для программирования микросхем памяти, содержащее блок формирования напряжений, первый и второй компараторы, первый и второй регистры, цифро- аналоговый преобразователь, первый блок ключей, источник опорного напряжения, выход которого подключен к второму входу второго компаратора, первый вход которого соединен с выходом первого блока ключей и является первым программируюш.им выходом устройства, вход режима первого блока ключей соединен с вторым выходом второго регистра, первый выход которого соединен с входом режима блока формирования напряжения, первый выход которого соединен с вторым входом первого компаратора и является входом разрешения программирования устройства, второй выход - с третьим входом первого компаратора и входом напряжения первого блока ключей, второй вход блока формирования напряжения является входом установки и записи устройства, группы информационных входов блока формирования напряжения и первого регистра являются первой и второй группой информационных входов устройства, входы управления записью первого и второго регистров являются первым и вторым входами разрешения записи устройства, первый вход первого компаратора является входом разрешения выдачи устройства, а выход - первым контрольным выходом устройства, четвертый вход первого компаратора соединен с выходом цифроаналогового преобразователя, вход которого соединен с выходом первого регистра, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности программирования програ ймирования логических матриц и повышения быстродействия устройства, в него введены пять счетчиков, пять блоков сравнения, три регистра, два блока памяти, мультиплексор, второй блок ключей и дешифратор, первый и второй входы которого соединены соответственно с первыми выходами второго и третьего счетчиков, вторые выходы которых соединены соответственно с входами управления выборкой мультиплексора и информационным входом второго регистра, выходы мультиплек

5

сора, дешифратора и третий выход второго регистра соединены с соответствующими информационными входами второго блока ключей, выход которого является вторым программирующим выходом устройства, а вход напряжения соединен со вторым выходом блока формирования напряжения, третий выход второго счетчика соединен с информационным входом третьего счетчика, информационный вход мультиплексора соединен с выходом первого блока памяти и с первым входом второго блока сравнения, группа информационных входов первого блока памяти является третьей группой информационных входов устройства, информационг ные входы третьего регистра являются четвертой группой информационных входов устройства, адресные входы первого и второго блоков памяти соединены с первым выходом первого счетчика, второй выход которого соединен с информационным входом четверто0 го счетчика, установочные входы счетчиков являются установочными входами устройства, третий выход первого счетчика является выходом останова устройства, выходы четвертого счетчика и третьего регистра соедииены соответственно с первым и вторым входами пятого блока сравнения, выход которого является вторым контрольным выходом устройства, выход пятого счетчика соединен с входами управления выборкой адреса тервого и второго ключей, второй вход втоQ рого блока сравнения соединен с выходом пятого регистра и входом четвертого блока сравнения, выходы второго и четвертого блоков сравнения являются третьим и четвертым контрольными выходами устройства, выход второго компаратора соединен с ин5 формационным входом пятого регистра и с первыми входами первого и третьего 6vioKOB сравнения, вторые входы которых соединены соответственно с выходами второго блока памяти и с первым информационным входом первого блока ключей, выходом чет0 вертого регистра и вторым информационным входом первого блока ключей, выходы первого и третьего блоков сравнения являются соответственно пятым и шестым контрольными выходами устройства, вход разре, шения блоков памяти являются входами управления записи и считывания устройства, выходы пятого регистра являются седьмым контрольным выходом устройства, информационные входы второго блока памяти, четвертого регистра и первого счетчика явля0 ются пятой, шестой и седьмой группами информационных входов устройства, входы управления записью с третьего по пятый регистры являются соответственно третьим, четвертым и пятым входами разрешения записи устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программатор | 1986 |

|

SU1439677A1 |

| Устройство для измерения угловых перемещений | 1986 |

|

SU1392350A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАТРИЦЫ НЕПОЛНОГО ПАРАЛЛЕЛИЗМА | 2009 |

|

RU2421804C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1989 |

|

RU2047920C1 |

| Стабилизатор переменного напряжения | 1982 |

|

SU1026123A1 |

| УСТРОЙСТВО ВЫПОЛНЕНИЯ ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2288500C1 |

| Устройство для психологических исследований | 1989 |

|

SU1621883A1 |

Изобретение относится к вычислительной технике, а именно к управляющим устройствам программирования, и может быть использовано при программировании интегральных микросхем типа программируемых логических матриц (ПЛМ). Целью изобретения является расширение области применения за счет обеспечения возможности Программирования ПЛМ и повышения быстродействия устройства. Поставленная цель достигается за счет введения пяти счетчиков 12-16, пяти блоков 19-23 сравнения, трех регистров 6, 7 и 8, двух блоков 17 и 18 памяти, мультиплексора 24, второго блока 10 ключей и дешифратора 25. 7 ил.

Прием Koda состгч- ния Sbixodai f pt - гистр 1

пшрослемы mnnmj

Прием слаба nwa ний конъюнктпр. паня г б 17

Прием CAoSo сое -юя ния дизъюнитср S 1 К память 18.

Нет

ФигЗ

CSpoc счетчика 16 (00/

c femwнoff 11J (00)

BbiSop daHHbi f. для прогр. (онъюнктора

12 - /7- 2

8ы$ор нонъюнкпюра

16- 9-26

Вы5ор перемычки. J3

Вк/ ючение реж. проер. конъюнктора 5.1

Подача импульса программирования 6 1

Выключение реж. прогр. конъюнкто- ра 5,1

Включение режима контроля перемычек конъюнктора ,7

Нет

Счетчик /J /Л-/

Нет /tovj/flwr- тор запрограмми ю8ан

Ш

ФигМ

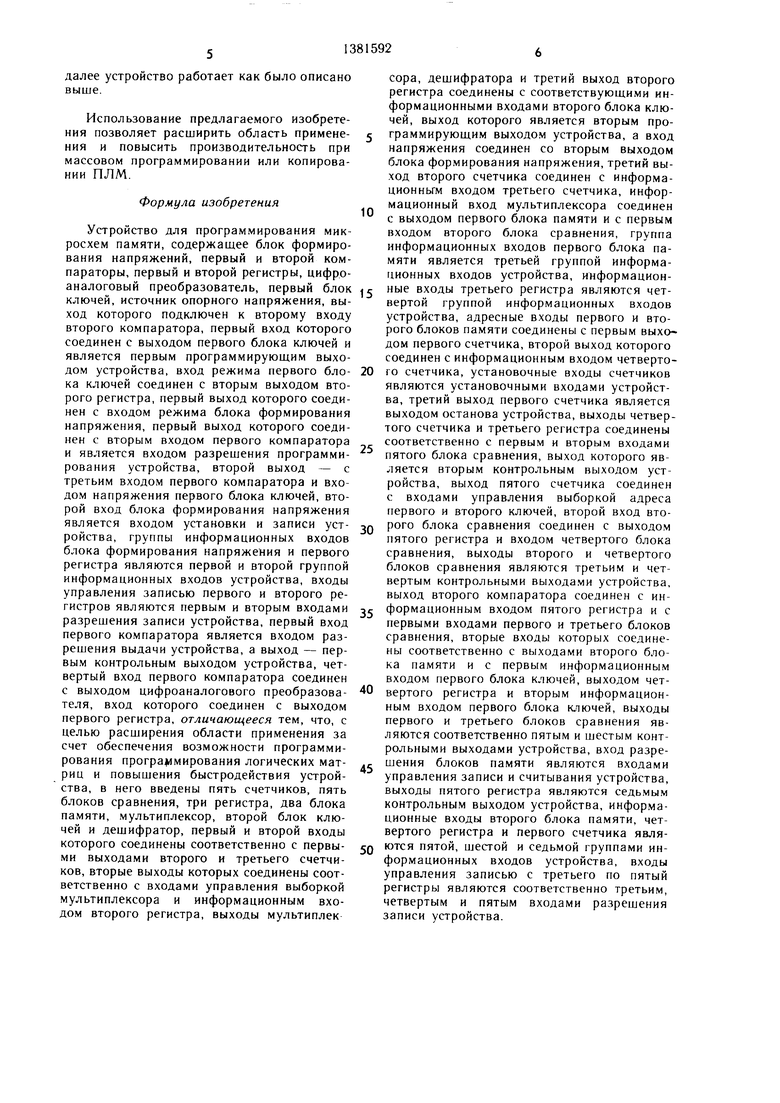

Вы5ор данных для прогр. дизъюнктороб /2

Выдор конъюнктора

миеВы5ор дизъюнмтора

Включение реж. прогр. дизъюннто- ро8 J,;

Подача импульса программиробания 6 1

Выключение реж. прогр. дизъюнкто- poS 5,1

Включение реж. контроля перемычек дизъюнктороб 5i I

Нет

Счетчики. 12 12- J 16 16 + 1

Нет

Программирование матриц И и ИЛИ закончено успешно

Фаг. 5

Счепт ик 75 /5-h /

Нет Имеются

Свободные конънш торы 23

Имеется пара целых пе- оемычек 22,

конъюнктора

Вилнзчение режима программирования диэюонктороб 5,1

Плавятся все перемычки дизнзнк- торов

Да

Фиг. 6

Дедзектный конънктор исключен

Счетчик. /5 /5 + /

Перемд к 2д) с/ едующецу свободному конъюктору

Исклнгчение десректного конъюнктора недозможно

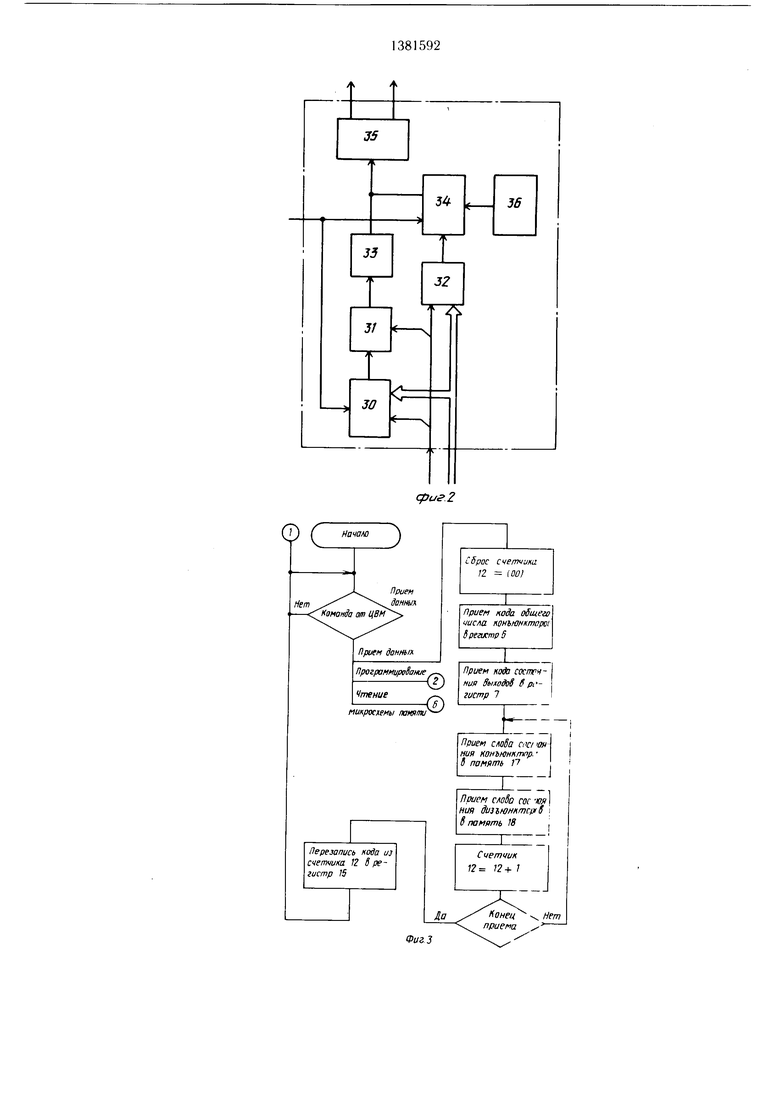

Включение реж. программирования оышныу. каскадоВ

Выбор данныу. из регистра 7

Подача импульсоВ программирования

Включение реж. контроля перемычек выходных каскадов

Сообщение НЕГОДЕН

Чтение, матрицы конънкторов, передача 8 ЦВМ

Чтение матрицы дизъюнктороо, передача б ЦВМ

Чтение состояния вы}(одны перемычек, передача в ЦВМ

Сообщение ГОДЕН

| Устройство для программирования микросхем памяти | 1981 |

|

SU1005183A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-03-15—Публикация

1986-03-10—Подача