SS (/

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое устройство формирования задержки и длительности импульсов | 1977 |

|

SU639381A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Многоканальный измеритель временных характеристик последовательности дискретных сигналов | 1987 |

|

SU1442971A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для обработки сообщений | 1990 |

|

SU1803919A1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| Устройство для измерения экстремумов временных интервалов | 1985 |

|

SU1282318A1 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Устройство для формирования пачки импульсов | 1983 |

|

SU1193784A1 |

| Устройство для ввода информации | 1988 |

|

SU1585790A1 |

Изобретение относится к вычислительной технике. Устройство с пн- формах ионным входом 1 и тактовыми входами 6,11 содержит группы элементов И 2-5, регистр 7, выполненный на триггерах 8, элемент И 9, элемент PfflH 10, счетчнк 12. Использование узлов со статической установкой обеспечивает сокращение аппаратурных затрат. 2 ил.

Фие.1

/3

Изобретение относится к вьгчнсли- тельнор технике и может быть использовано в контрольной аппаратуре для проверки ввода, обработки и передачи информации.

Цель изобретения - сокращение аппаратурных затрат.

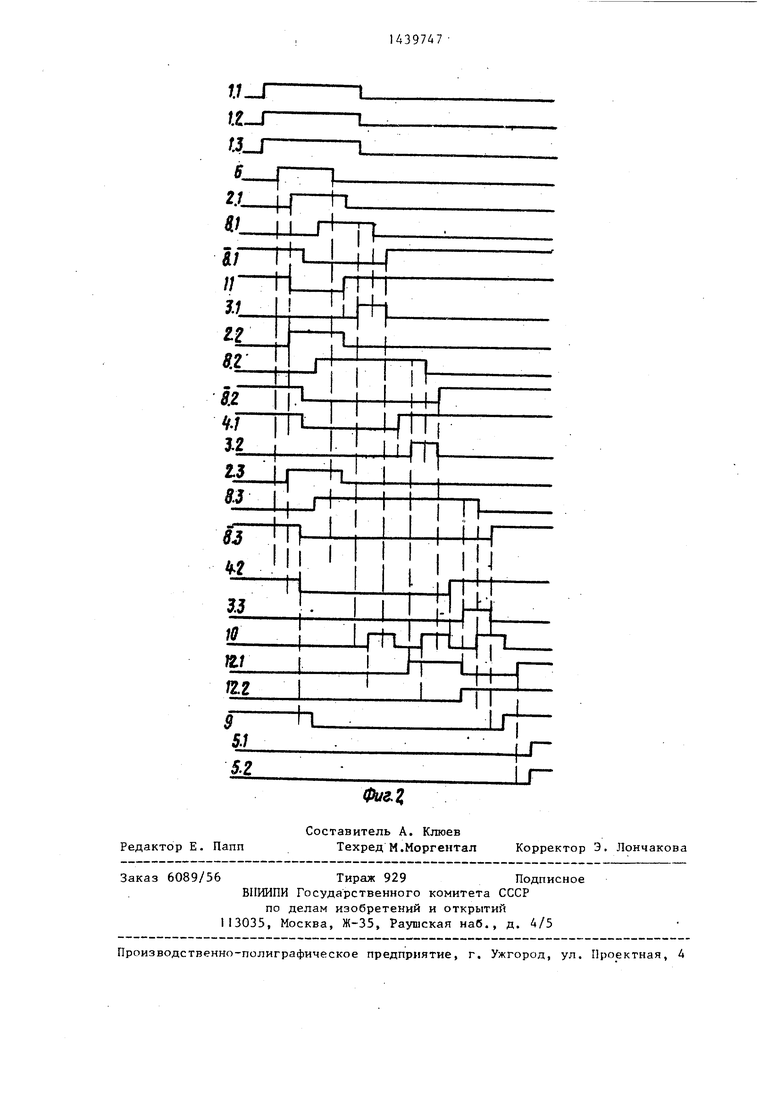

На фиг. 1 представлена схема устройства для свертки кода числа по мо- дулю, на фиг. 2 - временная диаграмма работы устройства.

Устройство (фиг. 1) имеет информационный вход.1 с первой по четвертую группы элементов И 2-5, первьм тактовый вход 6, регистр 7, содержа щий триггеры 8, элемент И 9, элемент ИЛИ 10, второй тактовый вход 1 , счечик 12 и выход 13.

Устройство работает следующим об- разом.

В исходном состоянии счетчик I2 и триггеры 8 регистра Л сброшены, на и прямых выходах присутствуют уровни логического нуля, а на инверсных выходах триггеров 8 -логической единицы.На информационном входе 1 представлены нулевые логические уровни, так как отсутствует код преобразуемого числа. На входе 6 устройства еще нет и -{пульса и присутствует уровень логического нуля. Поэтому на обоих входах всех элементов И 2 первой группы нулевые уровни, Что обуславливает уровни логических нулей и на их выходах и, следовательно, отсутствие сигнала установки на установочных входах триггеров В. На входе 11 устройства присутствует логическая единица и уровни логической единицы на инверсных выходах Bcejt триггеров 8 предопределяют наличие сигналов разрешения сбр са всех триггеров 8 в виде уровней логической единицы на выходах всех элементов И 4 третьей грзшпы и на вторых входах всех элементов И 3 второй группы. Однако нулевые логически уровни с прямых выходов триггеров 8, поступающие на первые входы этих элементов, обуславливают нулевые логические уровни на их выходах и на входах сброса триггеров 8, что означает отсутствие сброса. Нулевые логические уровни на вьрсодах элементов И 3 второй группы предопределяют уровень логического нуля на йыходе элемента ИЛИ 10 и на счетном входе счетчика 12, что обеспечивает сохранение этим счетчиком состояния

5

Q

0

5 дс

0

5

0

0

5

сброса и нулевых уровней на его выходах. Единичные логические уровни с инверсных выходов триггеров В, поступая на входы элемента И 3, обуславливают на его выходе уровень логической единицы, который по вторым входам создает условия для открытия элементов И 5 четвертой группы. Однако на выходах счетчика 12 находятся нулевые логичес ие уровни, что предопределяет нулевые логические уровни на первых входах этих элементов и на их выходах, а значит и на выходе 13 устройства.

Для подготовки устройства к работе необходимо установить на информационном входе 1 устройства закодированный логическими уровнями код преобразуемого числа, что не вызывает каких-либо изменений состояний выходов элементов устройства. Работа устройства начинается с подачи на вход 6 устройства импульса, по длительности не меньшего времени установки триггеров. Поступая на первые входы всех элементов И 2 первой группы, этот импульс совместно с единичными уровнями соответствующих разрядов информационного входа 1,, присутствующими на вторых входах соответствующих элементов И 2 группы, вызывает с задержкой на время переключения появление уровня логической единицы на выходах этих элементов и на входах установки соответствующих триггеров 8. Это в свою очередь вызывает установку в единичное состояние соответствующих триггеров В с задержкой на время установки, равное периоду переключения двух логических элементов. Общая задержка переключения триггеров 8 относительно переднего фронта импульса на входе 6 составляет за счет элементов И 2 первой группы три периода переключения логического элемента. Через один период переключения логического элемента от момента появления импульса на входе 6 устройства на вход 11 устройства подается нулевой логический уровень, который с задержкой еще на один период переключения логического элемента за счет элементов И 4 третьей группы блокирует по второму входу элементы И 3 второй группы и предотвращает выработку сигналов сброса триггеров 8. Сброс первого разряда регистра 7 будет блокирован через

один период переключения элемента от переднего фронта импульса на входе 6 устройства. Для остальных разрядов регистра 7 блокировка сброса возникает через два периода переключения логического элемента за счет соответствующих элементов И 4 третьей группы.

Таким образом, сигналы самосброса триггеров 8 могут возникнуть лишь по истечении трех периодов переключения логических элементов за счет задержки элементов И 2 первой группы и триггеров 8, а уровни, блокирующие сброс, формируются уже через два таких периода, что гарантирует надежную установку триггеров 8 регистра 7. Благодаря блокировке импульсы самосброса триггеров 8 через элемент ИЛИ 10 не поступают на счетный вход счетчика 12, а на его установочный вход в течение всего периода действия импульса на входе 6 устройства действует сигнал установки. Поэтому на протяжении всего периода действия импульса на входе 6 устройства на триггерах 8,регистра 7 сохраняется код преобразуемого числа, а счетчик 12 остается в нулевом состоянии. Так как в коде преобразуемого числа имеется хотя бы одна единица, то на инверсном выходе по крайней мере одного триггера 8 появляется нулевой логический уровень, вызывающий уровень логического нуля на вьпсоде элемента И 9, который по вторым входам блокирует элементы И 5 четвертой группы до момента сброса последней единицы в регистре 7 и не допускает прохождение информации через упомянутые элементы на выход 13 устройств

После завершения импульсов на входе 6 устройства нулевой уровень на первых входах элемента И 2 первой группы вызывает с задержкой в один период переключения логического элемента появление уровней логического нуля на их выходах и прекращение действия сигнала установки на установоч Hbix входах триггеров 8. На вход 11 устройства с задержкой в один период .переключения логического элемента относительно входа 6 устройства и соответственно на входы элементов И 4 третьей группы и первого элемента И второй группы поступает уровень логической единицы. Если первый триггер 8 установлен в единичное состоя

10

15

20

25

39747

ние, то уровень логической единицы с его прямого выхода присутствует на первом входе первого элемен га И 3 второй группы и при появлении на его втором входе единичного логического уровня через период переключения логического элемента на выходе этого элемента И 3 появляется уровень логической единицы. Он поступает на вход сброса первого триггера 8 и с задержкой на время переключения триггера от входа сброса до его прямого выхода, равной периоду переключения логического элемента, вызывает на этом выходе появление нулевого логического уровня. Этот уровень, поступив на первый вход первого элемента И 3 второй группы, вызьшает с задержкой на время переключения этого элемента на его выходе и на входе сброса первого триггера 8 уровень логического нуля.

Таким образом, импульс длительностью в два периода переключения логического элемента появляется на входе сброса первого триггера 8 с задержкой от момента окончания импульса на входе 6 устройства, равной упомянутому времени переключения этого триггера от входа сброса до его прямого выхода. Одновременно импульс сброса триггера 8 через элемент ИЛИ 10 с задержкой на время его переключения поступает на счетный вход счетчика 12, переводя его по переднему фронту в следующее состояние, и на соответствующий вход элемента И 9, не снимая блокировки по вторым входам элементов И 5 четвертой группы.

После завершения сброса первого триггера 8 единичный логический уровень с его инверсного выхода поступает на первый вход первого элемента И 4 третьей группы, на остальных вхо- с дах которого уже установлены уровни логической единицы, и с задержкой на время его переключения вызьюает на выходе этого элемента единичный логический уровень . Этот уровень поступает на второй вход второго элемента И 3 второй группы, инициируя процесс сброса второго триггера 8, и на второй вход второго элемента И 4 третьей группы, готовя условия для сброса третьего триггера 8. Если в момент поступления разрешения сброса на второй вход второго элемента И 3 второй группы первый триггер 8 был в нулевом состоянии, то уровень логического ну30

35

40

50

55

ля е его прямого выхода, действуя на первом входе второго элемента И 3 второй группы, блокирует выдачу этнм элементом сигнала сброса на этот триггер, а единичный логический уровень с его инверсного вькода по первому входу второго элемента И 4 третьей группы готовит условия для разрешения сброса следующего триггера 8.Если второй триггер 8 в момент поступления разрешения сброса был в единичном состоянии, то уровень логической единиды с его прямого вькода уже действовал на первом входе второго элемента И 3 второй группы. Поэтому при поступлении уровня логической единицы с выхода первого элемента И 4 третьей группы на второй вход второго элемента И 3 второй группы на выходе последнего с задержкой на время его переключения появляется единичный уровень, которьй запускает процесс сброса второго триггера 8. Процесс сброса этого триггера аналогичен описанному процессу сброса первого триггера 8.

Процесс последовательного сброса Триггеров 8, сопровождаемьй подсчетом импульсов сброса на счетчике 12, продолжается до тех пор, пока не будет сброшен последний триггер 8 регистра 7. Тогда единичные уровни с инверсных выходов всех триггеров поступают на все входы элемента И 9 и через период переключения этого элемента единичный уровень с выхода этого элемента поступает на вторые входы всех элементов И 5 четвертой группы, разрешив прохождение через эти элементы уровней с выходов счетчика 12 на выход 13 устройства. После этого состояние выходов элементов

10

15

20

Формула изобретения

Устройство для свертки кода числа по модулю содержащее с первой по четвертую группы элементов И, регистр счетчик, элемент И и элемент ИЛИ, при чём первые входы элементов И первой группы объединены и соединены с первым тактовым входом устройства, входы разрядов информационного входа которого соединены с вторыми входами соответствующих элементов И первой груп пы, выходы которых подключены к входам установки триггеров соответствующих разрядов регистра, прямые выходы которых соединены с первыми входами соответствующих элементов И второй группы, выходы которых подключены к входам сброса триггеров соответствующих разрядов регистра и к соответствующим входам элемента ИЛИ, выход которого соединен со счетным входом счетчика, инверсные выходы триггеров разрядов регистра соединены с соответствующими входами элемента И и с первьши входами соответствующих элементов И третьей группы, выходы которых соединены с вторыми входами 30 последующих элементов И второй группы, выход каждого предыдущего Элемента И третьей группы соединен с вторым входом последующего элемента И третьей группы, выходы разрядов счетчика соединены с первыми входами элементов И четвертой группы, вторые входы которьпс объединены и подключены к выходу элемента И, выходы элементов И четвертой группы являются выходом устройства, о т 25

35

40

личающееся тем, что.

с целью сокращения аппаратурных затрат, второй тактовый вход устройства соединен с установочным входом счет- устройства не меняется до подачи еле- 45 чика, с вторыми входами первых эле- дукицего импульса на вход 6 устройства, ментов И второй и третьей групп и с при поступлении которого цикл рабо- третьими входами элементов И треть- ты устройства повторяется.ей группы, кроме первого.

5

0

Формула изобретения

Устройство для свертки кода числа по модулю содержащее с первой по четвертую группы элементов И, регистр, счетчик, элемент И и элемент ИЛИ, причём первые входы элементов И первой группы объединены и соединены с первым тактовым входом устройства, входы разрядов информационного входа которого соединены с вторыми входами соответствующих элементов И первой группы, выходы которых подключены к входам установки триггеров соответствующих разрядов регистра, прямые выходы которых соединены с первыми входами соответствующих элементов И второй группы, выходы которых подключены к входам сброса триггеров соответствующих разрядов регистра и к соответствующим входам элемента ИЛИ, выход которого соединен со счетным входом счетчика, инверсные выходы триггеров разрядов регистра соединены с соответствующими входами элемента И и с первьши входами соответствующих элементов И третьей группы, выходы которых соединены с вторыми входами 0 последующих элементов И второй группы, выход каждого предыдущего Элемента И третьей группы соединен с вторым входом последующего элемента И третьей группы, выходы разрядов счетчика соединены с первыми входами элементов И четвертой группы, вторые входы которьпс объединены и подключены к выходу элемента И, выходы элементов И четвертой группы являются выходом устройства, о т 5

35

0

личающееся тем, что.

с це

| Устройство для формирования остатка по произвольному модулю от числа | 1983 |

|

SU1105895A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-11-23—Публикация

1987-05-25—Подача