Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано при построении алгоритмически распределенных устройств микропрограммного управления вычислительных и управляющих систем высокой производительности, проектируемых на базе однотипных БИС (СБИС) и реализующих параллельные алгоритмы обработки информации.

Известно микропрограммное устройство управления, содержащее блок постоянной памяти, блок формирования адреса микрокоманд, регистр микрокоманд, регистр начала микропрограммы, регистр конца микропрограммы, дешифратор адреса, триггер управления, генератор импульсов, четыре элемента ИЛИ, группу из N-1 элементов ИЛИ, блок элементов ИЛИ, пять элементов И, два блока элементов И, элемент задержки, триггер конца микропрограммы, триггер начала микропрограммы, пять одновибраторов, N-1 коммутатор и элемент ИЛИ-НЕ (а. с. N 1168936 СССР, кл. G 06 F 9/22; опубл. 23.07.85, БИ N 27).

Недостатком этого устройства является значительное число внешних входов/выходов, используемых для организации взаимодействия с другими аналогичными устройствами (приема и выдачи адресов передачи управления), что обуславливает резко ограниченную наращиваемость формируемых на его основе управляющих систем, а следовательно, и узкую область применения устройства.

Наиболее близким к предлагаемому устройству по технической сущности является микропрограммное устройство управления с контролем, включающее блок постоянной памяти, блок формирования адреса микрокоманд, регистр микрокоманд, группу из N регистров записи (где N - количество автономных микропрограмм), коммутатор управления счетчиком, счетчик выборки, дешифратор выборки, четыре группы из N шинных формирователей, блок управления пуском, блок управления остановом, группу из N элементов задержки, группу из N коммутаторов записи, счетчик опроса, дешифратор опроса, N+1 блоков элементов И, 2N+1 элементов И, группу из N элементов ИЛИ-НЕ, элемент ИЛИ, триггер режимов работы, триггер управления, генератор импульсов (а.с. N 1142832 СССР, кл. G 06 F 9/22; G 06 F 11/00; опубл. 28.02.85, БИ N 8).

Недостатком указанного устройства является отсутствие возможности опроса состояния (завершены/не завершены) параллельных участков микропрограмм, закрепленных за другими аналогичными устройствами в составе мультимикропрограммной управляющей системы, и, как следствие, узкая область его применения.

Технической задачей изобретения является расширение области применения устройства на основе организации возможности опроса состояния других аналогичных устройств и синхронизации завершения произвольных групп параллельных участков микропрограмм при функционировании устройства в составе мультимикропрограммной управляющей системы.

Техническая задача решается тем, что модуль мультимикропрограммной системы, содержащий блок памяти микропрограмм, блок формирования адреса микрокоманд, регистр микрокоманд, N регистров передачи управления, триггер управления, первый генератор тактовых импульсов, счетчики выборки и опроса, первый триггер, дешифраторы выборки и опроса, схему сравнения, первую и вторую группы из N блоков тристабильных элементов, группу из N элементов ИЛИ-НЕ, первую и вторую группы из N элементов И, с первого по третий элементы И, с первого по третий элементы ИЛИ, группу из N элементов задержки, одновибратор, шину передачи управления и шину синхронизации параллельных участков, причем прямой выход триггера управления соединен с управляющим входом первого генератора тактовых импульсов, первый и второй информационные входы блока формирования адреса микрокоманд являются соответственно входами логических условий и кода операции модуля, информационный выход блока формирования адреса микрокоманд соединен с адресным входом блока памяти микропрограмм, выход которого соединен с информационным входом регистра микрокоманд, выходы адреса и кода логического условия которого подключены к третьему информационному и управляющему входам блока формирования адреса микрокоманд соответственно, выход микроопераций регистра микрокоманд является выходом микроопераций модуля, выход счетчика выборки соединен с входом дешифратора выборки, выходы с первого по N-й которого подключены к первым входам элементов И первой группы с первого по N-й соответственно, выходы которых соединены с входами синхронизации регистров передачи управления с первого по N-й соответственно, прямые выходы которых подключены к информационным входам блоков тристабильных элементов первой группы с первого по N-й соответственно, выходы которых подключены к шине передачи управления, которая соединена с информационными входами блоков тристабильных элементов второй группы с первого по N-й, выходы которых соединены с входами элементов ИЛИ-НЕ группы с первого по N-й соответственно, выход N-го элемента ИЛИ-НЕ группы соединен с первым входом первого элемента И, выход которого подключен к счетному входу счетчика опроса, выход которого соединен с входом дешифратора опроса, выходы с первого по N-й которого подключены к первым входам элементов И второй группы с первого по N-й соответственно, выходы которых соединены с управляющими входами блоков тристабильных элементов первой и второй групп с первых по N-е соответственно, а также с входами элементов задержки группы с первого по N-й соответственно, выходы которых соединены с входами сброса регистров передачи управления с первого по N-й соответственно, выходы элементов ИЛИ-НЕ группы с первого по N-й подключены к вторым входам элементов И второй группы с первого по N-й соответственно, первый вход, второй вход и выход первого элемента ИЛИ соединены с управляющим входом модуля, выходом второго элемента И и входом сброса триггера управления соответственно, дополнительно включает формирователь признака принадлежности, второй генератор тактовых импульсов, счетчик времени ожидания, второй, третий и четвертый триггеры, первый и второй блоки тристабильных элементов, третью группу из N элементов И, элемент ИЛИ-НЕ, элемент И-НЕ, с четвертого по тринадцатый элементы И, с первого по четвертый элементы задержки, линию состояния параллельных участков, причем выход метки передачи управления/инициализации регистров микрокоманд соединен с первыми входами третьего и четвертого элементов И, выходы которых соединены с входом сброса и счетным входом счетчика выборки соответственно, выход управляющей информации регистра микрокоманд подключен к первому входу схемы сравнения, к информационному входу первого блока тристабильных элементов и к информационным входам регистров передачи управления с первого по N-й, инверсные выходы которых соединены с входами элементов И третьей группы с первого по N-й соответственно, выход статуса регистра микрокоманд соединен с первым входом пятого элемента И, выход которого соединен с входом одновибратора, выход которого подключен к входу первого элемента задержки и входу установки второго триггера, инверсный выход которого подключен к управляющему входу второго блока тристабильных элементов, прямой выход второго триггера соединен с управляющим входом первого блока тристабильных элементов, выход которого подключен к шине синхронизации параллельных участков, которая соединена с информационным входом второго блока тристабильных элементов, выход которого подключен к входам элемента ИЛИ-НЕ, адресному входу формирователя признака принадлежности и к второму входу схемы сравнения, первый и второй выходы первого генератора тактовых импульсов подключены к первым входам шестого и седьмого элементов И, выход шестого элемента И соединен с входом синхронизации блока формирования адреса микрокоманд, четвертый информационный вход которого подключен к шине передачи управления, выход седьмого элемента И соединен с входом синхронизации регистра микрокоманд и с входом второго элемента задержки, выход которого соединен с вторым входом третьего элемента И, инверсный выход второго триггера подключен к первому входу элемента И-НЕ, второй вход которого подключен к выходу формирователя признака принадлежности, выход элемента И-НЕ соединен с первым входом второго элемента ИЛИ, выход которого подключен к линии состояния параллельных участков, выход первого элемента задержки соединен со счетным входом второго триггера, а также с первыми входами восьмого и девятого элементов И, вторые входы которых подключены к линии состояния параллельных участков, выходы восьмого и девятого элементов И соединены соответственно с входом установки первого триггера и первым входом третьего элемента ИЛИ, прямой выход первого триггера соединен с управляющим входом второго генератора тактовых импульсов, выход которого соединен со счетным входом счетчика времени ожидания, выход которого подключен к входам десятого элемента И, выход которого подключен к входам сброса первого триггера и счетчика времени ожидания, выходы элементов И третьей группы с первого по N-й подключены к третьему входу третьего элемента И, третий выход первого генератора тактовых импульсов соединен с вторым входом четвертого элемента И, первым входом одиннадцатого элемента И и с входом третьего элемента задержки, выход которого подключен к вторым входам элемента И первой группы с первого по N-й, второму входу первого элемента И и к входу четвертого элемента задержки, выход которого соединен с первым входом двенадцатого элемента И, второй вход и выход которого подключены к N-му выходу дешифратора опроса и к входу сброса счетчика опроса соответственно, выход метки конца участка регистра микрокоманд подключен к первому входу тринадцатого элемента И, второй вход которого соединен с выходом второго элемента задержки, выход тринадцатого элемента И подключен к счетному входу третьего триггера, прямой выход которого подключен к вторым входам шестого и седьмого элементов И, инверсный выход третьего триггера соединен с вторым входом пятого элемента И, третий, четвертый и пятый входы которого соединены соответственно с инверсным выходом четвертого триггера, инверсным выходом первого триггера и с выходом элемента ИЛИ-НЕ, выход схемы сравнения подключен к второму входу второго элемента ИЛИ, выход метки конца микропрограммы регистра микрокоманд соединен с выходом конца микропрограммы модуля и с первым входом второго элемента И, второй вход которого подключен к третьему выходу первого генератора тактовых импульсов, управляющий выход блока формирования адреса микрокоманд подключен к входу установки триггера управления и к второму входу третьего элемента ИЛИ, выход которого подключен к входу установки четвертого триггера, прямой выход которого соединен с вторым входом одиннадцатого элемента И, выход которого соединен с входом установки третьего триггера и счетным входом четвертого триггера, а в блок формирования адреса микрокоманд, включающий шифратор начального адреса, мультиплексор, первый блок элементов ИЛИ, первый элемент ИЛИ и регистр адреса микрокоманды, причем вход шифратора начального адреса является четвертым информационным входом блока формирования адреса микрокоманд, управляющий и информационный входы мультиплексора являются соответственно управляющим и первым информационным входами блока формирования адреса микрокоманд, n-1 старших разрядов третьего информационного входа которого (где n - разрядность адреса микрокоманды) соединены с n-1 старшими разрядами первого входа первого блока элементов ИЛИ, а младший разряд подключен к первому входу первого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом мультиплексора и младшим разрядом первого входа первого блока элементов ИЛИ, вход синхронизации регистра адреса микрокоманды подключен к входу синхронизации блока формирования адреса микрокоманд, а выход является информационным выходом блока формирования адреса микрокоманд, дополнительно введены второй блок элементов ИЛИ, второй элемент ИЛИ, регистр и одновибратор, причем второй информационный вход блока формирования адреса микрокоманд соединен с первым входом второго элемента ИЛИ и первым входом второго блока элементов ИЛИ, выход которого соединен с информационным входом регистра, вход сброса которого соединен с входом синхронизации блока формирования адреса микрокоманд, а выход подключен к второму входу первого блока элементов ИЛИ, выход которого подключен к информационному входу регистра адреса микрокоманды, выход шифратора начального адреса соединен с вторым входом второго блока элементов ИЛИ и вторым входом второго элемента ИЛИ, выход которого соединен с входом одновибратора, выход которого подключен к входу синхронизации регистра и управляющему выходу блока формирования адреса микрокоманд.

Сущность предлагаемого изобретения состоит в следующем.

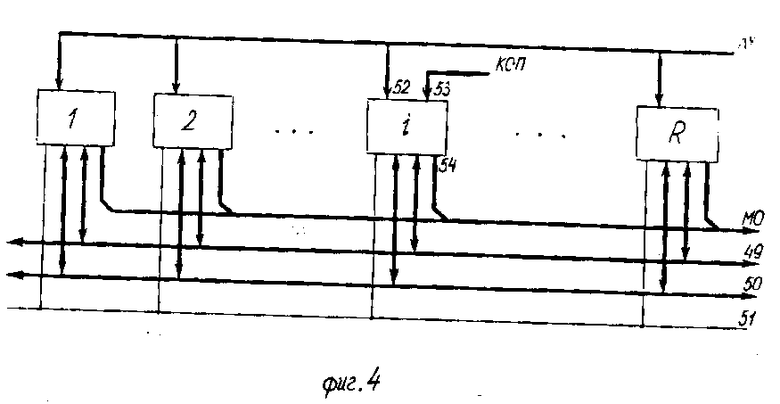

Предлагаемый модуль совместно с другими аналогичными устройствами образует мультимикропрограммную систему (ММПС), которая предназначается для реализации сложных комплексов микропрограмм, предусматривающих как последовательное, так и параллельное выполнение различных микрокоманд, образующих соответственно последовательные и параллельные участки. Каждый модуль реализует некоторое подмножество параллельных и последовательных участков, выделяемых при разбиении (декомпозиции) исходного комплекса микропрограмм.

В процессе выполнения тех или иных участков микропрограмм модули системы могут обмениваться управляющей информацией через соответствующие информационные шины и осуществлять запуск параллельных или последовательных участков, закрепленных за другими модулями, а также производить опрос модулей ММПС с целью определения состояния реализуемых ими параллельных участков. Наряду с инициализацией участков микропрограмм (основных микропрограмм) модули ММПС аналогично прототипу могут выдавать задания на выполнение автономных микропрограмм, стандартных микроподпрограмм, а также инициировать передачу результатов их реализации, при этом в отличие от прототипа шины системы используются только для передачи управляющих сообщений, в то время как данные между операционными устройствами транслируются по собственной шине данных (или через собственную коммуникационную подсистему) управляемой системы (объекта).

Для идентификации участков микропрограмм при их запуске используются специальные признаки (коды), присваиваемые таким образом, что одновременно инициализируемые в соответствии с реализуемым алгоритмом участки (участки, открывающиеся единой вершиной распараллеливания) получают одинаковые признаки, а признаки участков микропрограмм, относящихся к различным вершинам (микрокомандам) распараллеливания, являются различными. Аналогичные признаки применяются и для идентификации автономных микропрограмм и стандартных микроподпрограмм, однако в дальнейшем для упрощения описания между автономными микропрограммами, стандартными микроподпрограммами и участками микропрограмм различий условно не делается.

Процедура параллельных участков состоит в следующем.

Модуль Mi, инициирующий запуск, формирует и выдает на шину ММПС (шину передачи управления) код признака инициализируемых параллельных участков Пs. Данный код одновременно воспринимается всеми остальными модулями ММПС и, если за некоторым модулем Mj, j ≠ i, закреплен участок с признаком Пs, то в соответствии с кодом Пs j-й модуль формирует адрес начала этого участка Аjs (Анач) и начинает выполнение микропрограммы с адреса Аjs, в противном случае запуск модуля Мj не производится.

В отличие от прототипа, где возможность синхронизации завершения различных групп параллельных участков отсутствует, предлагаемый модуль в ходе реализации закрепленного за ним участка микропрограммы может опрашивать состояние других модулей и переходить к выполнению определенных микрокоманд только после завершения требуемых параллельных участков. Для реализации возможности синхронизации параллельных участков (ветвей параллельного алгоритма) все точки слияния различных групп параллельных участков (точки синхронизации) помечаются номерами 1, 2,..., R, где R - число точек синхронизации параллельных участков во всех реализуемых системой микропрограммах (предполагается, что указанные номера и упомянутые выше признаки участков не совпадают). В формат микрокоманд, реализуемых устройством, включается специальное поле, в котором фиксируется код номера точки синхронизации (НТС), закрывающей соответствующий участок микропрограммы. Данное поле заполняется только если соответствующая микрокоманда является последней в реализуемом участке, причем этот участок является параллельным (в противном случае содержимое рассматриваемого поля является нулевым).

Синхронизация окончания параллельных участков осуществляется следующим образом.

Модули ММПС после выполнения соответствующих параллельных участков микропрограммы переходят в состояние ожидания. Один из указанных модулей (например, Мi), считающийся ведущим, выдает на шину системы (шину синхронизации параллельных участков) код НТС Тr, закрывающий выполненный и опрашиваемые участки. Данный код поступает на входы всех остальных модулей и формирует на их выходах сигналы состояния. Формирование сигнала Sk модуля Mk, k≠i, осуществляется согласно следующему правилу.

1. Сигнал состояния Sk приобретает нулевое значение, если за k-м модулем закреплен участок, завершающийся точкой синхронизации Tr, но выполнение этого участка не окончено.

2. Сигнал состояния Sk принимает единичное значение, если за k-м модулем закреплен участок, закрываемый точкой Tr, и, кроме того, этот участок завершен, либо участка, завершающегося точкой Tr и закрепленного за k-м модулем, не существует.

Сигнал состояния ведущего модуля Si является единичным.

Сигналы состояния с выходов модулей ММПС передаются на общую линию состояния параллельных участков и формируют сигнал обобщенного состояния Z. Если хотя бы один из требуемых параллельных участков не завершен (т.е. для некоторого модуля Mt - St = "0"), то имеет место Z="0", иначе Z приобретает единичное значение. Модуль Mi (ведущий) опрашивает состояние уровня сигнала Z на линии состояния параллельных участков и при Z = "0" на некоторое время T освобождает шину ММПС, по истечении которого осуществляет повторный опрос состояния параллельных участков, а при Z = "1" выходит из режима ожидания и возобновляет выполнение микропрограммы.

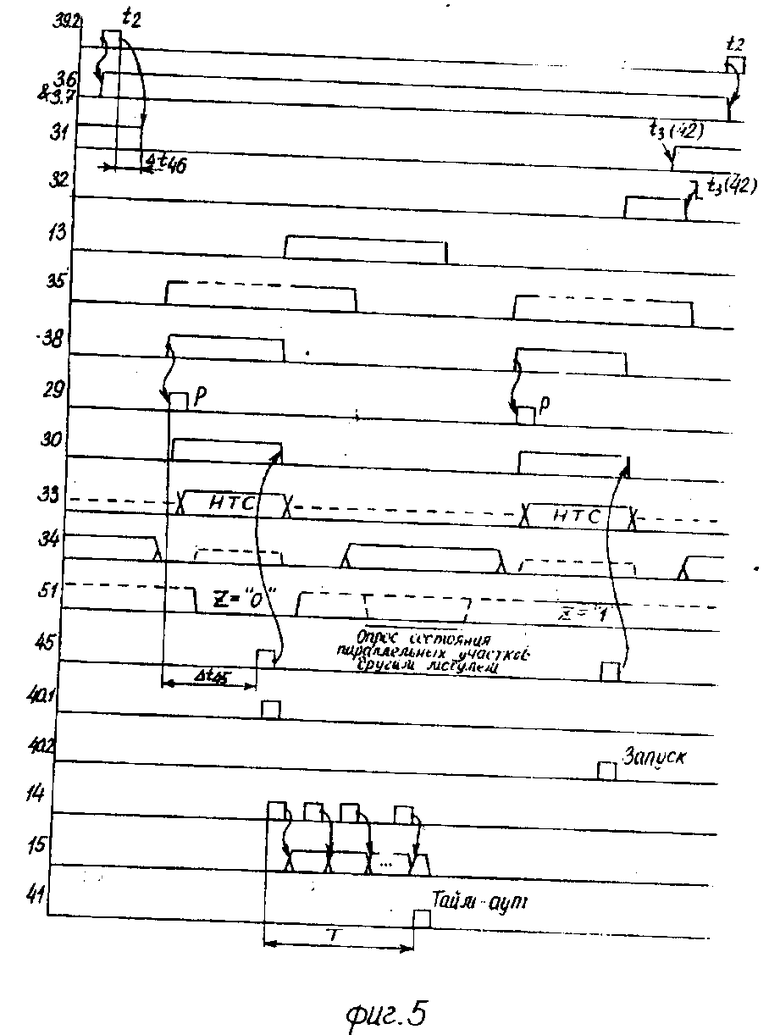

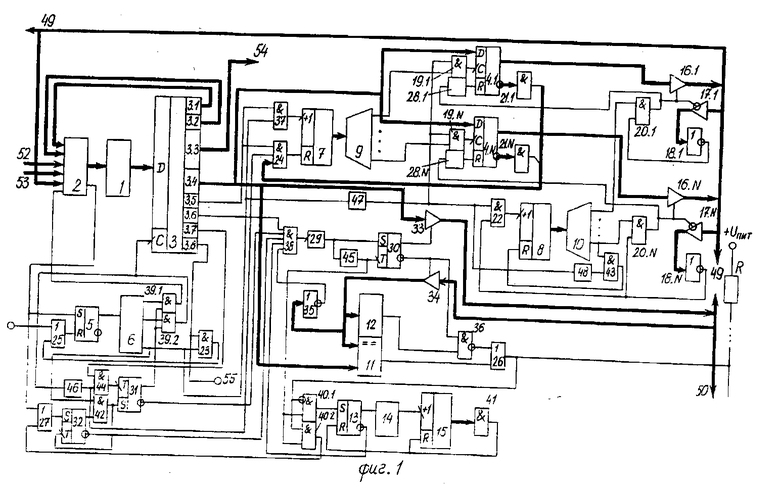

На фиг. 1 дана функциональная схема модуля мультимикропрограммной системы; на фиг. 2 - функциональная схема блока формирования адреса микрокоманд; на фиг. 3 представлены форматы микрокоманд, реализуемые устройством; на фиг. 4 изображена структурная схема мультимикропрограммной системы; на фиг. 5 приведены временные диаграммы работы устройства в режиме опроса состояния параллельных участков.

Модуль мультимикропрограммной системы (фиг. 1) содержит блок 1 памяти микропрограмм, блок 2 формирования адреса микрокоманд, регистр 3 микрокоманд, регистры 4.1-4. N передачи управления, триггер 5 управления, первый генератор 6 тактовых импульсов, счетчики 7 выборки и 8 опроса, дешифраторы 9 выборки и 10 опроса, схему 11 сравнения, первый триггер 13, первую 16.1-16.N и вторую 17.1-17.N группы блоков тристабильных элементов, группу элементов ИЛИ-НЕ 18.1-18. N, первую 19.1-19.N и вторую 20.1-20.N группы элементов И, первый 22, второй 23 и третий 24 элементы И, первый 25, второй 26 и третий 27 элементы ИЛИ, группу элементов задержки 28.1-28.N, одновибратор 29, шину 49 передачи управления и шину 50 синхронизации параллельных участков, причем прямой выход триггера 5 управления соединен с управляющим входом генератора 6 тактовых импульсов, первый и второй информационные входы блока 2 формирования адреса микрокоманд являются соответственно входами 52 логических условий и 53 кода операции модуля, информационный выход блока 2 формирования адреса микрокоманд соединен с адресным входом блока 1 памяти микропрограмм, выход которого соединен с информационным входом регистра 3 микрокоманд, выходы 3.1 адреса и 3.2. кода логического условия которого подключены к третьему информационному и управляющему входам блока 2 формирования адреса микрокоманд соответственно, выход 3.3 микроопераций регистра 3 микрокоманд является выходом 54 микроопераций модуля, выход счетчика 7 выборки соединен с входом дешифратора 9 выборки, выходы с первого по N-й которого подключены к первым входам элементов И 19.1-19.N соответственно, выходы которых соединены с входами синхронизации регистров 4.1-4.N передачи управления соответственно, прямые выходы которых подключены к информационным входам блоков тристабильных элементов 16.1-16. N соответственно, выходы которых подключены к шине 49 передачи управления, которая соединена с информационными входами блоков тристабильных элементов 17.1-17.N, выходы которых соединены с входами элементов ИЛИ-НЕ 18.1-18.N соответственно, выход элемента ИЛИ-НЕ 18.N соединен с первым входом элемента И 22, выход которого подключен к счетному входу счетчика 8 опроса, выход которого соединен с входом дешифратора 10 опроса, выходы с первого по N-й которого подключены к первым входам элементов И 20.1-20. N соответственно, выходы которых соединены с управляющими входами блоков тристабильных элементов 16.1, 17.1; ...; 16.N, 17.N соответственно, а также с входами элементов задержки 28.1-28.N соответственно, выходы которых соединены с входами сброса регистров 4.1-4-N передачи управления соответственно, выходы элементов ИЛИ-НЕ 18.1-18.N подключены к вторым входам элементов И 20.1-20.N соответственно, первый вход, второй вход и выход элемента ИЛИ 25 соединены с управляющим входом модуля, выходом элемента И 23 и входом сброса триггера 5 управления соответственно, а также дополнительно включенные формирователь 12 признака принадлежности, второй генератор 14 тактовых импульсов, счетчик 15 времени ожидания, третью группу элементов И 21.1-21. N, второй 30, третий 31 и четвертый 32 триггеры, первый 33 и второй 34 блоки тристабильных элементов, элемент ИЛИ-НЕ 35, элемент И-НЕ 36, четвертый 37, пятый 38, шестой 39.1, седьмой 39.2, восьмой 40.1, девятый 40.2, десятый 41, одиннадцатый 42, двенадцатый 43 и тринадцатый 44 элементы И, первый 45, второй 46, третий 47 и четвертый 48 элементы задержки, линию 51 состояния параллельных участков, причем выход 3.5 метки передачи управления/инициализации регистра 3 микрокоманд соединен с первыми входами элементов И 24 и 37, выходы которых соединены с входом сброса и счетным входом счетчика 7 выборки соответственно, выход 3.4 управляющей информации регистра 3 микрокоманд подключен к первому входу схемы 11 сравнения, к информационному входу блока 33 тристабильных элементов и к информационным входам регистров управления 4.1-4.N, инверсные выходы которых соединены с входами элементов И 21.1.-21.N соответственно, выход 3.6 статуса регистра 3 микрокоманд соединен с первым входом элемента И 38, выход которого соединен с входом одновибратора 29, выход которого подключен к входу элемента 45 задержки и входу установки триггера 30, инверсный выход которого подключен к управляющему входу блока 34 тристабильных элементов, прямой выход триггера 30 соединен с управляющим входом блока 33 тристабильных элементов, выход которого подключен к шине 50 синхронизации параллельных участков, которая соединена с информационным входом блока 34 тристабильных элементов, выход которого подключен к входам элемента ИЛИ-НЕ 35, адресному входу формирователя 12 признака принадлежности и к второму входу схемы 11 сравнения, первый и второй выходы генератора 6 тактовых импульсов подключены к первым входам элементов И 39.1 и 39.2, выход элемента И 39.1 соединен с входом синхронизации блока 2 формирования адреса микрокоманд, четвертый информационный вход которого подключен к шине 49 передачи управления, выход элемента И 39.2 соединен с входом синхронизации регистра 3 микрокоманд и с входом элемента 46 задержки, выход которого соединен с вторым входом элемента И 24, инверсный выход триггера 30 подключен к первому входу элемента И-НЕ 36, второй вход которого подключен к выходу формирователя 12 признака принадлежности, выход элемента И-НЕ 36 соединен с первым входом элемента ИЛИ 26, выход которого подключен к линии 51 состояния параллельных участков, выход элемента 45 задержки соединен со счетным входом триггера 30, а также с первыми входами элементов И 40.1 и 40.2, вторые входы которых подключены к линии 51 состояния параллельных участков, выходы элементов И 40.1 и 40.2 соединены соответственно с входом установки триггера 13 и первым входом элемента ИЛИ 27, прямой выход триггера 13 соединен с управляющим входом генератора 14 тактовых импульсов, выход которого соединен со счетным входом счетчика 15 времени ожидания, выход которого подключен к входам элемента И 41, выход которого подключен к входам сброса триггера 13 и счетчика 15 времени ожидания, выходы элементов И 21.1-21.N подключены к третьему входу элемента И 24, третий выход генератора 6 тактовых импульсов соединен с вторым входом элемента И 37, первым входом элемента И 42 и с входом элемента 47 задержки, выход которого подключен к вторым входам элементов И 19.1-19. N, второму входу элемента И 22 и к входу элемента 48 задержки, выход которого соединен с первым входом элемента И 43, второй вход и выход которого подключены к N-му выходу дешифратора 10 опроса и к входу сброса счетчика 8 опроса соответственно, выход 3.7 метки конца участка регистра 3 микрокоманд подключен к первому входу элемента И 44, второй вход которого соединен с выходом элемента 46 задержки, выход элемента И 44 подключен к счетному входу триггера 31, прямой выход которого подключен к вторым входам элементов И 39.1 и 39.2, инверсный выход триггера 31 соединен с вторым входом элемента И 38, третий, четвертый и пятый входы которого соединены соответственно с инверсным выходом триггера 32, инверсным выходом триггера 13 и с выходом элемента ИЛИ-НЕ 35, выход схемы 11 сравнения подключен к второму входу элемента ИЛИ 26, выход 3.8 метки конца микропрограммы регистра 3 микрокоманд соединен с выходом 55 конца микропрограммы модуля и с первым входом элемента И 23, второй вход которого подключен к третьему выходу генератора 6 тактовых импульсов, управляющий выход блока 2 формирования адреса микрокоманд подключен к входу установки триггера 5 управления и к второму входу элемента ИЛИ 27, выход которого подключен к входу установки триггера 32, прямой выход которого соединен с вторым входом элемента И 42, выход которого соединен с входом установки триггера 31 и счетным входом триггера 32.

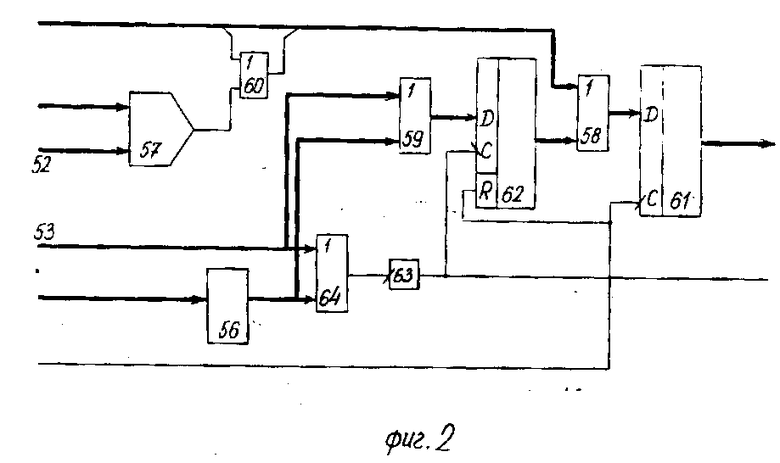

Блок 2 формирования адреса микрокоманд (фиг.2) включает шифратор 56 начального адреса, мультиплексор 57, первый 58 и второй 59 блоки элементов ИЛИ, первый элемент ИЛИ 60, регистр 61 адреса микрокоманд, регистр 62, одновибратор 63 и второй элемент ИЛИ 64, причем вход шифратора 56 является четвертым информационным входом блока формирования адреса микрокоманд, управляющий и информационный входы мультиплексора 57 являются соответственно управляющим и первым информационным входами блока формирования адреса микрокоманд, n-1 старших разрядов третьего информационного входа которого (где n - разрядность адреса микрокоманды) соединены с n-1 старшими разрядами первого входа блока 58 элементов ИЛИ, а младший разряд подключен к первому входу элемента ИЛИ 60, второй вход и выход которого соединены соответственно с выходом мультиплексора 57 и младшим разрядом первого входа блока 58 элементов ИЛИ, вход синхронизации регистра 61 подключен к входу синхронизации блока формирования адреса микрокоманд, а выход является информационным выходом блока формирования адреса микрокоманд, второй информационный вход которого соединен с первым входом элемента ИЛИ 64 и первым входом блока 59 элементов ИЛИ, выход которого соединен с информационным входом регистра 62, вход сброса которого соединен с входом синхронизации блока формирования адреса микрокоманд, а выход подключен к второму входу блока элементов ИЛИ 58, выход которого подключен к информационному входу регистра 61, выход шифратора 56 соединен с вторым входом блока 59 элементов ИЛИ и вторым входом элемента ИЛИ 64, выход которого соединен с входом одновибратора 63, выход которого подключен к входу синхронизации регистра 62 и управляющему выходу блока формирования адреса микрокоманд.

Назначение элементов модуля мультимикропрограммной системы (фиг.1) состоит в следующем.

Блок 1 памяти микропрограммы (БПМП) служит для постоянного хранения и выдачи микрокоманд, входящих в различные участки микропрограмм, закрепленные за данным модулем.

Регистр 3 микрокоманд предназначен для приема и фиксации микрокоманд, поступающих с выхода блока 1, на время их анализа или обработки.

Регистры 4.1-4. N передачи управления предназначены для приема, временного хранения и выдачи кодов признаков участков микропрограмм при передаче управления или инициализации других аналогичных модулей управляющей системы.

Генератор 6 тактовых импульсов служит для формирования трех сдвинутых друг относительно друга импульсных последовательностей t1, t2, t3, синхронизирующих работу различных элементов устройства.

Счетчик 7 выборки, дешифратор 9 выборки и элементы И 19.1-19.N предназначены для управления записью признаков участков микропрограмм в регистры 4.1-4. N, а элементы И 24 и 37 служат для формирования импульсов управления счетчиком 7 выборки.

Счетчик 8 опроса, дешифратор 10 опроса предназначены для управления считыванием информации и организации циклического опроса регистров 4.1-4.N, а блоки 16.1-16. N тристабильных элементов служат для передачи информации (кодов признаков участков микропрограмм) с выходов регистров 4.1-4.N соответственно на шину 49 передачи управления.

Шины 49 передачи управления и 50 синхронизации параллельных участков служат соответственно для передачи кодов признаков участков микропрограмм и кодов НТС при передаче управления и опросе состояния параллельных участков соответственно, а линия 51 используется для формирования сигнала обобщенного состояния Z опрашиваемых параллельных участков.

Блоки 17.1-17. N тристабильных элементов совместно с элементами ИЛИ-НЕ 18.1-18. N соответственно служат для формирования сигналов, характеризующих состояние шины 49, элементы И 20.1-20.N предназначены для формирования сигналов, являющихся одновременно сигналами управления блоков 16.1-16.N, 17.1-17. N тристабильных элементов соответственно и сигналами сброса регистров 4.1-4. N соответственно, а элементы 28.1-28. N используются для задержки поступления сигналов сброса регистров 4.1-4.N соответственно на время выдачи информации на шину 49 передачи управления.

Элемент И 22 предназначен для управления процессом счета счетчика 8 опроса в зависимости от текущего состояния шины 49, а элементы И 43 и задержки 48 служат для формирования сигнала сброса счетчика 8 при окончании очередного цикла опроса (появлении единичного сигнала на N-м выходе дешифратора 10), при этом элемент 48 предотвращает сброс счетчика 8 сразу же после его переключения в состояние "11...1" и возбуждения единичного сигнала на N-м выходе дешифратора 10, сдвигая импульс сброса t3 на время выдачи информации из регистра 4.N на шину 49.

Триггер 5 в объединении с элементом И 23 и элементом ИЛИ 25 служит для управления работой генератора 6.

Триггеры 31 и 32 совместно с элементами И 44, 42, 39.1, 39.2, элементом ИЛИ 27 и элементом 46 задержки используются для блокировки подачи импульсов t1 и t2 на входы синхронизации блока 2 и регистра 3 микрокоманд при работе модуля в режиме опроса состояния параллельных участков и нахождении в состоянии ожидания передачи управления от другого аналогичного устройства; при этом элемент ИЛИ 27 обеспечивает объединение сигналов запуска, возникающих при передаче управления на текущий модуль или завершении опроса состояния параллельных участков, элемент И 42 формирует сигнал переключения в единичное состояние триггера 31, а элемент 46 задержки введен для предотвращения повторного переключения триггера 31 в момент исчезновения единичного сигнала на выходе 3,7 метки конца участка регистра 3 и задержки импульса t2 на время установления единичного сигнала на выходе 3.5 регистра 3.

Блок 34 тристабильных элементов предназначен для передачи информации (кодов НТС) с шины 50 на входы формирователя 12 признака принадлежности, элемента ИЛИ-НЕ 35 и схемы 11 сравнения.

Элемент ИЛИ-НЕ 35 служит для формирования сигнала состояния шины 50 синхронизации параллельных участков.

Блок 33 тристабильных элементов обеспечивает передачу кодов НТС с выхода 3,4 регистра 3 на шину 50 при работе модуля в режиме опроса состояния параллельных участков.

Элемент И 38 в объединении с одновибратором 29 предназначен для формирования импульса p инициализации цикла опроса состояния параллельных участков.

Триггер 30 служит для управления приемом (выдачей) управляющей информации с шины (на шину) 50 через блок 34 (33) тристабильных элементов соответственно.

Формирователь 12 признака принадлежности выполняется в виде ППЗУ с организацией Qx1 бит (где Q - число различных точек синхронизации, которыми завершаются участки микропрограмм, закрепленные за текущим модулем) и предназначен для преобразования кода НТС Tr, поступающего с шины 50, в одноразрядный признак D, определяемый следующим образом:

Схема 11 сравнения введена для сопоставления кода НТС Tr, поступающего с шины 50, с кодом НТС Ts, соответствующим точке синхронизации, которая закрывает параллельный участок, выполненный текущим модулем.

Элемент ИЛИ 26 служит для формирования сигнала состояния Si текущего модуля. Элемент ИЛИ 26 имеет выходной каскад с "открытым" коллектором, нагрузкой для которого является внешнее сопротивление R (фиг. 1).

Элемент И-НЕ 36 обеспечивает формирование сигнала - маски, который осуществляет блокировку передачи сигнала с выхода схемы 11 сравнения на линию 51 состояния параллельных участков.

Элемент 45 предназначен для задержки подачи импульса p с выхода одновибратора 29 на счетный вход триггера 30 и входы элементов И 40.1 и 40.2 на время формирования сигнала обобщенного состояния Z на линии 51 при работе модуля в режиме опроса состояния параллельных участков.

Генератор 14, триггер 13, счетчик 15 времени ожидания и элемент И 41 предназначены для отсчета времени T между двумя смежными циклами опроса состояния параллельных участков, при этом триггер 13 используется для управления запуском генератора 14 и блокировки элемента И 38, а элемент И 41 служит для формирования сигнала "Тайм-аут", являющегося сигналом сброса триггера 13 и счетчика 15 и отмечающего конец требуемого временного интервала Т.

Элементы И 40.1 и 40.2 служит для формирования сигналов запуска процесса отсчета времени ожидания Т и инициализации текущего модуля после завершения всех требуемых параллельных участков соответственно.

Назначение элементов блока 2 формирования адреса микрокоманд (фиг. 2) состоит в следующем.

Шифратор 56 служит для формирования начального адреса параллельного или последовательного участка микропрограммы в блоке 1 при передаче управления данному модулю.

Мультиплексор 57 предназначен для формирования значения опрашиваемого логического условия.

Регистр 61 служит для приема, хранения и выдачи исполнительного адреса следующей микрокоманды.

Регистр 62 введен для предварительной записи адресов инициализации модуля (кодов операции) и исключает необходимость длительной фиксации информации на третьем и четвертом информационных входах блока 2 до момента появления первого тактового импульса t1 на выходе генератора 6.

Элемент ИЛИ 60 предназначен для модификации значения младшего разряда адреса следующей микрокоманды в точках ветвления микропрограммы.

Блок 59 элементов ИЛИ обеспечивает объединение адресов инициализации модуля, поступающих с входа 53 кода операции модуля и выхода шифратора 56, и передачу адресов на вход регистра 62.

Блок 58 элементов ИЛИ обеспечивает объединение адресов инициализации и адреса следующей микрокоманды, поступающих соответственно с выхода регистра 62 и третьего информационного входа блока 2, и передачу адресов на вход регистра 61.

Элемент ИЛИ 64 служит для формирования сигнала, индицирующего появление адреса инициализации на выходе шифратора 56 или кода операции на входе 53 модуля.

Одновибратор 63 предназначен для формирования импульса запуска текущего модуля при появлении адреса на выходе шифратора 56 или кода операции на входе 53 модуля.

Работу предлагаемого устройства (условно обозначаемого Mi) рассмотрим на примере функционирования ММПС, состоящей из множества идентичных модулей и реализующей микропрограмму сложного параллельного алгоритма управления.

Первоначально все регистры, триггеры и счетчики (фиг. 1, 2), за исключением счетчика 8, установленного в состояние "11...1", находятся в состоянии логического нуля, поэтому генераторы 6 и 14 выключены, на всех выходах дешифратора 9 выборки присутствует нулевой уровень сигнала, на выходах дешифратора 10 опроса находится код "100...0", а элементы блоков 16.1-16.N-1 и 33 находятся в состоянии высокого импеданса ("отключено") (цепи начальной установки на фиг. 1, 2 условно не показаны). В ячейках блока 1 с ненулевыми адресами записаны микрокоманды, составляющие участки микропрограмм, закрепленные за рассматриваемым модулем. На шинах 49 и 50 присутствует нулевой, а на линии 51 - единичный уровень сигнала.

Функционирование ММПС начинается с момента подачи на вход 53 одного из ее модулей (допустим, модуля Mi) кода выполняемой операции (фиг.1). Код операции (КОП), представляющий собой адрес начала соответствующей микропрограммы (адрес начального последовательного участка), с входа 53 поступает (фиг. 2) на первые входы элемента ИЛИ 64 и блока элементов ИЛИ 59. Поскольку КОП содержит по меньшей мере одну единицу, на выходе элемента 64 возникает положительный перепад уровня сигнала, который воздействует на одновибратор 63 и возбуждает на его выходе импульс "Пуск". Одновременно КОП проходит через блок 59, на втором входе которого присутствует нулевой код, обусловленный отсутствием информации на шине 49, и устанавливается на информационном входе регистра 62. Импульс с выхода одновибратора 63 подается на вход синхронизации регистра 62 и задним фронтом (срезом) фиксирует в нем поступивший КОП. КОП с выхода регистра 62 через блок элементов ИЛИ 58 (на первом входе которого находится нулевой код, обусловленный нулевым состоянием регистра 3) проходит на информационный вход регистра 61 адреса микрокоманд.

Одновременно импульс с выхода одновибратора 63 поступает (фиг.1) на вход установки триггера 5, а также через элемент ИЛИ 27 - на вход установки триггера 32 и переключает указанные триггеры в единичное состояние. Единичный сигнал с прямого выхода триггера 32 открывает элемент И 42, а единичный сигнал с прямого выхода триггера 5 подается на управляющий вход генератора 6 и разрешает формирование на его выходах импульсных последовательностей t1, t2 и t3.

Поскольку триггер 31 находится в исходном (нулевом) состоянии и нулевой сигнал с его прямого выхода блокирует элементы И 39.1, 39.2, первые импульсы t1 и t2 с первого и второго выходов генератора 6 соответственно не проходят на выходы элементов 39.1 и 39.2. В свою очередь импульс t3 с третьего выхода генератора 6 через открытый элемент 42 поступает на вход установки триггера 31 и переводит его в состояние логической единицы. Единичный сигнал с прямого выхода триггера 31 открывает элементы 39.1 и 39.2, а нулевой сигнал с инверсного выхода блокирует элемент И 38, предотвращая тем самым срабатывание одновибратора 29. Кроме того, импульс t3 с выхода элемента 42 поступает на счетный вход триггера 32 и срезом возвращает его в состояние логического нуля.

Одновременно импульс с третьего выхода генератора 6 передается на вход элемента 47 задержки и далее - на второй вход элемента И 22 и вход элемента 48 задержки. Если на первом входе элемента 22 находится единичный сигнал, то импульс t3 поступает на счетный вход счетчика 8 и переключает его в нулевое состояние, в противном случае передача импульса t3 на счетный вход счетчика не происходит и состояние последнего не изменяется. Импульс t3 с выхода элемента 48 спустя определенное время поступает на первый вход элемента И 43 и если счетчик 8 все еще находится в состоянии "11...1" и на N-м выходе дешифратора 10 соответственно присутствует единичный сигнал, через элемент 43 проходит на вход сброса счетчика 8 и переводит его в состояние "00...0". В противном случае счетчик 8 уже установлен в состояние "00...0", на всех выходах дешифратора 10 присутствует нулевой уровень сигнала и импульс через элемент 43 не проходит.

Таким образом, первый импульс t3 обеспечивает переключение счетчика 8 в состояние "00...0" и формирует на выходах дешифратора 10 нулевой уровень сигнала, блокируя тем самым элементы И 20.1-20.N.

Второй тактовый импульс последовательности t1 c первого выхода генератора 6 через открытый элемент И 39.1 передается на вход синхронизации блока 2 (фиг. 2) и, поступая далее на вход синхронизации регистра 61, фронтом фиксирует в нем ранее установленный на его информационном входе КОП, инициируя процесс считывания первой микрокоманды. Одновременно импульс t1 поступает на вход сброса регистра 62 и возвращает его в нулевое состояние; на выходе регистра 62 появляется нулевой код. КОП с выхода регистра 61 подается на адресный вход БПМП 1 (фиг. 1) и формирует на его выходе первую микрокоманду реализуемого участка микропрограммы (начального последовательного участка реализуемой микропрограммы). С выхода блока 1 данная микрокоманда поступает на информационный вход регистра 3. Очередной тактовый импульс t2 через открытый элемент 39.2 проходит на вход синхронизации регистра 3 и фиксирует в нем считанную из блока 1 микрокоманду.

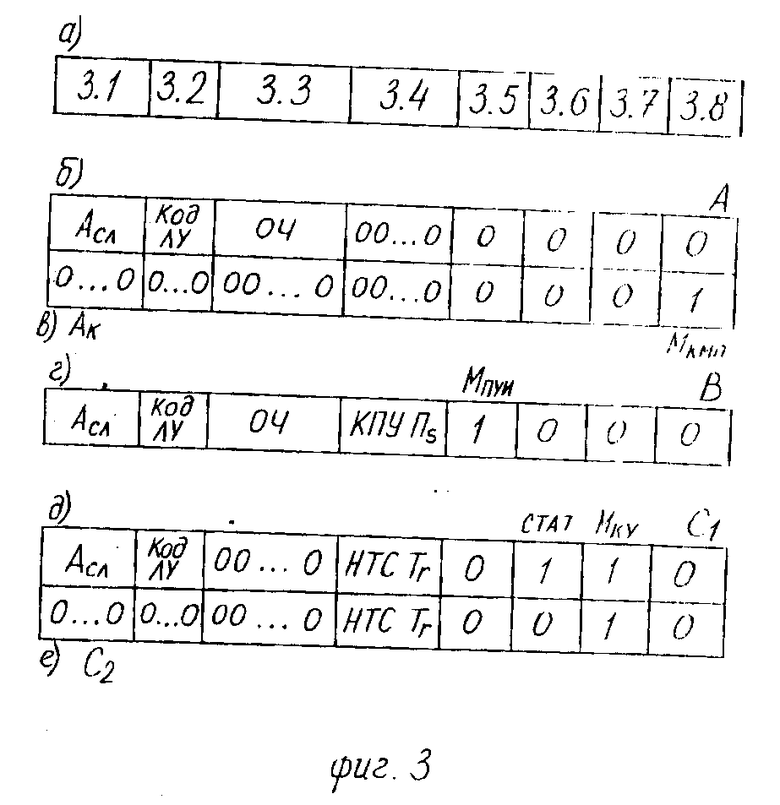

Далее в зависимости от формата считанной микрокоманды (фиг. 3) устройство может функционировать в одном из следующих режимов; выполнения операционной микрокоманды (режим А), передачи управления другим (другому) аналогичным устройствам системы или инициализации параллельных участков (режим B) и синхронизации завершения параллельных участков микропрограммы (режим C).

Рассмотрим работу устройства в каждом из перечисленных режимов.

Режим A. Функционирование устройства в режиме A начинается с момента фиксации в регистре 3 микрокоманды формата A или Ak (фиг. 3б,в). Первоначально предположим, что считанная микрокоманда имеет формат А (фиг. 3б). На выходах 3.4-3.8 регистра 3 устанавливаются сигналы логического нуля; на выходах 3.1 и 3.2 появляются соответственно адрес следующей микрокоманды (Aсл) и код опрашиваемого логического условия (ЛУ) (который, в частности, может быть нулевым), а на выходе 3.3 формируется операционная часть микрокоманды, содержащая информацию об инициируемых в данном такте работы устройства микрооперациях.

Операционная часть (ОЧ) микрокоманды с выхода 3.3 регистра 3 передается на выход 54 модуля и возбуждает требуемые микрооперации (МО). Нулевой сигнал с выхода 3.5 регистра 3 блокирует элементы И 24 и 37; нулевой сигнал с выхода 3.6 регистра 3 формирует нулевой уровень сигнала на выходе элемента И 38; нулевой сигнал с выхода 3.7 регистра 3 блокирует элемент И 44, не допуская тем самым обнуления триггера 31; сигнал логического нуля с выхода 3.8 регистра 3 блокирует элемент И 23, предотвращая срабатывание триггера 5 управления.

Одновременно адрес следующей микрокоманды и код опрашиваемого логического условия с выходов 3.1 и 3.2 регистра 3 соответственно поступает на третий информационный и управляющий входы блока 2 (фиг. 2). Код логического условия далее подается на управляющий вход мультиплексора 57 и обеспечивает передачу на его выход значения опрашиваемого логического условия с входа 52 модуля. Старшая часть адреса следующей микрокоманды с третьего информационного входа блока 2 через блок элементов ИЛИ 58, на втором входе которого находится нулевой код с выхода регистра 62, проходит на информационный вход регистра 61, а младший разряд (который является модифицируемым и может изменяться в точках ветвления микропрограммы) поступает на первый вход элемента ИЛИ 60.

Если опрашиваемое логическое условие истинно, то на выходе мультиплексора 57 возникает единичный сигнал, который поступает на второй вход элемента ИЛИ 60 и, проходя на его выход, изменяет значение младшего разряда адреса на единичное. Если опрашиваемое логическое условие ложно или код логического условия является нулевым, на выходе мультиплексора 57 сохраняется нулевой уровень сигнала и на выход элемента 60 передается исходное значение младшего разряда адреса. Младший разряд адреса с выхода элемента 60 через соответствующий элемент ИЛИ блока 58 передается на информационный вход регистра 61. Таким образом, на информационном входе регистра 61 появляется исполнительный адрес очередной микрокоманды реализуемого участка микропрограммы, сформированный с учетом значения требуемого логического условия.

Очередной тактовый импульс t1 (фиг. 1) через элемент И 39.1 проходит на вход синхронизации блока 2 (фиг. 2) и, поступая далее на вход синхронизации регистра 61, обеспечивает прием исполнительного адреса следующей микрокоманды. Этот же импульс подтверждает нулевое состояние регистра 62. Адрес следующей микрокоманды с выхода регистра 61 поступает (фиг. 1) на адресный вход блока 1 и обеспечивает считывание очередной микрокоманды. Считанная микрокоманда с выхода блока 1 подается на информационный вход регистра 3 и записывается в данный регистр по фронту очередного импульса t2, приходящего через элемент 39.2 с выхода генератора 6. Далее модуль приступает к выполнению считанной микрокоманды. Ход выполнения очередной микрокоманды аналогичен ходу реализации предшествующей микрокоманды.

Если считанная микрокоманда имеет формат Aк (фиг. 3в), то на выходах 3.1-3.7 регистра 3 формируется нулевой уровень сигнала, а на выходе 3.8 появляется единичный сигнал - метка конца реализуемой микропрограммы (Мкмп). Метка Мкмп поступает на выход 55 конца микропрограммы модуля и индицирует завершение выполнения текущей операции и готовность системы к реализации очередной. Одновременно эта же метка открывает элемент И 23. Импульс t3 с третьего выхода генератора 6 проходит через элемент И 23, элемент ИЛИ 25 и поступает на вход сброса триггера 5, переключая его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 5 блокирует работу генератора 6; таким образом, текущий модуль (и система в целом) заканчивает выполнение конечного последовательного участка микропрограммы и переходит в состояние ожидания задания на реализацию очередной микропрограммы (операции). Перед началом выполнения очередной операции элементы устройства вновь устанавливаются в исходное состояние, после чего на вход 53 соответствующего модуля подается КОП и система переходит к реализации следующей микропрограммы. Переход модуля в пассивное состояние может быть также осуществлен путем подачи на первый вход элемента ИЛИ 25 сигнала "Стоп".

Режим B. Переход устройства в режим функционирования B происходит после записи в регистр 3 микрокоманды формата B (фиг. 3г). Текущий модуль Mi переходит в режим инициализации группы P параллельных участков микропрограммы, закрепленных за другими аналогичными модулями управляющей системы. На выходах 3.6-3.8 регистра 3 появляются сигналы логического нуля, на выходах 3.1 и 3.2 формируются соответственно адрес следующей микрокоманды и код логического условия, а на выходе 3.3 образуется либо нулевой код, либо ненулевой код, определяющий выполняемые микрооперации.

Нулевой сигнал с выхода 3.6 регистра 3 блокирует элемент И 38, предотвращая срабатывание одновибратора 29; нулевой сигнал с выхода 3.7 блокирует элемент 44; нулевой сигнал с выхода 3.8 регистра 3 закрывает элемент И 23. Одновременно на выходе 3.5 регистра 3 образуется единичный сигнал - метка передачи управления или инициализации (Мпуи), а на выходе 3.4 устанавливается код признака инициализируемых участков микропрограммы (КПУ) Пр.

КПУ с выхода 3.4 регистра 3 передается на информационные входы регистров 4.1-4.N, а единичная метка Мпуи поступает на входы элементов И 24 и 37 и разрешает прохождение тактовых импульсов, управляющих работой счетчика 7 выборки. Код, характеризующий текущее состояние регистров 4.1-4.N и формируемый элементами И 21.1-21.N, поступает на третий вход элемента И 24. Импульс t2 с выхода элемента И 39.2 через элемент 46 поступает на второй вход элемента И 24 и, если состояние регистров 4.1-4.N является нулевым и, следовательно, на третьем входе элемента 24 присутствует код "11...1", проходит через элемент 24 на вход сброса счетчика 7 и переключает его в нулевое состояние (подтверждает его исходное состояние). Нулевой код с выхода счетчика 7 поступает на вход дешифратора 9 и формирует на его выходах нулевой уровень сигнала, обеспечивая тем самым блокировку элементов И 19.1-19.N. Если же состояние по крайней мере одного из регистров 4.1-4.N отлично от нулевого, на выходах элементов И 21.1-21.N устанавливается "неединичный" код и состояние счетчика 7 при поступлении импульса t2 не изменяется.

Очередной импульс t3 с третьего выхода генератора 6 через элемент И 37 проходит на счетный вход счетчика 7 и фронтом увеличивает его содержимое на единицу. Образующийся код ("00...01") с выхода счетчика 7 передается на вход дешифратора 9 и возбуждает его k-й (первый) выход. Единичный сигнал с k-го (первого) выхода дешифратора 9 открывает элемент И 19.k (19.1). Импульс t3, проходя через элемент 47 задержки, подается на второй вход элемента И 22, на первом входе которого образуется сигнал, определяемый состоянием шины 49 и формируемый элементом ИЛИ-НЕ 18.N. Если информация на шине 49 отсутствует, то нулевой код с шины 49 через открытый блок 17.N поступает на входы элемента 18. N и формирует на его выходе сигнал логической единицы. Этот сигнал подается на первый вход элемента И 22, импульс t3 проходит на выход элемента 22 и фронтом увеличивает содержимое счетчика 8 на единицу. Код с выхода счетчика 8 поступает на вход дешифратора 10 и возбуждает его i-й выход. Если шина 49 занята, то на выходе элемента 18.N устанавливается нулевой сигнал, который блокирует элемент 22 и не допускает прохождение импульса t3 на счетный вход счетчика 8.

В то же время импульс t3 с выхода элемента 47, будучи задержанным на время, достаточное для формирования очередного кода на выходах счетчиков 7 и 8, подается на входы элементов И 19.1-19.N, а также на вход элемента 48. Так как единичный сигнал присутствует только на k-м (первом) выходе дешифратора 9, импульс t3 проходит через элемент 19.k (19.1) и фронтом фиксирует код Пр в регистре 4.k (4.1).

Единичный сигнал с i-го выхода дешифратора 10 поступает на первый вход элемента И 20.i и в случае, если шина 49 свободна и на второй вход элемента 20. i подается единичный сигнал с выхода элемента 18.i, передается на выход элемента 20. i. Единичный сигнал с выхода элемента 20.i поступает на управляющие входы блоков 16. i и 17.i и обеспечивает передачу информации (кода признака участков либо нулевого кода) с прямого выхода регистра 4.i (в общем случае i≠k) на шину 49. Одновременно сигнал с выхода элемента 20.i переводит элементы блока 17.i в высокоимпедансное состояние, отключая тем самым второй вход элемента 20.i и обусловливая работу этого элемента в режиме безусловной передачи сигнала с его первого входа на выход. В то же время единичный сигнал с выхода элемента 20.i поступает на вход элемента 28.i, с заданным сдвигом во времени появляется на его выходе и осуществляет сброс регистра 4. i. Если i=N, т.е. считывание информации осуществлялось из регистра 4.N, то единичный сигнал с N-го выхода дешифратора 10 открывает элемент 43 и поэтому импульс t3 с выхода элемента 48 проходит через элемент 43 на вход сброса счетчика 8, переводит его в нулевое состояние и инициирует тем самым очередной цикл опроса регистров 4.1-4.N.

Одновременно с выдачей на шину 49 кода Пр адрес следующей микрокоманды и код логического условия с выходов 3.1 и 3.2 регистра 3 поступают на соответствующие входы блока 2 и аналогично ранее рассмотренному (режим A) обеспечивают формирование исполнительного адреса очередной микрокоманды. Устройство приступает к считыванию и исполнению следующей микрокоманды реализуемого участка. Если в соответствии с алгоритмом управления после инициализации параллельных участков текущей модуль должен переходить в состояние ожидания, то для очередной считываемой из БПМП 1 микрокоманды должен использоваться формат C1 или C2 (фиг. 3д, е).

Работа модуля в режиме приема и анализа кодов признаков участков микропрограммы состоит в следующем.

Коды признаков участков с шины 49 передачи управления поступают на четвертые информационные входы блоков 2 и одновременно анализируются всеми модулями системы. Анализ кода Пs модулем Мk сводится к установлению факта существования параллельного (последовательного) участка микропрограммы, закрепленного за данным модулем и обладающего этим же признаком Пs. Код Пs поступает (фиг. 2) на вход шифратора 56 и, в случае наличия участка, обладающего признаком Пs, формирует на выходе шифратора 56 начальный адрес Анач этого участка в блоке 1, в противном случае на выходе шифратора 56 сохраняется нулевой код.

Адрес Анач с выхода шифратора 56 через блок элементов ИЛИ 59, на первом входе которого установлен нулевой код, обусловленный отсутствием кода операции на входе 53 модуля, походит на информационный вход регистра 62. Одновременно этот же адрес поступает на вход элемента ИЛИ 64. Если Анач="00... 0", то на выходе элемента 64 сохраняется нулевой уровень сигнала, иначе положительный перепад уровня сигнала, возникающий на выходе элемента 64, воздействует на одновибратор 63 и формирует на его выходе импульс. Данный импульс передается на вход синхронизации регистра 62 и фиксирует в нем сформированный адрес Анач.

Импульс с выхода одновибратора 63, кроме того, поступает (фиг. 1) на вход установки триггера 5 и через элемент ИЛИ 27 - на вход установки триггера 32 и подтверждает единичное состояние триггера 5, переключая в то же время в единичное состояние триггер 32. Единичный сигнал с прямого выхода триггера 32 открывает элемент И 42. Очередной импульс t3, поступая через элемент И 42 на вход установки триггера 31 и счетный вход триггера 32, переключает первый в состояние логической единицы, а второй (срезом) - в состояние логического нуля. Нулевой сигнал с выхода триггера 32 блокирует элемент 42, а единичный сигнал с прямого выхода триггера 31 открывает элементы 39.1 и 39.2.

Очередной импульс t1 через открытый элемент И 39.1 подается на вход синхронизации блока 2 и фиксирует адрес Анач в регистре 61 (на выходе блока 2). Адрес Анач с выхода блока 2 поступает на адресный вход БПМП 1 и обеспечивает считывание первой микрокоманды инициализируемого участка. Модуль приступает к выполнению заданного участка микропрограммы и далее функционирует аналогично работе модуля при реализации начального участка микропрограммы.

Режим C. Функционирование модуля Mi в режиме C начинается после фиксации в регистре 3 микрокоманды формата C1 или C2 (фиг. 3д, е). Если считанная микрокоманда имеет формат C1 (фиг. 3д), то модуль получает статус ведущего и переходит к опросу состояния требуемых параллельных участков микропрограммы, иначе модуль считается ведомым и переходит в состояние ожидания, которое идентично состоянию устройства после передачи управления другим аналогичным устройствам.

Первоначально предположим, что считанная микрокоманда имеет формат C2 (фиг. 3е).

На выходах 3.5, 3.6, 3.8, 3.1-3.3 регистра 3 появляется нулевой уровень сигнала, на выходе 3.7 формируется единичная метка конца параллельного участка (Мку), а на выходе 3.4 образуется код номера точки синхронизации (НТС) Ts, закрывающей реализуемый параллельный участок микропрограммы. Нулевые сигналы с выходов 3.5, 3.6 и 3.8 регистра 3 блокируют соответственно элементы И 24, 37, элемент И 38 и элемент И 23; нулевой код с выхода 3.3 поступает на выход 54 микроопераций модуля; нулевые коды с выходов 3.1 и 3.2 передаются соответственно на третий информационный и управляющий входы блока 2; код НТС Ts подается на первый вход схемы 11 сравнения, а единичная метка Мку открывает элемент И 44. Нулевые коды, поступившие на третий информационный и управляющий входы блока 2 (фиг. 2), формируют нулевой уровень сигнала на выходах мультиплексора 57 и элемента ИЛИ 64 и подготавливают тем самым текущий модуль к возможному последующему приему управления от другого устройства.

Импульс t2, поступивший ранее на вход элемента 46 задержки, через открытый элемент И 44 подается на счетный вход триггера 31 и срезом устанавливает его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 31 блокирует элементы 39.1 и 39.2, не допуская прохождения тактовых импульсов на их выходы. Выборка микрокоманд из БПМП 1 прекращается и устройство переходит в пассивное состояние, в котором пребывает вплоть до передачи управления от другого аналогичного устройства.

Теперь предположим, что считанная из блока 1 микрокоманда имеет формат C1 (фиг. 3д).

В отличие от вышерассмотренного случая на выходах 3.1 и 3.2 регистра 3 формируются соответственно адрес следующей микрокоманды и код опрашиваемого логического условия, а на выходе 3.6 образуется единичный сигнал статуса, который указывает, что текущий модуль для точки синхронизации Ts является ведущим и управляет синхронизацией требуемых параллельных участков. Нулевые сигналы с выходов 3.5 и 3.8 регистра 3 формируют нулевой уровень сигнала соответственно на выходах элементов И 24, 37 и элемента И 23, а единичная метка Mку открывает элемент И 44. Импульс t2 с выхода элемента 46 задержки проходит через элемент 44 и срезом сбрасывает триггер 31 в состояние логического нуля. Нулевой сигнал с прямого выхода триггера 31 блокирует элементы 39.1 и 39.2, а единичный сигнал с инверсного выхода поступает на второй вход элемента И 38, на первый вход которого подается единичный сигнал статуса, на третьем и четвертом входах присутствуют единичные сигналы с инверсных выходов триггеров 32 и 13 соответственно, а на пятом входе установлен сигнал с выхода элемента ИЛИ-НЕ 35, определяемый состоянием шины 50 синхронизации параллельных участков.

Так как триггер 30 находится в нулевом состоянии, единичный сигнал с его инверсного выхода поступает на управляющий вход блока 34 и обеспечивает передачу информации с шины 50 на его выход. Код с выхода блока 34 подается на входы элемента 35. В случае наличия информации на шине 50 на выходе элемента 35 формируется потенциал логического нуля, который блокирует элемент И 38 и предотвращает возникновение перепада уровня сигнала на входе одновибратора 29. Как только шина 50 освобождается, на выходе элемента 35 устанавливается сигнал логической единицы. Единичный сигнал с выхода элемента 35 подается на пятый вход элемента 38 и изменяет уровень сигнала на его выходе с нулевого на единичный. Перепад уровня сигнала на выходе элемента 38 воздействует на одновибратор 29 и возбуждает на его выходе импульс p.

Импульс p с выхода одновибратора 29 переключает триггер 30 в состояние логической единицы и, кроме того, поступает на вход элемента 45 задержки. Нулевой сигнал с инверсного выхода триггера 30 поступает на управляющий вход блока 34 и переводит элементы блока 34 в состояние высокого импеданса, а единичный сигнал с прямого выхода триггера 30 открывает блок 33. Одновременно нулевой сигнал с инверсного выхода триггера 30 поступает на первый вход элемента И-НЕ 36 и формирует на его выходе единичный сигнал-маску. Этот сигнал подается на первый вход элемента ИЛИ 26 и тем самым блокирует прохождение сигнала с выхода схемы 11 на линию 51. На выходе элемента 26 образуется сигнал логической единицы; таким образом, текущий модуль не оказывает влияния на состояние сигнала Z на линии 51.

В то же время Код НТС Ts через блок 33 передается на шину 50 и обеспечивает опрос состояния остальных модулей системы. Процедура опроса состоит в следующем.

Код НТС Ts с шины 50 поступает на информационные входы блоков 34 модулей ММПС и, так как триггеры 30 всех модулей, за исключением триггера 30 модуля Mi, установлены в состояние логического нуля (что обусловливается блокировкой возможности одновременного обращения к шине 50 нескольких модулей), проходит на выходы блоков 34 и обеспечивает формирование сигналов состояния модулей по отношению к точке синхронизации Ts. В то же время текущий модуль не принимает информацию с шины 50, поскольку на управляющем входе его блока 34 находится запрещающий (нулевой) сигнал с инверсного выхода триггера 30.

Формирование сигнала состояния модуля Mu, u ≠ i, происходит следующим образом.

Код НТС Ts с выхода блока 34 поступает на входы элемента 35, формирует на его выходе сигнал логического нуля и, таким образом, блокирует элемент 38, предотвращая возможное начало процесса опроса состояния параллельных участков при возникновении единичного сигнала статуса на выходе 3.6 регистра 3 (данная ситуация не исключена в случае наличия нескольких одновременно завершаемых групп параллельных участков). Одновременно код Ts поступает на второй вход схемы 11 сравнения и сопоставляется с кодом НТС Tp, который формируется на выходе 3.4 регистра 3 и присутствует на первом входе схемы 11. Кроме того, код Ts подается на адресный вход формирователя 12.

В случае отсутствия участков микропрограмм, закрепленных за модулем Mu и завершающихся в точке Ts, на выходе формирователя 12 появляется сигнал логического нуля. Этот сигнал подается на второй вход элемента И-НЕ 36 и формирует на его выходе сигнал логической единицы. Единичный сигнал с выхода элемента 36 поступает на первый вход элемента ИЛИ 26 и устанавливает на его выходе единичный сигнал состояния Su.

Если за текущим модулем Mu закреплен параллельный участок микропрограммы, оканчивающийся точкой синхронизации Ts (состояние этого участка может быть произвольным: "завершен", "начат и находится в стадии реализации" или "не начат"), то на выходе формирователя 12 образуется единичный сигнал - признак принадлежности D. Этот сигнал (признак) поступает на второй вход элемента 36 и устанавливает на его выходе сигнал логического нуля. На первом входе элемента 26 формируется нулевой уровень сигнала и теперь уровень сигнала на выходе элемента 26 (сигнал Su) определяется соотношением кодов Ts и Tp, т.е. уровнем сигнала на выходе схемы 11 сравнения.

Если коды Tp и Ts различны, т.е. u-й модуль не завершил выполнение участка микропрограммы (в этом случае Tp=0) или выполнил участок, не входящий в подмножество контролируемых параллельных участков, то на выходе схемы 11 формируется нулевой сигнал. Если коды Ts и Tp совпадают, т.е. модуль Mu выполнил участок, оканчивающийся требуемой точкой синхронизации Ts, то на выходе схемы 11 образуется единичный сигнал. Сигнал с выхода схемы 11 через элемент ИЛИ 26 передается на линию 51 и совместно с аналогичными по функциональному назначению сигналами с выходов элементов 26 других модулей ММПС формирует на линии 51 обобщенный сигнал Z состояния параллельных участков (данный сигнал формируется как результат операции "монтажное И" над сигналами состояния с выходов элементов 26 модулей системы).

Если хотя бы один из опрашиваемых параллельных участков не завершен, т. е. на выходе элемента 26 соответствующего модуля находится нулевой сигнал, сигнал с выхода элемента 26 соответствующего модуля поступает на линию 51 и определяет нулевое значение сигнала Z; в противном случае, т.е. когда все требуемые параллельные участки выполнены и на выходах элементов 26 всех модулей присутствуют сигналы логической единицы, на линии 51 устанавливается сигнал логической единицы (Z="1"). Состояния модулей, выполняющих или выполнивших участки микропрограммы, не входящие в заданное кодом Ts подмножество участков, не влияют на значение сигнала Z, поскольку на выходах соответствующих элементов И-НЕ 36, а следовательно, и элементов ИЛИ 26 находится сигнал логической единицы.

Ведущий модуль Mi спустя время, требуемое для формирования сигнала состояния параллельных участков Z, опрашивает состояние линии 51 и либо освобождает шину 50 и через некоторый промежуток времени T (при наличии незавершенных параллельных участков и нулевом уровне сигнала Z) вновь опрашивает состояние параллельных участков, либо выходит из состояния ожидания (при окончании требуемых параллельных участков и наличии единичного уровня сигнала на линии 51) и возобновляет выполнение микропрограммы.

Импульс p, выработанный ранее одновибратором 29 и задержанный элементом 45 на время dt, достаточное для установления сигнала Z на линии 51, с выхода элемента 45 поступает на счетный вход триггера 30, а также на первые входы элементов И 40.1, 40.2, на вторых входах которых появляется сигнал Z с линии 51.

1. Если Z="0", т.е. по меньшей мере один из контролируемых параллельных участков не завершен, то элемент 40.2 оказывается закрытым, а импульс p через открытый элемент 40.1 проходит на вход установки триггера 13 и переводит его в состояние логической единицы, инициируя тем самым процесс отсчета времени T. Триггер 31, а соответственно, и триггер 32 остаются в состоянии логического нуля, а нулевой сигнал с инверсного выхода триггера 13 блокирует элемент 38 и не допускает повторное срабатывание одновибратора 29. В то же самое время по срезу импульса p с выхода элемента 45 триггер 30 устанавливается в нулевое состояние; нулевой сигнал с прямого выхода триггера 30 переводит блок 33 в состояние высокого импеданса - текущий модуль освобождает шину 50 синхронизации параллельных участков, а единичный сигнал с инверсного выхода триггера 30 открывает элемент 36 и возвращает в активное состояние блок 34.

Единичный сигнал с прямого выхода триггера 13 включает генератор 14. Импульсы с выхода генератора 14 начинают поступать на счетный вход счетчика 15 времени ожидания и инициируют процесс счета от"00...0" до "11...1". Код с выхода счетчика подается на входы элемента И 41. Очередной импульс с выхода генератора 14 поступает на счетный вход счетчика 15 и срезом переводит его в очередное состояние. Если код на выходе счетчика является отличным от единичного, то на выходе элемента 41 сохраняется нулевой потенциал и процесс счета продолжается. При переходе счетчика в состояние "11...1" на выходе элемента 41 возникает единичный сигнал "Тайм-аут". Данный сигнал поступает на входы сброса счетчика 15 и триггера 13 и переводит их в исходное (нулевое) состояние. Таким образом, отсчет требуемого промежутка времени T завершается. Нулевой сигнал с прямого выхода триггера 13 останавливает генератор 14, а единичный сигнал с инверсного выхода открывает элемент И 38.

Как только сигнал на выходе элемента 35 приобретает единичное значение (что означает освобождение шины 50), на выходе элемента 38 возникает положительный перепад уровня сигнала, который воздействует на одновибратор 29 и вновь возбуждает на его выходе импульс p. Текущий модуль Mi снова выдает на шину 50 код НТС Ts и повторно опрашивает состояние параллельных участков. Если после реализации данного цикла опроса сигнал Z вновь принимает нулевое значение, то спустя время T, отсчитываемое счетчиком 15, i-й модуль снова осуществляет опрос состояния параллельных участков и т.д. Опрос производится до тех пор, пока сигнал Z не примет единичное значение.

2. Если Z="1", т.е. все опрашиваемые параллельные участки завершены, то элемент 40.1 оказывается заблокированным, а импульс p через открытый элемент 40.2 и элемент ИЛИ 27 проходит на вход установки триггера 32 и переводит триггер 32 в единичное состояние. Единичный сигнал с прямого выхода триггера 32 открывает элемент И 42, а нулевой сигнал с инверсного выхода блокирует элемент 38, не допуская повторного срабатывания одновибратора 29. Очередной тактовый импульс с третьего выхода генератора 6 проходит через открытый элемент 42 на вход установки триггера 31 и переключает его в состояние логической единицы.

Единичный сигнал с прямого выхода триггера 31 разрешает прохождение тактовых импульсов через элементы 39.1 и 39.2, а нулевой сигнал с инверсного выхода подтверждает блокировку элемента И 38. В то же время импульс с выхода элемента 42 поступает на счетный вход триггера 32 и срезом возвращает его в исходное состояние. Нулевой сигнал с прямого выхода триггера 32 блокирует элемент 42. Поскольку элемент 38 заблокирован нулевым сигналом с инверсного выхода триггера 31, появление единичного уровня сигнала на инверсном выходе триггера 32 не вызывает изменение уровня сигнала на выходе элемента 38, что обусловливает блокировку одновибратора 29. В то же самое время по срезу импульса p с выхода элемента 45 триггер 30 устанавливается в нулевое состояние; нулевой сигнал с прямого выхода триггера 30 переводит блок 33 в состояние высокого импеданса - текущий модуль освобождает шину 50, а единичный сигнал с инверсного выхода триггера 30 открывает элемент 36 и возвращает в активное состояние блок 34.

Импульс t1 с первого выхода генератора 6 через открытый элемент 39.1 проходит на вход синхронизации блока 2 и обеспечивает запись исполнительного адреса очередной микрокоманды, сформированного ранее с использованием содержимого полей 3.1 и 3.2 регистра 3, в регистр 61 адреса микрокоманды (фиг. 2). Формирование исполнительного адреса следующей микрокоманды происходит аналогично ранее рассмотренному (см. режим A). Адрес с выхода регистра 61 передается на адресный вход блока 1 (фиг.1), и текущий модуль Mi возобновляет выполнение микропрограммы, приостановленное на время синхронизации параллельных участков. На выходе блока 1 появляется следующая микрокоманда. Данная микрокоманда поступает на информационный вход регистра 3 и фиксируется в регистре 3 в момент появления фронта импульса t2 на его входе синхронизации. Далее работа устройства ничем не отличается от его функционирования при выполнении начального последовательного участка микропрограммы.

Таким образом, введение в устройство дополнительные элементы и обусловленные ими связи позволяют существенно расширить его функциональные возможности, а следовательно, и область целесообразного применения, обеспечивая возможность построения на его основе модульных мультимикропрограммных систем, реализующих сложные комплексы параллельных и последовательных микропрограмм, в том числе микропрограмм, содержащих значительное число точек распараллеливания и синхронизации параллельных участков. Применение введенных аппаратных и алгоритмических средств синхронизации параллельных участков позволяет исключить одновременное выполнение несовместимых микрокоманд (участков), что может иметь место при использовании прототипа. Максимальное число как параллельно выполняемых, так и одновременно инициализируемых или синхронизируемых (т.е. сходящихся к единой точке синхронизации) участков микропрограммы ограничивается только числом модулей в составе управляющей системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2146064C1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2166793C1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1999 |

|

RU2168198C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении алгоритмически распределенных устройств микропрограммного управления вычислительных и управляющих систем высокой производительности, реализующих параллельные алгоритмы обработки информации. Устройство содержит блок памяти микропрограмм, блок формирования адреса микрокоманд, регистр микрокоманд, N регистров передачи управления, триггер управления, два генератора тактовых импульсов, счетчики выборки и опроса, схему сравнения, дешифраторы выборки и опроса, две группы из N блоков тристабильных элементов, группу из N элементов ИЛИ-НЕ, три группы из N элементов И, три элемента ИЛИ, группу из N элементов задержки, одновибратор, формирователь признака принадлежности, счетчик времени ожидания, четыре триггера, два блока тристабильных элементов, элемент ИЛИ-НЕ, тринадцать элементов И, четыре элемента задержки. 1 з.п. ф-лы, 5 ил.

| DE, заявка, 3238566, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| FR, заявка, 2491654, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1168936, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1142832, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-07-27—Публикация

1997-02-18—Подача