4 4 Ю ;О vj

1144

Изобретение относится к измерительной технике и может быть использовано в системах автоматического контроля для многоканального широкодиапазонного измерения временных интервалов, а также для измерения и регистрации временных характеристик последовательности дискретных сигналов ,

Целью изобретения является расширение функциональных возможностей и диапазона измерений.

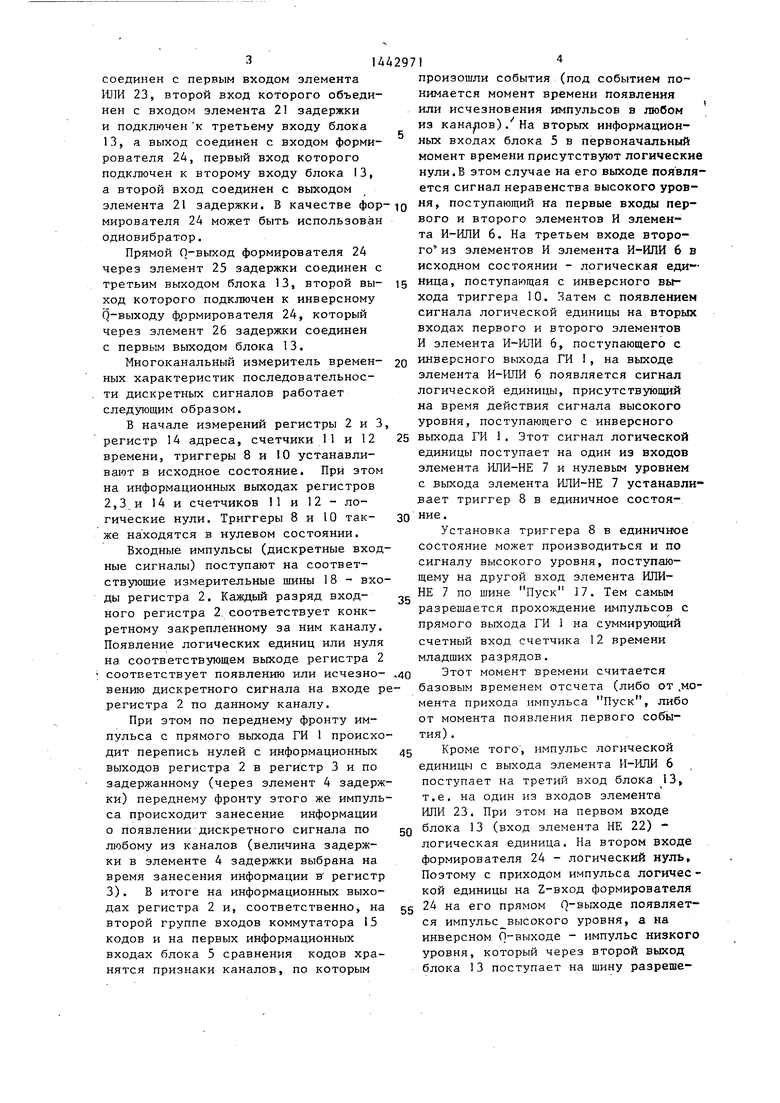

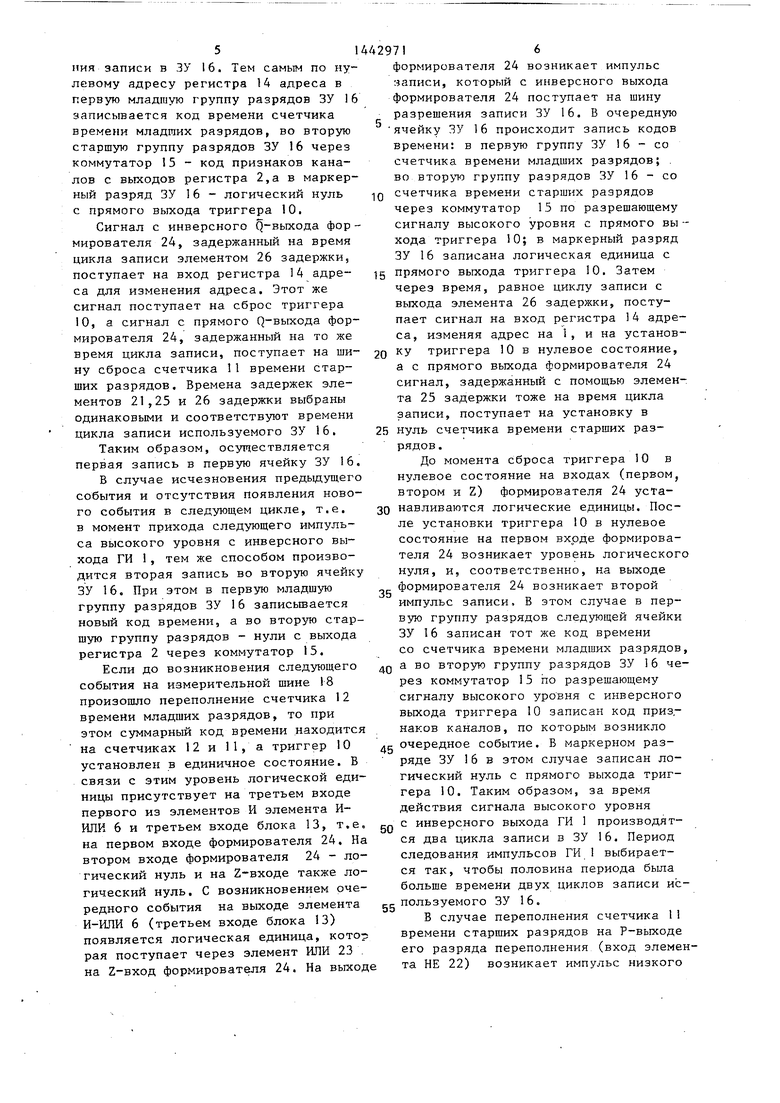

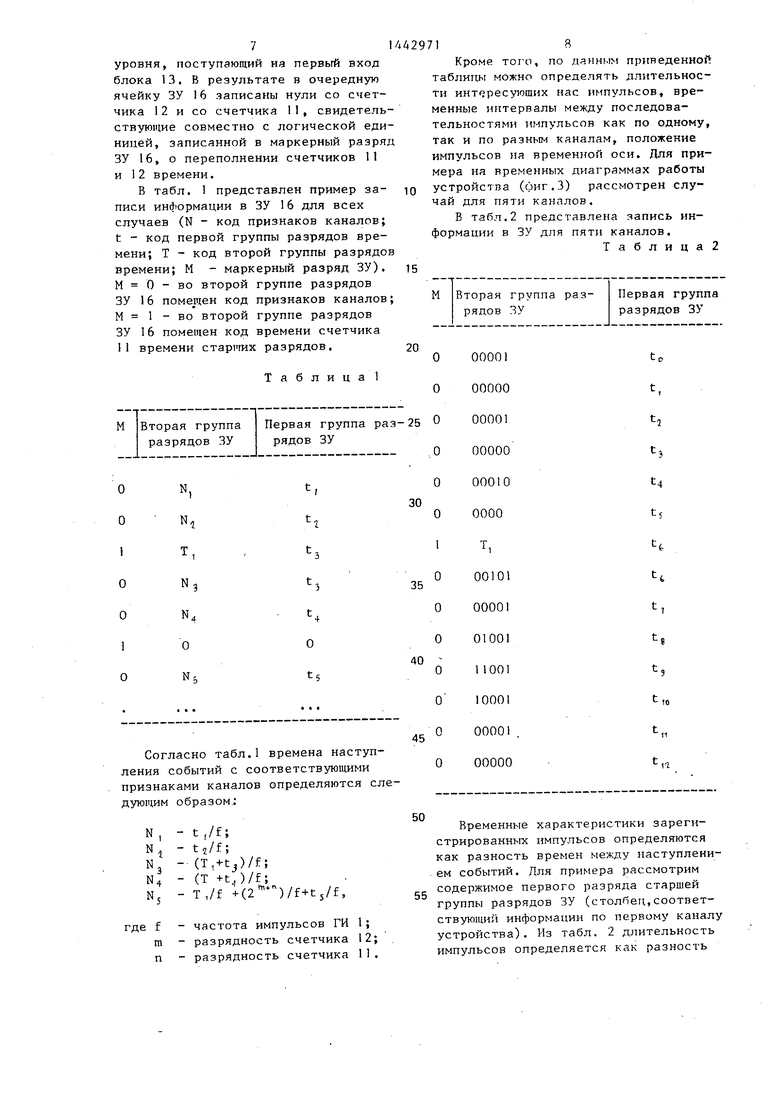

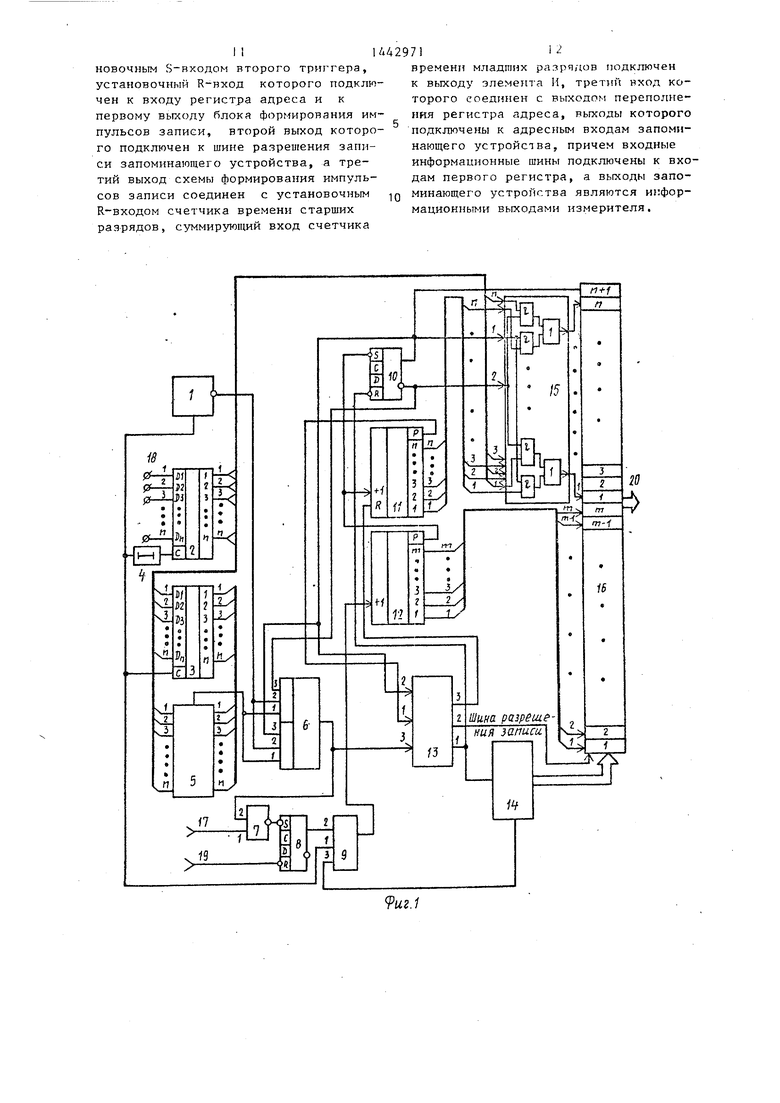

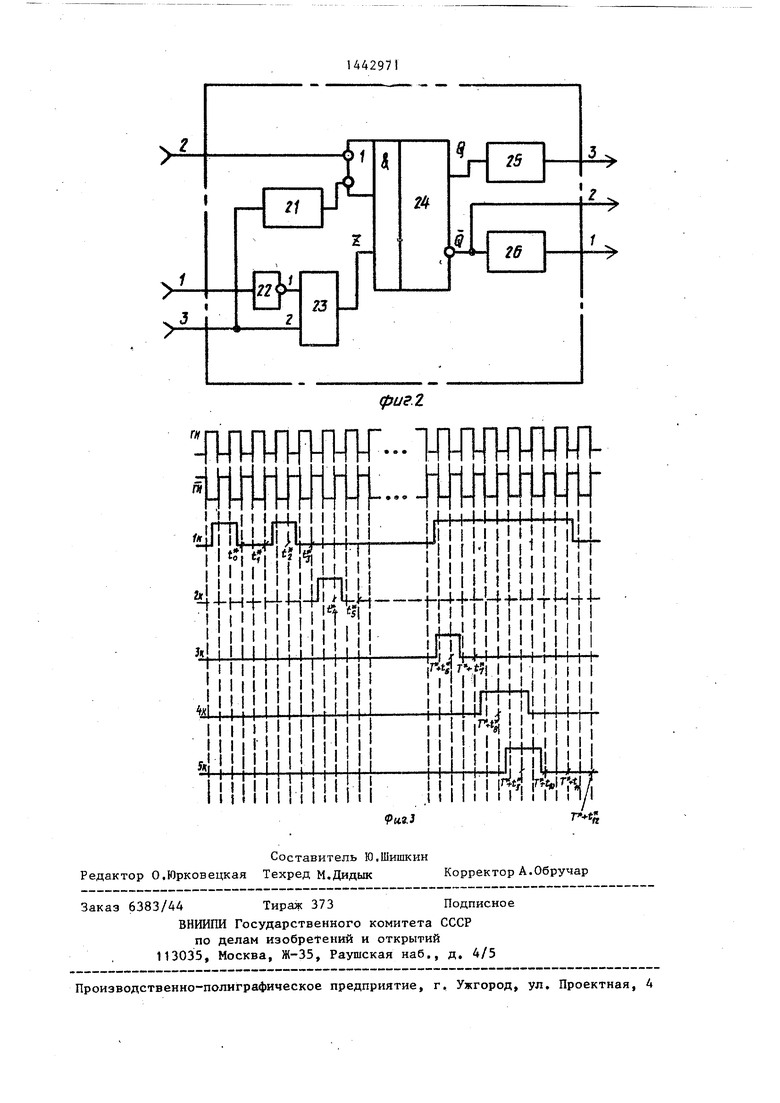

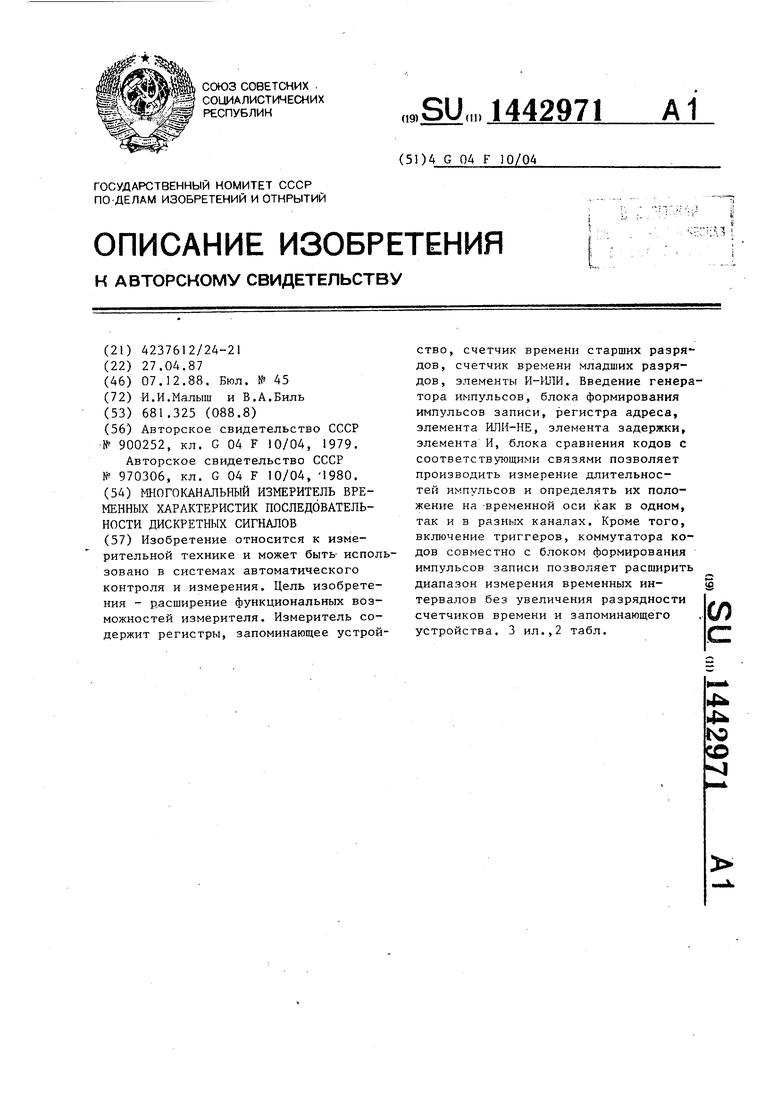

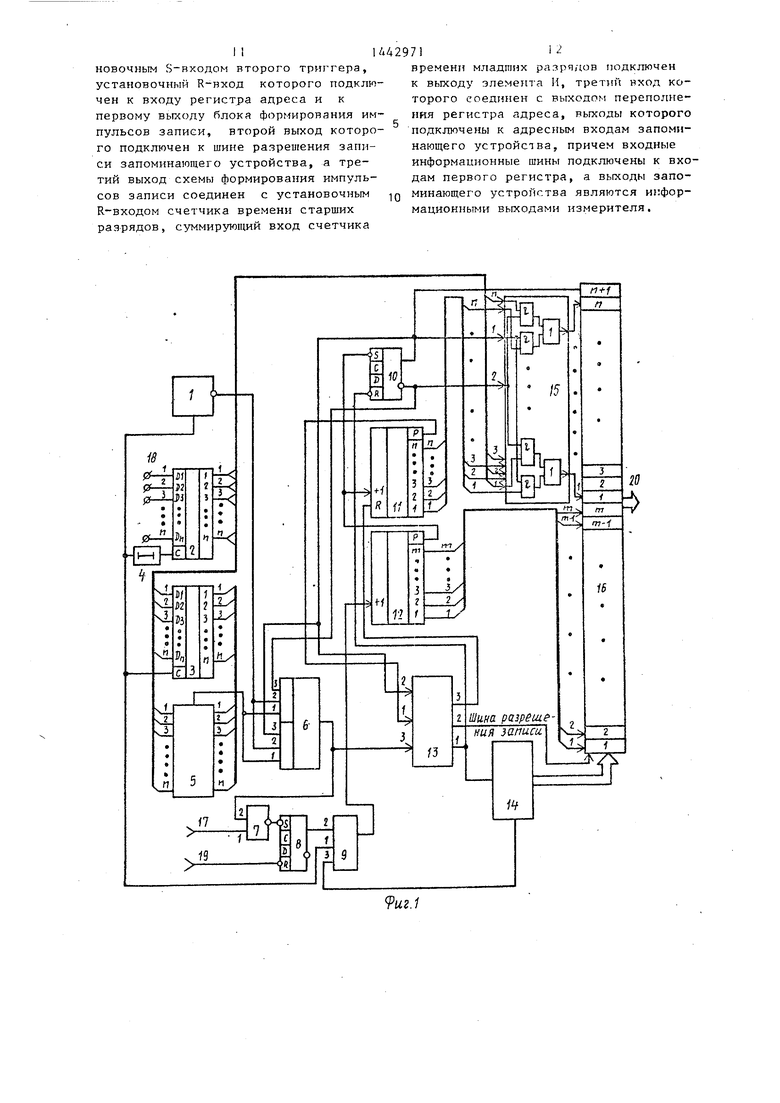

На фиг.1 приведена функциональная схема многоканального измерителя временных характеристик последовательности дискретных сигналов; на фиг.2 - пример выполнения блока формирования импульсов записи; на фиг.З - временные ди а г р аммы,

Измеритель содержит генератор импульсов (ГИ) 1, регистры 2 и 3, элемент 4 задержки, блок 5 сравнения кодов , элемент И-ИЛИ 6, элемент ИЛИ- НЕ 7, триггер 8, элемент И 9, триггер 0, счетчик 11 времени старших разрядов, счетчик 12 времени младших разрядов, блок 13 формирования импульсов записи, регистр 14 адреса, коммутатор 15 кодов, запоминающее устрой- ство (ЗУ) 16, шину Пуск 17, измерительные шины 18, шину Стоп 19 и группу выходных шин 20.

Первая группа входов блока 5 сравнения кодов соединена с информационными входами регистра 3 и информационными выходами регистра 2, синхро- вход которого подключен к выходу элемента 4 задержки. Вторые информационные входы блока 5 сравнения кодов соединены с информационными выходами регистра 3, синхровход которого подключен к прямому выходу генератора 1 импульсов, к входу элемента 4 задержки и к первому входу элемента И 9, второй вход которого соединен с прямым выходом триггера 8, которого подключен к шине 19 Стоп, а установочный Я-вход соединен с выходом элемента ИЛИ-НЕ 7, первый вход которого подключен к шине Пуск 17,, а второй вход соединен с третьим входом блока 13 формирования импульсов записи и с выходом элемента И- ИЛИ 6, первые входы дв ух элементов И

которого соединены с выходом блока 5 сравнения кодов, вторые входы подключены к инверсному выходу генератора 1 импульсов, а третий вход пер

0

0

5

5

О

5

0

5

0

5

вого из элементов И элемента И-ИЛИ 6 . соединен с прямым выходом триггера 10, с первым управляющим входом коммутатора 15 кодов, с маркерным разрядом запоминающего устройства 16 и с вторым входом блока 13 формирования импульсов записи, а третий вход второго из элементов И элемента И- ИЛИ 6 подклк1чен к инверсному выходу триггера 10 и второму управляющему входу коммутатора 15 кодов, информационные выходы которого подключены к второй группе разрядов запоминающего устройства 16.

Первая группа информационных вхо- дов коммутатора 15 кодов соединена с информационными выходами регистра 2, а вторая группа информационных входов коммутатора i 5 кодов подключена соответственно к информационным выходам счетчика 11 времени старших разрядов, разряд переполнения которого соединен с первым входом блока 13 формирования импульсов записи, а разряд переполнения счетчика 12 времени младших разрядов соединен с суммирующим входом счетчика I времени старших разрядов и с установочным S-входом триггера 10, R-вход которого подключен к входу регистра 14 адреса и к первому выходу блока 13 формирования импульсов записи, второй выход которого подключен к шине разрешения записи запоминающего устройства 16, а третий выход блока 13 формирования импульсов записи соединен с установочным входом счетчика 11 времени старших разрядов, Суммирующий вход счетчика 12 времени младших разрядов подключен к выходу элемента И 9, третий вход которого соединен с выходом переполнения регистра 14 адреса, выходы которого подключены к адресным входам запоминающего устройства 1 б. Информационные выходы счетчика 12 времени младших разрядов подключены к первой группе разрядов запоминающего устройства 16. Цепи питания и установки устройства в исходное состояние (цепи сброса) на фиг,1 не показаны.

Блок 13 формирования импульсов записи (фиг.2) содержит элемент 21 задержки, элемент НЕ 22, элемент ИЛИ 23, формирователь 24 и элементы 25 и 26 задержки.

Первый вход блока 13 формирования импульсов записи через элемент НЕ 22

3

соединен с первым входом элемента Ш1И 23, второй вход которого объединен с входом элемента 21 задержки и подключен к третьему входу блока 13, а выход соединен с входом формирователя 24, первый вход которого подключен к второму входу блока 13, а второй вход соединен с выходом

ДА2971

произошли события (лод событием понимается момент времени появления или исчезновения импульсов в любом из каналов)/На вторых информационных входах блока 5 в первоначальный момент времени присутствуют логические нули.В этом случае на его выходе поя вля- ется сигнал неравенства высокого уров

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1543232A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1385294A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

Изобретение относится к измерительной технике и может быть использовано в системах автоматического контроля и измерения. Цель изобретения - р,асширение функциональных возможностей измерителя. Измеритель содержит регистры, запоминающее устройство, счетчик времени старших разрядов, счетчик времени младших разрядов, элементы И-ИЛИ. Введение генератора импульсов, блока формирования импульсов записи, регистра адреса, элемента ИЛИ-НЕ, элемента задержки, элемента И, блока сравнения кодов с соответствующими связями позволяет производить измерение длительностей импульсов и определять их положение на -временной оси как в одном, так и в разных каналах. Кроме того, включение триггеров, коммутатора кодов совместно с блоком формирования импульсов записи позволяет расширить диапазон измерения временных интервалов без увеличения разрядности счетчиков времени и запоминающего устройства. 3 ил.,2 табл. (Л

элемента 21 задержки. В качестве фор- ю поступающий на первые входы пермирователя 24 может быть использован одновибратор.

Прямой О-выход формирователя 24 через элемент 25 задержки соединен с третьим выходом блока 13, второй выход которого подключен к инверсному Q-выходу фррмирователя 24, который через элемент 26 задержки соединен с первым выходом блока 13.

Многоканальный измеритель временных характеристик последовательности дискретных сигналов работает следующим образом.

В начале измерений регистры 2 и 3 регистр 14 адреса, счетчики 11 и 12 времени, триггеры 8 и 10 устанавливают в исходное состояние. При этом на информационных выходах регистров 2,3 и 14 и счетчиков 11 и 12 - логические нули. Триггеры 8 и 10 также находятся в нулевом состоянии.

Входные импульсы (дискретные входные сигналы) поступают на соответствующие измерительные шины 18 - входы регистра 2. Каждый разряд входного регистра 2. соответствует конкретному закрепленному за ним каналу. Появление логических единиц или нуля на соответствующем выходе регистра 2 соответствует появлению или исчезновению дискретного сигнала на входе р регистра 2 по данному каналу.

При этом по переднему фронту импульса с прямого выхода ГИ 1 происходит перепись нулей с информационных выходов регистра 2 в регистр 3 и по задержанному (через элемент 4 задержки) переднему фронту этого же импульса происходит занесение информации о появлении дискретного сигнала по любому из каналов (величина задержки в элементе 4 задержки выбрана на время занесения информации в регистр 3). В итоге на информационных выходах регистра 2 и, соответственно, на второй группе входов коммутатора 15 кодов и на первых информационных входах блока 5 сравнения кодов хранятся признаки каналов, по которым

5

5

0

5

0

5

0

5

вого и второго элементов И элемента И-ИЛИ 6. На третьем входе второго из элементов И элемента И-ИЛИ 6 в исходном состоянии - логическая единица, поступающая с инверсного выхода триггера 10. Затем с появлением сигнала логической единицы на вторых входах первого и второго элементов И элемента И-ИЛИ 6, поступающего с инверсного выхода ГИ I, на выходе элемента И-ИЛИ 6 появляется сигнал логической единицы, присутствующий на время действия сигнала высокого уровня, поступающего с инверсного выхода ГИ 1. Этот сигнал логической единицы поступает на один из входов элемента ИЛИ-НЕ 7 и нулевым уровнем с вькода элемента ИЛИ-НЕ 7 устанавливает триггер 8 в единичное состояние.

Установка триггера 8 в единичное состояние может производиться и по сигналу высокого уровня, поступающему на другой вход элемента ИЛИ- НЕ 7 по шине Пуск J7. Тем самым разрешается прохождение импульсов с прямого выхода ГИ J на о ммирующий счетный вход счетчика 12 времени младших разрядов.

Этот момент времени считается базовым временем отсчета (либо от .момента прихода импульса Пуск, либо от момента появления первого события) .

Кроме того, импульс логической единицы с выхода элемента И-ИЛИ 6 поступает на третий вход блока 13, т.е. на один из входов элемента ИЛИ 23. При этом на первом входе блока 13 (вход элемента НЕ 22) - логическая единица. На втором входе формирователя 24 - логический нуль. Поэтому с приходом импульса логичес - кой единицы на Z-вход формирователя 24 на его прямом Q-выходе появляется импульс BEiicoKoro уровня, а на инверсном 0-выходе - импульс низкого уровня, который через второй выход блока 13 поступает на щину разреше

ПИЯ записи в ЗУ 16. Тем самым по нулевому адресу регистра 14 адреса в первую младшую группу разрядов ЗУ 16 записывается код времени счетчика времени младших разрядов, во вторую старшую группу разрядов ЗУ 16 через коммутатор 15 - код признаков каналов с выходов регистра 2,а в маркерный разряд ЗУ 16 - логический нуль с прямого выхода триггера 10,

Сигнал с инверсного Q-выхода фор - мирователя 24, задержанный на время цикла записи элементом 26 задержки, поступает на вход регистра 14 адре- са для изменения адреса. Этот же сигнал поступает на сброс триггера 10, а сигнал с прямого Q-выхода формирователя 24, задержанный на то же время цикла записи, поступает на ши- ну сброса счетчика 11 времени старших разрядов. Времена задержек элементов 21,25 и 26 задержки выбраны одинаковыми и соответствуют времени цикла записи используемого ЗУ 16.

Таким образом, осуществляется первая запись в первую ячейку ЗУ 16, В случае исчезновения предыдущего события и отсутствия появления нового события в следующем цикле, т.е, в момент прихода следующего импульса высокого уровня с инверсного выхода ГИ 1, тем же способом производится вторая запись во вторую ячейку ЗУ 16, При этом в первую младшую группу разрядов ЗУ 16 записывается новый код времени, а во вторую старшую группу разрядов - нули с выхода регистра 2 через коммутатор 15,

Если до возникновения следующего события на измерительной шине 8 произошло переполнение счетчика 12 времени младших разрядов, то при этом суммарный код времени находится на счетчиках 12 и 11, а триггер 10 установлен в единичное состояние, В связи с этим уровень логической единицы присутствует на третьем входе первого из элементов И элемента И- ИЛИ 6 и третьем входе блока 13, т,е на первом входе формирователя 24, На втором входе формирователя 24 - логический нуль и на Z-входе также логический нуль, С возникновением очередного события на выходе элемента И-ИЛИ 6 (третьем входе блока 13) появляется логическая единица, котор рая поступает через элемент ИЛИ 23 на Z-вход формирователя 24. На выход

.

5

О

д 5 Q g

5

формирователя 24 возникает импульс записи, который с инверсного выхода формирователя 24 поступает на шину разрешения записи ЗУ 16, В очередную ячейку ЗУ 16 происходит запись кодов времени: в первую группу ЗУ 6 - со счетчика времени младших разрядов; . во вторую группу разрядов ЗУ 16 - со счетчика времени старших разрядов через коммутатор 15 по разрешающему сигналу высокого уровня с прямого вы хода триггера 10; в маркерный разряд ЗУ 16 записана логическая единица с прямого выхода триггера 10. Затем через время, равное циклу записи с выхода элемента 26 задержки, поступает сигнал на вход регистра 14 адреса, изменяя адрес на 1, и на установку триггера 10 в нулевое состояние, а с прямого выхода формирователя 24 сигнал, задержанный с помощью элемента 25 задержки тоже на время цикла записи, поступает на установку в нуль счетчика времени старших разрядов ,

До момента сброса триггера 10 в нулевое состояние на входах (первом, втором и Z) формирователя 24 устанавливаются логические единицы. После установки триггера 10 в нулевое состояние на первом входе формирователя 24 возникает уровень логического нуля, и, соответственно, на выходе формирователя 24 возникает второй импульс записи, В этом случае в первую группу разрядов следующей ячейки ЗУ 16 записан тот же код времени со счетчика времени младших разрядов, а во вторую группу разрядов ЗУ 16 через коммутатор 15 по разрешающему сигналу высокого уровня с инверсного выхода триггера 10 записан код приз,- наков каналов, по которым возникло очередное событие, В маркерном разряде ЗУ 16 в этом случае записан логический нуль с прямого выхода триггера 10, Таким образом, за время действия сигнала высокого уровня с инверсного выхода ГИ 1 производятся два цикла записи в ЗУ 16, Период следования импульсов ГИ 1 выбирается так, чтобы половина периода была больше времени двух циклов записи используемого ЗУ 16,

В случае переполнения счетчика 11 времени старших разрядов на Р-выходе его разряда переполнения (вход элемента НЕ 22) возникает импульс низкого

уровня, поступающий на первый вход блока 13, В результате в очередную ячейку ЗУ 16 записаны нули со счетчика 12 и со счетчика 11, свидетельствующие совместно с логической единицей, записанной в маркерный разряд ЗУ 16, о переполнении счетчиков 11 и 12 времени.

В табл. 1 представлен пример за- писи информации в ЗУ 16 для всех случаев (N - код признаков каналов; t код первой группы разрядов времени; Т - код второй группы разрядов времени; М - маркерный разряд ЗУ). М О - во второй группе разрядов ЗУ 16 помегцен код признаков каналов; М 1 - во второй группе разрядов ЗУ 16 помещен код времени счетчика 11 времени разрядов.

Кроме того, по данным приведенной таблицы можно определять длительности интересующих нас импульсов, временные интервалы между последовательностями импульсов как по одному, так и по разным каналам, положение импульсов на временной оси. Для примера на временных диаграммах работы устройства (фиг.З) рассмотрен слу чай для пяти каналов.

В табл.2 представлена запись информации в ЗУ для пяти каналов.

Таблица2

времен между моментами появления первой единицы после нулей и моментом появления первого нуля после единиц в данном столбце.

Временной интервал между импульсами определяется как разность времен между моментами появления единиц, следующих за нулями. Например, для первого канала временной интервал между моментами появления второго .и третьего импульсов определяется выражением

t lTii t4i:t2 , f

Tf.

a длительность третьего импульса - выражением

- t:

/г

tn - tfe

где t; и Т

коды времен, находящиеся в первой и второй группах разрядов ЗУ 16i

t и тТ - времена, соответствующие этим кодам. Процесс регистрации и измерения заканчивается или по сигналу низкого уровня с выхода переполнения регист-, ра 14 адреса, поступающему на третий вход элемента И 9, или по импульсу Стоп, поступающему по шине 19 на установочный R-вход триггера 8.

Изобретение позволяет определять наряду с временными интервалами длительности дискретных импульсов и положение их на временной оси как . в отдельном канале, так и в разных каналах. Кроме того, изобретение позволяет расширить диапазон измерений без увеличения емкости счетчиков времени и запоминающего устройства.

Фо рмулаи

зобретения 45 Формирования импульсов записи, а

третий вход-второго из элементов элемента И-РШИ соединен с инверсн выходом второго триггера и с втор управляющим входом коммутатора ко

Многоканальный измеритель временных характеристик последовательности дискретных сигналов, содержащий два регистра, элемент И-ИЛИ, запоминаю - щее устройство, коммутатор, счетчик времени старших разрядов, счетчик времени младших разрядов, группы входных и выходных шин, информационные выходы счетчика времени младших разрядов соединены с первой группой входов запоминающего устройства, к второй группе входов которого, подключены выходы коммутатора, первая

группа входов которого соединена с | информационными выходами счетчика вре мени старших разрядов, отличающийся тем, что, с целью расширения функциональных возможностей и диапазона измерений, в него дополнительно введены генератор импульсов, блок формирования импульсов записи,

два триггера, регистр адреса, элемент ИЛИ-НЕ, элемент задержки, элемент И и блок сравнения кодов, первая группа информационных входов которого соединена соответственно с информационньгми входами второго регистра и информационными выходами первого регистра, синхровход которого соединен с выходом.линии задержки, вторая группа информационных входов блока

сравнения кодов соединена с информационными выходами второго регистра, синхровход которого подключен к прямому выходу генератора импульсов, к входу элемента задержки и к первому

входу элемента И, второй вход которого соединен с прямым выходом пер- .вого триггера, R-вход которого соединен с шиной Стоп, а установочньй S-вход которого подключен к выходу

элемента ИЛИ-НЕ, первый вход которого соединен с шиной Пуск, а второй -вход подключен к третьему входу блока формирования импульсов записи и к выходу элемента И-ИЛИ,первые входы двух элементов И которого соеди

нены с выходом блока сравнения кодов , вторые входы подключены к инверсному выходу генератора импульсов, а третий вход первого из элементов И

элемента И-ИЛИ соединен с прямым выходом второго триггера, с первым управляющим входом коммутатора кодов, с маркернь М разрядом запоминающего . устройства и с вторым входом блока

45 Формирования импульсов записи, а

третий вход-второго из элементов И элемента И-РШИ соединен с инверсным выходом второго триггера и с вторым управляющим входом коммутатора коgQ дов, вторая группа информационных входов которого соединена с информационными выходами первого регистра, разряд переполнения счетчика времени старших разрядов соединен с перgg вьтм входом блока формирования импульсов записи, а разряд переполнения счетчика времени младших разрядов соединен с суммирующим входом счетчика времени старших разрядов и с установочным S-входом второго триггера, установочный R-вход которого подклю чен к входу регистра адреса и к первому выходу блока формирования им пульсов записи, второй выход которого подключен к шине разрешения записи запоминающего устройства, а третий выход схемы формирования импульсов записи соединен с установочным R-входом счетчика времени старших разрядов, суммирующий вход счетчика

времени младгаих разрч,чов подключен к выходу элемента И, третий вход которого соединен с выходом переполнения регистра адреса, выходы которого подключены к адресным входам запоминающего устройства, причем входные информационные шины подключены к входам первого регистра, а выходы запо- 1Q минающего устройства являются информационными выходами измерителя.

:j

г- // -I

23

Составитель Ю.Шишкин Редактор О.Юрковецкая Техред М.Дидык Корректор А.Обручар

Заказ 6383/44 Тираж 373Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

a

25

2

(ft и г. 2

.9.3

| Устройство для многоканальной регистрации временных характеристик процессов | 1980 |

|

SU900252A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Многоканальный измеритель временных интервалов | 1981 |

|

SU970306A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-12-07—Публикация

1987-04-27—Подача