во

Изобретение относится к вьр|исли- тельной технике и может быть использовано в системах контроля информации в р-кодах Фибоначчи.

Целью изобретения является повышение помехозап(ищенности устройства.

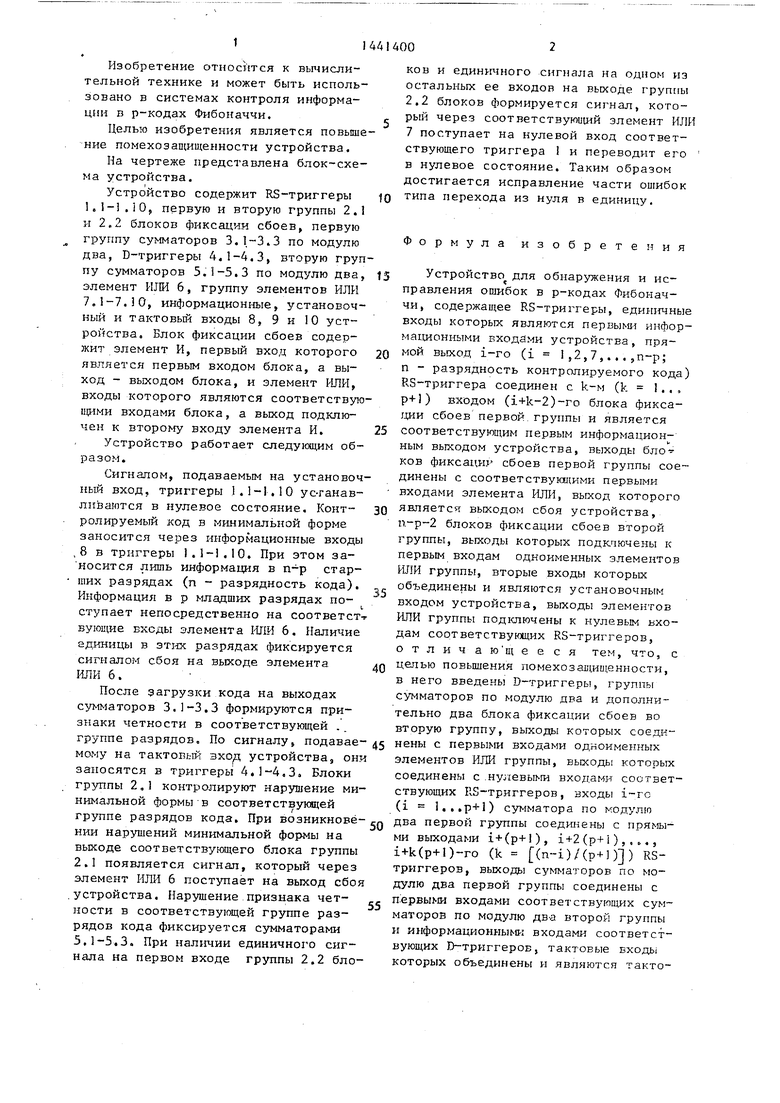

На чертеже представлена блок-схема устройства.

Устройство содержит RS-триггеры .l-l.iOj первую и вторую группы 2.1 и 2.2 блоков фиксации сбоев, первую группу сумматоров 3.1-3.3 по модулю два, D-триггеры 4.1-4.3, вторую группу сумматоров 5.1-5.3 по модулю два, элемент ИЛИ 6, группу элементов ИЛИ 7,1-7.О, информационные, установочный и тактовый входы 8, 9 и 10 устройства. Блок фиксации сбоев содержит элемент И, первый вход которого является первым входом блока, а выход - выходом блока, и элемент ИЛИ, входы которого являются соответствую- Ц1ДМИ входами блока, а выход подключен к второму входу элемента И.

Устройство работает следующим образом.

Сигналом, подаваемым на установочный вход, триггеры 1.1-1.10 ус-ганав- ливаются в нулевое состояние. Контролируемый код в минимальной форме заносится через информационные входы ,8 в триггеры 1.1-i.IO. При этом за- носится лишь информация в п-р старших разрядах (п - разрядность кода). Информация в р младших разрядах поступает непосредственно на соответст вующие входы элемента liTIH 6. Наличие единицы в этих разрядах фиксируется сигналом сбоя на выходе элемента I-UIH 6.

После загрузки кода на выходах сумматоров 3.1-3,3 формируются признаки четности в соответствующей .. группе разрядов. По сигналу, подаваемому на тактовый зхо устройства, они заносятся в триггеры ,3a Блоки группы 2,1 контролируют нарушение минимальной формы В соответствующей группе разрядов кода. При возникновении нарушений минимальной формы на выходе соответствуннцего блока группы 2.1 появляется сигнал, который через элемент ИЛИ 6 поступает на выход сбоя .устройства. Нарушение признака четности в соответствующей группе разрядов кода фиксируется сумматорами 5.1-5.3. При наличии единичного сигнала на первом входе группы 2.2 бло

ков и единичного сигнала на одном из остальнь х ее входов на выходе группы 2,2 блоков формируется сигнал, который через соответствуюишй элемент ИЛИ 7 поступает на нулевой вход соответствующего триггера 1 и переводит его в нулевое состояние. Таким образом достигается исправление части ошибок типа перехода из нуля в единицу.

5

0

5

0

5

0

5

0

5

Формула изобретения

Устройство для обнаружения и исправления ошибок в р-кодах Фибоначчи, содержащее RS-триггеры, единичные входы которых являются первыми информационными входами устройства, прямой выход i-ro (i 1 ,2,7,...,n-p; п - разрядность контролируемого кода) RS-триггера соединен с k-м (k I... р+1) входом Ci+k-2)-ro блока фиксации сбоев первой, группы и является соответствующим первым информационным выходом устройства, выходы бло ков фиксации сбоев первой группы соединены с соответствукщими первыми входами элемента ИЛИ, выход которого является выходом сбоя устройства, гг-р-2 блоков фиксации сбоев второй группы, выходы которых подкпючены к первым входам одноименных элементов ШШ группы, вторые входы которых объединены и являются установочным входом устройства, выходы элементов ИЛИ группы подключены к нулевым входам соответствующих RS-триггеров, о т л и ч а ю щ е е с я тем, что, с целью повьшения помехозащищенности, в него введены D-триггеры, группы сумматоров по модулю два и дополнительно два блока фиксации сбоев во вторую группу, выходы которых соединены с первыми входами одноименных элементов ИЛИ группы, выходь которых соединены с нулевьп ги входами соответствующих IlS-триггеров, входы i-rc (i i,.,p+l) сумматора по модулю два первой группы соединены с прямыми выходами i+(p+I), i+2 (р+1 ),..., i+k(p+l)-ro (k (n-i)/(p+l)) RS- триггеров, выходы сумматоров по модулю два первой группы соединены с первыми входами соответствующих сумматоров по модулю дв-а второй группы и информационными входами соответствующих D-триггеров, тактовые входь которых объединены и являются такто .

вым пходом устройства, а выходы сое-цин сбоев второй группы, k-i i (k

динены с вторыми вкодамн соответст- 2.,,р4-1) вход i-ro блока фиксации

вутощих сумматоров по модулю два вто-сбоев второй группы подключен к выхорой группы, выход i-ro сумматора поду (i+k-2)-ro блока фиксации сбоевмодулю два второй группы соединен спервой группы, вторые входы элемента

соответстБутио-1м входом элемента ИЛИИЛИ являются соответствующими вторыми

и первыми входами i, Ср),...,информационными входами и выходами

+2 (р+1),..., (p- -l )-х блоков фикса-устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок | 1987 |

|

SU1578811A1 |

| Устройство для обнаружения ошибок в пакетном @ -коде | 1987 |

|

SU1483645A1 |

| Генератор случайных чисел | 1984 |

|

SU1310813A1 |

| Устройство для обнаружения и исправления однократных ошибок оптимальных р-кодов Фибоначчи | 1987 |

|

SU1479932A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1982 |

|

SU1086437A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| Устройство для умножения | 1988 |

|

SU1501047A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах контроля информации в р-кодах Фибоначчи. Целью изобретения является повьпиение помехоустойчивости устройства. Устройство содержит ES-триггеры 1.1-1.10, первую и вторую группы 2,1 и 2.2 блоков фиксации сбоев, первую группу сумматоров 3.1-3.3 по модулю два, D-триг- геры 4.1-4.3, вторую группу сумматоров 5.1-5.3 по модулю два, элемент ИЛИ 6, группу элементов ИЛИ 7.1-7.10, информационные, установочный и тактовый входы 8, 9 и 10 устройства. Блок фиксации сбоев содержит элемент И, первьй вход которого является первым входом блока, а вьпсод - выходом блока, и элемент ИЛИ, входы которого являются соответствующШ П входами блока, а выход подключен к второму входу элемента И. 1 ил.

| Гидрокопировальный станок | 1960 |

|

SU136155A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-30—Публикация

1986-07-16—Подача