Изобретение относится к цифровой вычислительной технике и предназна- чено для использования в универсаль ных и специализированных цифровых

Вычислительных устройствах.

Целью изобретения является расширение функциональных возможностей за счет обеспечения умножения чисел, представленных в дополнительном ко-

. де.

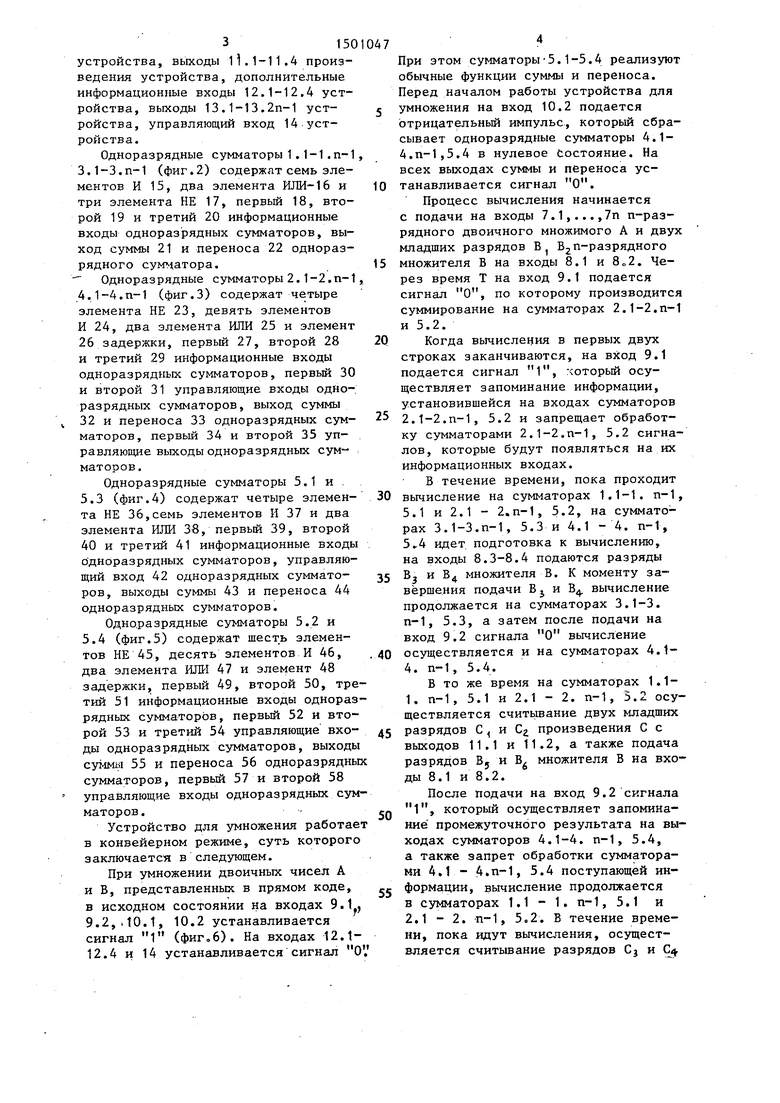

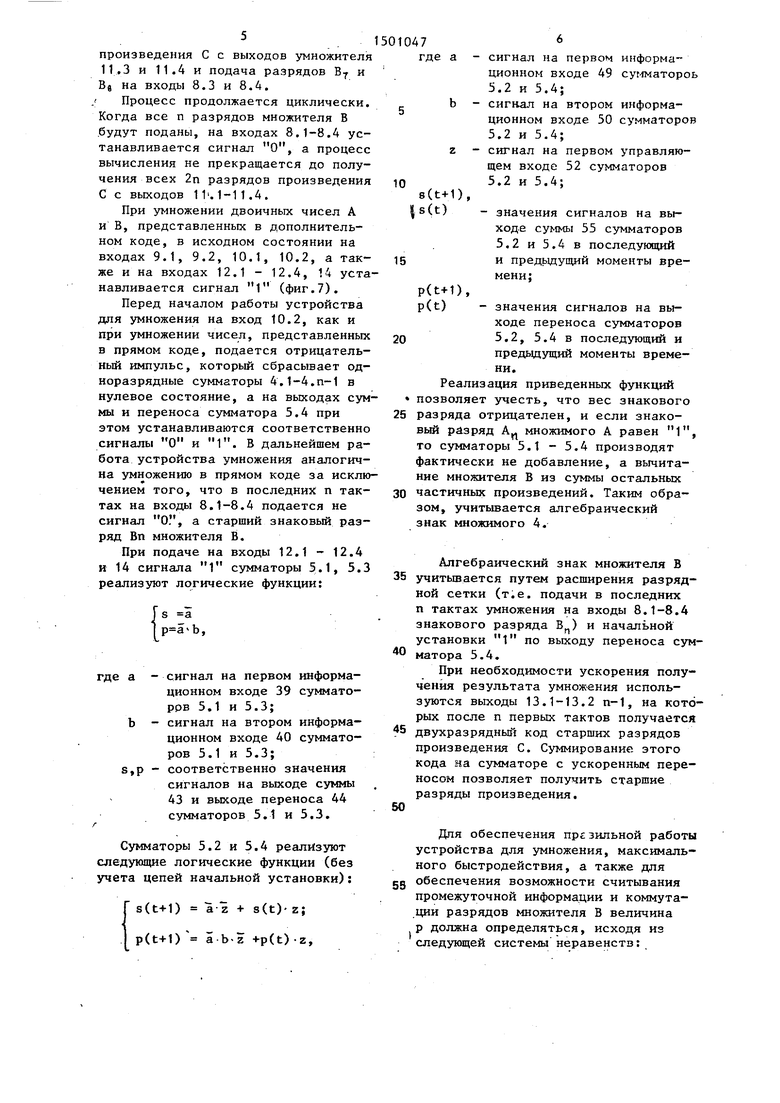

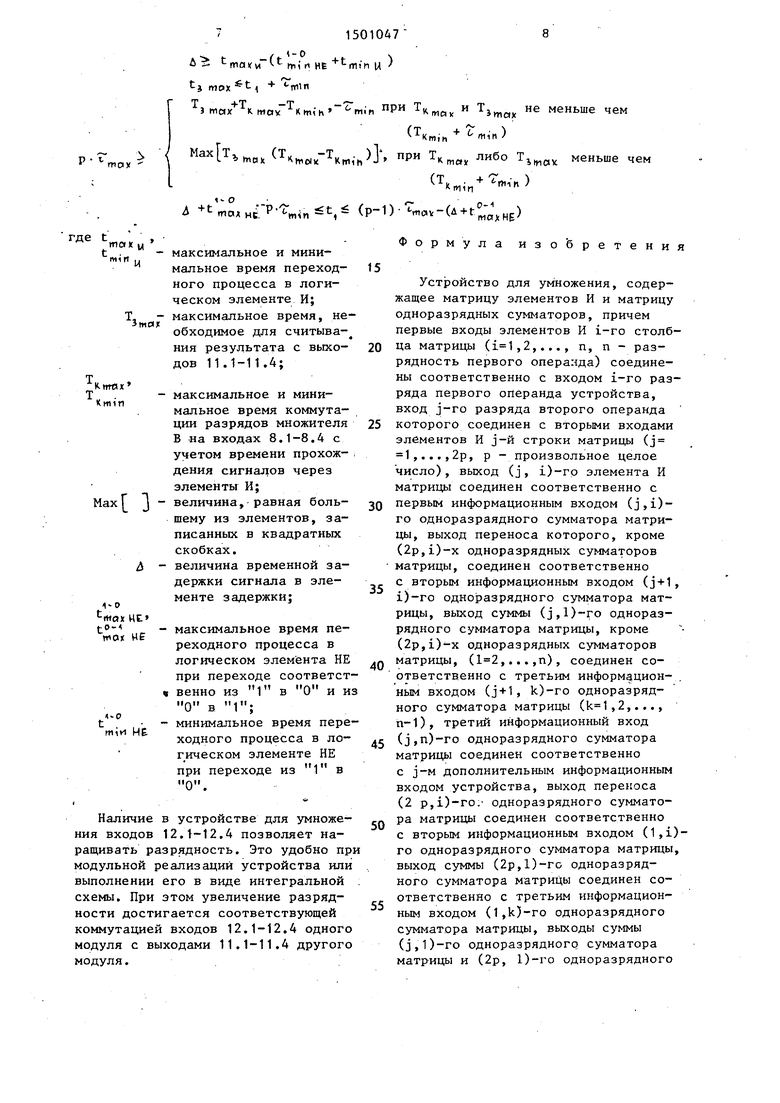

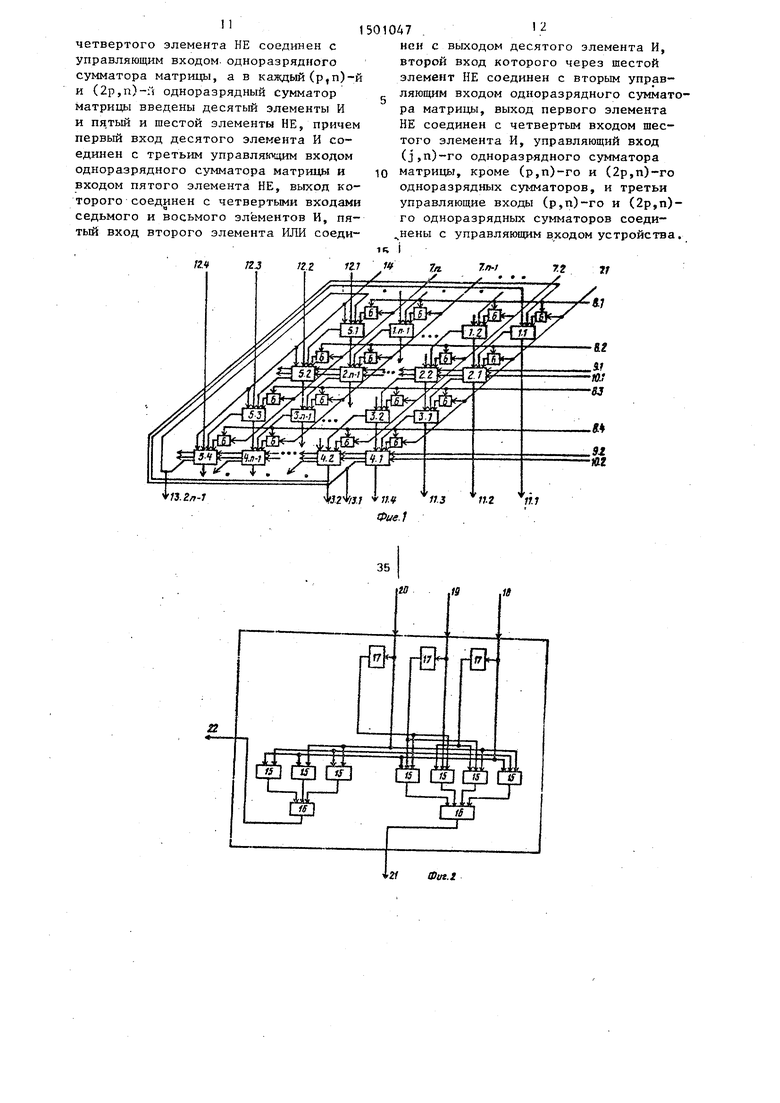

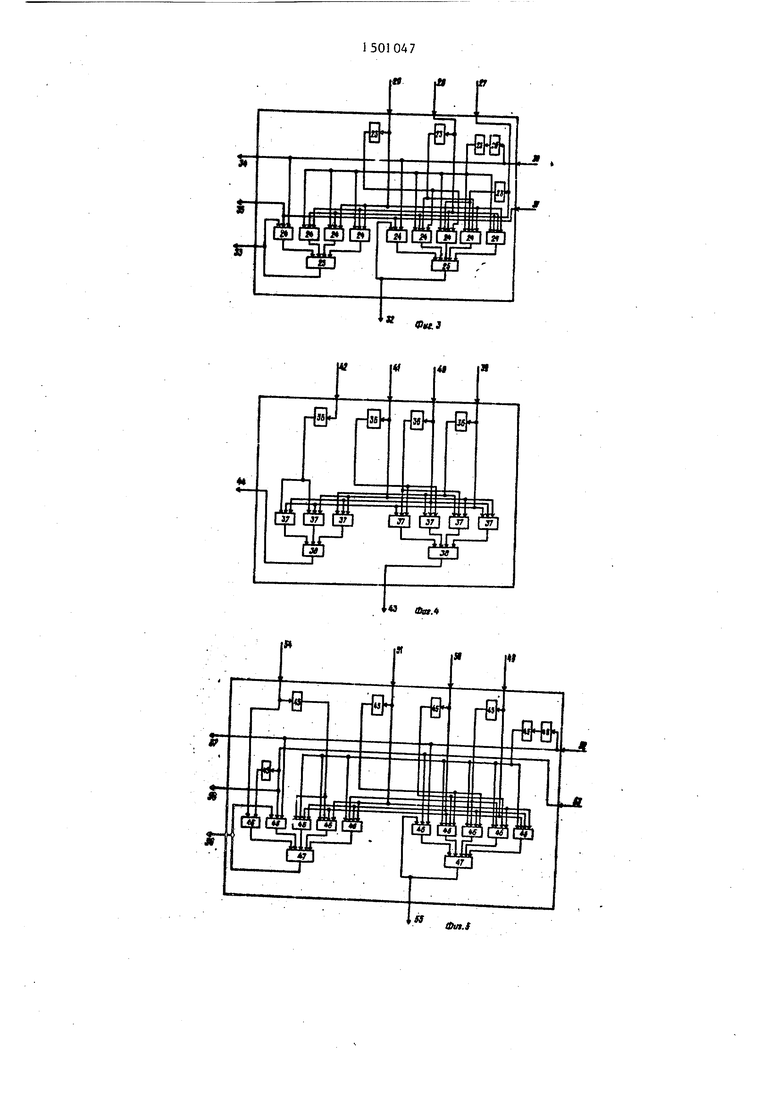

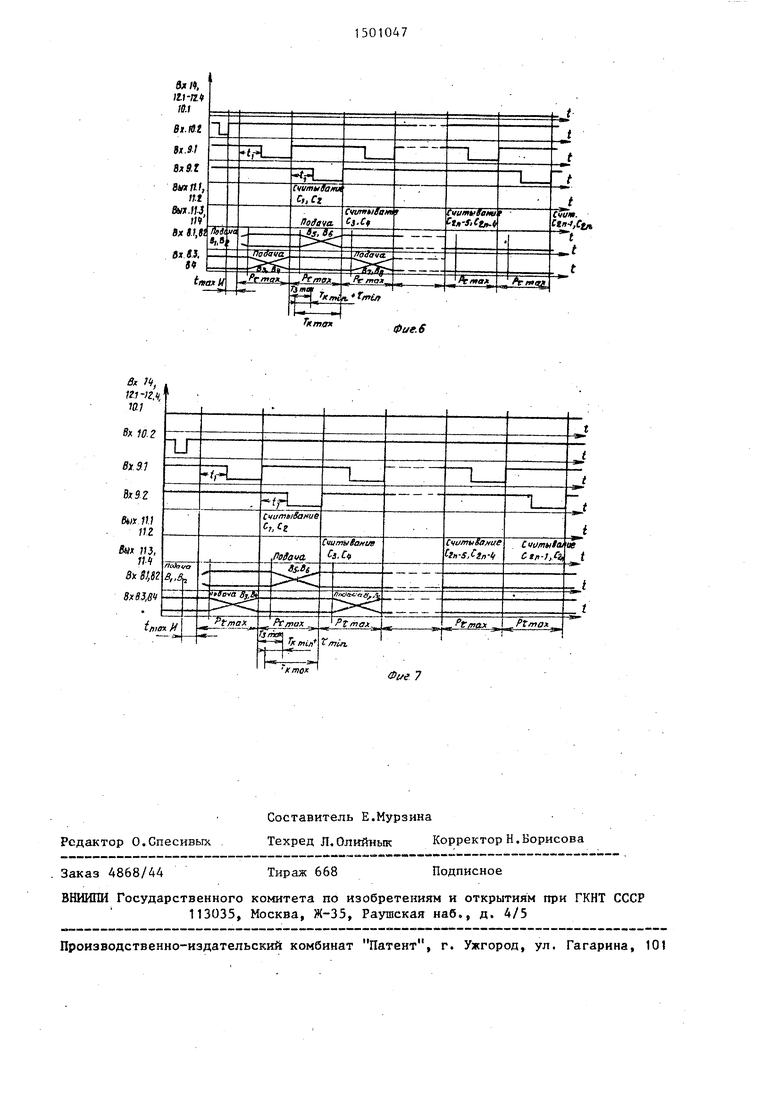

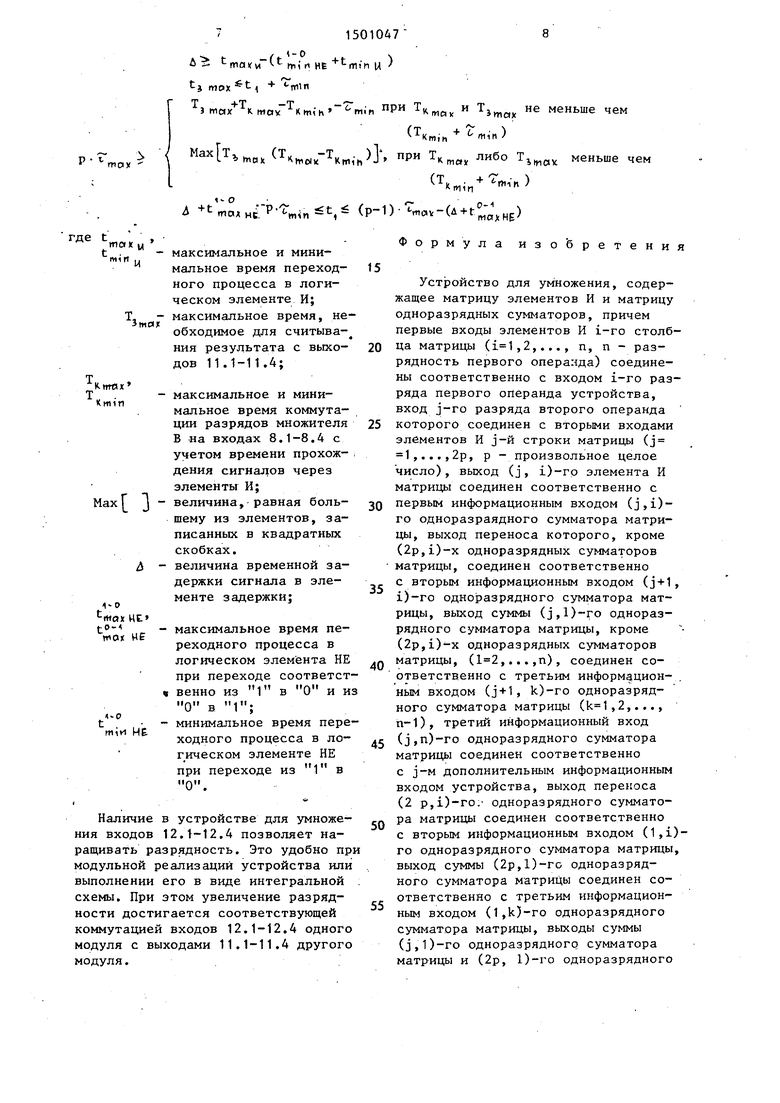

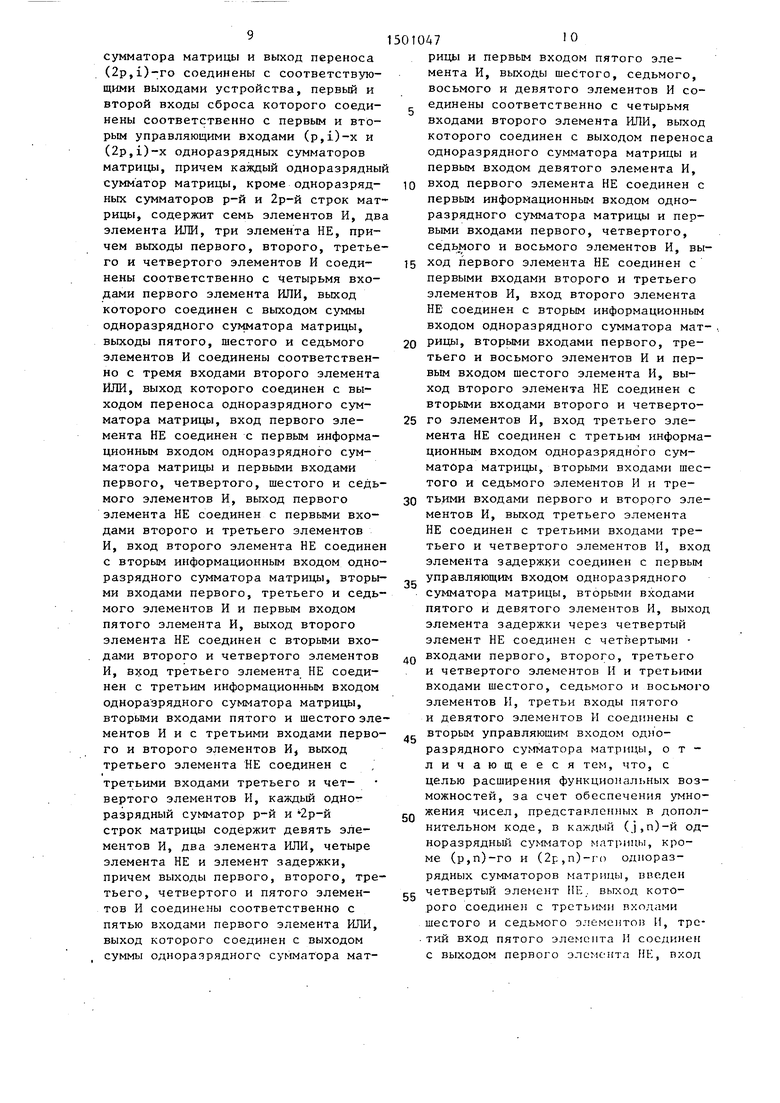

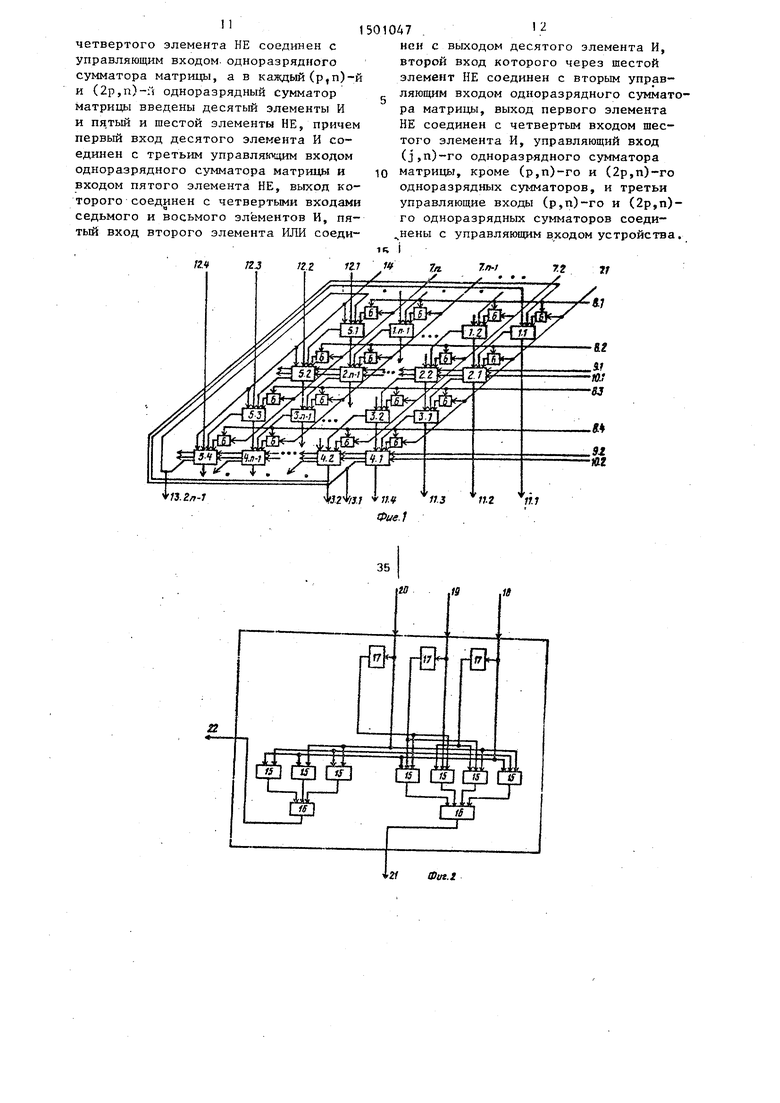

На фиг.1 представлена функциональная схема устройства для умножения; на фиг.2 - схема (j,K)-ro одноразрядного сумматора матрицы, кроме (р,К)го и (2р,К)-го одноразрядных сумматоров матрицы; на фиг.З - схема (р,К)-го и (2р,К)-го одноразрядных сумматоров матрицы; на фиг.4 - функциональная схема (j,n)- го одноразрядного сумматора матрицы,, кроме (р,п)-го и (2р,п)-го одноразрядных сумматоров матрицы; на фиг.5- функциональная схема (р,п)-го и (2р,п)-го одноразрядных сумматоров матрицы; на фиг.6 - временные диаграммы работы устройства соответст-- венно в прямом и дополнительных кодах.

Устройство для умножения (фиг.1) содержит матрицу одноразрядных сумматоров 1.1-ln-l, 2.1-1.П-1, 3.1- ,3 п-1, 4,1-4.п-1 и 5.1-5.4, матрицу элементов И 6, входы 7.1-7.П разрядов первого операнда А устройства, входы 8.1-8.4 разрядов второго операнда В устройства, первый 9.1-9.2 и второй 10.1-10.2 входы сброса

СП

iti 31501047

устройства, выходы 11.1-11.4 произведения устройства, дополнительные информационные входы 12.1-12.4 устройства, выходы 13.1-13.2n-1 уст- с ройства, управляющий вход 14 устройства.

Одноразрядные сумматоры 1.1-1 .п-1 , 3.1-З.П-1 (фиг.2) содержат семь элементов И 15, два элемента ИЛИ-16 и Ю три элемента НЕ 17, первый 18, второй 19 и третий 20 информационные входы одноразрядных сумматоров, выход суммы 21 и переноса 22 одноразрядного сумматора.15 Одноразрядные сумматоры 2.1-2,п-1, 4.1-4.п-1 (фиг.З) содержат четыре элемента НЕ 23, девять элементов И 24, два элемента ИЛИ 25 и элемент 26 задержки, первый 27, второй 28 2Q и третий 29 информационные входы одноразрядных сумматоров, первый 30 и второй 31 управляющие входы одноразрядных сумматоров, выход суммы 32 и переноса 33 одноразрядных сум- 25 маторов, первый 34 и второй 35 управляющие выходы одноразрядных сумматоров.

Одноразрядные сумматоры 5.1 и .

5.3(фиг.4) содержат четыре элемен- 30 та НЕ 36,семь элементов И 37 и два элемента ИЛИ 38, первый 39, второй

40 и третий 41 информационные входы одноразрядных сумматоров, управляющий вход 42 одноразрядных суммато- з5 ров, выходы суммы 43 и переноса 44 одноразрядных сумматоров.

Одноразрядные сумматоры 5.2 и

5.4(фиг.5) содержат шесть элементов НЕ 45, десять элементов И 46, .40 два элемента ИЛИ 47 и элемент 48 задержки, первый 49, второй 50, третий 51 информационные входы одноразрядных сумматоров, первый 52 и вто рой 53 и третий 54 управляющие вхо- 5 ды одноразрядных сумматоров, выходы сумма 55 и переноса 56 одноразрядных сумматоров, первьй 57 и второй 58 управляющие входы одноразрядных сумматоров .- 50

Устройство для умножения работает в конвейерном режиме, суть которого заключается в следующем.

При умножении двоичных чисел А и В, представленных в прямом коде, в исходном состоянии на входах 9.1 , 9.2,.t0.t, 10.2 устанавливается сигнал 1 (фиг,6). На входах 12.1- 12.4 и 14 устанавливается сигнал OV

При этом сумматоры-5.1-5.4 реализуют обычные функции суммы и переноса. Перед началом работы устройства для умножения на вход 10.2 подается отрицательный импульс, который сбрасывает одноразрядные сумматоры 4.1- 4.п-1,5.4 в нулевое Состояние. На всех выходах суммы и переноса устанавливается сигнал О.

Процесс вычисления начинается с подачи на входы 7.1,...,7п п-раз- рядного двоичного множимого А и двух младших разрядов В В2П-разрядного множителя В на входы 8.1 и 8.2. Через время Т на вход 9.1 подается сигнал О, по которому производится суммирование на сумматорах 2.1-2.п-1 и 5.2.

Когда вычисления в первых двух строках заканчиваются, на вход 9.1 подается сигнал 1, хоторьй осуществляет запоминание информации, установившейся на входах сумматоров 2.1-2.п-1, 5.2 и запрещает обработку сумматорами 2.1-2.п-1, 5.2 сигналов, которые будут появляться на их информационных входах.

В течение времени, пока проходит вычисление на сумматорах 1.1-1. п-1, 5.1 и 2.1 - 2.п-1, 5.2, на сумматорах 3.1-3.п-1, 5.3 и 4.1 - 4. п-1, 5..4 идет подготовка к вычислению, на входы 8.3-8.4 подаются разряды В и В множителя В. К моменту завершения подачи Bj и В. вычисление продолжается на сумматорах 3.1-3. п-1, 5.3, а затем после подачи на вход 9.2 сигнала О вычисление осуществляется и на сумматорах 4.1- 4. п-1, 5.4.

В то же время на сумматсзрах 1.1- 1. п-1, 5.1 и 2.1 - 2. п-1, 5.2 осуществляется считьшание двух младших разрядов С и Cj произведения С с выходов 11.1 и 11.2, а также подача разрядов By и Bg множителя В на входы 8.1 и 8.2.

После Подачи на вход 9.2 сигнала 1, который осуществляет запоминание промежуточного результата на выходах сумматоров 4.1-4. п-1, 5.4, а также запрет обработки сумматорами 4,1- 4.п-1, 5.4 поступающей информации, вычисление продолжается в сумматорах 1.1 - 1. п-1, 5.1 и 2.1 - 2. п-1, 5.2. В течение времени, пока идут вычисления, осуществляется считывание разрядов Cj и С

произведения С с выходов умножителя 11.3 и 11.4 и подача разрядов В- и Bg на входы 8.3 и 8.4. Процесс продолжается циклически. Когда все п разрядов множителя В будут поданы, на входах 8.1-8.4 устанавливается сигнал О, а процесс вычисления не прекращается до получения всех 2п разрядов произведения С с выходов 11. 1-11.4.

При умножении двоичных чисел А и В, представленных в дополнительном коде, в исходном состоянии на входах 9.1, 9.2, 10.1, 10.2, а также и на входах 12.1 - 12.4, 14 устанавливается сигнал 1 (фиг.7).

Перед началом работы устройства для умножения на вход 10.2, как и при умножении чисел, представленных в прямом коде, подается отрицательный импульс, который сбрасывает одноразрядные сумматоры 4.1-4.П-1 в нулевое состояние, а на выходах суммы и переноса сумматора 5.4 при этом устанавливаются соответственно сигналы О и 1. В дальнейшем работа устройства умножения аналогична умножению в прямом коде за исключением того, что в последних п тактах на входы 8.1-8.4 подается не сигнал О, а старший знаковый разряд Вп множителя В.

При подаче на входы 12.1 - 12.4 и 14 сигнала 1 сумматоры 5.1, 5.3 реализуют логические функции:

S а ,

где а - сигнал на первом информационном входе 39 суммато- ррв 5.1 и 5.3;

b - сигнал на втором информационном входе 40 сумматоров 5.1 и 5.3;

8,р - соответственно значения сигналов на выходе суммы 43 и выходе переноса 44

сумматоров 5.1 и 5.3.

/

Сумматоры 5.2 и 5.4 реализуют следующие логические функции (без учета цепей начальной установки):

s(t+1) a-z + s(t)-z; p(t+1) a b-z +p(t)-z,

где a - сигнал на первом информационном входе 49 суг-1матороь 5.2 и 5.4;

b - сигнал на втором информационном входе 50 сумматоров 5.2 и 5.4;

Z - сигнал на первом управляющем входе 52 сумматоров 5.2 и 5.4;

8(t-H), |s(t)

значения сигналов на выходе суммы 55 сумматоров 5.2 и 5.4 в последующий и предьщущий моменты времени:

p(t+1), p(t)

- значения сигналов на выходе переноса сумматоров 5.2, 5.4 в последующий и предыдущий моменты времени.

Реализация приведенных функций позволяет учесть, что вес знакового разряда отрицателен, и если знаковый разряд А множимого А равен 1, то сумматоры 5.1 - 5.4 производят фактически не добавление, а вычитание множителя В из суммы остальных частичных произведений. Таким образом, учитывается алгебраический знак множимого 4.

Алгебраический знак множителя Б учитьшается путем расширения разрядной сетки (т.е. подачи в последних п тактах умножения на входы 8.1-8.4 знакового разряда В) и начальной установки 1 по выходу переноса сумматора 5.4.

При необходимости ускорения получения результата умнож-ения используются выходы 13.1-13.2 п-1, на которых после п первых тактов получается двухразрядный код старших разрядов произведения С. Суммирование этого кода на сумматоре с ускоренным переносом позволяет получить старшие разряды произведения.

Для обеспечения пр зильной работы устройства для умножения, максимального быстродействия, а также для обеспечения возможности считывания промежуточной информации и коммутации разрядов множителя В величина р должна определяться, исходя из следующей системы неравенств:

t

так и

r(t

-0 ..- ч

mi п НЕ min и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Устройство для умножения | 1987 |

|

SU1501045A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Матричный умножитель | 1988 |

|

SU1615704A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения | 1989 |

|

SU1697078A1 |

| Устройство для умножения | 1989 |

|

SU1770960A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных цифровых вычислительных устройствах. Цель изобретения - расширение функциональных возможностей за счет обеспечения умножения чисел, представленных в дополнительном коде. Новым в устройстве для умножения, содержащем матрицы одноразрядных сумматоров и элементов И, является объединение двух алгоритмов: алгоритма умножения двоичных чисел, представленных в дополнительном коде, основанном на присвоении знаковым частичным произведениям отрицательного веса и добавлении корректирующих слов, и алгоритма умножения с расширением разрядной сетки. 7 ил.

tj mox t, t niin

Т -i-T

3 wax K. к mi h

, h rriiM РИ Тц и Tj не меньше чем

p- I

may

У

(т,„.-ь2:,,„)

(T«,.-T.)J% при либо Т,,., меньше чем

(T,. ° - . . - р.,

.-x.

4 ,,„-р. г„., .v-(,HE)

де t

так у

mirt

И

- максимальное и минимальное время переходного процесса в логическом элементе И;

Т, - максимальное время, не- Jmajt „1-

обходимое для считывания результата с выходов 11.1-11.4;

- максимальное и минимальное время коммутации разрядов множителя В на входах 8.1-8.4 с учетом времени прохож- ; дения сигналов через элементы И;

J - величина, равная большему из элементов, записанных в квадратных скобках.

и - величина временной задержки сигнала в элементе задержкиj

Е

ИЕ

- максимальное время переходного процесса в логическом элемента НЕ при переходе соответст- в О и из

НЕ

о

при переходе из 1 О.

в

- минимальное время переходного процесса в ло- г ическом элементе НЕ

It t I

Наличие в устройстве для умножения входов 12.1-12.4 позволяет наращивать разрядность. Это удобно при модульной реализаций устройства или выполнении его в виде интегральной : схемы. При этом увеличение разрядности достигается соответствующей коммутацией входов 12.1-12.4 одного модуля с выходами 11.1-11.4 другого модуля.

Формула

изобретени

0

5

0

5

0

5

0

5

Уст1эойство для умножения, содержащее матрицу элементов И и матрицу одноразрядных сумматоров, причем первые входы элементов И i-ro столбца матрицы (,2п, п - разрядность первого операнда) соединены соответственно с входом i-ro разряда первого операнда устройства, вход j-ro разряда второго операнда которого соединен с вторыми входами элементов И j-и строки матрицы (j 1,...,2р, р - произвольное целое число), выход (j, i)-ro элемента И матрицы соединен соответственно с первым информационным входом (j,i)- го одноразраядного сумматора матрицы, выход переноса которого, кроме (2p,i)-x одноразрядных сумматоров матрицы, соединен соответственно с вторым информационным входом (j+1, i)-ro одноразрядного сумматора матрицы, вьгход суммы (j,l)-ro одноразрядного сумматора матрицы, кроме (2p,i)x одноразрядных сумматоров матрицы, (,...,п), соединен соответственно с третьим информ цион- . ным входом (J+1, k)-ro одноразрядного сумматора матрицы (,2,..., п-1), третий информационный вход (j,n)-ro одноразрядного сумматора матрицы соединен соответственно с J-M дополнительным информационньш входом устройства, выход переноса (2 p,i)-ro. одноразрядного сумматора матрицы соединен соответственно с вторым информационным входом (1,1)- го одноразрядного сумматора матрицы, выход суммы (2р,1)-го одноразрядного сумматора матрицы соединен соответственно с третьим информационным входом (1,k)-ro одноразрядного сумматора матрицы, выходы суммы (J.O-ro одноразрядного сумматора матрицы и (2р, 1)-го одноразрядного

сумматора матрицы и выход переноса (2p,i)-ro соединены с соответствующими выходами устройства, первый и второй входы сброса которого соединены соответственно с первым и вторым управляющими входами (p,i)-x и (2p,i)-x одноразрядных сумматоров матрицы, причем каждый одноразрядный сумматор матрицы, кроме одноразрядных сумматоров р-и и 2р-й строк матрицы, содержит семь элементов И, два элемента ИЛИ, три элемента НЕ, причем выходы первого, второго, третьего и четвертого элементов И соединены соответственно с четырьмя входами первого элемента ИЛИ, выход которого соединен с выходом суммы одноразрядного сумматора матрицы, выходы пятого, шестого и седьмого элементов И соединены соответственно с тремя входами второго элемента Или, выход которого соединен с выходом переноса одноразрядного сумматора матрицы, вход первого элемента НЕ соединен с первь1м информационным входом одноразрядного сумматора матрицы и первыми входами первого, четвертого, шестого и седьмого элементов И, выход первого элемента НЕ соединен с первыми входами второго и третьего элементов И, вход второго элемента НЕ соединен с вторым информационным входом одноразрядного сумматора матрицы, вторыми входами первого, третьего и седьмого элементов И и первым входом пятого элемента И, выход второго элемента НЕ соединен с вторыми входами второго и четвертого элементов И, вход третьего элемента НЕ соединен с третьим информационным входом одноразрядного сумматора матрицы, вторыми входами пятого и шестого элементов И и с третьими входами первого и второго элементов И выход третьего элемента НЕ соединен с третьими входами третьего и четвертого элементов И, каждый одноразрядный сумматор р-й и 2р-й строк матрицы содержит девять элементов И, два элемента ИЛИ, четыре элемента НЕ и элемент задержки, причем выходы первого, второго, третьего, четвертого и пятого элементов И соединены соответственно с пятью входами первого элемента ИЛИ, выход которого соединен с выходом суммы одноразрядного сумматора мат01047 О

рицы и первым входом пятого элемента И, выходы шестого, седьмого, восьмого и девятого элементов И соединены соответственно с четырьмя входами второго элемента ИЛИ, выход которого соединен с выходом переноса одноразрядного сумматора матрицы и первым входом девятого элемента И,

10 вход первого элемента НЕ соединен с первым информационным входом одноразрядного сумматора матрицы и первыми входами первого, четвертого, седьмого и восьмого элементов И, вы15 ход первого элемента НЕ соединен с первыми входами второго и третьего элементов И, вход второго элемента НЕ соединен с вторым информационным входом одноразрядного сумматора мат20 рицы, вторыми входами первого, третьего и восьмого элементов И и первым входом шестого элемента И, выход второго элемента НЕ соединен с вторыми входами второго и четверто25 го элементов И, вход третьего элемента НЕ соединен с третьим информационным входом одноразрядного сумматора матрицы, вторыми входами шестого и седьмого элементов И и тре30 тьими входами первого и второго элементов И, выход третьего элемента НЕ соединен с третьими входами третьего и четвертого элементов И, вход элемента задержки соединен с первым управляющим входом одноразрядного сумматора матрицы, вторыми входами пятого и девятого элементов И, выход элемента задержки через четвертый элемент НЕ соединен с четвертыми входами первого, второго, третьего и четвертого элементов И и третьими входами шестого, седьмого и восьмого элементов И, третьи входы пятого и девятого элементов И соединены с вторым управляющим входом одно35

45

50

55

разрядного cyhJMaTopa матрицы, отличающееся тем, что, с целью расширения функциональных возможностей, за счет обеспечения умножения чисел, предстарленных в дополнительном коде, в кажд1 1й (|,п)-й одноразрядный сумматор матрицы, кроме (р,п)-го и (2р,п)-г() одноразрядных сумматоров матрицы, нводен четвертый элемент . выход которого соединен с третьими входами шестого и седьмого элементов И, трс- . тий вход пятого элe ClIтa И соединен с выходом первого элемента НЕ, пход

«41

fZj

Zf Фиг. г

PMJ

«4f41я

« Д.4

a

Ohn-S

Редактор О.Спесивых

Составитель Е.Мурзина

Техред Л,Олийнык Корректор Н. Борисова

Заказ 4868/44

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1982 |

|

SU1156064A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-01-25—Подача