3

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительное устройство атомно-абсорбционного спектрофотометра | 1984 |

|

SU1223051A1 |

| Синхронный демодулятор | 1987 |

|

SU1478286A1 |

| Устройство воспроизведения информации с поперечных фонограмм | 1986 |

|

SU1332371A1 |

| Фазочувствительный детектор | 1973 |

|

SU567199A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1989 |

|

SU1713103A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКИХ ПАРАМЕТРОВ | 1991 |

|

RU2017161C1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Способ контроля удаления детали из рабочей зоны пресса и устройство для его осуществления (его варианты) | 1985 |

|

SU1276525A1 |

| Синхронный детектор | 1984 |

|

SU1352613A1 |

| Синхронный детектор | 1976 |

|

SU657581A1 |

Изобретение относится к области радиотехники и автоматики и может использоваться в системах автоматического регулирования и синхронного детектирования. Цель изобретения - повышение точности и быстродействия. Устр-во содержит два идентичных канала I и 2, алгебраический сумматор 3, г-р 4 опорной частоты, временной расt пределитель импульсов 5. Каждый канал содержит элемент интегрирования 6, ключ 7, запоминакщий элемент 8. В устр-во введены в каждый канал буфер- каскад 9 и сумматор 10. В предлагаемом устр-ве за счет совмещения процессов выдачи информации и стирания t предыдущей информации время выдачи каждого канала составляет половину периода опорного сигнала, т. е. повышается быстродействие. Из-за отсутствия разрядных ключей интеграторов, которые приводят к увеличению уровня коммутационных помех и к неполному разряду конц-ра, устр-во имеет более высокую точность детектирования по g сравнению с известным устр-вом, Уро- - вень пульсаций Шз1ходного сигнала зна- // чительно ниже, чем в известном устр- ве, что тоже повышает точность фазо- чувствительного демодулятора. 1 ил.

Изобретение относится к радиотехнике и автоматике и может использоваться в системах автоматического регулирования и синхронного детектирования.

Цель изобретения - повышение точности и быстродействия.

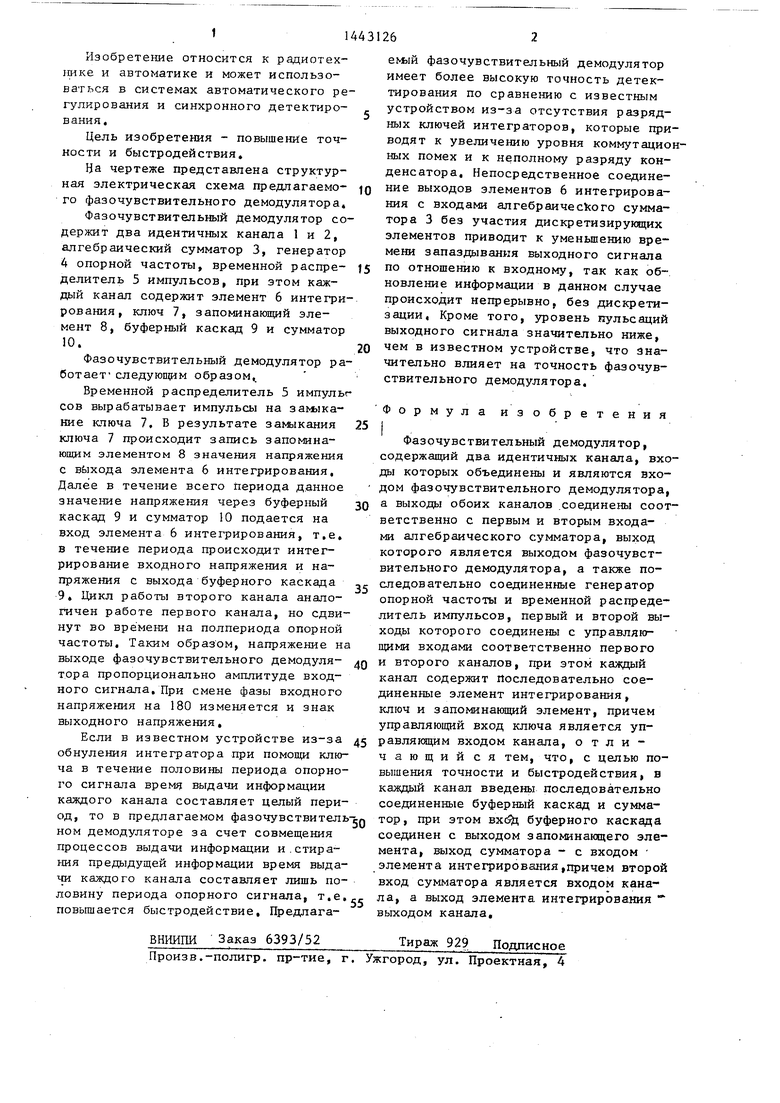

На чертеже представлена структурная электрическая схема предлагаемо- го фазочувствительного демодулятора,

Фазочувствительный демодулятор содержит два идентичных канала 1 и 2, алгебраический сумматор 3, генератор 4 опорной частоты, временной распре- делитель 5 импульсов, при этом каждый канал содержит элемент 6 интегрирования, ключ 7, запоминающий элемент 8, буферный каскад 9 и сумматор 10.

Фазочувствительный демодулятор работает- cлeдyюп5 м образом

Временной распределитель 5 импулы сов вырабатывает импульсы на замыкание ключа 7. В результате за№1кания ключа 7 происходит запись запоминающим элементом 8 значения напряжения С элемента 6 интегрирования. Далее в течение всего периода д.анное значение напряжения через буферный каскад 9 и сумматор 10 подается на вход элемента 6 интегрирования, т,е, в течение периода происходит интегрирование входного напряжения и напряжения с выхода буферного каскада 9, Цикл работы второго канала аналогичен работе первого канала, но сдвинут во времени на полпериода опорной частоты. Таким образом, напряжение на выходе фазочувствительного демодуля- тора пропорционально амплитуде входного сигнала. При смене фазы входного напряжения на 180 изменяется и знак выходного напряжения.

Если в известном устройстве из-за обнуления интегратора при помощи ключа в течение половины периода опорного сигнала время выдачи информации каждого канала составляет целый период, то в предлагаемом фазочувствитель ном демодуляторе за счет совмещения процессов выдачи информации и.стирания предыдущей информации время выдачи каждого канала составляет лишь половину периода опорного сигнала, т,е повышается быстродействие, ПредлагаВНИИПИ Заказ 6393/52

емый Фазочувствительный демодулятор имеет более высокую точность детектирования по сравнению с известным устройством из-за отсутствия разрядных ключей интеграторов, которые приводят к увеличению уровня коммутационых помех и к неполному разряду конденсатора. Непосредственное соединение выходов элементов 6 интегрирования с входами алгебраического сумматора 3 без участия дискретизиругацих элементов приводит к уменьшению времени запаздывания выходного сигнала по отношению к входному, так как обновление информации в данном случае происходит непрерывно, без дискретизации. Кроме того, уровень пульсаций выходного сигнала значительно ниже, чем в известном устройстве, что значительно влияет на точность фазочувствительного демодулятора.

Формула изобретения

Фазочувствительный демодулятор, содержащий два идентичных канала, входы которых объединены и являются входом фазочувствительного демодулятора, а выходы обоих каналов .соединены соответственно с первым и вторым входами алгебраического сумматора, выход которого является выходом фазочувствительного демодулятора, а также последовательно соединенные генератор опорной частоты и временной распределитель импульсов, первый и второй выходы которого соединены с управляющими входами соответственно первого и второго каналов, при этом каждый канал содержит Последовательно соединенные элемент интегрирования, ключ и запоминающий элемент, причем управляющий вход ключа является управляющим входом канала, отличающийся тем, что, с целью повышения точности и быстродействия, в каждый канал введены последовательно соединенные буферный каскад и сумматор, при этом Bxdjt; буферного каскада соединен с выходом запоминагацего элв мента, выход сумматора - с входом элемента интегрирования,причем второй вход сумматора является входом канала, а выход элемента интегрирования выходом канала.

Тираж 929 Подписное

Авторы

Даты

1988-12-07—Публикация

1986-03-04—Подача