(54) ВРЕМЯ-ИМПУЛЬСНОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Время-импульсное множительное устройство | 1982 |

|

SU1048489A1 |

| Множительно-делительное устройство | 1980 |

|

SU934494A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947958A1 |

| СПОСОБ ДИСКРЕТНОГО КОНТРОЛЯ РАССТОЯНИЙ ДО ИСТОЧНИКА КОЛЕБАНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2028579C1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Устройство для передачи телеметрической информации | 1986 |

|

SU1336077A1 |

| Калибратор напряжения | 1984 |

|

SU1244646A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Адаптивный коррелометр | 1979 |

|

SU809196A1 |

Изобретение относится к аналоговой вычислительной технике, и может быть использовано в аналоговых и ана логово-цифровых вычислительных систе мах. Известно время-импульсное устройство для умножения, содержащее блок хранения временных интервалов, BRJDOчающий регистр памяти и счетчик,распределитель тактовых импульсов, последговательно включенные интегратор и блок запоминания, в котором первый вход,усТройства связан.со входом бло ка хранения интервалов, вход тактовой частоты и входы .записи и считыва НИН которого соединены с соответствующими выходами распределителя тактовых импульсов, вход интегратора че рез второй ключ - с выходом блока запоминания, вход управления первого ключа соединен с выходом блока фиксации и считывания временных интерва лов, а входы управления второго ключа и блока запоминания подключены к соответствующим выходам распределителя тактовых импульсов pi . Недостатком этого устройства является то, что при работе в области больших времен требуется увеличит постоянную времени интегрирования. это приводит к увеличению погрешности устройства из-за неидеальности усилителей, входящих в состав реального интегратора, а, следовательно, при заданных точных характеристиках сужает его рабочий диапазон. Известно время-импульсное устройство для-умножения, содержащее блок хранения временных интервалов, распределитель тактовых импульсов для интегратора, блок запоминания, в котором первый вход блока хранения временных интервалов является первым входом устройства, вход тактовой частоты и входы записи и считывания блока хранения временн лх интервалов соединены с соответсвующими выходами распределителя тактовых импульсов, вход первого интегратора через первый ключ подключен ко второму входу устройства, а через второй ключ - с выходом,блока запоминания, вход второго интегратора через третий ключ связан с выходом первого интегратора, выход второго интегратора подключен ко входу блока запоминания, вход управления первого ключа соединен с выходом блока хранения временных интервалов, а управляющие входы второго интегратора.

блока запоминания и остальных ключей соединены с соответствукидими выходами распределителя тактовых импульсов p2j.

Нестабильность постоянных времени первого и второго интеграторов ведет к ухудшению сходимости итерационного процесса и требует увеличения числа циклов для достижения заданной погрешности установления, что существенно снижает его быстродействие.

Цель изобретения- - повышение быстродействия.

Поставленная цель достигается тем, что во время-импульсное устройство для умножения, содержащее блок хранения временных интервалов, вход которого является первым входом устройства, распределитель тактовых HivmyjibcoB, первый, второй и третий выходы которого подключены соответственно ко входам тактовой частоты, записи и считывания блока хранения временных интервалов, последогг вательно соединенные первый ключ, первый интегратор, второй ключ, второй интегратор и первый запоминаю.щии блок, третий ключ, информационный вход которого подключен ко входу интегратора, а выход подключен к выходу первого запоминающего блока и является выходом устройства, информационный вход первого ключа является вторым входом устройства, управляюций вход первого ключа подключен к выходу блока хранения временнрго интервала, вход сброса второго интегратора и управляющие входы первого запоминающего блока и третьего.ключа подключены соответственно к четвертому, пятому и шестому входам распределителя тактовых импульсов, источник опорного напряжения, второй запоминающий блок, четвертый ключ, преобразователь напряжений в код, накапливающий сумматор, блок сравнения кодов, счетчик, триггер и элемент И, вход источника опорного напряжения подключен к первому входу преобразователя напряжений в код и через четвертый ключ ко входу первого интегратора, выход которого через второй запоминающий блок подключен ко второму входу преобразователя напряжений в код, выход преобразователя напряжений в код подключен ко входу накапливающего сумматора, выход которого подключен к первому входу блока сравнения кодов, второй вход блока сравнения кодов подключен к выходу счетчика, а выход - к первому входу триггера, второй вход которого подключен к седьмому выходу распределителя тактовых импульсов,, выход триггера подключен к управляющему входу второго ключа и к первому входу элемента И, второй вход которого подключен к

первому выходу распределителя тактовых импульсов, выход элемента И подключен ко входу счетчика, вход сброса первого интегратора и управляющие входы четвертого ключа, второрого запоминающего блока и преобразователя напряжений в код соответственно подключены к восьмому, деэятому, десятому и одиннадцатому выходам распределителя тактовых импульсов .

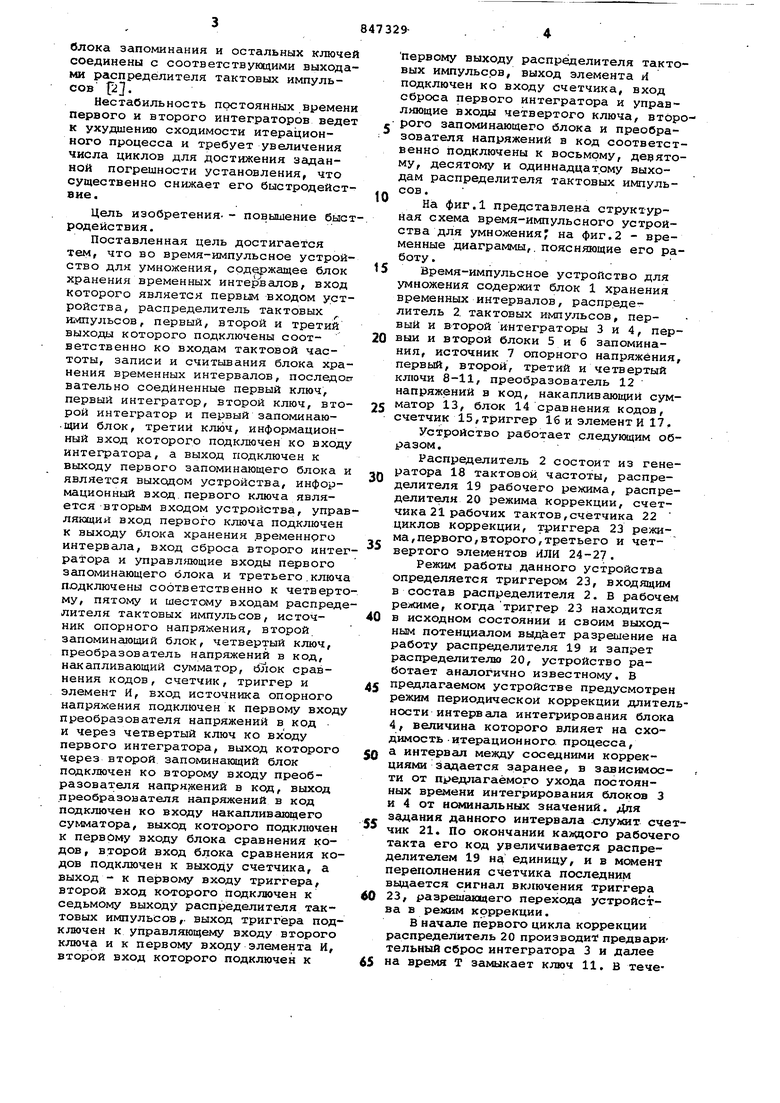

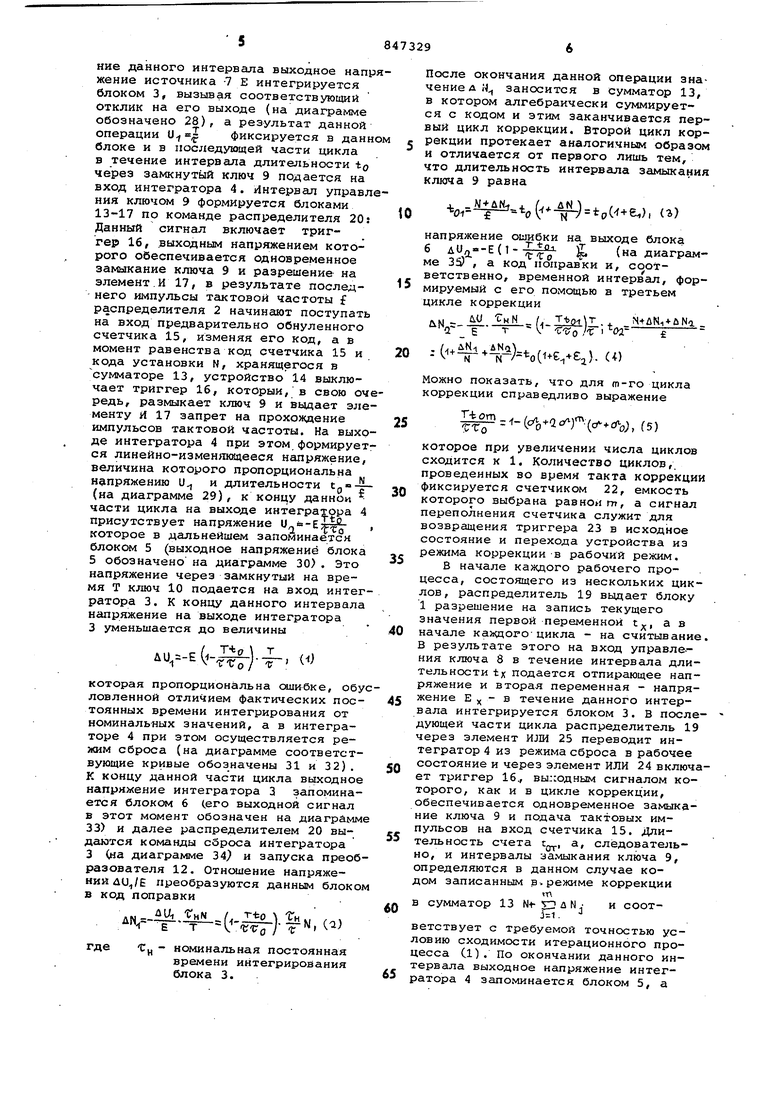

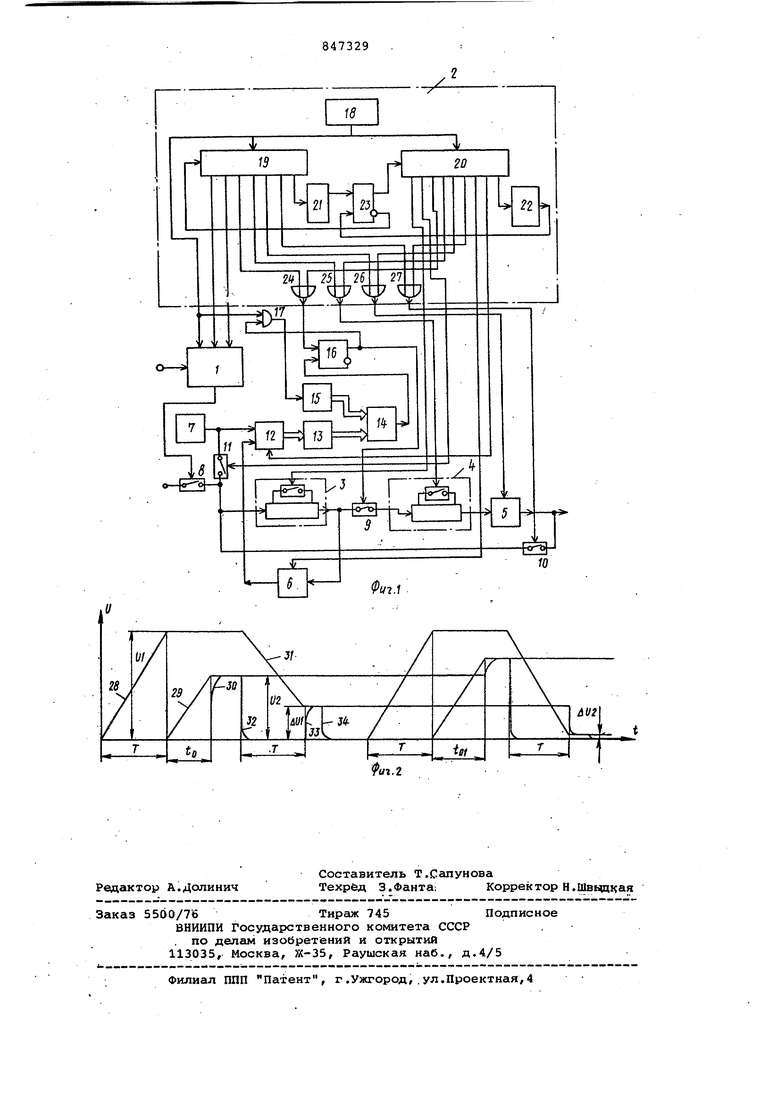

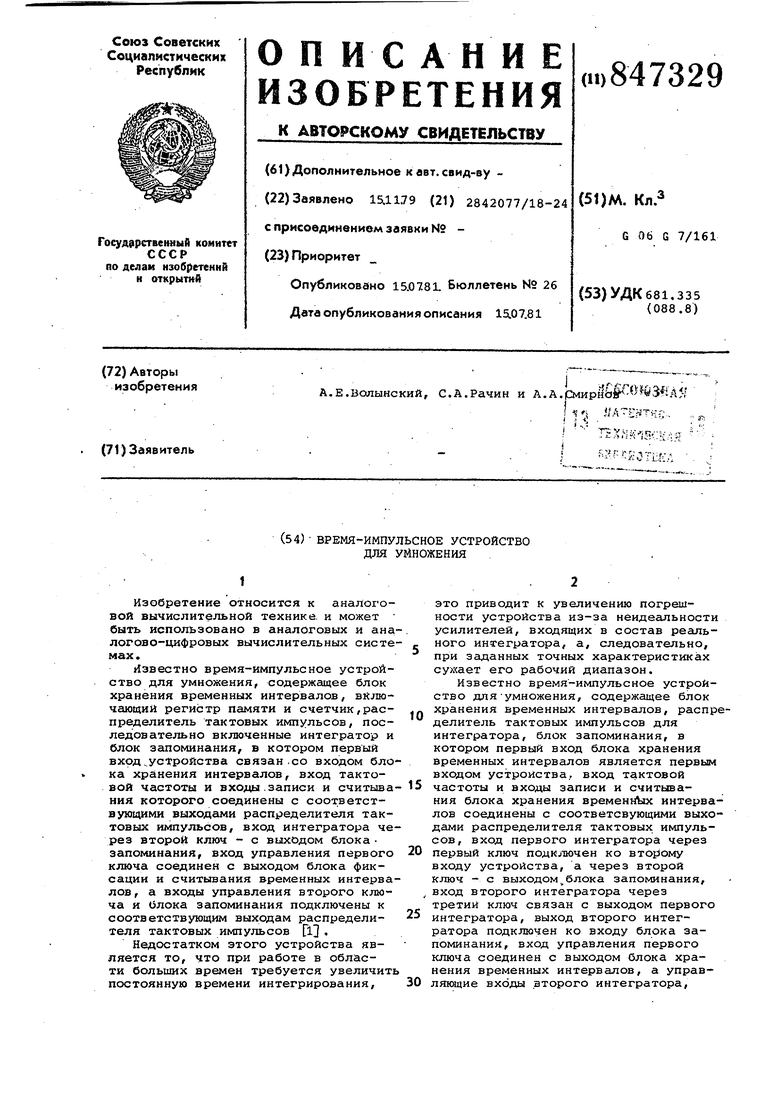

На фиг.1 представлена структурная схема время-импульсного устройства для умножения на фиг.2 - временные диаграммы,, поясняющие его работу .

Время-импульсное устройство для умножения содержит блок 1 хранения временных интервалов, распределитель 2. тактовых импульсов, первый и второй интеграторы 3 и 4, первый и второй блоки 5 и 6 запоминания, источник 7 опорного напряжения, первый, второй, третий и четвертый ключи 8-11, преобразователь 12 напряжений в код, накапливающий сумматор 13, блок 14 сравнения кодов, счетчик 15,триггер 16 и элемент И 17.

Устройство работает следующим образом.

Распределитель 2 состоит из генератора 18 тактовой частоты, распределителя 19 рабочего режима, распределителя 20 режима коррекции, счетчика 21 рабочих тактов,счётчика 22 циклов коррекции, триггера 23 режима, первого, второго, третьего и четвертого элементов ИЛИ 24-2.

Режим работы данного устройства определяется триггером 23, входящим в состав распределителя 2. В рабочем режиме, когда триггер 23 находится в исходном состоянии и своим выходным потенциалом выд&ет разрешение на работу распределителя 19 и запрет распределителю 20, устройство работает аналогично известному. В предлагаемом устройстве предусмотрен режим периодической коррекции длителности интервала интегрирования блока 4, величина которого влияет на сходимость итерационного процесса, а интервал мегкду соседними коррекциями задается заранее, в зависимости от пpeдJИгaёмoгo ухода постоянных времени интегрирования блоков 3 и 4 от номинальных значений. Для з щания данного интервала служит счечик 21. По окончании казедого рабочег такта его код увеличивается распределителем 19 на единицу, и в момент переполнения счетчика последним вьщается сигнал вк {ючения триггера 23, разрешающего перехода устройства в режим коррекции.

В начгше первого цикла коррекции распределитель 20 производи предварительный сброс интегратора 3 и далее на время Т замыкает ключ 11. Б течение данного интервала выходное напр жение источника -7 Е интегрируется блоком 3, вызывая соответствующий отклик на его выходе (на диаграмме обозначено 28), а результат данной операции фиксируется в данн блоке и в последующей части цикла Б течение интервала длительности t через замкнутый ключ 9 подается на вход интегратора 4. Интервал управл ния ключом 9 формируется блоками 13-17 по команде распределителя 20: Данный сигнал включает триггер 16, .выходным напряжением которого обеспечивается одновременное замыкание ключа 9 и разрешение на элемент.И 17, в результате последнего И1м1пульсы тактовой частоты f распределителя 2 начинают поступать на вход предварительно обнуленного счетчика 15, изменяя его код, а в момент равенства код счетчика 15 и кода установки N, хранящегося в Ъумматоре 13, устройство 14 выключает триггер 16, который, в свою оч редь, размыкает ключ 9 и выдает эле менту И 17 запрет на прохождение импульсов тактовой частоты. На выхо де интегратора 4 при этом формирует ся линейно-изменяквдееся напряжение, величина которого пропорциональна напряжению и и длительности tjj -j- (на диаграмме 29), к концу данной части цикла на выходе интегратора 4 присутствует напряжение которое в дальнейшем запоминается блоком 5 (выходное напряжение блока 5 обозначено на диаграмме 30). Это напряжение через замкнутый на время Т ключ 10 подается на вход интег ратора 3. К концу данного интервала напряжение на выходе интегратора 3 уменьшается до величины )-f которая пропорциональна ошибке, обу ловленной отличием фактических постоянных времени интегрирования от номинальных значений, а в интеграторе 4 при этом осуществляется режим сброса (на диаграмме соответствующие кривые обозначены 31 и 32). К концу данной части цикла выходное напряжение интегратора 3 запоминается блоком 6 (его выходной сигнал в этот момент обозначен на диаграмм 33) и далее распределителем 20 выдаются команды сброса интегратора 3 (на диаграмме 34 и запуска преоб разователя 12. Отношение напряжении dU.,/E преобразуются данным блоко в код поправки .АУч. Гн .(.-).«,и. где Сц - номинальная постоянная времени интегриробания блока 3. После окончания данной операции значение д i-) заносится в сумматор 13, в котором алгебраически суммируется с кодом и этим заканчивается первый цикл коррекции. Второй цикл коррекции протекает аналогичным образом и отличается от первого лишь тем, что длительность интервала замыкания ключа 9 равна ,,-.±.t,(.j te,(..e.). (г) напряжение ошибки на выходе блока 6 ди/1.-Е( §. (на диаграмме 35) , а код поправки и, соответственно, временной интервгш, формируемый с его помощью в третьем цикле коррекции ли СнМ /. Т-ЬрИтNtuNi uNg . 11т tVo i ,(,..t,,.e.). („ Можно показать, что для т-го цикла коррекции справедливо выражение (),(5} которое при увеличении числа циклов сходится к 1. Количество циклов,, проведенных во время такта коррекции фиксируется счетчиком 22, емкость которого выбрана равной т, а сигнал переполнения счетчика служит для возвращения триггера 23 в исходное состояние и перехода устройства из режима коррекции -в рабочий режим. В начале каждого рабочего процесса, состоящего из нескольких циклов, распределитель 19 выдает блоку 1 разрешение на запись текущего значения первой переменной , а в начале казедого-цикла - на считывание. В результате этого на вход управления ключа 8 в течение интервала длительности tx подается отпирающее напряжение и вторая переменная - напряжение Е - в течение данного интервала интегрируется блоком 3. В последующей части цикла распределитель 19 через элемент ИЛИ 25 переводит интегратор 4 из режима сброса в рабочее состояние и через элемент ИЛИ 24 включает триггер 16., выгодным сигналом которого, как и в цикле коррекции, обеспечивается одновременное замыкание ключа 9 и подача тактовых импульсов на вход счетчика 15. Длительность счета ty, а, следовательно, и интервалы замыкания ключа 9, определяются в данном случае кодом записанным в режиме коррекции в сумматор 13 Nt-SDaN. и соотj i. ветствует с требуемой точностью условию сходимости итерационного процесса Cl). По окончании данного интервала выходное напряжение интегратора 4 запоминается блоком 5, а в оставшейся части цикла выходное напряжение блока 5 через замкнутый в течение интервала длительности Т ключ 9 подается на вход интегратора 3, в котором интегрируется и результат интегрирования алгебраи 1ески суммируется с ошибкой, накоппенной устройством в предыдущих цик лах. Аналогично известному, можно показать, что проведение рабочего цикла п раз обеспечивает на выходе блока 5 напряжение , (с.-аслГ(.Сб) Итерационный процесс.в данном устройстве сходится к установив.щемуся значению намного быстрее, чем в известном, т.е. позволяет в рабочем режиме при заданной погрешности установления сократить число циклов итерации. Учитывая, что коррекция может проводиться достаточно редко (интер вал мезвду коррекциями зависит от с бильности постоянных времени интег раторов и может изменяться часами), это означает существенное повышение быстродействия устройств По сравнению с известным. Формула изобретения. Время-импульсное устройство для умножения, содержащее блок хра нения временных, интервалов, вход к торого является первым входом устройства, распределитель тактовых импульсов, первый, второй и третий выходы которого подключены соответ ственно ко входам тактовой частоты записи и считывания блока хранения временных интервалов, послед вательно соединенные первый ключ, первый интегратор, второй ключ, вт ро.й интегратор и первый запоминающий блок,, третий ключ, информацион ный вход которого подключен ко входу первого интегратора, а выход подключен к выходу первого запомин щего блока и является выходом устр ства, информационный вход первого ключа является вторым входом устро на, управляющий вход первого ключа подключен к выходу блока хранения временного интервала, вход сброса второго интегратора и управляющие входы первого запоминающего блока и третьего ключа подключены соответственно к четвертому, пятому и шестому выходам распределителя тактовых импульсов, отличающееся тем, что, с целью увеличения быстродействия, в устройство введены источник .опорного напряжения, второй запоминающий блок, четвертый ключ, /преобразователь напряжений в код, накапливающий сумматор, блок сравнения кодов, счетчик, триггер и элемент И, выход источника опорного напряжения подключен к первому входу преобразователя напряжения в код и через четвертый ключ ко входу первого интегратора, выход которого через второй запоминающий блок подключен ко второму входу преобразователя напряжений в ксщ, выход преобразователя напряжений в код подключен ко входу накапливающего сумматора, выход которого подключе1 { первому входу блока сравнения кодой,второй вход блока сравнения кодов подключен к выходу счетчика, а выход - к первому входу триггера, второй вход которого подключен к седьмому выходу распределителя тактовых импульсов, выход триггера подключен к управляющему входу второго ключа и к первому входу элемента И, второй вход кбтсхрого подключен к первому выходу распределителя тактовых импульсов, выход элемента И Подключен ко входу счетчика, вход сброса первого интегратора и управляющие входы четвертого ключа, второго запоминающего блока и преобразователя напряжений в код соответственно подключены к восьмому, девятому, десятому и одиннадцатому вых,С)дам рас предеЛителя тактовых импульсов. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3646545, кл.340347, опублик.1972. 2.Авторское свидетельство СССР W 619927, кл. G 06 G 7/161, 1978 (прототип).

J/

Л v

A-JO

2S

J2

uUf

j

jjC

т

Cfl

/Л

/jw

w

Авторы

Даты

1981-07-15—Публикация

1979-11-15—Подача