1

Изобретение относится к измерительной технике и может быть использовано в системах автоматического регулирования для фазочувствительного выпрямления переменных напряжений.

Цель изобретения - повышение точности детектирования в области малых входных сигналов.

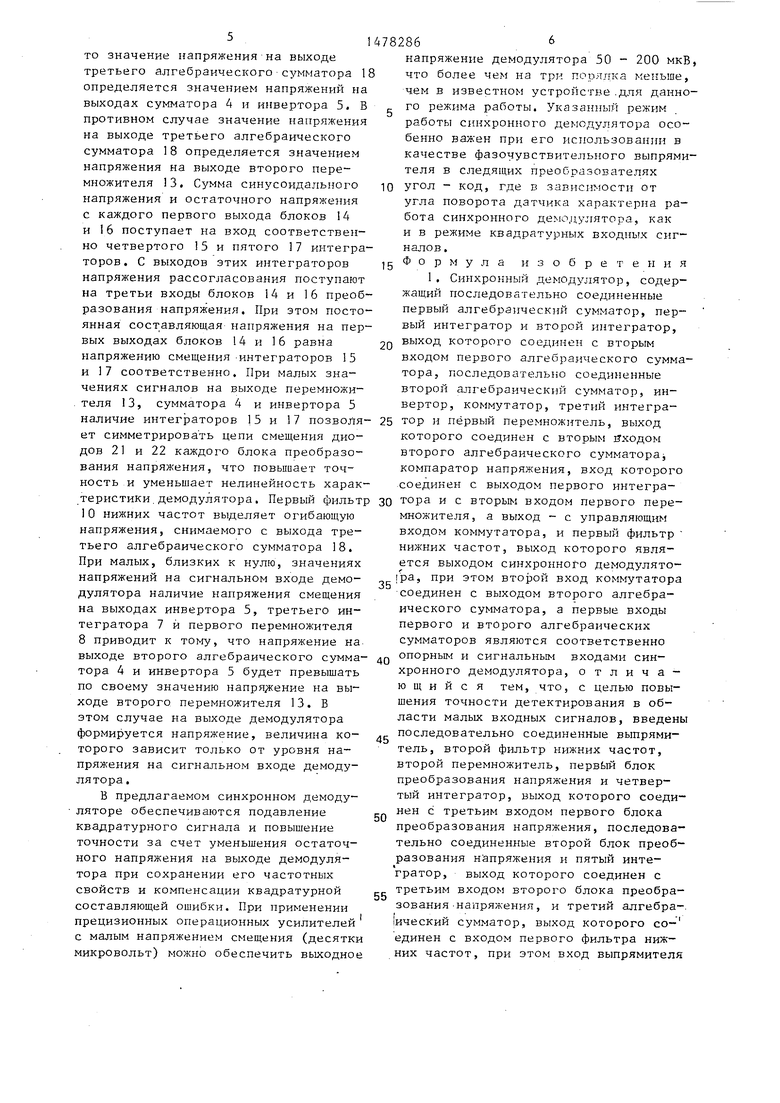

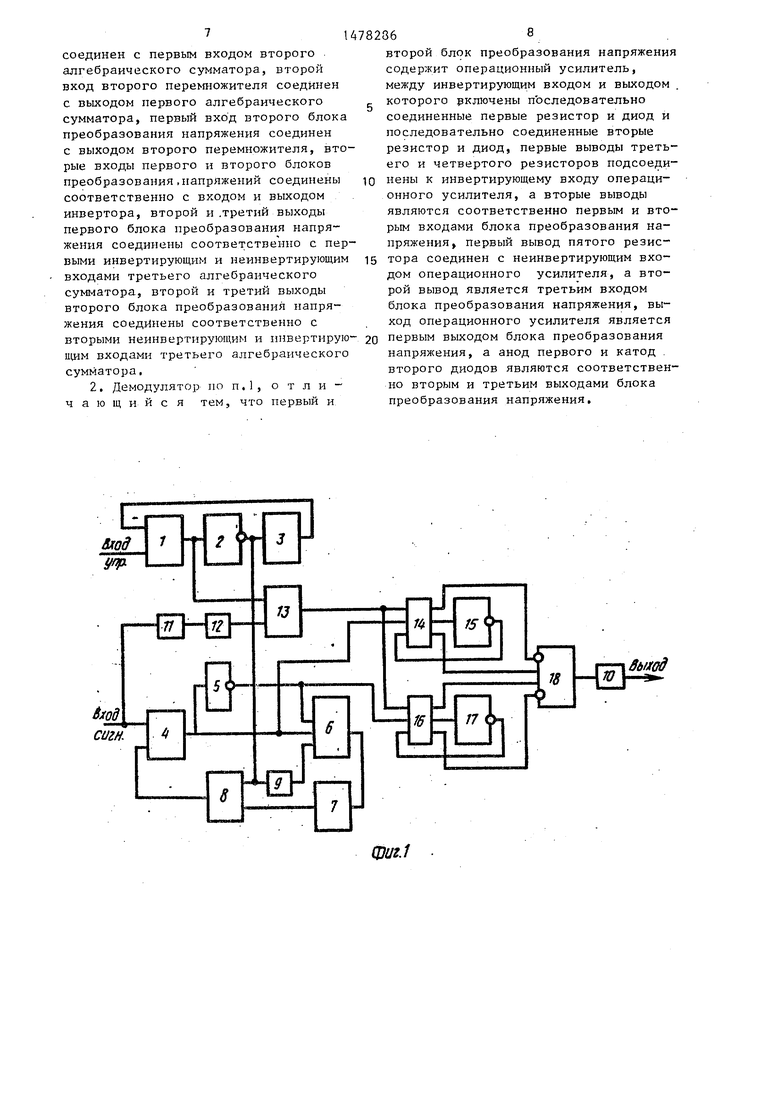

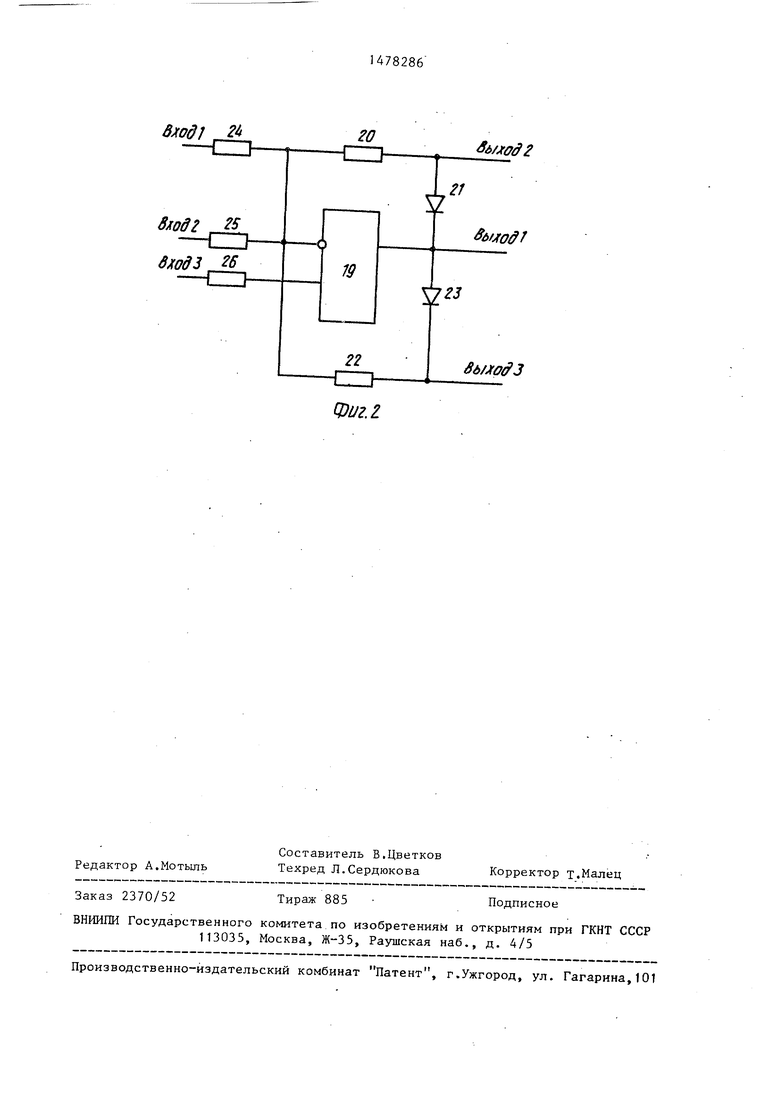

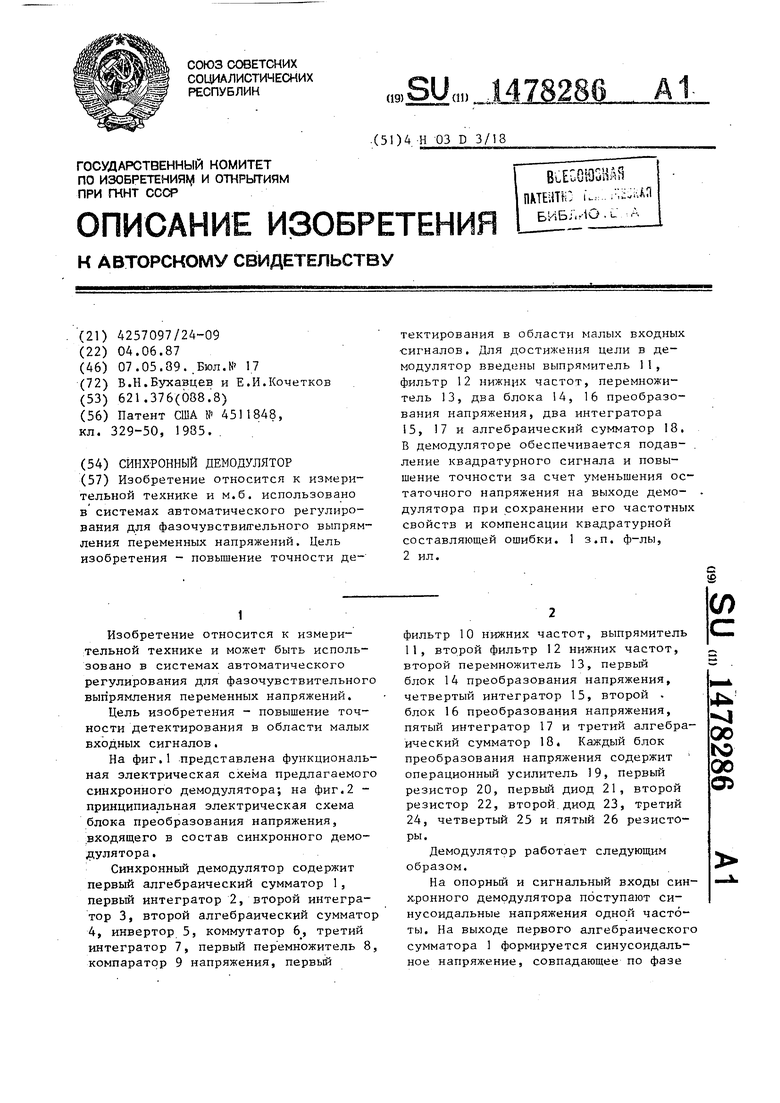

На фиг.1 представлена функциональная электрическая схема предлагаемого синхронного демодулятора; на фиг.2 - принципиальная электрическая схема блока преобразования напряжения, входящего в состав синхронного демодулятора .

Синхронный демодулятор содержит первый алгебраический сумматор 1, первый интегратор 2, второй интегратор 3, второй алгебраический сумматор 4, инвертор 5, коммутатор 6, третий интегратор 7, первый пер емножитель 8, компаратор 9 напряжения, первый

СО

фильтр 10 нижних частот, выпрямитель 11, второй фильтр 12 нижних частот, второй перемножитель 13, первый блок 14 преобразования напряжения, четвертый интегратор 15, второй . блок 16 преобразования напряжения, пятый интегратор 17 и третий алгебраический сумматор 18. Каждый блок преобразования напряжения содержит операционный усилитель 19, первый резистор 20, первый диод 21, второй резистор 22, второй диод 23, третий 24, четвертый 25 и пятый 26 резисторы.

Демодулятор работает следующим образом.

На опорный и сигнальный входы синхронного демодулятора поступают синусоидальные напряжения одной частоты. На выходе первого алгебраического сумматора 1 формируется синусоидальное напряжение, совпадающее по фазе

Јь J

00

к

00 О)

с напряжением на опорном демодулятора. На выходе первого интегратора 2 формируется синусоидальное напряжение, сдвинутое по фазе на четверть периода относительно напряжения на выходе первого алгебраического сумматора 1. Цепь местной отрицательной обратной связи, состоящая из второго интегратора 3 и сумматора 1, стабилизирует минимальное значение напряжения смещения на выходах сумматора 1 и интегратора 2. На .выходе компаратора 9 напряжения формируется прямоугольное напряжение со -/ скважностью, близкой к двум, в моменты перехода синусоидального напряжения с выхода первого интегратора 2 через нуль - напряжение, управляющее работой коммутатора 6, Лнформацион- ный сигнал поступает на первый вход алгебраического сумматора 4 и на вход выпрямителя 11. Па выходе выпрямителя 11 формируются положительные полуволны напряжения, амплитуда ко- торых зависит от величины напряжения па сигнальном входе демодулятора. Второй фильтр 12 нижних частот выделяет огибающую напряжения на сигнальном входе демодулятора, управ ляющую работой второго перемножителя 13. Алгебраический сумматор 4, инвертор 5, коммутатор 6, интегратор 7 и первый перемножитеЛь 8 предназначены

для компенсации квадратурной состав

лягощей напряжения на сигнальном входе демодулятора. При отсутствии квадратурной составляющей напряжения на сигнальном входе демодулятора на выходе второго алгебраического сумма- тора 4 формируется напряжение, равное входному напряжению. При этом на выходе коммутатора 6 формируется напряжение, в котором отсутствует постоянная составляющая. На выходах третьего интегратора 7 и перемножителя 8 напряжение при этом равно нулю. При подаче на сигнальный вход демодулятора квадратурной составляющей

входного сигнала на выходе коммутатора 6 появляется постоянная составляющая напряжения, которая, поступая на вход третьего интегратора 7, приводит к увеличению или уменьшению (в зависимости от знака постоянной составляющей) напряжения на его выхо де до значения, пока синусоидальное- напряжение на выходе первого перемножителя 8 не скомпенсирует по знаку

гJQ J5 20 25 30

35

Q .

50

55

и значению входное квадратурное напряжение .

Таким образом, при подаче на сиг- нальный вход демодулятора квадратурной составляющей входного сигнала в установившемся режиме на выходах алгебраического сумматора 4 и инвертора 5 устанавливается напряжения, близкие к нулю.При подаче на сигнальный вход демодулятора напряжения, синфазного или противофазного напряжению на опорном входе демодулятора, на выходах алгебраического сумматора 4 и инвертора 5 устанавливаются напряжения, равные по значению напряжению на сигнальном входе демодулятора синфазное с ним на выходе сумматора 4 и противофазное на выходе инвертора 5. При подаче на вход демодулятора напряжения, сдвинутого на произволь- ный угол относительно напряжения на опорном входе демодулятора, на выходах сумматора 4 и инвертора 5 сформируется только составляющая входного сигнального напряжения, совпадающая по фазе (или противофазная) с напряжением на опорном входе демодулятора .

На первом выходе блока 14 преобразования напряжения формируется напряжение, пропорциональное сумме напряжений на выходах второго перемножителя 13 и второго алгебраического сумматора 4. На первом выходе второго блока 1 б преобразования напряжения формируется синусоидальное напряжение, пропорциональное сумме напряжений, поступающих с выходов второго перемножителя 13 и инвертора 5. На втором и третьем выходах первого 14 и втдро- го 16 блоков преобразования напряжения формируются соответственно отрицательные и положительные полуволны указанных напряжений.

После алгебраического суммирования полуволн напряжений, поступающих на входы третьего алгебраического сумматора 18, на его выходе формируется двухполупериодное напряжение, значение которого зависит от значений напряжений, поступающих с выходов второго перемножителя 13, второго алгебраического сумматора 4 и инвертора 5. Если напряжение, поступающее с выхода перемножителя 13, больше по абсолютной величине значения напряжения на выходе алгебраического сумматора 4 (нормальный режим работы),

то значение напряжения на выходе третьего алгебраического сумматора 1 определяется значением напряжений на выходах сумматора 4 и инвертора 5. В противном случае значение напряжения на выходе третьего алгебраического сумматора 18 определяется значением напряжения на выходе второго перемножителя 13, Сумма синусоидального напряжения и остаточного напряжения с каждого первого выхода блоков 14 и 16 поступает на вход соответственно четвертого 15 и пятого 17 интеграторов. С выходов этих интеграторов напряжения рассогласования поступают на третьи входы блоков 14 и 16 преобразования напряжения. При этом постоянная составляющая напряжения на первых выходах блоков 14 и 16 равна напряжению смещения интеграторов 15 и 17 соответственно. При малых значениях сигналов на выходе перемножителя 13, сумматора 4 и инвертора 5 наличие интеграторов 15 и 17 позволяет симметрировать цепи смещения диодов 21 и 22 каждого блока преобразования напряжения, что повышает точность и уменьшает нелинейность характеристики демодулятора. Первый фильт 10 нижних частот выделяет огибающую напряжения, снимаемого с выхода третьего алгебраического сумматора 18. При малых, близких к нулю, значениях напряжений на сигнальном входе демодулятора наличие напряжения смещения на выходах инвертора 5, третьего интегратора 7 и первого перемножителя 8 приводит к тому, что напряжение на выходе второго алгебраического сумматора 4 и инвертора 5 будет превышать по своему значению напряжение на выходе второго перемножителя 13. В этом случае на выходе демодулятора формируется напряжение, величина которого зависит только от уровня напряжения на сигнальном входе демодулятора .

В предлагаемом синхронном демодуляторе обеспечиваются подавление квадратурного сигнала и повышение точности за счет уменьшения остаточного напряжения на выходе демодулятора при сохранении его частотных свойств и компенсации квадратурной составляющей ошибки. При применении прецизионных операционных усилителей с малым напряжением смещения (десятки микровольт) можно обеспечить выходное

10

15

20

25

30

782866

напряжение демодулятора 50 - 200 мкВ, что более чем на три порядка меньше,

чем в известном устройстве для данно. го режима работы. Указанный режим

Ь

работы синхронного демодулятора особенно важен при его использовании в качестве фазочувствитепьного выпрямителя в следящих преоСтрахователях угол - код, где в зависимости от угла поворота датчика характерна работа синхронного демодулятора, как и в режиме квадратурных входных сигналов . Формула изобретения

1. Синхронный демодулятор, содержащий последовательно соединенные первый алгебраический сумматор, первый интегратор и второй интегратор, выход которого соединен с вторым входом первого алгебраического сумматора, последовательно соединенные второй алгебраический сумматор, инвертор, коммутатор, третий интегратор и первый перемножитель, выход которого соединен с вторым выходом второго алгебраического сумматора, компаратор напряжения, вход которого соединен с выходом первого интегратора и с вторым входом первого перемножителя, а выход - с управляющим входом коммутатора, и первый фильтр нижних частот, выход которого является выходом синхронного демодулято- ipa, при этом второй вход коммутатора соединен с выходом второго алгебраического сумматора, а первые входы первого и второго алгебраических сумматоров являются соответственно опорным и сигнальным входами синхронного демодулятора, отличающийся тем, что, с целью повышения точности детектирования в области малых входных сигналов, введены последовательно соединенные выпрямитель, второй фильтр нижних частот, второй перемножитель, первый блок преобразования напряжения и четвертый интегратор, выход которого соединен с третьим входом первого блока преобразования напряжения, последовательно соединенные второй блок преобразования напряжения и пятый интегратор, выход которого соединен с третьим входом второго блока преобразования напряжения, и третий алгебра- ический сумматор, выход которого со- единен с входом первого фильтра нижних частот, при этом вход выпрямителя

35

40

45

50

55

I

соединен с первым входом второго алгебраического сумматора, второй вход второго перемножителя соединен с выходом первого алгебраического сумматора, первый вход второго блока преобразования напряжения соединен с выходом второго перемножителя, вто1 рые входы первого и второго блоков преобразования.напряжений соединены соответственно с входом и выходом инвертора, второй и .третий выходы первого блока преобразования напряжения соединены соответственно с пер1 выми инвертирующим и неинвертирующим входами третьего алгебраического сумматора, второй и третий выходы второго блока преобразования напряжения соединены соответственно с вторыми неинвертирующим и инвертирую щим входами третьего алгебраического сумматора.

2. Демодулятор но п.1, о т ли - чающийся тем, что первый и

782368

второй блок преобразования напряжения содержит операционный усилитель, между инвертирующим входом и выходом ,. которого включены последовательно соединенные первые резистор и диод и последовательно соединенные вторые резистор и диод, первые выводы третьего и четвертого резисторов подсоединены к инвертирующему входу операционного усилителя, а вторые выводы являются соответственно первым и вторым входами блока преобразования напряжения , первый вывод пятого резистора соединен с неинвертирующим вхо10

15

0

дом операционного усилителя, а второй вывод является третьим входом блока преобразования напряжения, выход операционного усилителя является первым выходом блока преобразования напряжения, а анод первого и катод второго диодов являются соответственно вторым и третьим выходами блока преобразования напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ КОРОТКОВОЛНОВЫЙ МОДЕМ | 2004 |

|

RU2286648C2 |

| Демодулятор сигналов частотной телеграфии | 1987 |

|

SU1497756A1 |

| ПОМЕХОЗАЩИЩЕННАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2285344C2 |

| Электропривод переменного тока | 1989 |

|

SU1757041A1 |

| Вентильный электропривод | 1990 |

|

SU1791953A1 |

| АППАРАТУРА ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ, УСТОЙЧИВАЯ К ВОЗДЕЙСТВИЮ МОЩНОЙ ЧМ ПОМЕХИ | 2001 |

|

RU2205506C1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2003 |

|

RU2271071C2 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2015 |

|

RU2582557C1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ПЕРЕМЕЩЕНИЯ В КОД И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (ВАРИАНТЫ) | 1992 |

|

RU2068619C1 |

Изобретение относится к измерительной технике и может быть использовано в системах автоматического регулирования для фазочувствительного выпрямления переменных напряжений. Цель изобретения - повышение точности детектирования в области малых входных сигналов. Для достижения цели в демодулятор введены выпрямитель 11, фильтр 12 нижних частот, перемножитель 13, два блока 14,16 преобразования напряжения, два интегратора 15,17 и алгебраический сумматор 18. В демодуляторе обеспечивается подавление квадратурного сигнала и повышение точности за счет уменьшения остаточного напряжения на выходе демодулятора при сохранении его частотных свойств и компенсации квадратурной составляющей ошибки. 1 з.п.ф-лы, 2 ил.

выход

фиг.1

toodi г

вход г к

i

вход я

Фиг.г

Редактор А.Мотыль

Составитель В.Цветков Техред Л.Сердюкова

Заказ 2370/52

Тираж 885

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г.Ужгород, ул. Гагарина,101

20

&шод2

Корректор х.Малец

Подписное

| Патент США № 4511848, кл | |||

| Букса для железнодорожного подвижного состава | 1922 |

|

SU329A1 |

Авторы

Даты

1989-05-07—Публикация

1987-06-04—Подача