Ю

лю два, НЕ 7 и 10 формирователь 9 стробирующих импульсов, инт.ег- раторы 11 и 13, вьгчитатель 12, источник 14 опорных напряжений, формирователи 15 и 16 прямоугольных импульсов и триггеры 19 и 20, Из знаковых последовательностей, вьщеленных выпрямителем 15 формируются формирователями 15 и 16 импульсные последо- вательности соответствующих логических уровней, которые нормируют во времени относительно тактовых импульсов триггерами 19 и 20, После этого они используются для временной селекции, осуществляемой эл-тами И 17 и 18 выходного сигнала единиц эл-та И 5 на положительные и отрицательные единицы, соответствующие символам положительной и отрицательной полярности трехуровневого биполярного сигнала на 1-м входе устр-ва, и их коммутации соответственно на 2 -й и 3-й выходы устр-ва. Цель достигается введением формирователей 15 и 16, эл-тов И 17 и 18 и триггеров 19 и 20. Устр-во по п. 2 ф-лы отличается выполнением выпрямителя 1. 1 з.п.ф-лы, 2 ил о, 1 табЛо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля трехуровневых биполярных сигналов | 1986 |

|

SU1354424A1 |

| Формирователь биполярных импульсов | 1989 |

|

SU1662002A1 |

| Стабилизированный преобразователь напряжения постоянного тока | 2024 |

|

RU2822294C1 |

| Стабилизатор напряжения постоянного тока | 2024 |

|

RU2826844C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| ГЕНЕРАТОР ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ | 2022 |

|

RU2784622C1 |

| Стабилизированный преобразователь напряжения постоянного тока | 2024 |

|

RU2833008C1 |

| Стабилизированный преобразователь напряжения с защитой от перегрузок | 1985 |

|

SU1295490A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| Аналого-цифровой преобразователь | 1979 |

|

SU836794A1 |

Изобретение относится к технике связио Иель изобретения - увеличение точности контроля о Устр-во содержит выгфямитель 1, выделитель 2 тактовой частоты, пороговые блоки 3 и 4, эл-ты И 5, 8, 17 и 18, сумматор 6 по моду

Изобретение относится к технике СВЯЗИ;, может быть использовано при контроле цифровых каналов связи и является усовершенствованием устройства по авто с:з, № 1354424..

Ц&ль изобретения - увеличение точности контроля,

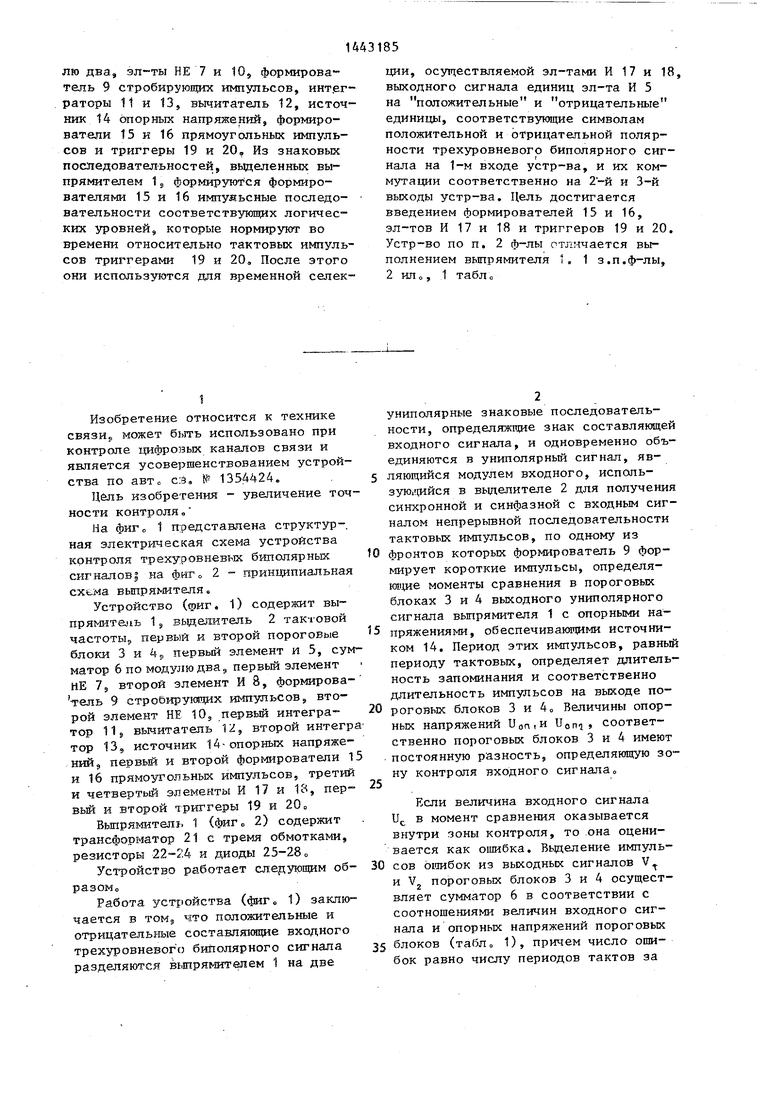

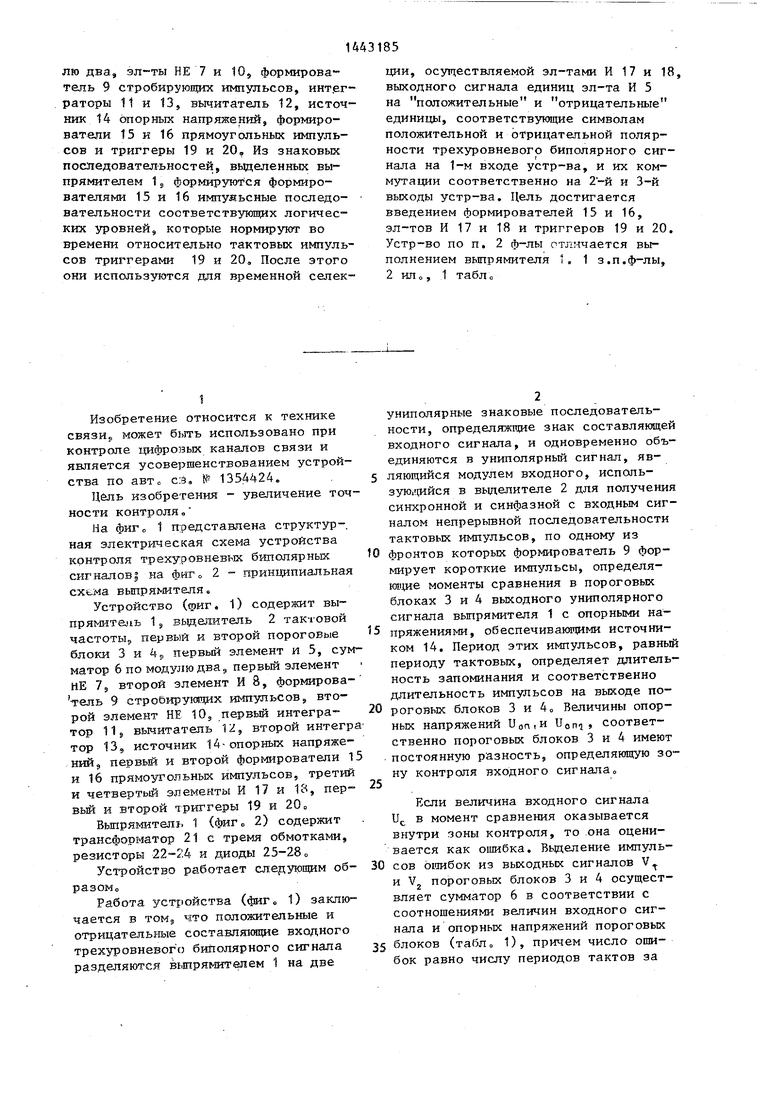

На фиг о 1 представлена структур-. ная электрическая схема устройства контроля трехуровневых биполярных

сигналов| на фиг с, 2 - принципиальная схема выпрямителя.

Устройство (фиг, 1) содержит выпрямитель 1J вьщелитель 2 тактовой

частоты, первый и второй пороговые

блоки 3 и 5 первый элемент и 5, сумматор 6 по модулю два, первый элемент НЕ 7j второй элемент И 8, формирова тель 9 стробирующих импульсов, второй элемент НЕ 10, первый интегра- тор 11s вычитатель 12, второй интегра тор ISj источник 14-опорных напряжений, первый и второй формирователи 15 и 16 прямоугольных импульсов, третий и четвертый элементы И 17 и 18, пер- вьй и второй триггеры 19 и 20„

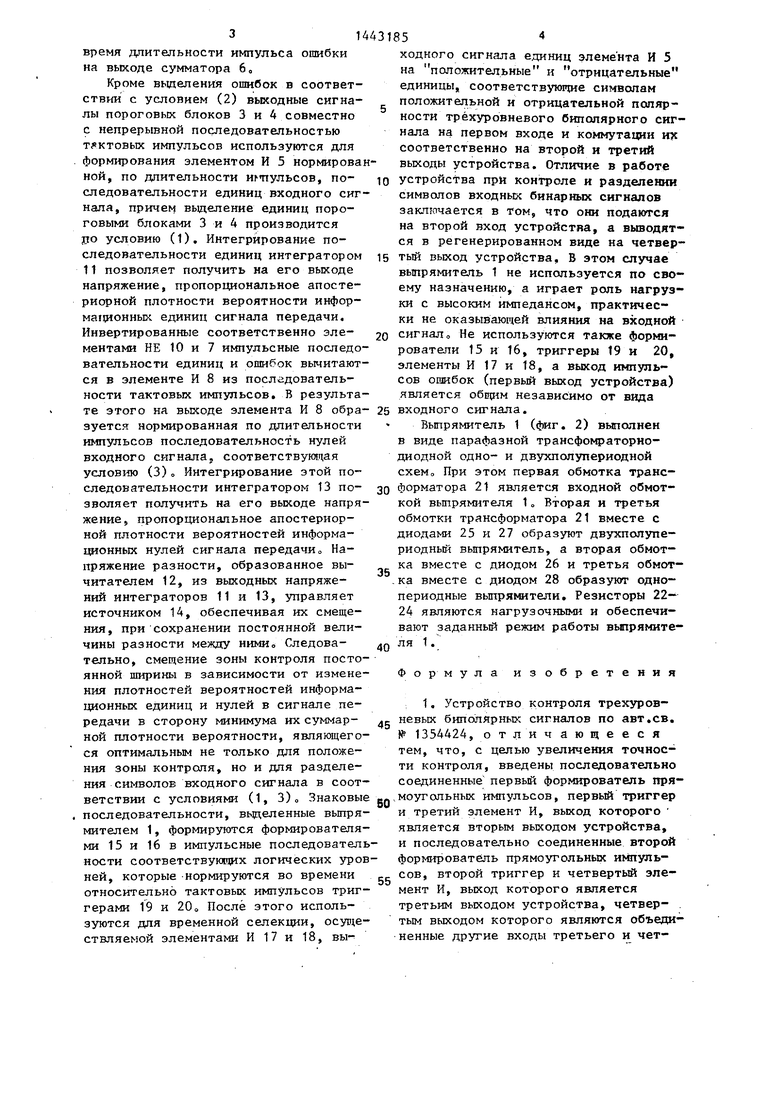

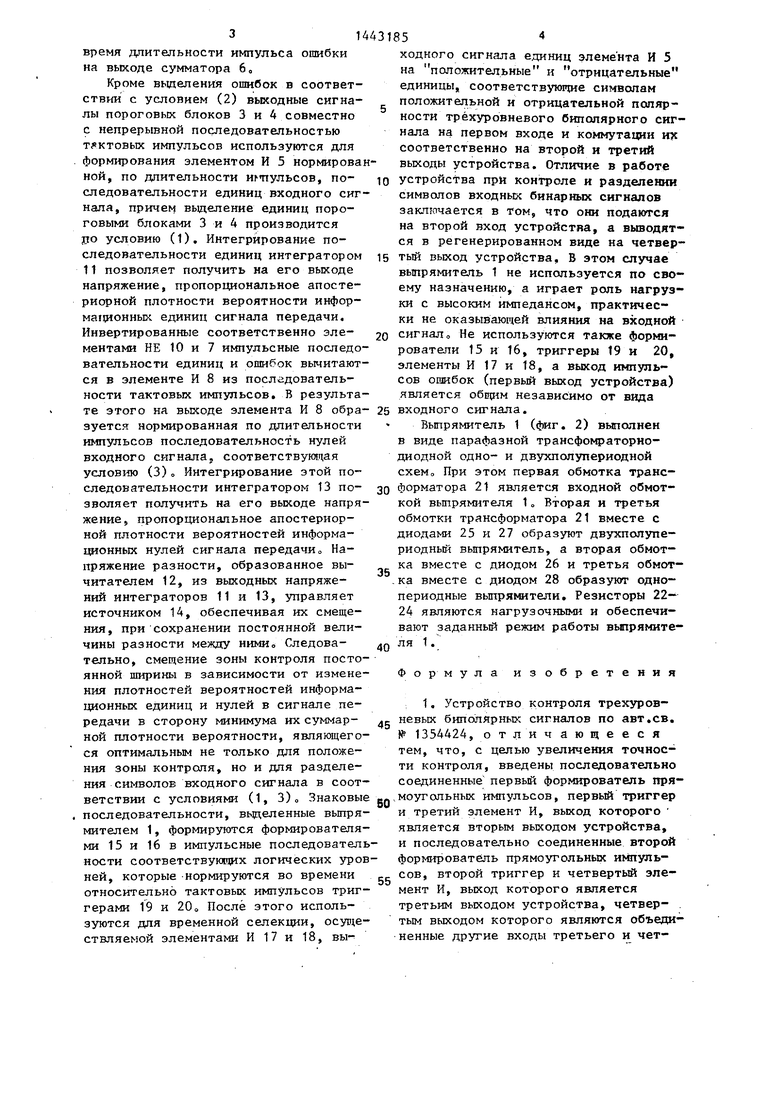

Выпрямитель 1 (фиг 2) содержит трансформатор 21 с тремя обмотками, резисторы 22-2.4 и диоды 25-28

Устройство работает следующим об- разомо

Работа устройства (фиг 1) заключается в TOMj что положительные и отрицательртые составлянлцие входного трехуровневог о биполярного сигнала разделяются выпрямителем 1 на две

5

0

0

5

униполярные знаковые последовательности, определяжщие знак составляющей входного сигнала, и одновременно объединяются в униполярный сигнал, являющийся модулем входного, исполь- зую1 1ийся в выделителе 2 для получения синхронной и синфазной с входным сигналом непрерьшной последовательности тактовых импульсов, по одному из фронтов которых формирователь 9 формирует короткие импульсы, определя- юпще моменты сравнения в пороговых блоках 3 и 4 выходного униполярного сигнала выпрямителя 1 с опорными напряжениями, обеспечивающими источником 14. Период этих импульсов, равный периоду тактовых, определяет длительность запоминания и соответственно длительность импульсов на выходе пороговых блоков 3 и 4о Величины опорных напряжений Цощи Uon-i соответственно пороговых блоков 3 и 4 имеют постоянную разность, определяющую зону контроля входного сигнала

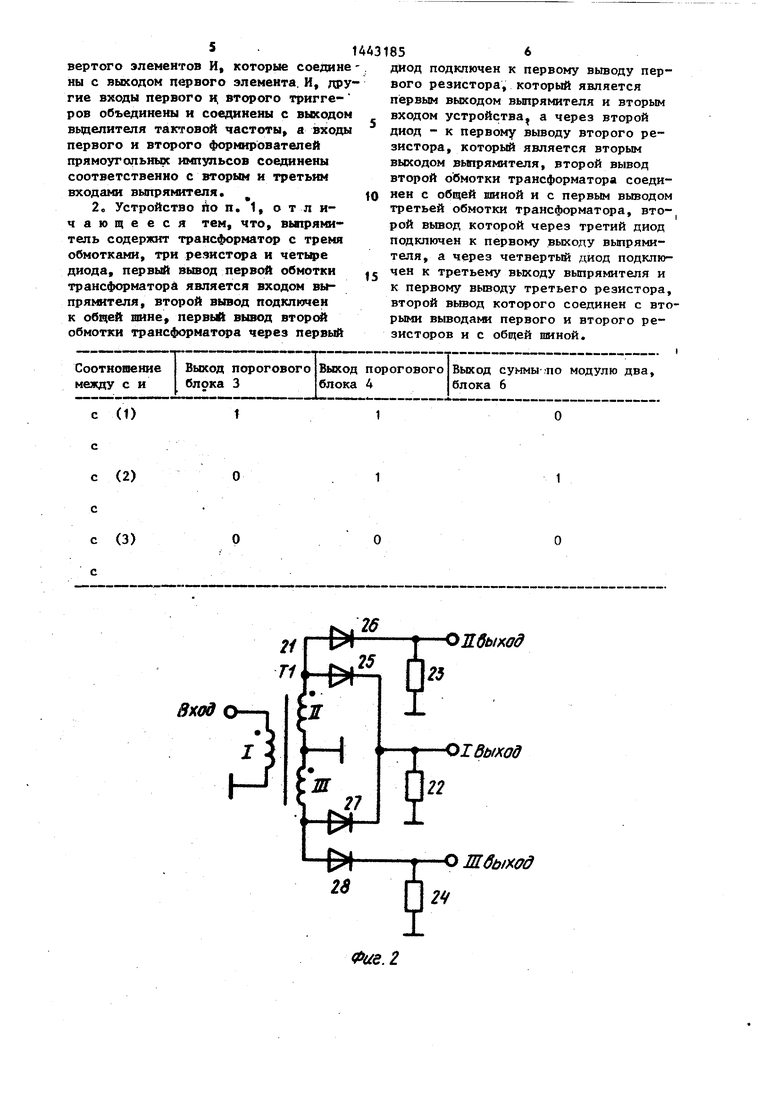

Если величина входного сигнала Uj в момент сравнения оказывается внутри зоны контроля, то она оценивается как ошибка. Вьщеление импульсов оигабок из выходных сигналов V и V пороговых блоков 3 и 4 осуществляет сумматор 6 в соответствии с соотношениями величин входного сигнала и опорных напряжений пороговых блоков (табЛо 1), причем число ошибок равно числу периодов тактов за

время длительности импульса ошибки на выходе сумматора 6,

Кроме вьщеления ошибок в соответствии с условием (2) выходные сигналы пороговых блоков 3 и 4 совместно с непрерывной последовательностью TJSKTOBbDC импульсов используются для формирования элементом И 5 нормированной, по длительности тттульсов, последовательности единиц входного сигнала, причем вьщеление единиц пороговыми блоками 3 и 4 производится jto условию (1). Интегрирование последовательности единиц интегратором 11 позволяет получить на его выходе напряжение, пропорциональное апостериорной плотности вероятности инфор- ма 1ионных единиц сигнала передачи. Инвертированные соответственно элементами НЕ 10 и 7 импульсные последовательности единиц и ошибок вычитаются в элементе И 8 из последовательности тактовых импульсов, В результате этого на выходе элемента И 8 образуется нормированная по длительности иьшульсов последовательность нулей входного сигнала, соответствующая условию (3)о Интегрирование этой последовательности интегратором 13 позволяет получить на его выходе напряжение, пропорциональное апостериорной плотности вероятностей информационных нулей сигнала передачи Напряжение разности, образованное вы- читателем 12, из выходных напряжений интеграторов 11 и 13, управляет источником 14, обеспечивая их смещения, при сохранении постоянной вели

чины разности между ними Следовательно, смещение зоны контроля постоянной ширины в зависимости от изменения плотностей вероятностей информационных единиц и нулей в сигнале передачи в сторону минимума их суммарной плотности вероятности, являющегося оптимальным не только для положения зоны контроля, но и для разделения символов входного сигнала в соответствии с условиями (1, 3)о Знаковые последовательности, вьделенные выпрямителем 1, формируются формирователями 15 и 16 в импульсные последовательности соответствуюр91х логических уровней, которые нормируются во времени относительно тактовых импульсов триггерами 19 и 20 После этого используются для временной селекции, осув;е- ствляемой элементами И 17 и 18, вы

ходкого сигнала единиц элемента И 5 на положительные и отрицательные единицы, соответствующие символам положительной и отрицательной полярности трёхуровневого биполярного сигнала на первом входе и коммутации соответственно на второй и третий выходы устройства. Отличие в работе

устройства при контроле и разделении символов входных бинарных сигналов заключается в том, что они подаются на второй вход устройства, а выводятся в регенерированном виде на четвертый выход устройства, В этом случае выпрямитель 1 не используется по своему назначению, а играет роль нагрузки с высоким импедансом, практически не оказывающей влияния на входной сигнал. Не используются также формирователи 15 и 16, триггеры 19 и 20, элементы И 17 и 18, а выход импульсов ошибок (первый выход устройства) является обвц1м независимо от вида входного сигнала.

Выпрямитель 1 ((jMr. 2) выполнен в виде парафазной трансфомраторно- диодной одно- и двухполупериодной схемо При этом первая обмотка трансформатора 21 является входной обмоткой вьтрямителя 1„ Вторая и третья обмотки трансформатора 21 вместе с диодами 25 и 27 образуют двухполупе- риодный вьирямитель, а вторая обмотка вместе с диодом 26 и третья обмотка вместе с диодом 28 образуют одно- периодные выпрямители. Резисторы 22- 24 являются нагрузочными и обеспечивают заданный режим работы выпрямителя 1.

5

g

О

Формула изобретения

2о Устройство йо п. 1, отличающееся тем, что, выпрямитель содержит трансформатор с тремя обмотками, три резист ч а и четыре диода, первый вывод первой обмотки трансформатора является входом выпрямителя, второй вывод подклпчен к общей внне, первый вывод вторЫ обмотки трансформатора через первый

(1)

(2)

(3)

Х

5

диод подключен к первому вьшоду первого резистора, который является первым выходом выпрямителя и вторым входом устройства а через второй диод - к первому выводу второго резистора, который является вторым выходом выпрямителя, второй вывод второй обмотки трансформатора соединен с общей шиной и с первым выводом третьей обмотки трансформатора, вто- рой вывод которой через третий диод подключен к первому выходу вьлрями- теля, а через четвертый диод подключен к третьему выходу выпрямителя и к первому вьтоду третьего резистора, второй вьгаод которого соединен с вторыми выводаг первого и второго резисторов и с общей шиной.

ОЖбымд

ОХВыкод

О Шбь1)ад

| Устройство контроля трехуровневых биполярных сигналов | 1986 |

|

SU1354424A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-12-07—Публикация

1987-04-06—Подача