Изобретение относится к радиотехнике и может использоваться при построении устройств контроля передачи Tf)exypoBHeBbrx: сигналов в цифровых каналах связи.

Цель изобретения - повышение точности контроля.

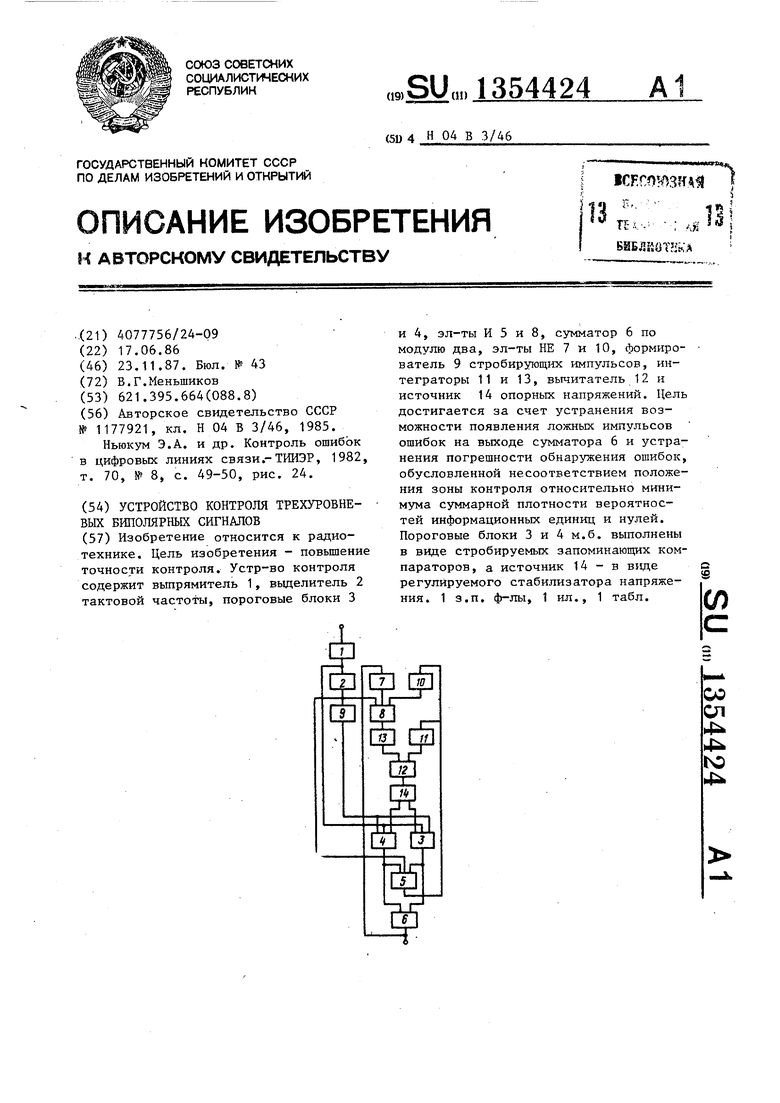

На-чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство контроля трехуровневых биполярных сигналов .содержит выпрямитель 1, выделитель 2 тактовой часто- ты, первый 3 и второй 4 пороговые блоки, выполненные в виде стробируе- мых запоминающих компараторов первый элемент И 5, сумматор 6 по модулю два, первый элемент НЕ 7, второй элемент И 8, формирователь 9 стробиругопщх импульсов, второй элемент НЕ 10, первый интегратор 11,. вычитатель 12, второй интегратор 13, источник 14 опорных напряжений, выполненный в виде регулируемого стабилизатора напряения. f

Устройство работает следующим образом.

Вьщелитель 2 тактовой частоты обеспечивает выделение из входного сигнала синхронной и синфазной с Hpqi

непрерывной последовательности тактовых имцульсов, из которых формирователь 9 стробирующих импульсов формирует узкие импульсы, определяющие мо- мент сравнения сигнала и опорных напряжений в первом 3 и втором 4 пороговых блоках и, следовательно, их срабатывание на каждом такте, что

в совокупности с запоминанием состояния между стробирующими импульсами в первом 3 и втором 4 пороговых блоках обеспечивает нормирование по длительности их выходных импульсов, благодаря чему устраняется возможность появления ложных импульсов ошибок на выходе сумматора 6 по модулю два и повьшается точность контроля ошибок в канале связи. Первый элемент И 5 из выходных сигналов первого 3 и второго 4 пороговых блоков и тактовых импульсов, скважность которых равна двум, формирует нормированную по длительности импульсов последовательность единиц, являющуюся модулем информационных единиц входного сигнала при условии |U(t)| ,.при , и„„,идп,, , где

и

ОП1

Uc(t) - модуль входного сигнала.

t(, - момент стробирования, UQ, и Ugj - опорные напряжения первого 3 и второго 4 пороговых блоков, Второй элемент И 8 из тактовых импульсов и инверсных последовательностей единиц и ошибок формирует нормированную по длительности импульсов последовательность нулей, являющихся 0 информационными нулями входного сигнала при условии |U(,,(t), , при

5

5

0

0

5

0

5

о

,

опг

Полученные, таким

образом, последовательности импульсов единиц и нулей интегрируются, соответственно первым 11 и вторым 13 интеграторами, из выходных напряжений которых, пропорциональных плотностям вероятностей информационных единиц и нулей входного сигнала, вы- 0 читателем 1.2 формируется напряжение разности, управляющее одновременным сдвигом в источнике 14 опорных напряжений величин Ugp, и сохранении постоянной величины разности между ними и, следовательно, ширины зоны контроля, величина сдвига которой и его знак, определяемые величиной и знаком напряжения разности, таковы, что положение зоны контроля автоматически приходит в соответствие миниму1лу апостериорной суммарной плотности вepoятнocтJИ информационных единиц и нз лей в сигнале передачи ,

благодаря чему устраняется погреш- 5 кость обнаружения ошибок, обусловленная несоответствием положения зоны контроля относительно минимума суммарной плотцости вероятностей информационных единиц и нулей и повышается точность контроля ошибок в канале связи.

Положительные и отрицательные составляющие входного трехуровневого биполярного сигнала объединяются выпрямителем 1 в униполярный сигнал, использующийся в выделителе 2 тактовой частоты для получения синхронной и синфазной с входньм сигналом непрерывной последовательности тактовых импульсов, по одному из фронтов которых формирователь 9 стробирующих импульсов формирует короткие импульсы, определяющие моменты сравнения в первом 3 и втором 4 пороговых блоках выходного униполярного сигнала выпрямителя 1 с опорными напряжениями, обеспечиваемыми источником 14 опорных напряжений, а период этих импульсов, равный периоду тактовых, определяет длительность запоминания и, соответственно, длительность импульсов на выходе первого 3 и второго 4 пороговых блоков. Величины опорных

напряжений и

от

и и

jQ соответственно первого 3 и второго 4 пороговых блоков, причем Uon,U(jn, имеют постоянную разность, определяющую зону контроля входного сигнала. Если величина входного сигнала U, в момент сравнения оказывается внутри зоны контроля, то она оценивается как ошибка.

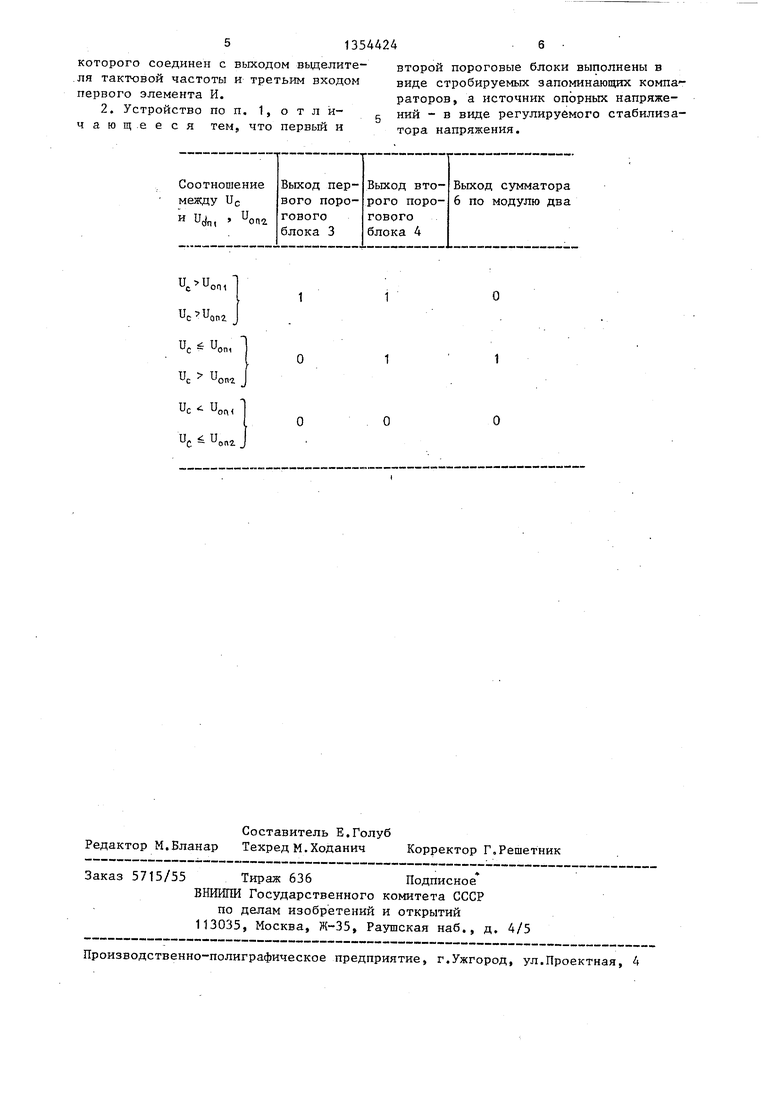

Выделение импульсов ошибок из выходных сигналов V, и V соответственно первого 3 и второго 4 пороговых блоков осуществляет сумматор 6 по модулю два в соответствии с соот- ношениями величин входного сигнала и опорных напряжений пороговых блоков, приведенными в таблице, причем число ошибок равно числу периодов тактов за время длительности импульса ошибки на выходе сумматора 6 по модулю два.

Кроме выделения ошибок, в соответствии с таблицей выходные сигналы первого 3 и второго 4 пороговых блоков совместно с непрерьтной последовательностью тактовых импульсов используются для формирования первым элементом И 5 нормированной по длительности импульсов последовательности единиц входного сигнала, при- чем вьщеление единиц первым 3 и вторым 4 пороговыми блоками производится по таблице. Интегрирование послеf

довательности единиц первым интегратором 11 позволяет получить на его выходе напряжение, пропорциональное апостериорной плотности вероятности информационных единиц сигнала передачи. Инвертированные соответственно первым 7 и вторым 10 элементами НЕ импульсные последовательности единиц .и ошибок вычитаются во втором элементе И 8 из последовательности тактовых импульсов, в результате чего на вьтхопе второго элемента И 8 образуется нормированная, по длительности импульсов последовательность нуле входного сигнала, соответствующая таблице. Интегрирование этой последо вательности вторым интегратором 13 позволяет получить на его выходе напряжение, пропорциональное апостериорной плотности вероятностей инфор

54424

мационных нулей сигнала передачи. Напряжение разности, образованное вы- читателем 12 из выходных напряжений первого 11 и второго 13 интеграторов, управляет источником 14 опорных напряжений, обеспечивая их смещение, при сохранении постоянной величины разности между ними и, следовательно, 1Q смещение зоны контроля постоянной ширины в зависимости от изменения плотностей вероятностей информационных единиц и нулей в сигнале передачи в сторону минимума их суммарной 15 плотности вероятности, которьш является оптимальным для положения, зоны контроля,30

Формула изобретения

20

1, Устройство контроля трехуровневых биполярных сигналов, содержащее выпрямитель, вход которого является входом устройства, а выход подключен 25 к первым входам первого и второго пороговых блоков, источник опорных напряжений, первый и второй выходы которого подключены к вторым входам соответственно первого и второго пороговых блоков, сумматор по модулю два, выход которого является выходом уст5

0

5

5

0

ройства, а первый и второй входы соединены с выходами соответственно первого и второго пороговых блоков, отличающееся тем, что, с целью повышения точности контроля, введены последовательно соединенные вьщелитель тактовой частоты, вход которого соединен с выходом вьтрями- теля, и формирователь стробирующих импульсов, выход которого подключен к стробирующим входам первого и второго пороговых блоков, последовательно соединенные первый элемент И, первый и второй входы которого соединены с выходами соответственно первого и второго пороговых блоков, первый интегратор и вычитатель, выход которого подключен к входу источника опорных напряжений, последовательно соединенные первый элемент НЕ, вход которого соединен с выходом сумматора по модулю два, второй элемент И и второй интегратор, выход которого подключен к второму входу вычитателя, второй элемент НЕ, вход и выход которого соединены соответственно с выходом первого элемента Ни вторым входом второго элемента И, третий вход

513544246

которого соединен с выходом выделите-второй пороговые блоки выполнены в

ля тактовой частоты и третьим входомвиде стробируемых запоминающих компапервого элемента И.раторов, а источник опорных напряже2. Устройство по п, 1, о т л й- „ий - в виде регулируемого стабилизачающееся тем, что первый итора напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля трехуровневых биполярных сигналов | 1987 |

|

SU1443185A2 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Адаптивный дискретный согласованный фильтр | 1981 |

|

SU995284A1 |

| Устройство регенерации трехуровневого биполярного сигнала | 1989 |

|

SU1800648A1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

Изобретение относится к радиотехнике. Цель изобретения - повьшение точности контроля. Устр-во контроля содержит вьтрямитель 1, вьщелитель 2 тактовой частоты, пороговые блоки 3 и 4, эл-ты И 5 и 8, сумматор 6 по модулю два, эл-ты НЕ 7 и 10, формирователь 9 стробирующих импульсов, интеграторы 11 и 13, вычитатель 12 и источник 14 опорных напряжений. Цель достигается за счет устранения возможности появления ложных импульсов ошибок на выходе сумматора 6 и устранения погрешности обнаружения ошибок, обусловленной несоответствием положения зоны контроля относительно минимума суммарной плотности вероятностей информационных единиц и нулей. Пороговые блоки 3 и 4 м.б. выполнены в виде стробируемых запоминающих компараторов , а источник 14 - в В1ще регулируемого стабилизатора напряжения. 1 з.п. ф-лы, 1 ил., 1 табл. Q « (Л

| Авторское свидетельство СССР № 1177921, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Ньюкум Э.А | |||

| и др | |||

| Контроль ошибок в цифровых линиях связи .-ТИИЭР, 1982, т | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

Авторы

Даты

1987-11-23—Публикация

1986-06-17—Подача