N)

Изобретение относится к радиотехнике, может быть Использовано для подавления помех, например, при измерении малых сигналов на фоне значительно превосходящих их по уровню промыпленных помех и является усовершенствованием Изобретения по авт. св. № 1187242.

Цель изобретения - расширение ди- :апазона управления полосой режекции |и повышение помехоустойчивости блока (управления,

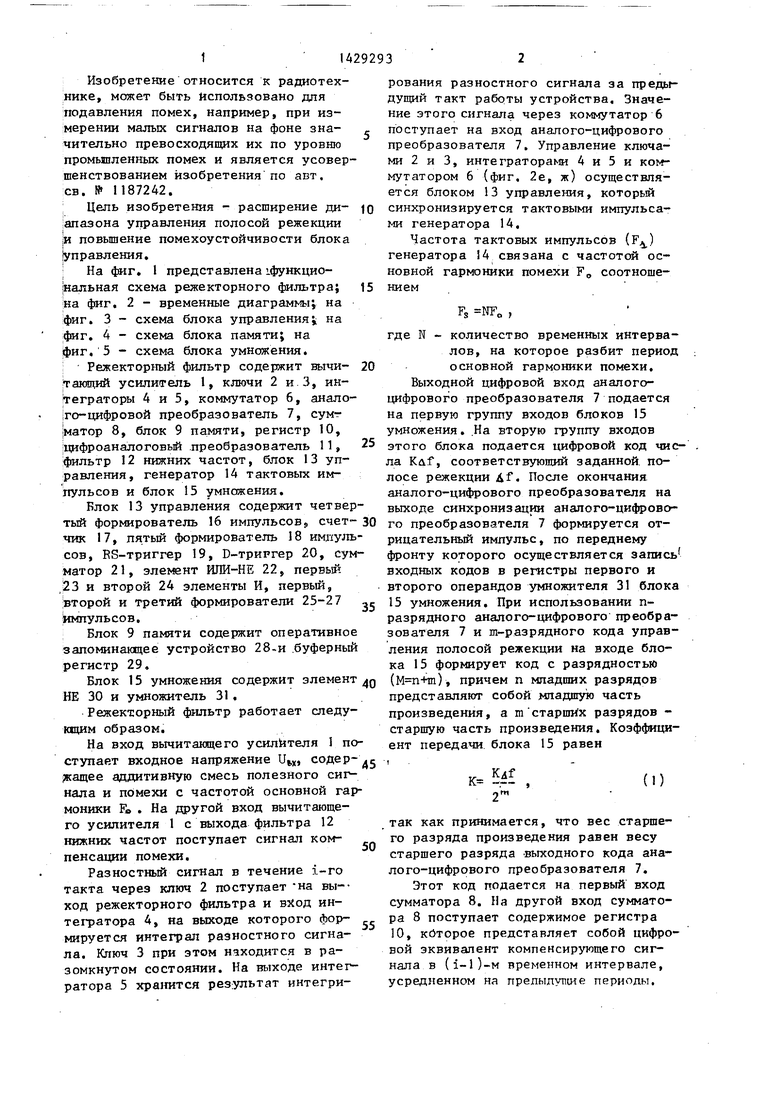

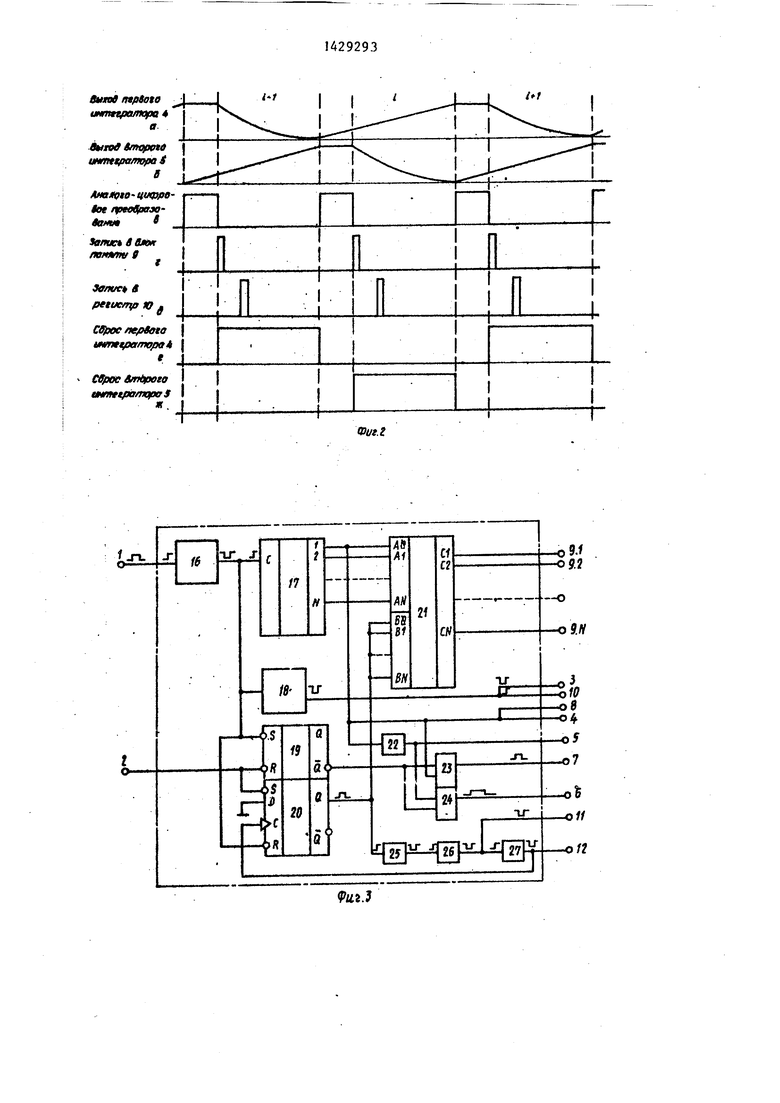

; На фиг, 1 представлена 1функцио- |нальная схема режекторного фильтра; «а фиг. 2 - временные диаграммыj на фиг. 3 - схема блока управленияj на ;фиг, 4 - схема блока памяти; на фиг. 5 - схема блока умножения. ; Режекторный фильтр содержит вычи- |так)щий усилитель 1, ключи 2 и.З, интеграторы 4 и 5, коммутатор 6, анало- |го-цифровой преобразователь 7, сум- 1матор 8, блок 9 , регистр 10, |цифроаналоговый .преобразователь 11, фильтр 12 нижних частот, блок 13 управления, генератор 14 тактовых импульсов и блок 15 умножения.

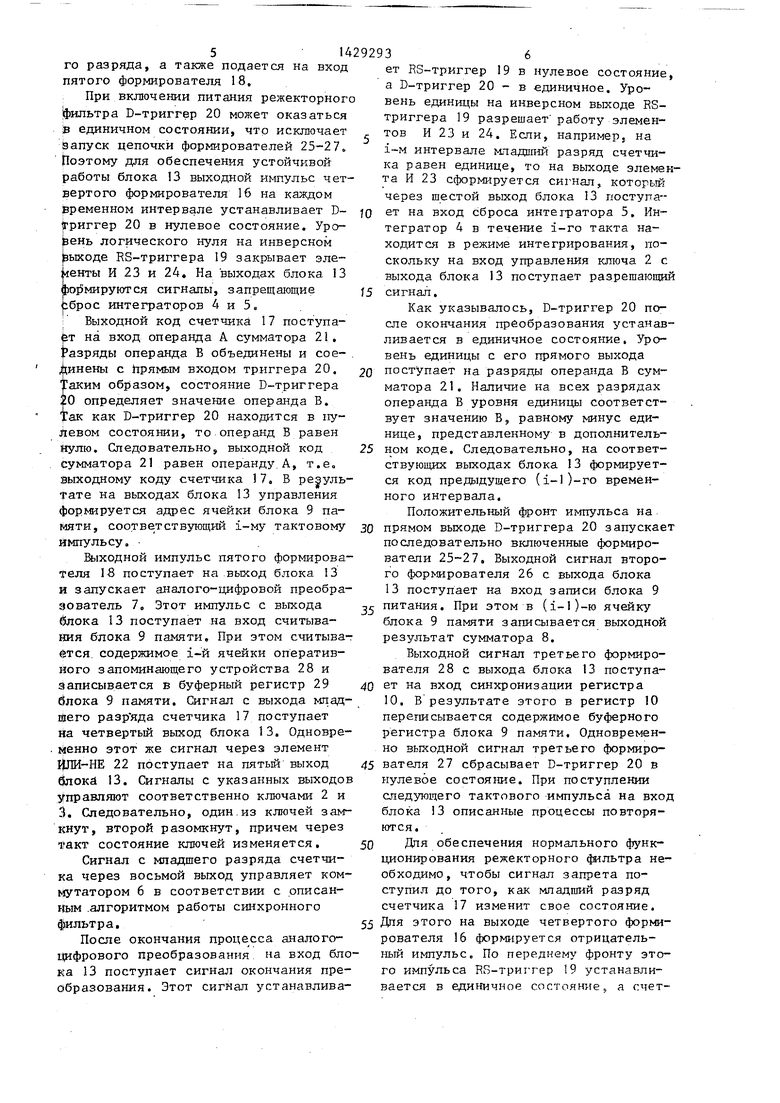

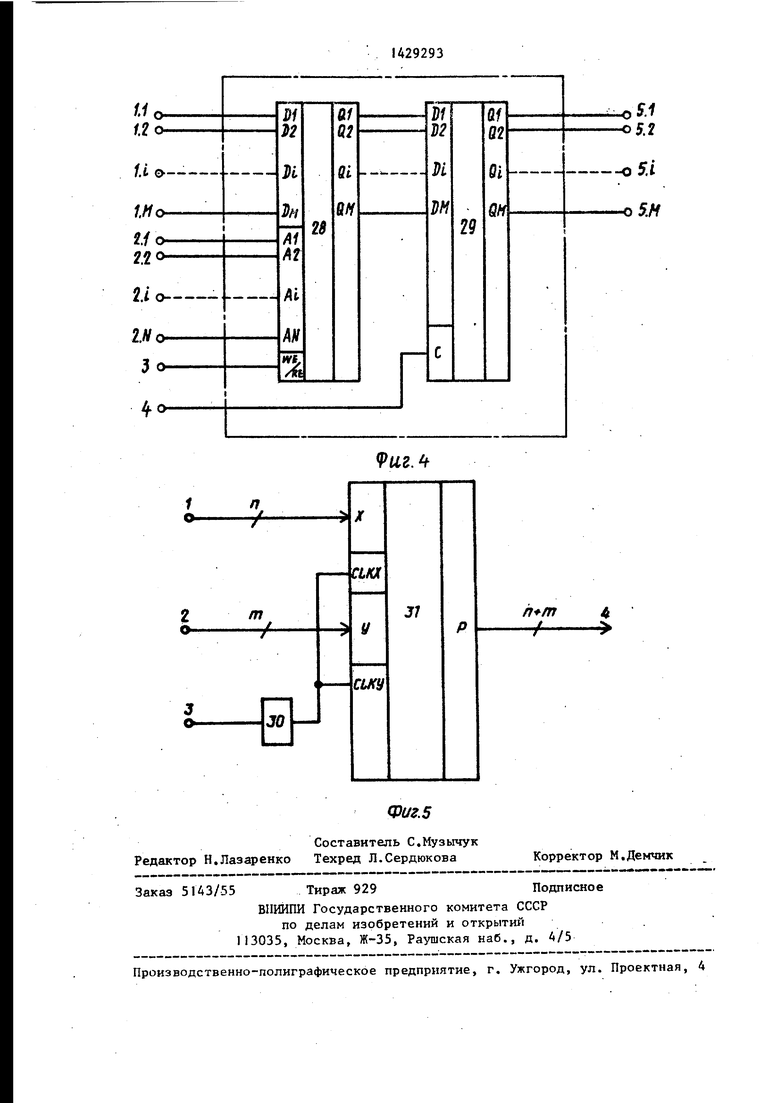

Блок 13 управления содержит четвертый формирователь 16 импульсов., счет- чик 17, пятый формирователь 18 имлуль сов, RS-триггер 19, D-триргер 20, сумматор 21, элемент ЙПИ-НЕ 22, первый 23 и второй 24 элементы И, первый, второй и третий формирователи 25-27 импульсов.

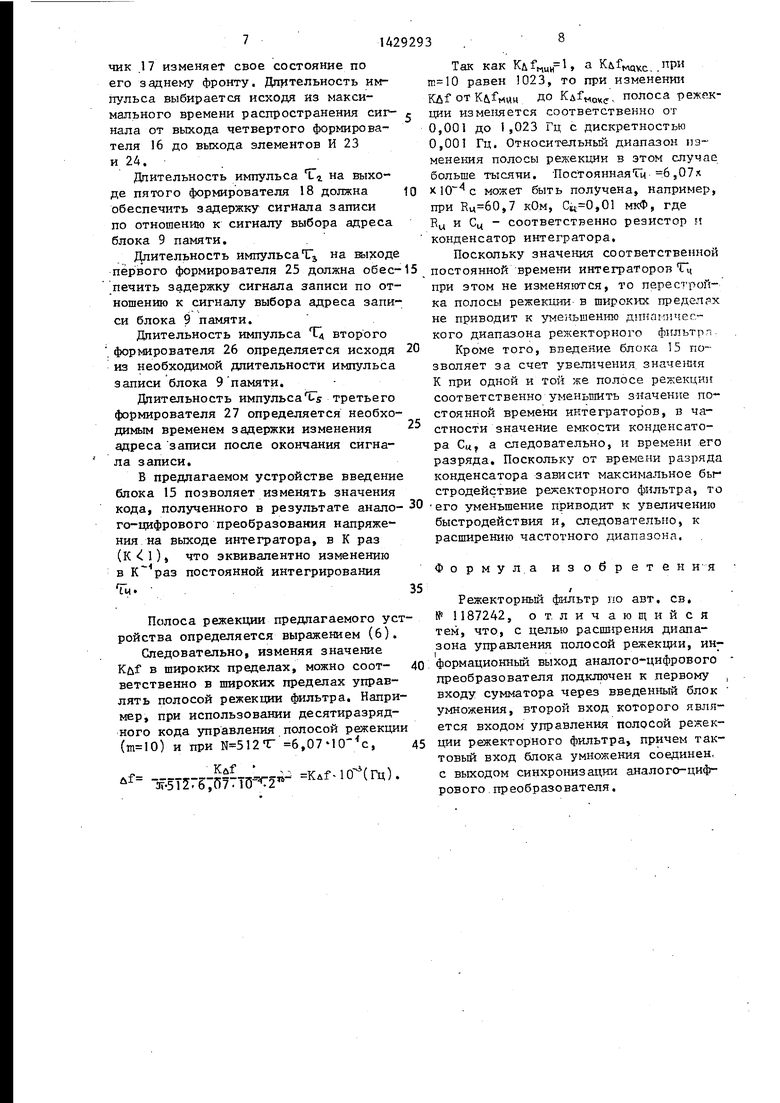

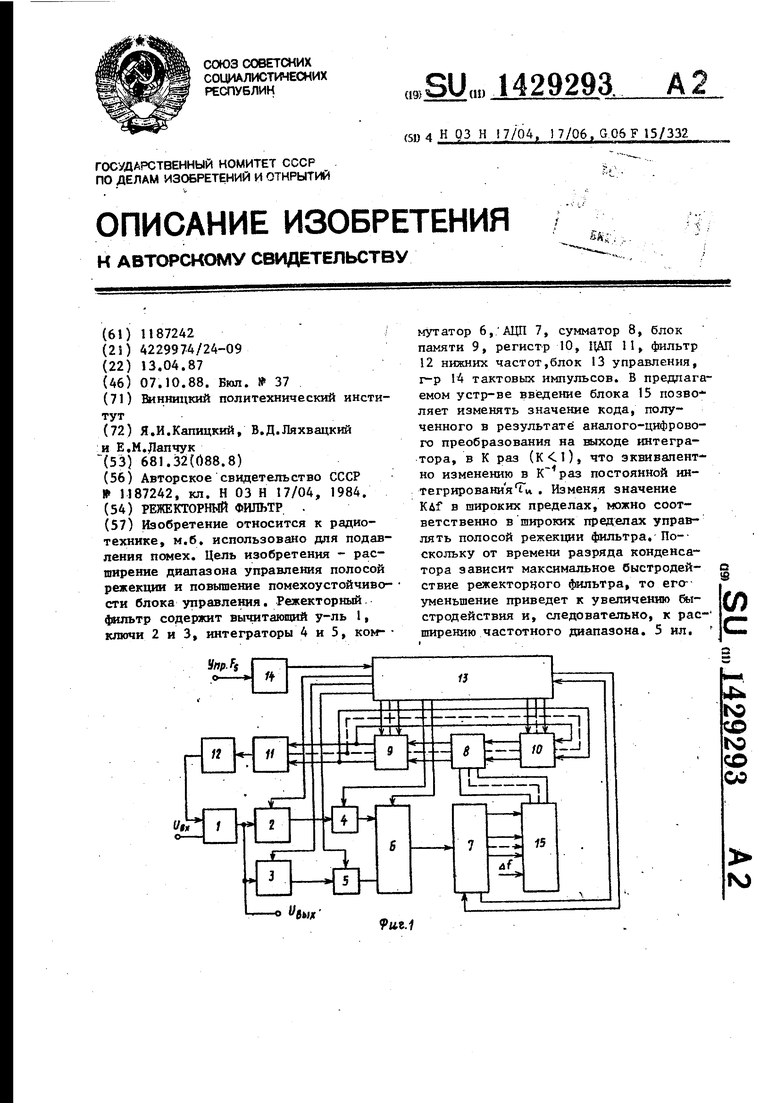

Блок 9 памяти содержит оперативное запоминающее устройство 28-и .буферный регистр 29.

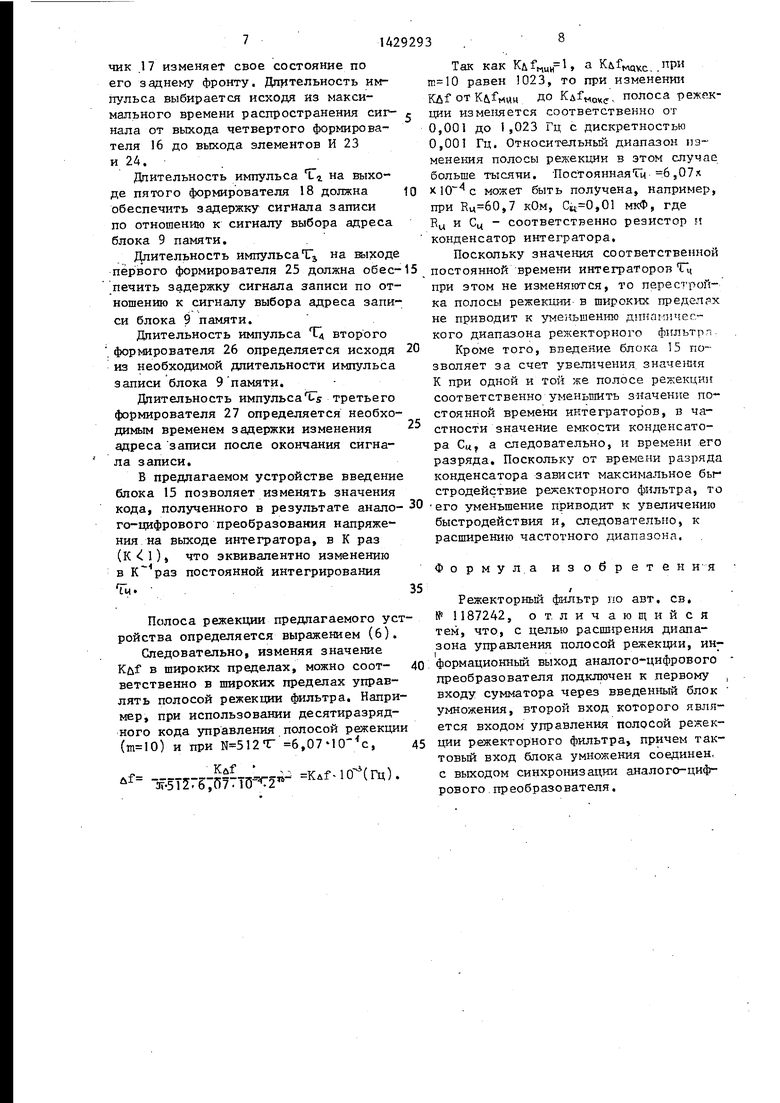

Блок 15 умножения содержит элемент НЕ 30 и умножитель 31.

Режекторный фильтр работает следу- гацим образом.

На вход вычитающего усилИтеля 1 поступает входное напряжение U, содерЗкащее аддитивную смесь полезного сигнала и помехи с частотой основной гармоники Fe . На другой вход вычитающего усилителя 1 с выхода фильтра 12 нижних частот поступает сигнал компенсации помехи.

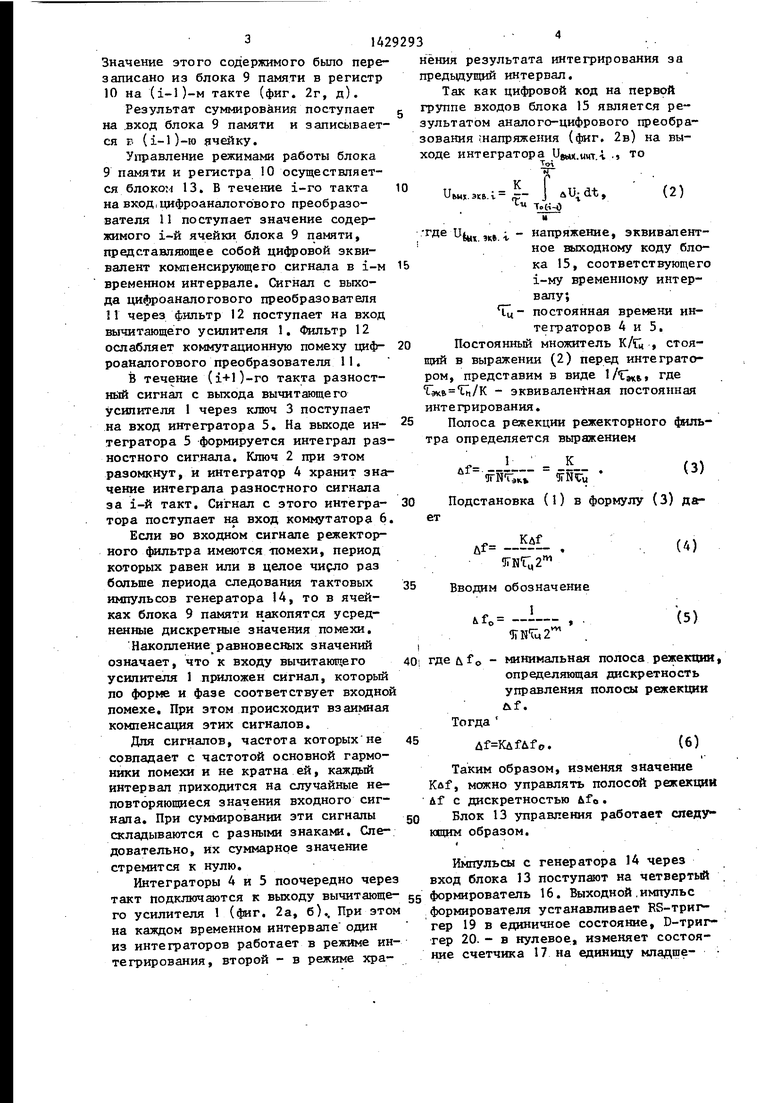

Разностный сигнал в течение i-ro такта через ключ 2 поступает на вы-- ход режекторного фильтра и вход интегратора 4, на выходе которого фор- мируется интеграл разностного сигнала. Ключ 3 при этом находится в разомкнутом состоянии. На выходе интегратора 5 хранится рез;ультат интегри

рования разностного сигнала за предыдущий такт работы устройства. Значение этого сигнала через коммутатор 6 поступает на вход аналого-цифрового преобразователя 7. Управление ключами 2 и 3, интеграторами 4 и 5 и коммутатором 6 (фиг. 2е, ж) осуществляется блоком 13 управления, которьй синхронизируется тактовыми импульсами генератора 14.

Частота тактовых импульсов (F) генератора 14 связана с частотой основной гармоники помехи F соотношением

FS NF, ,

где N - количество временных интервалов, на которое разбит период основной гармоники помехи. Выходной цифровой вход аналого- цифрового преобразователя 7 подается на первую группу входов блоков 15 умножения, .На вторую группу входов этого блока подается цифровой код числа Kuf, соответствующий заданной полосе режекции if. После окончания аналого-цифрового преобразователя на выходе синхронизации аналого-цифрового преобразователя 7 формируется отрицательный импульс, по переднему фронту которого осуществляется запись входных кодов в регистры первого и второго операндов умножителя 31 блока 15 умножения. При использовании п- разрядного аналого-цифрового преобразователя 7 и т-разрядного кода управления полосой режекции на входе блока 15 формирует код с разрядностью (), причем п младших разрядов представляют собой младшую часть произведения, а т старших разрядов - старшую часть произведения. Коэффициент передачи блока 15 равен

.. -- ,

так как принимается, что вес старшего разряда произведения равен весу старшего разряда выходного кода аналого-цифрового преобразователя 7.

Этот код подается на первый вход сумматора 8. На другой вход сумматора 8 поступает содержимое регистра 10, кйторое представляет собой цифровой эквивалент компенсирующего сигнала в (i-l)-M временном интервале, усредненном на прелылупще пери)ды.

Значение этого содержимого бьшо перезаписано из блока 9 памяти в регистр

10на (i-l)-M такте (фиг. 2г, д). Результат суммирования поступает

на .вход блока 9 памяти и записывается в (i-l)-io ячейку.

Управление режимами работы блока 9 памяти и регистра 10 осуществляется блоком 13. В течение i-ro такта на вхоД|Цифроаналогового преобразователя 11 поступает значение содержимого i-й ячейки блока 9 памяти, представляющее собой цифровой зкви- вапент компенсирующего сигнала в i-м временном интервале. Сигнал с выхода цифроаналогового преобразователя

11через фильтр 12 поступает на вход вычитающего усилителя 1. Фильтр 12 ослабляет коммутационную помеху циф- роаналогового преобразователя 11.

В течение (i+l)-го такта разност- нйй сигнал с выхода вычитающего усипителя 1 через ключ 3 поступает на вход интегратора 5. На выходе ин- тегратора 5 формируется интеграл разностного сигнала. Ключ 2 при этом разомкнут, и интегратор 4 хранит значение интеграла разностного сигнала за i-й такт. Сигнал с этого интегра- тора поступает на вход коммутатора 6

Бели во входном сигнале режектор- ного фильтра имеются -помехи, период которых равен или в целое чирло раз больше периода следования тактовых импульсов генератора 14, то в ячейках блока 9 памяти накопятся усредненные дискретные значения помехи.

Накопление равновесных значений

нения результата интегрирования за предьщущий интервал.

Так как цифровой код на первой группе входов блока 15 является результатом аналого-цифрового преобразования (Напряжения (фиг. 2в) на выходе интегратора Ug«x.uHT4 . то

к г ..

.f- J i

dt.

(2)

7oCi-0 u

ет

где U|y ,j 4, - напряжение, эквивалент- ное выходному коду блока 15, соответствующего i-му временному интервалу;

ц- постоянная времени интеграторов 4 и 5. Постоянный множитель K/tli стоящий в выражении (2) перед интегратором, представим в виде 1/Тжь где T9K6 Lrt/K - эквивалентная постоянная интегрирования.

Полоса режекции режекторного фильтра определяется выражением

f- i. .К. OTN u

(3)

Подстановка (1) в формулу (З) дадг KAL ,

5ГиГу2

Вводим обозначение 1

bfo

JrN u,2

| название | год | авторы | номер документа |

|---|---|---|---|

| Режекторный фильтр | 1986 |

|

SU1417180A2 |

| Цифровой режекторный фильтр | 1988 |

|

SU1608786A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАПРАВЛЕНИЯ НА ИСТОЧНИК СИГНАЛА | 2012 |

|

RU2484495C1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАПРАВЛЕНИЯ НА ИСТОЧНИК СИГНАЛА | 2011 |

|

RU2486535C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАПРАВЛЕНИЯ НА ИСТОЧНИК СИГНАЛА | 2012 |

|

RU2486534C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2253183C1 |

| Анализатор амплитуд и частот формант речевого сигнала | 1981 |

|

SU953658A1 |

Изобретение относится к радиотехнике, м.б. использовано для подавления помех. Цель изобретения - расширение диапазона управления полосой режекции и повышение помехоустойчивости блока управления. Режекторный. содержит вычитающий у-ль I, ключи 2 и 3, интеграторы 4 и 5, ком- мутатор 6,;АЦП 7, сумматор В, блок памяти 9, регистр 10, ЦАП 11, фильтр 12 нижних частот,блок 13 управления, г-р 1А тактовых импульсов. В предлагаемом устр-ве введение блока 15 позво- ляет изменять значение кода, полученного в результате аналого-цифрового преобразования на выходе интегратора, в К раз (), что эквивалентно изменению в К раз постоянной интегрирования Ти . Изменяя значение Кif в широких пределах, можно соответственно в широких пред:елах управлять полосой режекции фильтра. По-- скольку от времени разряда конденсатора зависит максимальное быстродействие режекторного фильтра, то его- уменьшение приведет к увеличению быстродействия и, следовательно, к рас- ширению частотного диапазона. 5 ил. (П с

усилителя 1 приложен сигнал, который по форме и фазе соответствует входной помехе. При этом происходит взаимная компенсация этих сигналов.

Для сигналов, частота которых не 45 совпадает с частотой основной гармоники помехи и не кратна ей, каждый интервал приходится на случайные неповторяющиеся значения входного сигнала. При суммировании эти сигналы QQ складываются с разными знаками. Сле- довательио, их суммарное значение стремится к нулю.

Интеграторы 4 и 5 поочередно через

Тогда

Af KAfufo.

(6)

Таким образом, изменяя значение Kuf, можно управлять полосой режекции Af с дискретностью &fo.

Блок 13 управления работает следующим образом.

Импульсы с генератора 14 через вход блока 13 поступают на четвертый

такт подключаются к выходу вычитающе- 55 формирователь 16. Выходной.импульс го усилителя 1 (фиг. 2а, б).. При этом формирователя устанавливает RS-триг- на каждом временном интервале один из интеграторов работает в режиме ингер 19 в единичное состояние, D-триг гер 20. - в нулевое, изменяет состояние счетчика 17 на единицу кла1дщетегрирования, второй - в режиме хра40. - минимальная полоса режекцни, определяющая дискретность управления полосы режекцки &f.

Тогда

Af KAfufo.

(6)

Таким образом, изменяя значение Kuf, можно управлять полосой режекции Af с дискретностью &fo.

Блок 13 управления работает следующим образом.

формирователь 16. Выходной.импульс формирователя устанавливает RS-триг-

гер 19 в единичное состояние, D-триг- гер 20. - в нулевое, изменяет состояние счетчика 17 на единицу кла1дщего разряда, а также подается на вход пятого формирователя 18.

При включении питания режекторног (фильтра D-триггер 20 может оказаться iB единичном состоянии, что исключает запуск цепочки формирователей 25-27. Поэтому для обеспечения устойчивой работы блока 13 выходной иьшульс четвертого формирователя 16 на каждом рременном интервале устанавливает D- |григгер 20 в нулевое состояние. Уровень логического нуля на инверсном зькоде BS-триггера 19 закрывает элементы И 23 и 24, На выходах блока 13 (Ьо15мируются сигналы, запрещающие интеграторов 4 и 5. : Выходной код счетчика 17 поступа- т на вход операнда А сумматора 21, разряды операнда В объединены и сое- ;инены с прямым входом триггера 20. аким образом, состояние D-триггера О определяет значение операнда В, ак как D-триггер 20 находится в нулевом состоянии, то операнд В равен Нулю, Следовательно, выходной код сумматора 21 равен операнду. А, т,е„ выходному коду счетчика 17, В тате на выходах блока 13 управления формируется адрес ячейки блока 9 памяти, соответствующий i-му тактовому импульсу,

.входной импульс пятого формирователя IS поступает на выход блока 13 и запускает аналого-цифровой преобразователь 7, Этот импульс с выхода блока 13 поступает на вход считывания блока 9 памяти. При этом считывается. содержимое i-й ячейки оперативного запоминающего устройства 28 и записывается в буферный регистр 29 блока 9 памяти. Сигнал с выхода младшего разр яда счетчика 17 поступает на четвертый выход блока 13, Одновременно этот же сигнал через элемент Р ЛИ-НЕ 22 поступает на пятьй выход блоки 13, Сигналы с указанных выходов управляют соответственно ключами 2 и 3, Следовательно, один-из ключей замкнут, второй разомкнут, причем через такт состояние ключей изменяется,

Сигнал с младшего разряда счетчика через восьмой выход управляет коммутатором 6 в соответствии с описанным .алгоритмом работы синхронного фильтра.

После окончания процесса аналого- цифрового преобразования на вход блока 13 поступает сигнал окончания преобразования. Этот сигнал устанавливает ЙЗ-триггер 19 в нулевое состояние, а Б-триггер 20 - в единичное. Уровень единицы на инверсном выходе RS- триггера 19 разрешает работу элементов И 23 и 24, Если, например, на интервале младший разряд счетчика равен единице, то на выходе элемента И 23 сформируется сигнал, который через шестой выход блока 13 поступает на вход сброса интегратора 5, Интегратор 4 в течение 1-го такта находится в режиме интегрирования, поскольку на вход управления ключа 2 с выхода блока 13 поступает разрешающий

сигнал.

Как указывалось, D-триггер 20 после окончания преобразования устанавливается в единичное состояние. Уровень единицы с его прямого выхода

поступает на разряды операнда В сумматора 21. Наличие на всех разрядах операвда В уровня единицы соответствует значению В, равному минус единице, представленному в дополнительном коде. Следовательно, на соответствующих выходах блока 13 формируется код предыдущего (i-l)-ro временного интервала.

Положительный фронт импульса на

прямом выходе D-триггера 20 запускает последовательно включенные формирователи 25-27, Выходной сигнал второго формирователя 26 с выхода блока 13 поступает на вход записи блока 9

питания. При этом в (1-1)-ю ячейку блока 9 памяти записывается выходной результат сумматора 8,

Выходной сигнал третьего формирователя 28 с выхода блока 13 поступает на вход синхронизации регистра 10. В результате этого в регистр 10 переписывается содержимое буферного регистра блока 9 памяти. Одновременно выходной сигнал третьего формирователя 27 сбрасывает D-триггер 20 в нулевое состояние. При поступлении следующего тактового импульса на вход блока 13 описанные процессы повторяются,

Для обеспечения нормального функционирования режекторного фильтра необходимо, чтобы сигнал запрета поступил до того, как младший разряд счетчика 17 изменит свое состояние.

Для этого на выходе четвертого формирователя 16 формируется отрицательный импульсе По переднему фронту этого импульса RS-триггер 19 устанавливается в единичное состояние,, а счетчик 17 изменяет свое состояние по его заднему фронту. Длительность импульса выбирается исходя из максимального времени распространения сиг- нала от выхода четвертого формирователя 16 до выхода элементов И 23 и 24.

Дпительность импульса Тг на выходе пятого формирователя 18 должна обеспечить задержку сигнала записи по отношению к сигналу выбора адреса блока 9 памяти. .

Дпительность импульса Tj на выходе первого формирователя 25 должна обес печить задержку сигнала записи по отношению к сигналу выбора адреса записи блока 9 памяти.

Длительность импульса Тд второго . формирователя 26 определяется исходя из необходимой длительности импульса записи блока 9 памяти.

Длительность импульс а ТТ. третьего формирователя 27 определяется необходимым временем задержки изменения адреса записи после окончания сигнала записи.

В предлагаемом устройстве введение блока 15 позволяет изменять значения кода, полученного в результате анало- го-цифрового преобразования напряжения на выходе интегратора, в К раз (), что эквивалентно изменению в постоянной интегрирования Ти.

Полоса режекции предлагаемого устройства определяется выражением (6).

Следовательно, изменяя значение Kuf в широких пределах, можно соот- ветственно в широких пределах управлять полосой режекции фильтра. Например, при использовании десятиразрядного кода управления полосой режекции

() и при Т 6,07ЧО с,

-f -лГ.5Тггб-7 7-тс--:2-- (гц).

5

0

5

0 5

0

5

Так как КлГмин и а при равен 1023, то при изменении KAfoTK/ fnv H ДО КдГ„с„(,, полоса режекции изме11яется соответственно от 0,001 до 1,023 Гц с дискретностью 0,001 Гц. Относительньш диапазон пз- менения полосы режекции в этом случае больше тысячи. ПосТояннаяТц 6,07л )(10 с может быть получена, например, при ,7 кОм, ,01 мкФ, где Ry и Сц - соответственно резистор и конденсатор интегратора.

Поскольку значения соответственной постоянной времени интеграторов Тц при этом не изменяются, то перест рой- ка полосы режекшш- в широких пределРХ не приводит к уменьшеш-ш динамического диапазона режекторного фильтрлКроме того, введение блока 15 позволяет за счет увешгчения. значе1шя К при одной и той же полосе режекци соответственно уменьвшть з-наченне постоянной времени интеграторов, в частности значение емкости конденсатора Си, а следовательно, и времени его разряда. Поскольку от времени разряда конденсатора зависит максимальное бы стродействие режекторного фильтра, то его уменьшение приводит к увеличению быстродействия и, следовательно, к расширению частотного диапазона.

Формула изобретен и я

/

Режекторньй фильтр по авт. ев,

№ 1187242, отличающийся тем, что, с целью расширения диапазона управления полосой режекции, информационный выход аналого-цифрового преобразователя подключен к первому , входу сумматора через введенный блок умножения, второй вход которого является входом управления полосой режекции режекторного фильтра, причем тактовый вход блока умножения соединен, с выходом синхро1шза1 ки аналого-цифрового преобразователя.

iHfttoto

uHmnflomape 4

a

nff tmtyme

UHmttpamopa ii 8

9 игл

| Авторское свидетельство СССР 1187242, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-07—Публикация

1987-04-13—Подача