13.1

п.г

JS.ffff

г№.т,

.f7

4iai . ЭО

4

йзоёретение относится к вьиисли- тельной технике и технике связи и может использоваться в системах хранения, обработки и передачи цифровой ин формации, в том числе по линиям связ с многопозйционной модуляцией,

.Цель изобретенид - упрощение устройства и расширение области его применения за счет обеспечения возмож- ности кодирования нелинейных кодов.

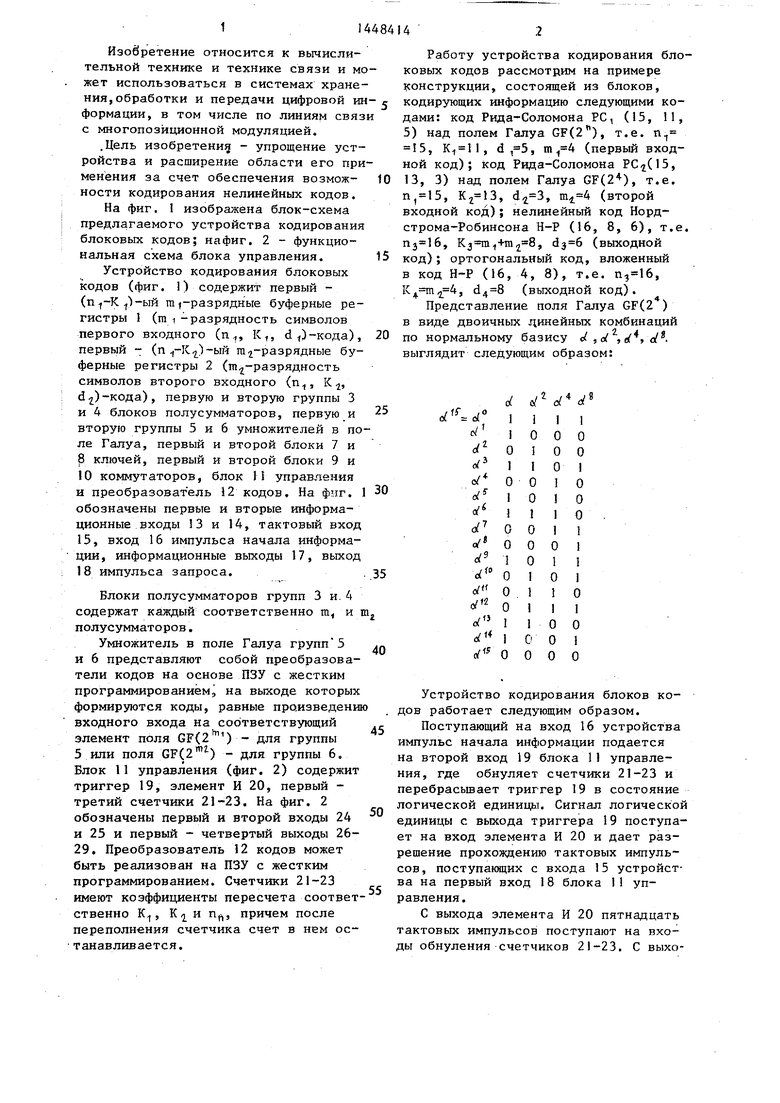

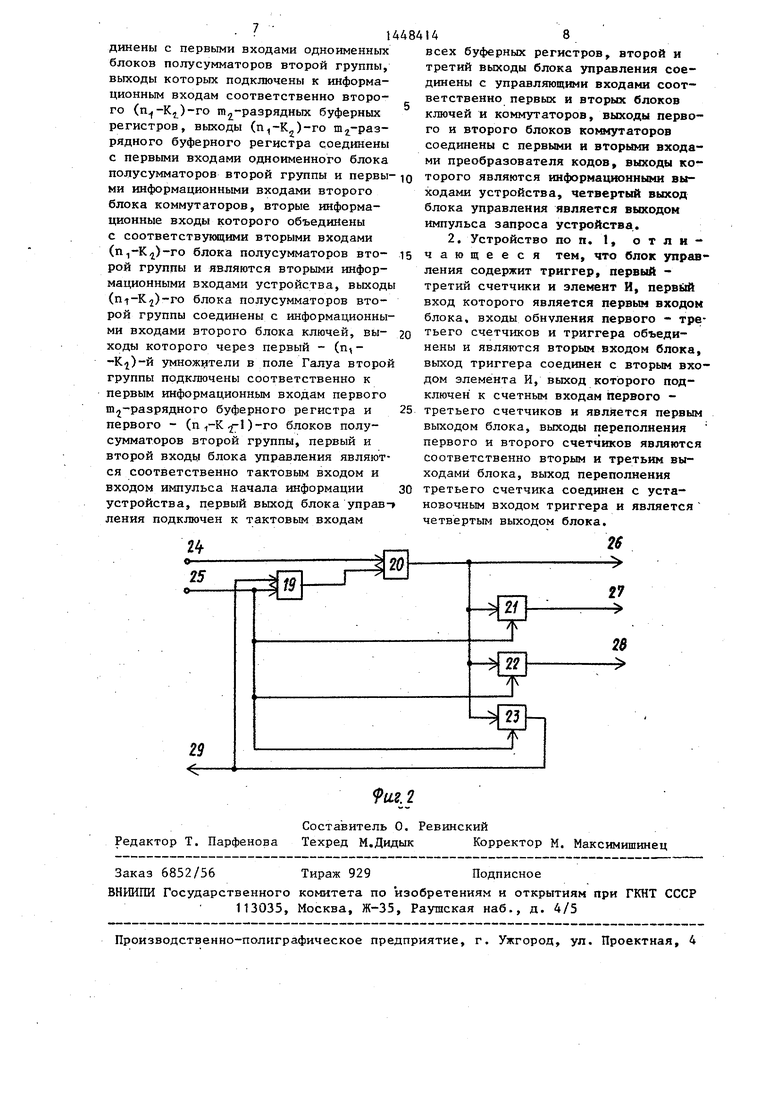

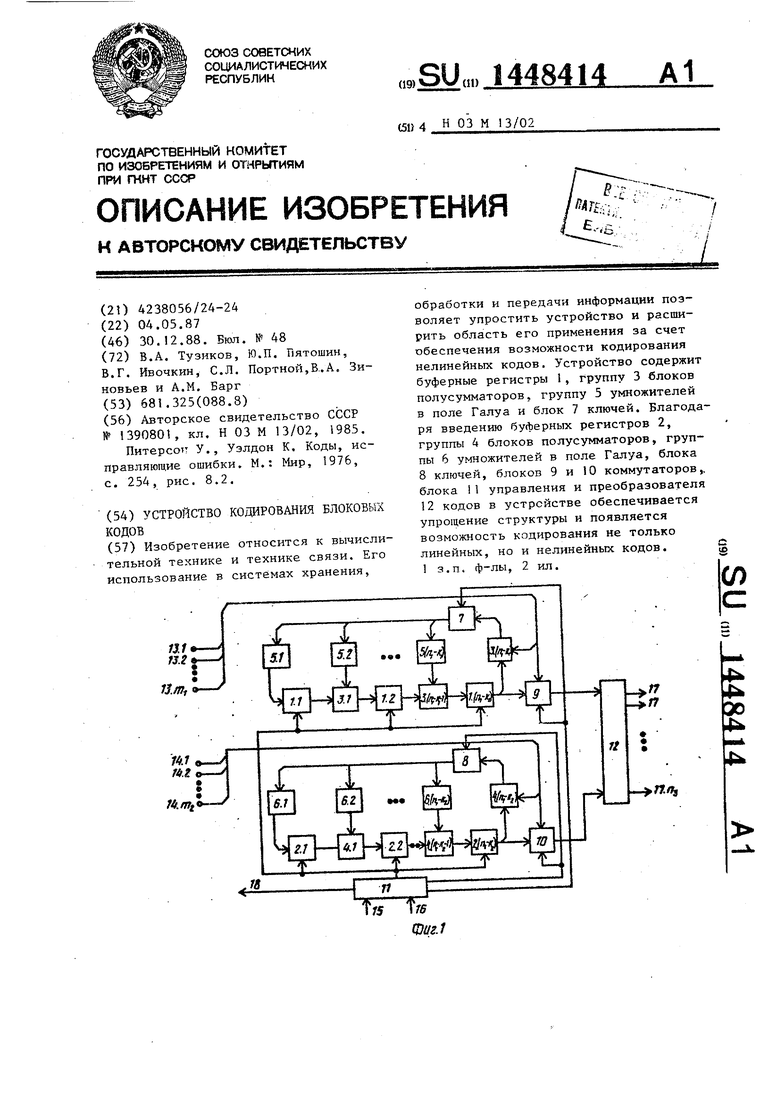

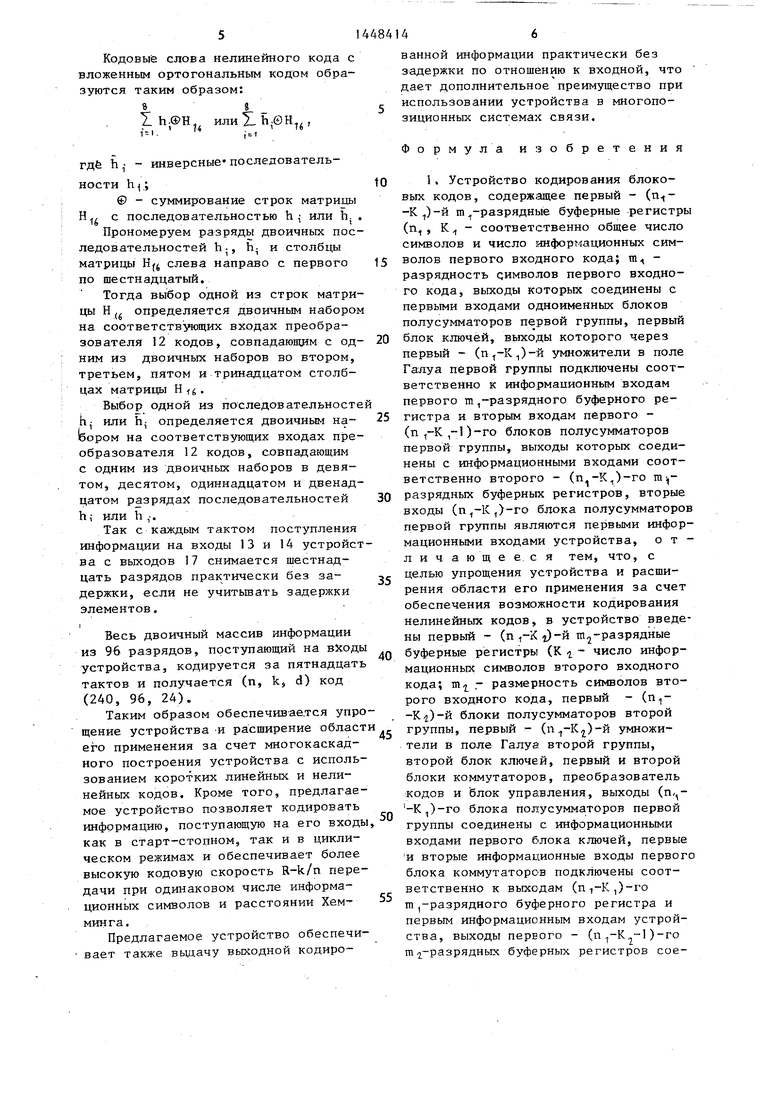

На фиг. 1 изображена блок-схема предлагаемого устройства кодирования блоковых кодов; нафиг, 2 - функциональная схема блока управления.

Устройство кодирования блоковых кодов (фиг. 1) содержит первый - ()-ый га (-разрядные буферные регистры 1 (т 1-разрядность символов первого входного (п. К,, d)-кoдa), первый - ()-ый т -разрядные буферные регистры 2 (т -разрядность символов второго входного (п, К, d2)-кoдa), первую и вторую группы 3 и 4 блоков полусумматоров, первую и вторую группы 5 и 6 умножителей в поле Галуа, первый и второй блоки 7 и 5 ключей, первый и второй блоки 9 и Ю коммутаторов, блок li управления и преобразователь 12 кодов. На фиг. обозначены первые и вторые информационные входы 13 и 14, тактовый вход 15, вход 16 импульса начала информации, информационные выходы 17, выход 18 импульса запроса.

Блоки полусумматоров групп 3 и.4 содержат каждый соответственно т, и ю полусумматоров.

Умножитель в поле Галуа групп 5 и 6 представляют собой преобразователи кодов на основе ПЗУ с жестким программированием, на выходе которых формируются коды, равные произведению входного входа на соответствующий элемент поля GF(2 ) - для группы 5 или поля СЕСЗ) - для группы 6. Блок 11 управления (фиг. 2) содержит триггер 19, элемент И 20, первый - третий счетчики 21-23. На фиг. 2 обозначены первый и второй входы 24 и 25 и первый - четвертый выходы 26- 29, Преобразователь 12 кодов может быть реализован на ПЗУ с жестким программированием. Счетчики 21-23

имеют коэффициенты пересчета соответственно К, К и п,, причем после переполнения счетчика счет в нем останавливается.

Работу устройства кодирования блоковых кодов рассмотрим на примере конструкции, состоящей из блоков, кодирующих информацию следующими кодами: код Рида-Соломона PC, (15, 11, 5) над полем Галуа GF(2), т.е. п 15, , d ,5, (первый входной код); Код Рида-Соломона РС2(15, 13, 3) над полем Галуа GF(2), т.е. п, 15, , d,3, (второй входной код); нелинейный код Норд- строма-Робинсона Н-Р (16, 8, 6), т.е , ,, (выходной код); ортогональный код, вложенный в код Н-Р (16, 4, 8), т.е. п,16, , (выходной код).

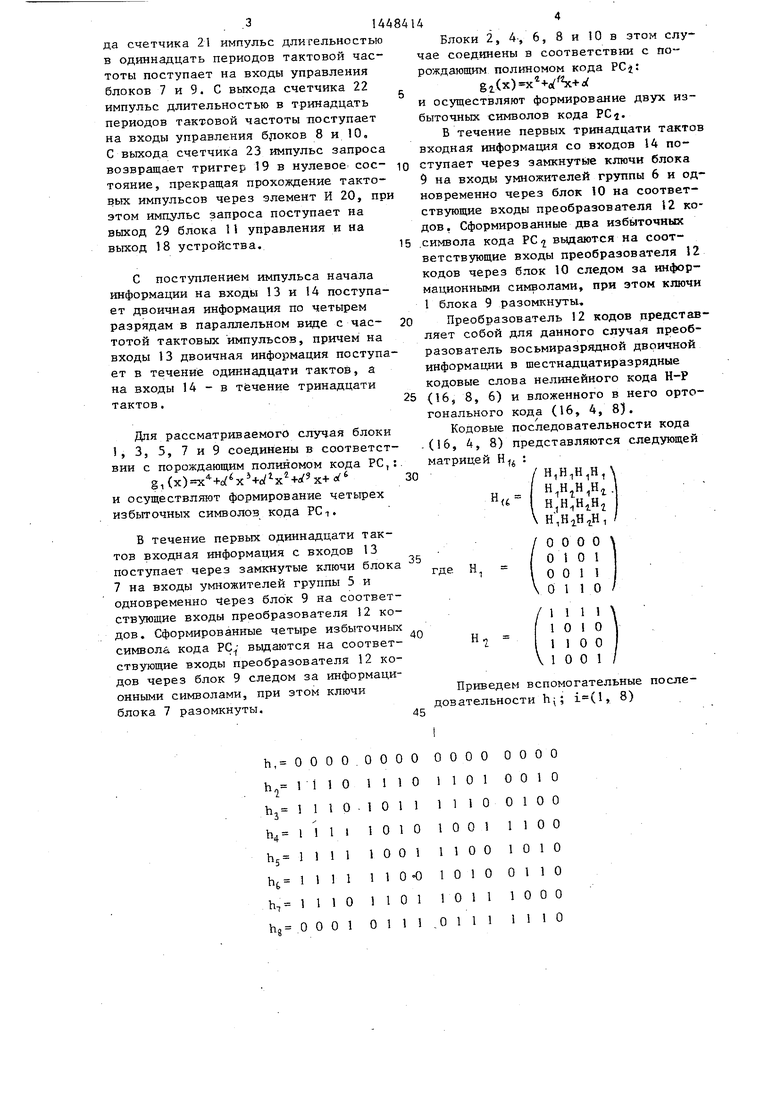

Представление поля Галуа GF(2 ) в виде двоичньж динейных комбинаций по нормальному базису d ,o(tf,cl. выглядит следующим образом:

0 5 0 5

0

.с/

0 0

о1

п

d d с(

1111

1000 0500

1101 00 1 о

о 1 о о

сз о о 1 1 о/ о о о

d 1 О

1 1 1

1

о( О 1 О 1 О 1 1

1

1

,11

о 1 о о

)

0000

i 00

5

0

5

Устройство кодирования блоков кодов работает следующим образом.

Поступающий на вход 16 устройства импульс начала информации подается на второй вход 19 блока 11 управления, где обнуляет счетчики 21-23 и перебрасьшает триггер 19 в состояние логической единищ. Сигнал логической единицы с выхода триггера 19 поступает на вход элемента И 20 и дает раз- рещение прохождению тактовых импульсов, поступающих с входа 15 устройства на первый вход 18 блока 11 управления.

С выхода элемента И 20 пятнадцать тактовых импульсов поступают на входы обнуления счетчиков 21-23. С выхо. 3J4

да счетчика 21 импульс длич ельностыо в одиннадцать периодов тактовой частоты поступает на входы управления блоков 7 и 9. С выхода счетчика 22 импульс длительностью в тринадцать периодов тактовой частоты поступает на входы управления блоков 8 и 10, С выхода счетчика 23 импульс запроса возвращает триггер 19 в нулевое сое- тояние, прекращая прохождение тактовых импульсов через элемент И 20, пр этом импульс запроса поступает на выход 29 блока 1I управления и на выход 18 устройства.

С поступлением импульса начала информации на входы 13 и 14 поступает двоичная информация по четырем разрядам в параллельном виде с час- тотой тактовых импульсов, причем на входы 13 двоичная информация поступает в течение одиннадцати тактов, а на входы 14 - в течение тринадцати тактов,

Для рассматриваемого случая блоки 1, 3, 5, 7 и 9 соединены в соответствии с порождающим полиномом кода PC,

gi{x)x +of x +c/44 x+ и осуществляют формирование четырех избыточных символов кода PC-,.

В течение первых одиннадцати тактов входная информация с входов 13 поступает через замкнутые ключи блока 7 на входы умножителей группы 5 и одновременно ерез блок 9 на соответствующие входы преобразователя 12 кодов. Сформированные четыре избыточных символа кода вьщаются на соответствующие входы преобразователя 12 кодов через блок 9 следом за информационными символами, при этом ключи блока 7 разомкнуты.

14-

Блоки 2, 4-, 6, 8 и 10 в этом случае соединены в соответствии с порождающим полиномом кода PC4:

gi(x)(

и осуществляют формирование двух избыточных символов кода PCj.

В течение первых тринадцати тактов входная информация со входов 14 поступает через замкнутые ключи блока 9 на входы умножителей группы 6 и одновременно через блок 10 на соответствующие входы преобразователя 12 кодов. Сформированные два избыточных .символа кода PC - выдаются на соответствующие входы преобразователя 12 кодов через блок 10 следом за информационными символами, при этом ключи 1 блока 9 разомкнуты.

Преобразователь 12 кодов представляет собой для данного случая преобразователь восьмиразрядной двоичной информации в шестнадцатиразрядные кодовые слова нелинейного кода Н-Р (16, 8, 6) и вложенного в него ортогонального кода (16, 4, 8).

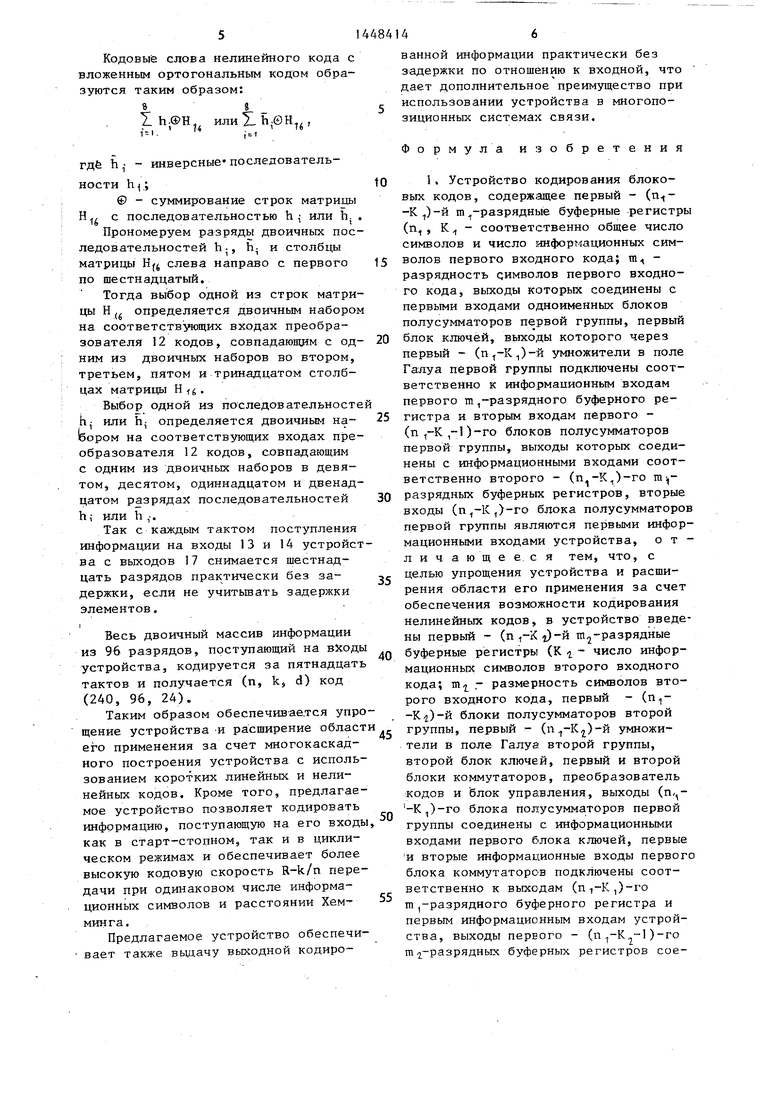

Кодовые последовательности кода .(16, 4, 8) представляются следующей матрицей Н, :

Н,Н,Н,Н,

HU

5

где Н.

,j -1

Н

Н, Н Н -jH 1

0000 01 о 1 0011 0110

1111

1010 1100 1001

Приведем вспомогательные последовательности i(l, 8)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Устройство контроля качества дискретного канала связи | 1988 |

|

SU1599997A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для кодирования | 1986 |

|

SU1390801A1 |

| Манипулятор частоты без разрыва фазы | 1987 |

|

SU1515384A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| СПОСОБ ТРАНСЛЯЦИОННОГО УСЛОЖНЕНИЯ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ В ВИДЕ КОДОВ КВАДРАТИЧНЫХ ВЫЧЕТОВ, СУЩЕСТВУЮЩИХ В ПРОСТЫХ ПОЛЯХ ГАЛУА GF(p), И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2017 |

|

RU2669506C1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах хранения. обработки и передачи информации позволяет упростить устройство и расширить область его применения за счет тэбеспечения возможности кодирования нелинейных кодов. Устройство содержит буферные регистры 1, группу 3 блоков полусумматоров. группу 5 умножителей в поле Галуа и блок 7 ключей. Благодаря введению буферных регистров 2, группы 4 блоков полусумматоров, группы 6 умножителей в поле Галуа, блока 8 ключей, блоков 9 и 10 коммутаторов блока 1 управления и преобразователя 12 кодов в устройстве обеспечивается упрощение структуры и появляется возможность кодирования не только линейных, но и нелинейных кодов. 1 з.п. ф-лы, 2 ил. о U (Л

0000.000000000000

1 1 1 О 111011010010

1 1 1 I 101010011100

1 1 1 1 100111001010

llll 110Ю1010Olio

1 1 1 0 1101roil1000

0 0 0 1 0111,01111110

Кодовые слова нелинейного кода с вложенным ортогональным кодом образуются таким образом:

«

Z h.®H. илиЦЬ-еН,. , 1--1. |.,

где h ,- - инверсные последовательности

© - суммирование строк матрицы Н с последовательностью h или Ь.

Прономеруем разряды двоичных последовательностей h., h. и столбцы матрицы H(j слева направо с первого по шестнадцатый.

Тогда выбор одной из строк матрицы Н ( определяется двоичным набором на соответствующих входах преобразователя 12 кодов, совпадающим с од- ним из двоичных наборов во втором, третьем, пятом и тринадцатом столбцах матрицы Е 1,

Выбор одной из последовательносте h,- или h определяется двоичным на- оором на соответствующих входах преобразователя 12 кодов, совпадающим с одним из двоичных наборов в девятом, десятом, одиннадцатом и двенадцатом разрядах последовательностей hi или h ,-.

Так с каждым тактом поступления информации на входы 13 и 14 устройства с выходов 17 снимается шестнадцать разрядов практически без задержки, если не учитьюать задержки элементов,

Весь двоичный массив информации из 96 разрядов, поступающий на входы устройства, кодируется за пятнадцать тактов и получается (п, k, d) код (240, 96, 24).

Таким образом обеспечивается упрощение устройства и расширение област его применения за счет многокаскадного построения устройства с использованием коротких линейных и нелинейных кодов. Кроме того, предлагаемое устройство позволяет кодировать информацию, поступающую на его входы как в старт-стопном, так и в циклическом режимах и обеспечивает более высокую кодовую скорость R-k/n передачи при одинаковом числе информационных символов и расстоянии Хем- минга.

Предлагаемое устройство обеспечивает также выдачу выходной кодиро5

to

15

20

25 30

40

45

, 5

484146

ванной информации практически без задержки по отношению к входной, что дает дополнительное преимущество при использовании устройства в многопозиционных системах связи.

Формула изобретения

1

динены с первыми входами одноименных блоков полусумматоров второй группы, выходы которых подключены к информационным входам соответственно второго ()-го т -разрядных буферных регистров, вькоды (п,-К2)-го m -разрядного буферного регистра соединены с первыми входами одноименного блока полусумматоров второй группы и первы ми информационными входами второго блока коммутаторов, вторые информационные входы которого объединены с соответствующими вторыми входами ( блока полусумматоров вто- рой группы и являются вторыми информационными входами устройства, вькоды ()-го блока полусумматоров второй группы соединены с информационными входами второго блока ключей, вы- ходы которого через первый - (п,- -К)-й умножители в поле Галуа второй группы подключены соответственно к первым информационным входам первого го -разрядного буферного регистра и первого - ()-го блоков полусумматоров второй группы, первый и второй входы блока управления являются соответственно тактовым входом и входом импульса начала информации устройства, первый выход блока управления подключен к тактовым входам

148

всех буферных регистров, второй и третий выходы блока управления соединены с управляющими входами соответственно первых и вторых блоков ключей и коммутаторов, выходы первого и второго блоков коммутаторов соединены с первыми и вторыми входами преобразователя кодов, выходы которого являются информационными выходами устройства, четвертый выход блока управления является выходом импульса запроса устройства.

| Устройство для кодирования | 1986 |

|

SU1390801A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Питерсо Т У., Уэлдон К | |||

| Коды, исправляющие ошибки | |||

| М.: Мир, 1976, с | |||

| Гонок для ткацкого станка | 1923 |

|

SU254A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-12-30—Публикация

1987-05-04—Подача