1

Изобретение относится к элек тро- технике, а именно к защите синхронных машино

Цель, изобретения - повышение

быстродействия и упрощение устройства для выявления асинхронного режима синхронных машин.

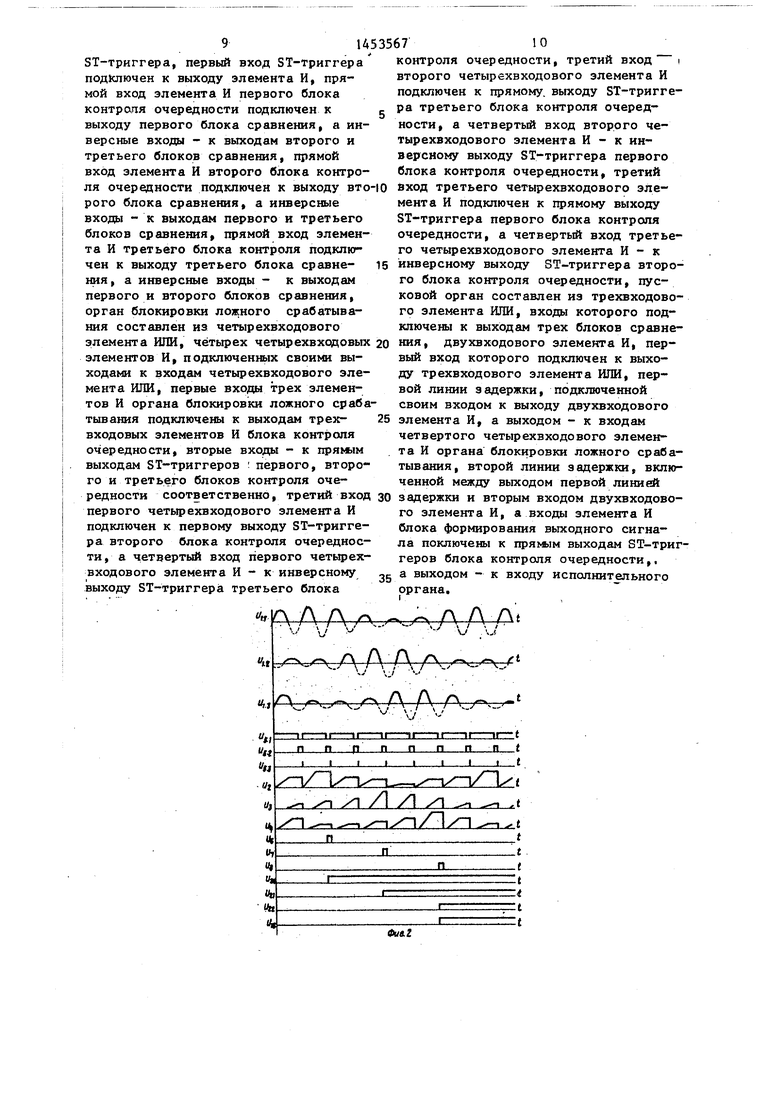

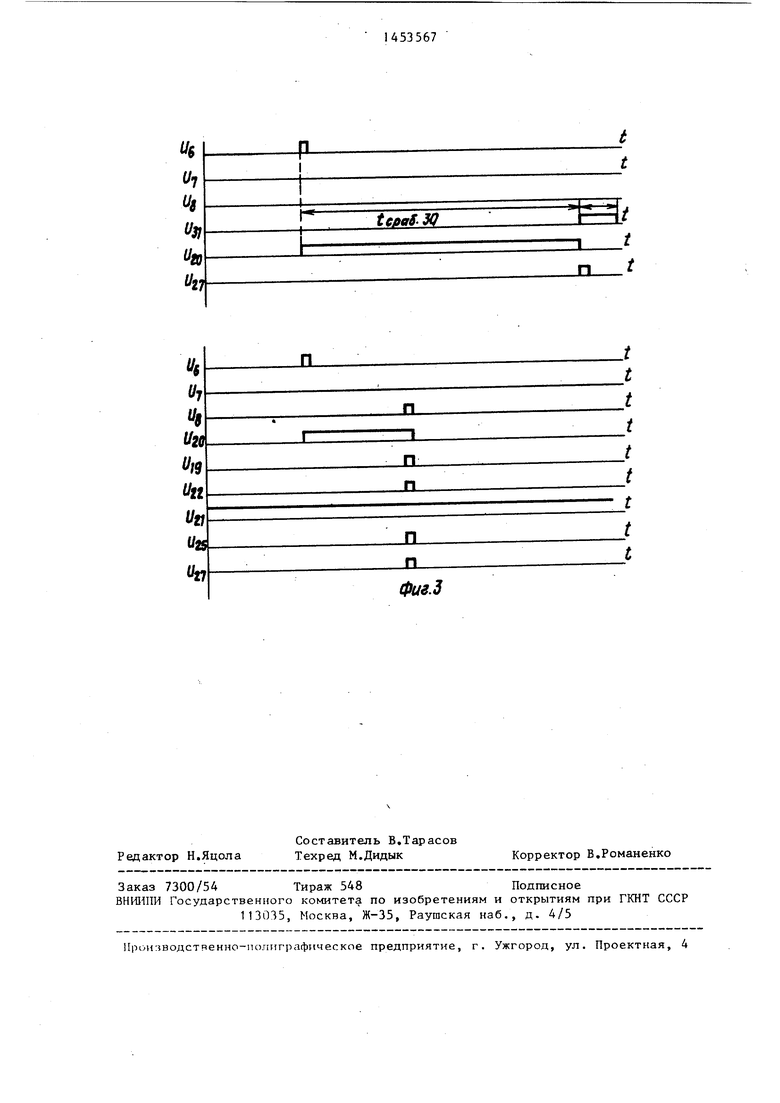

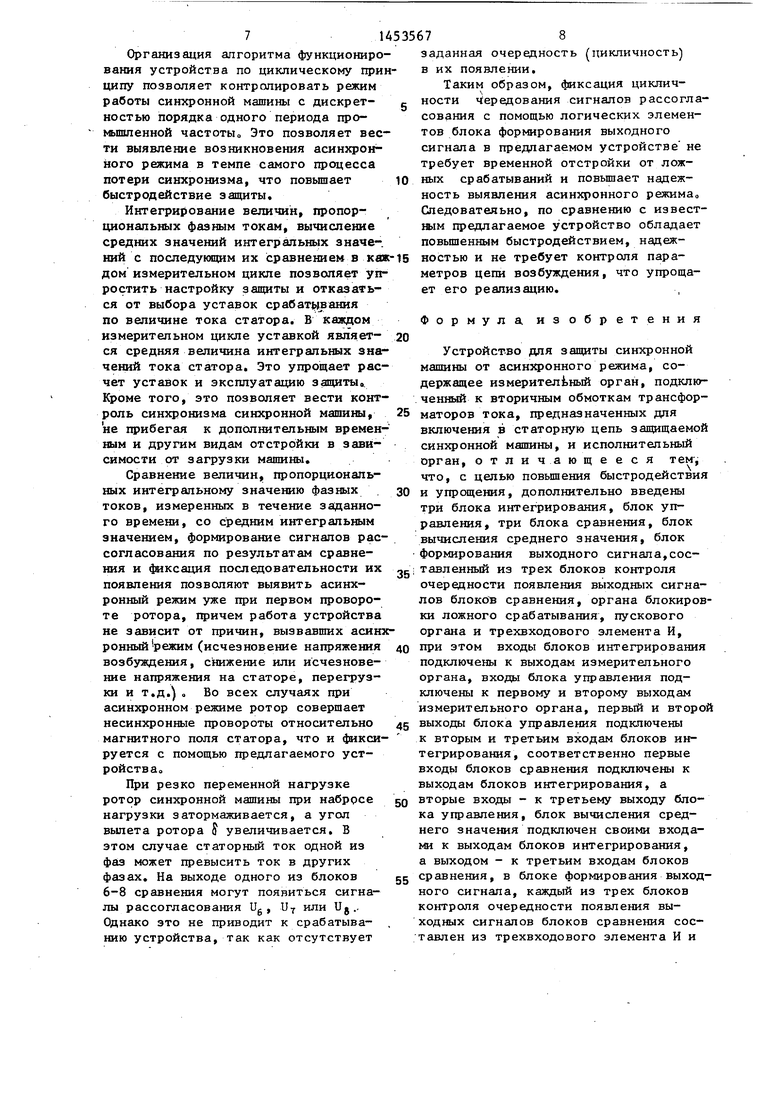

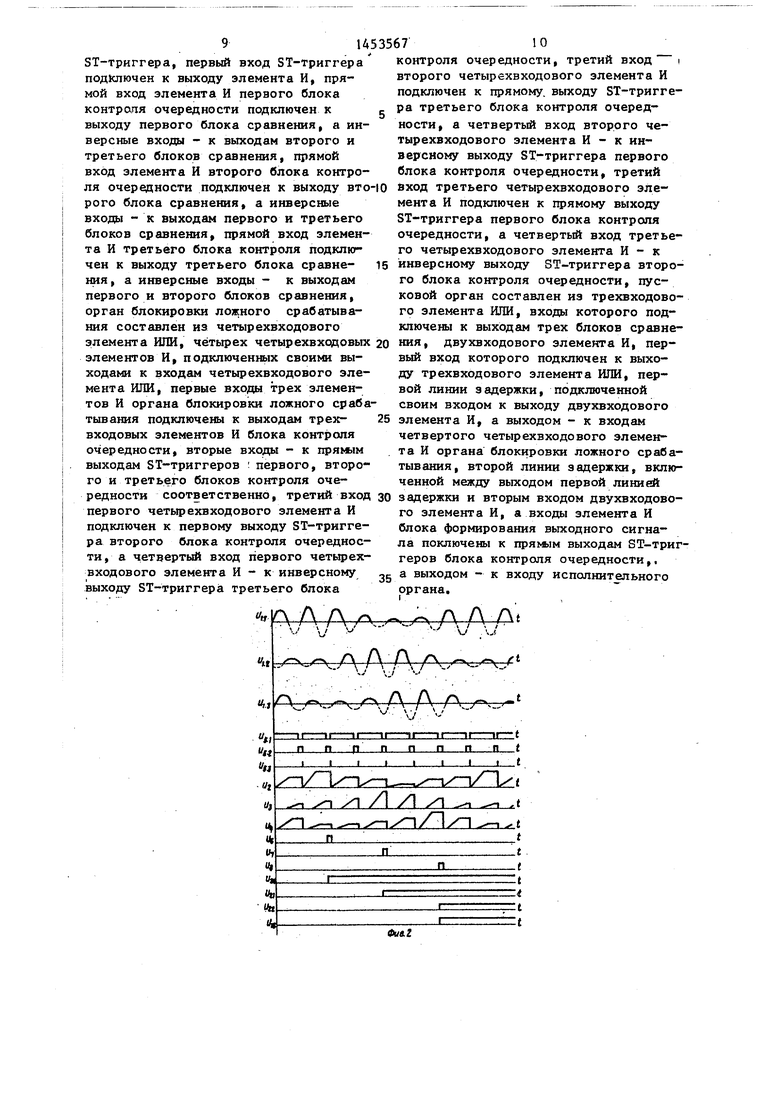

На фиго1 приведена принципиальная схема с выделением функциональных блоков; на фиг.2 и 3 - время-импульсные диаграммы поясняющие работу основных элементов устройства.

Устройство для защиты синхронной машины от асинхронного режима содержит измерительный орган 1, на входы которого подают токи трех фаз статора, три блока 2-4 интегрирования, первые входы которых подключены к перво- му и третьему выходам измерительного органа 1 соответственно, блок 5 управления, входы которого подключены к первому и второму выходам измерительного органа 1. Первьй и второй выходы блока 5 управления подключены к вторым и третьим входам блоков 2-4 интегрирования. Устройство также содержит три блока 6-8 сравнения, первые входы которых соединены с третьим входом блока 5 управления, вторые входы блоков 6-8 сравнения подключены к выходам блоков 2-4 интегрирования соответственно, блок 9 вычиспе- ния среднего значения, входы которого соединены с выходами блоков 2-4 интег рирования, а выходы - с третьими входами блоков 6-8 сравнения соответст

венно, блок 10 формирования выходного сигнала, состоящий из трех блоков 11-13 контроля очередности появления выходных сигналов блоков сравнения, органа 14 блокировки ложного срабатывания, пусковой орган 15 и трех- входовый элемент И 16

Каждый ия блоков 11-13 включает в себя один из трехвходовых элементов И 17-19 и один из ST-триггеров 20-:22, причем первый вход каждого из ST-триггеров 20-22 подключен к выходу одного из элементов И 17-19 соответственно. Прямой вход логического элементам 17 подключен к выходу блока 6 сравнения, а инверсные входы логического элемента И 17 - к выходам блоков 7 и 8 сравнения. Прямой вход логического элемента И 18 подключен к выходу блока 7 сравнения, а инверсные входы логического элемента И 18 - к выходам блоков 6 и 8 сравнения. вход логического элемента И 19 подключен к выходу блока 8 сравнения, а инверсные входы логического элемента И 19 - к выходам блоков 6 и 7 сравнения. Орган 14 блокировки ложного срабатывания состоит из четырех элементов И 23-26, своими .выходами подключенных к входам элемента ИЛИ 27, выход которого подключен к вторым входам ST-триггеров 20-22. Первые входы элементов И 23-25 подключены к выходам элементов И 17-19 соответственно, вторые входы элементов И 23-25 подключены к пряьым выходам ST-триггеров 20-22 соответственно. Третий вход элемента И 23 подключен к прямому выходу ST-триггера 21, а четвертый вход элемента И 23 - к инверсному выходу ST-триггера 22, Третий вход элемента И 24 подключен к прямому выходу 8Т-триггера 22, а четвертый вход элемента И 24 - к инверсному выходу ST-триггера 20 третий вход элемента И 25 подключен к прямому входу ST-триггера 20, а четвертый выход элемента И 25 - к инверсному выходу ST-триггера 21,

тельным значениям другого выходного сигнала измерительного органа 1, нагт- ример . На втором выходе блока 5 управления формируется управляющий сигнал Uj Сброс, который формируется в момент окончания текущего и на- чала поспедукщего измерительного периода, т,е при переходе через нуль от отрицательных к положительным значениям выходного сигнала U,, . На

третьем выходе блока 5 управления формируется управляющий сигнал U Сравнение, который формируется с

у.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматический регулятор для настройки дугогасящих реакторов | 1987 |

|

SU1451798A1 |

| Способ измерения среднего значения напряжения произвольной формы и устройство для его осуществления | 1983 |

|

SU1150561A1 |

| Реверсивный вентильный электродвигатель | 1983 |

|

SU1132329A1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Устройство для одноканального синхронного фазового управления вентильным преобразователем | 1982 |

|

SU1046894A1 |

| Устройство для защиты синхронного электродвигателя от асинхронного режима | 1986 |

|

SU1431002A2 |

| Устройство для контроля статических параметров цифроаналоговых преобразователей | 1986 |

|

SU1352647A1 |

| Устройство для защиты электроустановки от неправильного чередования фаз | 1983 |

|

SU1108548A1 |

| Устройство для синхронного управления многофазным вентильным преобразователем | 1982 |

|

SU1108602A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

Изобретение относится к электротехнике. Целью изобретения является повьшение быстродействия и упрощение. Устройство для защиты синхронной ма- щины от асинхронного режима снабжено блоком 5 управления, подключенным двумя входами к выходам измерительного органа 1, а выходами - к входам Интегрирования и Сброс блоков 2-4 интегрирования. Выходы блоков 2-4 соединены соответственно с первыми входами блоков 6-8 сравнения, вторые входы которых подключены к третьему выходу блока 5. Выход каждого из блоков 2-4 соединен с прямым входом одного из элементов И 17- 19, принадлежащих блокам 11-13 контроля очередности появления сигналов блоков 6-8 сравнения, входящих в О)

Пусковой орган 15 состоит из.трех-is момента перехода через нуль от поповходового логического элемента ИЛИ 28, входа которого подключены к выходам блоков 6-8 сравнения, двухвко- дового логического элемента И 29, первый вход которого подключен к выходу элемента ИЛИ 28, первой линии 30 задержки, вход которой подключен к выходу элемента И 29, а выход - к входу элемента И 26, второй линии

31 задержки, включенной между выходом 25 значений выходных сигналов измерительлинии 30 задержки и вторым входом элемента И 29, входы элемента И 16 подключены к прямым выходам ST-триггеров 20-22f а выход элемента И 16 подключен к входу исполнительного органа 32,

Устройство работает следующим образом.

На вход измерительного органа 1

30

кого органа 1, гфопорциональных фазным токам статора. Интегрирование, происходит в течение части каждого периода проилпленной частоты, равной длительности управляющего импульса

,5л- ления

Одновременно в блоке 9 вычис- среднего значения осуществляется вычисление интегрального среднего полупериодного значения выходных сиг- подают от измерительных трансформато-.. налов блоков 2-4 интегрирования, ПосJb

ров тока токи трех фаз статора, Вле окончания управляющего сигнала

измерительном органе 1 осуществляет- y выходные сигналы блоков 2-4 инея разделение цепей трансформаторов тока и данного устройства и преобразование входных сигналов к виду, удобно- о щего сигнала Uy j Сравнение в блоках му для дальнейшей обработки в соот-6-8 сравнения производится сравнение

ветствии с элементной базой, реализуг нщей устройство. На первом выходе измерительного органа 1 формируется сигнал и, (г,2}, пропорциональный токухд, на втором выходе - сигнал и , пропорциональный току ij, а на третьем выходе - сигнал Uij, пропорциональный проинвертированному току i.

В блоке 5 управления формируются gQ управляющие сигналы. На первом выходе блока 5 управления формируется управляющий сигнал и5, Интегрирование, который формируется с момента перехода через нуль отрицательных к положительным значениям одного из выходных сигнгшов измерительного органа 1, например V( , до момента перехода через нуль от положительных к отрица45

55

тегрирования U, U, U и блока 9 не изменяются, С приходом управляюсигналов и, и и и. с выходным сигналом блока 9 равным среднему значению этих сигналов. На выходах блоков сравнения формируются сигналы рассогласования положительной полярности (соответствующие уровню логической единицы), если величина сигнала, пос тупакщего на второй вход от блока сравнения, больше среднего значения, поступающего от блока 9 на третий вход, В противном случае, а также при равенстве поступающих сигналов на второй и третий входы блока 9 сигнал на выходе блока сргшнения отсутствует (соответствует уровню логического нуля), По окончании текущего и в начале поспедукщего измерительного периодов производится обнуление бло

жительных к отрицательным значениям сигнала U, до момента перехода через нуль от отрицательных к положительным значениям сигнала U,.

С приходом управляющего сигнала g Интегрирование в блоках 2-4 интегрирования происходит ийтегриро- вание положительных полупериодных

кого органа 1, гфопорциональных фазным токам статора. Интегрирование, происходит в течение части каждого периода проилпленной частоты, равной длительности управляющего импульса

,5л- ления

ся выч полупе налов

y выходные сигналы блоков 2-4 инщего сигнала Uy j Сравнение в блоках 6-8 сравнения производится сравнение

тегрирования U, U, U и блока 9 не изменяются, С приходом управляю

сигналов и, и и и. с выходным сигналом блока 9 равным среднему значению этих сигналов. На выходах блоков сравнения формируются сигналы рассогласования положительной полярности (соответствующие уровню логической единицы), если величина сигнала, пос тупакщего на второй вход от блока сравнения, больше среднего значения, поступающего от блока 9 на третий вход, В противном случае, а также при равенстве поступающих сигналов на второй и третий входы блока 9 сигнал на выходе блока сргшнения отсутствует (соответствует уровню логического нуля), По окончании текущего и в начале поспедукщего измерительного периодов производится обнуление блоков 2-4 интегрирования и блока 9 импульсом Uj Сброс,

При синхронной работе защищаемой синхронной машины ее статорные токи равны между собой, следовательно равны между собой сигналы U, Uj, U и и., а выходные сигналы на выходах

ра 20. В результате на прямом выходе. ST-триггера 20 устанавливается единичный сигнал и

го

Аналогично появление

блоков сравнения соответствуют уровню логического нуля. В результате этого выходной сигнал блока 10 также равен нулю, и исполнительный ор- гаи 32 не срабатьшаетд

импульсов Uf и Ug приводит к изменению состояния ST-триггеров 21 и 22, появлению сигналов U и Ц, Появление единичных сигналов U, U, U

10

на всех трех входах элемента И 16 приводит к его срабатыванию и запуску исполнительного органа 32,

При кратковременных возмущениях, вызывакицих появление одиночных импульсов и, и или Ug, либо при При выпадении иэ синхронизма синхг 15 нарушении принятой очередности их

ронной малишл ее ротор начинает гфо- ворачиваться относительно магнитного поля статора Для примера рассмотрим асинхронный режим со снижением частоты вращения ротора (фиго2а). Пусть в момент потери синхронизма ;поперечная ось ротора совпадает с осью фазы А статора, В этом случае значение выходного сигнала на выходе блока 2 интегрирования U, пропорциональное величине тока фазы А, больше по величине, чем выходные сигналы блоков 3 и 4 интегрирования Uj и и, пропорциональные величинам токов в фазах В и С, так как оси их обмоток сдвинуты по отношению к фазе А на угол +:120°, На выходе блока 6 сравнения появляется сигнагЕ, соответствукнций уровню логической единищ 1, а на выходах блоков 7 и 8 сравнения выходные сигналы равны нулю. После поворота ротора на бО против часовой стрелки относительно магнитного поля статора максимальное значение фазного тока будет в фазе В, а при повороте еще на 60 - в

появления ложной работы устройства не . На фиг,26 показан случай, когда появляется сигнал только на вы- ходе блока 6 сравнения, В результате

20 на выходе пускового органа 15 спустя заданное время, определяемое лииией 30 задержки, появляется выходной сигнал элемента И, которьй, поступая на вход элемента И 26 блока 4,

25 вызывает его срабатывание. Выходной импульс органа 14 U , поступая на второй вход (вход установки нулевого состояния) ST-триггера 20 (а также и ST-триггера 21 и 22), приводит к

30 его возврату в исходное состояние, Щ)и этом на прямых выходах ST-триггеров 20-22 устанавливается нулевой, а на инверсных - единичный выходной сигнал, В результате этого элемент И 16 и исполнительный орган 32 не срабатываю,;

На фиго2в показан случай блокировки ложного срабатывания устройства при нарушении очередности появле40 ния сигналов рассогласования Ug, U и Uj, например, при кратковременном увеличении частоты вращения защищаемого синхронного двигаФепя, В этом случае вслед за импульсом U появ35

40 ния сигналов рассогласования Ug, U и Uj, например, при кратковременном увеличении частоты вращения защищаемого синхронного двигаФепя, В этом случае вслед за импульсом U появфазе С, В соответствии с этим формируются выходные сигналы блоков сравнения: в первом случае сигнал, соот- ветствугаций уровню логической едини- 5 ляется импульс Ug , а затем U , цы, появляется на выходе блока 7 срав- При этом после появления импульса Ug нения, а во втором - на выходе блока 8единичные сигналы будут на всех вхосравнения. Таким образом, наблкщает- ся определенная последовательность появления выходных снгналов блока сравнеиия, соответствующая изменению углового положения ротора относительно магнитного поля статора.

При появлении мпульса Uj (фиг„3) на прямом входе элемента И 17 и от50

дах элемента И 25. На первом его входе - сигнал U , на втором - сигнал Ujif на третьем - сигнал так как 8Т-триггер 20 уже сработал после появления импульсов Ug и U,, на четвертом - сигнал U, , так как

ST-триггёр 21 находится в исходном ее состоянии, и на его инверсном высутствии импульсов и и Ujj на его инверсшлх входах на выходе элемег та , И 17 появляется единичный сигнал, поступающий на первый вход ST-триггера 20. В результате на прямом выходе. ST-триггера 20 устанавливается единичный сигнал и

го

Аналогично появление

импульсов Uf и Ug приводит к изменению состояния ST-триггеров 21 и 22, появлению сигналов U и Ц, Появление единичных сигналов U, U, U

на всех трех входах элемента И 16 приводит к его срабатыванию и запуску исполнительного органа 32,

появления ложной работы устройства не . На фиг,26 показан случай, когда появляется сигнал только на вы- , ходе блока 6 сравнения, В результате

на выходе пускового органа 15 спустя заданное время, определяемое лииией 30 задержки, появляется выходной сигнал элемента И, которьй, поступая на вход элемента И 26 блока 4,

вызывает его срабатывание. Выходной импульс органа 14 U , поступая на второй вход (вход установки нулевого состояния) ST-триггера 20 (а также и ST-триггера 21 и 22), приводит к

его возврату в исходное состояние, Щ)и этом на прямых выходах ST-триггеров 20-22 устанавливается нулевой, а на инверсных - единичный выходной сигнал, В результате этого элемент И 16 и исполнительный орган 32 не срабатываю,;

На фиго2в показан случай блокировки ложного срабатывания устройства при нарушении очередности появления сигналов рассогласования Ug, U и Uj, например, при кратковременном увеличении частоты вращения защищаемого синхронного двигаФепя, В этом случае вслед за импульсом U появ

ляется импульс Ug , а затем U , При этом после появления импульса Ug единичные сигналы будут на всех вхо

дах элемента И 25. На первом его входе - сигнал U , на втором - сигнал Ujif на третьем - сигнал так как 8Т-триггер 20 уже сработал после появления импульсов Ug и U,, на четвертом - сигнал U, , так как

ST-триггёр 21 находится в исходном состоянии, и на его инверсном выходе устанавливается единичный выходной сигнал на органе 14 U , ко- торьй возвращает все ST-триггеры 20- 22 в исходное состояние

Организация алгоритма функционирования устройства по циклическому приципу позволяет контропировать режим работы синхронной машины с дискретностью порядка одного периода про- мьштенной частоты Это позволяет вести выявление возникновения асинхронного режима в темпе самого процесса потери синхронизма, что повьшает быстродействие защиты.

Интегрирование величин, пропорциональных фазным токам, вычисление средних значений интегральных значе-. НИИ с последующим их сравнением в каж дом измерительном цикле позволяет упростить настройку защиты и отказаться от выбора уставок срабатывания по величине тока статора. В каждом измерительном цикле уставкой является средняя величина интегральных знаг чений тока статора. Это упрощает расчет уставок и эксплуатацию защиты Кроме того, это позволяет вести контроль синхронизма синхронной машины, не прибегая к дополнительным временным и другим видам отстройки в зависимости от загрузки машины.

Сравнение величин, пропорциональных интегральному значению фазных токов, измеренных в течение заданного времени, со средним интегральным значением, формирование сигналов рассогласования по результатам сравнения и фиксация последовательности их появления позволяют выявить асинхронный режим уже при первом проворо- те ротора, причем работа устройства не зависит от причин, вызвавших асинхронный режим (исчезновение напряжения возбуждения, снижение или исчезновение напряжения на статоре, перегрузки и т.д.) « Во всех случаях при асинхронном режиме ротор совершает несинхронные провороты относительно магнитного поля статора, что и фиксируется с помощью предлагаемого устройства

При резко переменной нагрузке ротор синхронной машины при набросе нагрузки затормаживается, а угол вьиета ротора S увеличивается. В этом случае статорный ток одной из фаз может превысить ток в других . На выходе одного из блоков 6-8 сравнения могут появиться сигналы рассогласования Ug , U или Uj.. Однако это не приводит к срабатыва- нию устройства, так как отсутствует

0

5

заданная очередность (цикличность) в их появлении.

Таким образом, фиксация цикличности «Чередования сигналов рассогласования с помощью логических элементов блока формирования выходного сигнала в предлагаемом устройстве не требует временной отстройки от ложных срабатываний и повышает надежность выявления асинхронного режима Следовательно, по сравнению с извест- предлагаемое устройство обладает повьш1енным быстродействием, надежностью и не требует контроля параметров цепи возбуждения, что упрощает его реализацию.

Формула изобретения

20

15

5

0

5

0

0

5

Устройство для защиты синхронной машины от асинхронного режима, содержащее H3MepHTentHb орган, подклкг- .ченный к вторичным обмоткам трансфор5 маторов тока, предназначенных для

включения в статорную цепь защищаемой синхронной машины, и исполнительный орг ан, отличающееся т ем, что, с целью повьш1ения быстродействия и упрощения, дополнительно введены три блока интегрирования, блок управления, три блока сравнения, блок вычисления среднего значения, блок формирования выходного сигнала,составленный из трех блоков контроля очередности появления выходных сигналов блоков сравнения, органа блокировки ложного срабатывания, пускового органа и трехвходового элемента И, при этом входы блоков интегрирования подключены к выходам измерительного органа, входы блока управления подключены к первому и второму выходам измерительного органа, первый и второй выходы блока управления подключены к вторым и третьим входам блоков интегрирования, соответственно первые входы блоков сравнения подключены к выходам блоков интегрирования, а вторые входы - к третьему выходу блока управления, блок вычисления среднего значения подключен своими входами к выходам блоков интегрирования, а выходом - к третьим входам блоков

5 сравнения, в блоке формирования выходного сигнала, каждый из трех блоков контроля очередности появления выходных сигналов блоков сравнения составлен из трехвходового элемента И и

ST-триггера, первый вход ST-триггера подключен к выходу элемента И, прямой вход элемента И первого блока контрапя очередности подключен к выходу первого блока сравнения, а инверсные входы - к выходам второго и третьего блоков сравнения, прямой вход элемента И второго блока контроля очередности подключен к выходу вто-Ю вход третьего четырехвходового эле- рого блока сравнения, а инверсныемента И подключен к прямому выходу

к выходам первого и третьего

входы блоков сравнения, прямой вход элемента И третьего блока контроля подюпн - чей к выходу третьего блока сравне- шя, а инверсные входы - к выходам первого и второго блоков сравнения, орган блокировки ложного срабатывания составлен из четырехвходового

ST-триггера первого блока контроля очередности, а четвертый вход третьего четырехвходового элемента И - к 15 инверсному выходу ST-триггера второго блока контроля очередности, пусковой орган составлен из трехвходово- го элемента ИЛИ, входы которого подключены к выходам трех блоков сравне- элемента ИЛИ, четырех четырехвхсдовых 20 «ия, двухвходового элемента И, пер- элементов И, подключенных своими вы-вый вход которого подключен к выхоходами к входам четырехвходового эле- ду трехвходового элемента ИЛИ, пер- мента ИТШ, первые входы трех элемен-вой линии задержки, подключенной

тов И органа блокировки ложного сраба- своим входом к выходу двухвходового тывания подключены к выходам Tpejc- 25 элемента И, а выходом - к входам входовых элементов И блока контроля очередности, вторые входы - к выходам ST-триггеров : первого, второго и третьего блоков контроля очередности соответственно, третий вход зо задержки и вторым входом двухвходово- первого четырехвходового элемента Иго элемента И, а входы элемента И

блока формирования выходного сигнала поключены к выходам ST-триггеров блока контроля очередности,, 3g а выходом - к входу испсшнительного

четвертого четырехвходового элемента И органа блокировки ложного срабатывания, второй линии задержки, включенной между выходом первой линией

подключен к первому выходу ST-трнгге- ра второго блока контроля очередности, а четвертый вход первого четьфех- входового элемента И - к инверсному выходу ST-триггера третьего блока

органа.

контроля очередности, третий вход i второго четырехвходового элемента И подключен к прямому, выходу ST-триггера третьего блока контроля очередности, а четвертый вход второго четырехвходового элемента И - к инверсному выходу ST-триггера первого блока контроля очередности, третий

своим входом к выходу двухвходового элемента И, а выходом - к входам задержки и вторым входом двухвходово- го элемента И, а входы элемента И

четвертого четырехвходового элемента И органа блокировки ложного срабатывания, второй линии задержки, включенной между выходом первой линией

органа.

| Патент США № 3525913, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| , : Сподарж М.Н | |||

| Режимы работы, релейная защита и автоматика синхронных электродвигателей | |||

| - М.: Энергия, 1977, с | |||

| Способ приготовления кирпичей для футеровки печей, служащих для получения сернистого натрия из серно-натриевой соли | 1921 |

|

SU154A1 |

Авторы

Даты

1989-01-23—Публикация

1987-03-25—Подача