равлеиия, а выходы - с входами выходного индикатора, входы регистратора знака подключены к шестому и седьмому выходам блока управления, а вторые сигнальные входы обоих интеграторов соединены с вьрсодом источника опорного напряжения через третий входной ключ, подключенный управляющим входом к второму выходу

блока управления.

I

3. Устройство по п.2, отличающееся тем, что блок управления Состоит из трех триггеров двух элементов И, двух элементов ИЛИ-НЕ, инвертора, трех дифференциальных звеньев, пяти разделительных диодов и резистора смещения, причем первый вход и выход первого триггера соединены соответственно с первым и вторым входами второго триггера, одни входы первого и второго элементов И пoдкJBoчeны к инверсному выходу второго триггера, а друГ-ие входы - соответственно к входу и выходу инвертора, вход первого дифференцирующего звена соединен с инверсным вькодом второго триггера, а выход через первый разделитель ный диод - с первым входом третьего триггера, вход второго дифференцирующего звена ггодключен к входу инвертора, а выход через второй разделительный диод - к второму входу третьего триггера и через третий разделительный диод - к первому входу первого элемента ИЛИ-НЕ, вход третьего дифференцирующего звена соединен с выходом инвертора, а выход через четвертый разделительный диод - с вторым входом третьего триггера и через пятый разделительный диод - с первым входом второго элемента ИЛИ-НЕ, второй вход g выход первого элемента ИЛИ-НЕ подключены соответственно к выходу и второму входу второго элемента ИЛИ-НЕ, резистор смещения включен между вторым входом третьего триггера и шиной нулевого потенциала, в качестве первого, второго и третьего входов блока управления использованы соответственно первый, второй входы первого триггера и вход инвертора, а в качестве первого, второго, третьего, четвертого, пятого, шестого и седьмого выходов - соответственно выход первого, прямой выход второго триггеров, выходы первого, второго элементов И, третьего триггера, первого и второго элементов ИЖ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ ПРОИЗВОЛЬНОЙ ФОРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2034302C1 |

| Устройство допускового контроля двухканальных усилителей | 1989 |

|

SU1679423A1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| Способ преобразования временного сдвига между двумя сигналами и устройство для его осуществления | 1989 |

|

SU1723560A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347028A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| Устройство для контроля времени выключения тиристоров | 1990 |

|

SU1725316A1 |

| Преобразователь сигналов датчиков переменного тока | 1986 |

|

SU1332531A1 |

1. Способ измерения среднего значения напряжения произвольной формы, основанный на раздельном интегрировании двух величин с нулевыми начальными условиями в течение кр,нечного интервала времени, отличающийся тем, что, с целью повышения точности измерения, упомянутому раздельному интегрированию подвергают сумму и разность опорного и исследуемого напряжений, сравнивают результаты интегрирования, по результату сравнения определяют знак среднего значения исследуемого, напряжения, большую из полученных в результате интегрирования величин уменьшают по.зкспоненциальному закону до меньшей и по интервалу времени, отсчитанному от начала уменьшения большей величины до момента ее сравнения с меньшей, судят о собственно среднем значении исследуемого напряжения. 2. Устройство для измерения среднего значения напряжения произвольной формы, содержащее два интегратора, первые сигнальные входы которых соединены с выходами соответственно первого и второго входных ключей, блок управления, первый выход которого подключен к управляющим йходам обоих интеграторов, а второй выход - к управляющим входам первого и второго входных ключеу, источник опорного напряжения, входную шину, шину синхронизации и шину запуска, соединенные соответственно i с сигнальным входом первого входного ключа, первым и вторым входами блока (Л управления, выходной индикатор, отличающееся тем, что, С с целью повышения точности, в него введены компаратор, инвертор,.третий входной ключ, два коммутирукядих ключа, преобразователь время-код и регистратор знака , а интеграторы снабжены вторыми сигнальными входами и СП выполнены с суммированием входных о ел напряжений, причем входы компаратора соединены с выходами интегра05 тор ов, а выход - с третьим входом блока управления, инвертор включен между входной шиной и сигнальным входом второго входного ключа, коммутирующие ключи включены между выходами и перв.ыми сигнальньми входа ми соответствующих интеграторов и подключены управляющими входами соответственно к третьему и четвертому выходам блока управления, информационный и управляющий входы преобразователя время-код соединены с пятым и вторым выходами блока уп

Изобретение относится к электроизмерительной технике и предназначено для использования при контроле средних значений сигналов, например, в установках технической диагностики различных промьшшенных объектов по спектральному составу шумов и вибраций,.

Целью изобретения является повышение точности измерения.

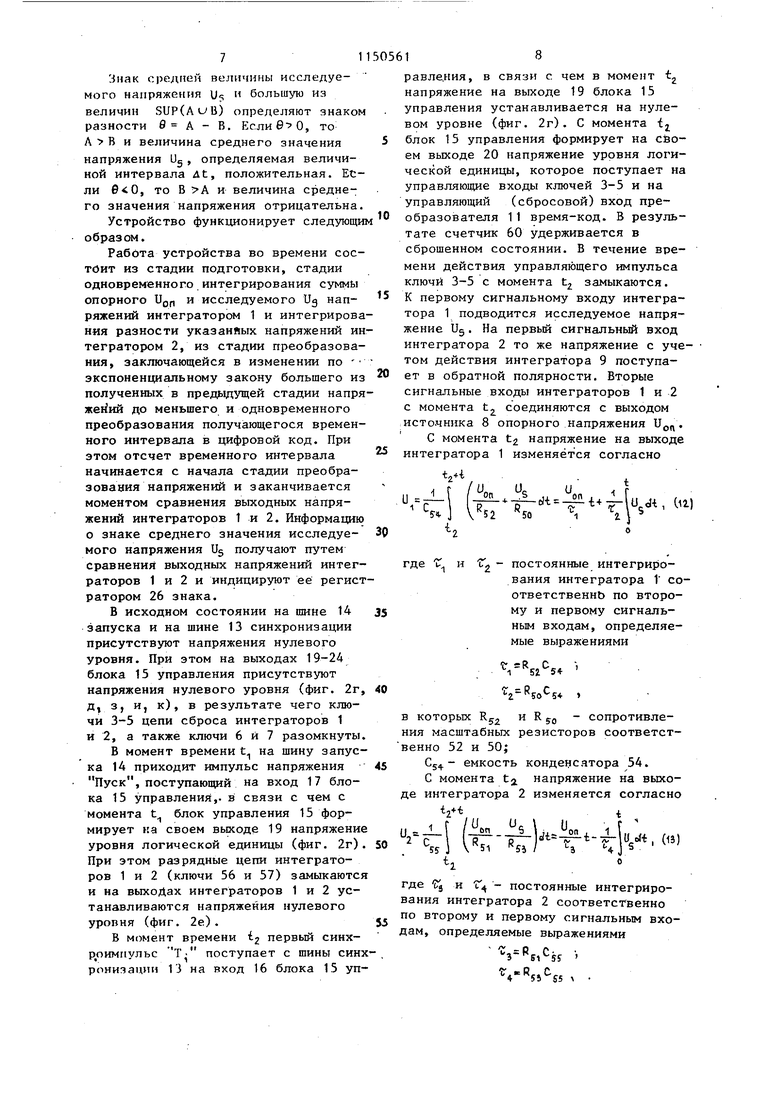

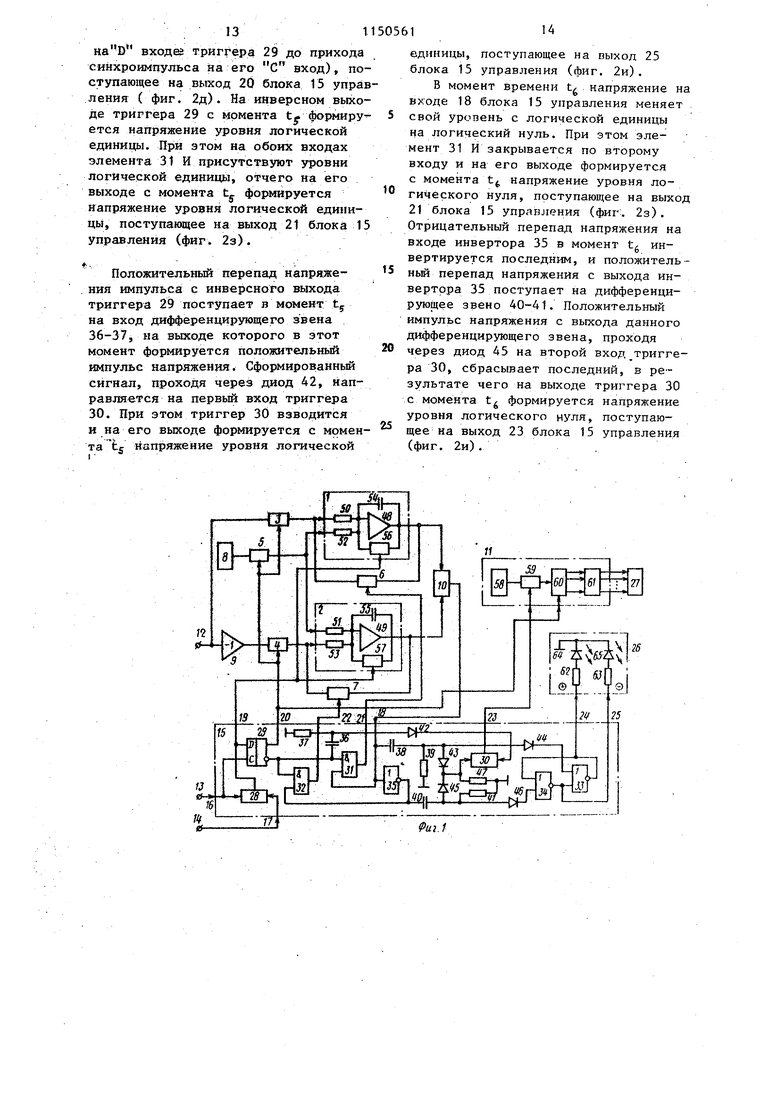

На фиг. 1 представлена функциональная схема устройства, реализующего предложенный способ измерения среднего значения напряжения произвольной формы; на фиг; 2 - временные диаграммы сигналов, отражающие сущность составных операций способа и иллюстрирующие работу данного устройства.

Устройство содержит интеграторы 1 и 2 (фиг. 1), снабженные двумя сигнальными входами каждый и выполненные с суммированием входных напряжений, входные ключи 3-5, коммутирующие ключи 6 и 7, источник 8 опорного напряжения, инвертор 9, компаратор 10, преобразователь 11 времякод, входную шину 12, шину 13 синхронизации, шину 14 запуска, блок 15 управления с входами 16-18 и выходами 19-25, регистратор 26 знака и выходной индикатор 27. Первые сигнальные входы интеграторов 1 и 2 соеди-

нены с выходами соотнетственно входных ключей 3 и 4, а вторые сигнальные входы через входной ключ 5 - с

выходом источника 8 опорного напряжения. Сигнальный вход входного ключа 3 подключен к входной шине 12. Входы компаратора 10 соединены с выходами интеграторов 1 и 2. Инвертор 9 включен между входной шиной 12 и сигиальЕГЫм входом входного ключа 4. Коммутирующие ключи 6 и 7 включены между выходами и первыми сигнальными входами соответственно интеграторов 1 и 2, Выходы преобразователя 11 время-код подключены к входам выходного индикатора 27. Входы 16, 17 и 18 блока 15 управления соединены соответственно с шиной 13 синхронизации, шиной 14 запуска и выходом компаратора 10. Выходы 19-25 подключены соответственно к управляющим входам интеграторов 1 и 2, управляющим входам входных ключей 3-5 и преобразователя 11 время-код, управляющему входу коммутирующего ключа 6, управляющему входу коммутирующего ключа 7, информационному входу преобразователя 11 время-код, первому входу регистратора 26 знака, второму входу последнего.

В одном из вариантов исполнения блок 15 управления состоит из триггеров 28-30, элементов 31 и 32 И, элементов 33 и 34 ИЖ-НЕ, инвертора 35, дифференцирующих звеньев, выполненных на ко.нденсаторе 36 и резисторе 37, на конденсаторе 38 и резисторе 39, на конденсаторе 40 и резисторе 41, разделительных диодов 42-46 и резисторл 47 смещения. Первьй вход и выход тригегра 28 соединены соответственно с первым и вторы входами-триггера 29. Одни входы элементов 31 и 32 И подключены к инверсному выходу триггера 29 а другие -входы - соответственно к входу и выходу инвертора 35. Вход дифференцирующего звена 36-37 соединен с инверсным выходом триггера 29, а выход через разделительный диод 42 - с пер вымвходом триггера 30, Вход дифференцирующего звена 38-39 подключен к входу инвертора 35, а выход через разделительный диод 43 - к второму входу триггера 30 и через разделительньй диод 44 - к первому входу элемента 33 ИПИ-НЕ. Вход дифференцирующего звена 40-41 соединен с выходом инвертора 35, а вьтход через разделительньй диод 45 - с вторым входом триггера 30 и через разделительньй диод 46 - с первым входом элемента 34 ИЛИ-НЕ. Второй вход и

выход элемента 33 ИПИ-НЕ подключены соответственно к выходу и второму входу элемента 34 ИЛИ-НЕ. Резистор 47 смещения включен между вторым входом триггера 30 и шиной нулевого потенциала. В качестве входов 16, 17 и 18 блока 15 управления использованы соответственно первьй, второ входы триггера 28 и вход инвертора 35, а в качестве выходов 19-25 соответственно выход триггера 28, прямой выход триггера 29, выходы элментов 31 и 32 И триггера 30, элементов 33 и 34 ИЛИ-НЕ.

В одном из возможных вариантов исполнения интегратор 1(2) состоит из операционного усилителя 48(49) с резисторами 50(51) и 52(53) на сигнальных входах и с целью обратной связи, включающей в себя параллельно соединенные конденсатор 54(55) и разрядньй ключ 56(57).

В, одном из вариантов исполнения преобразователь 11 время-код состоит из последовательно соединенных генератора 58 импульсов, ключа 59, счетчика 60 импульсов и дешифратора 61, причем управляюпще входы ключа 59 и счетчика 60 являются соответственно информационным и управляющим входами преобразователя 11, а выходы дешифратора 61 его выходами. Регистратор 26 знака состоит из двух цепей, включающих в себя последовательно соединенные резистор 62(63) и светодиод 64(65). Последние связаны с щиной нулевого потенциала.

Сущность предложенного спосбба заключается в следующем.

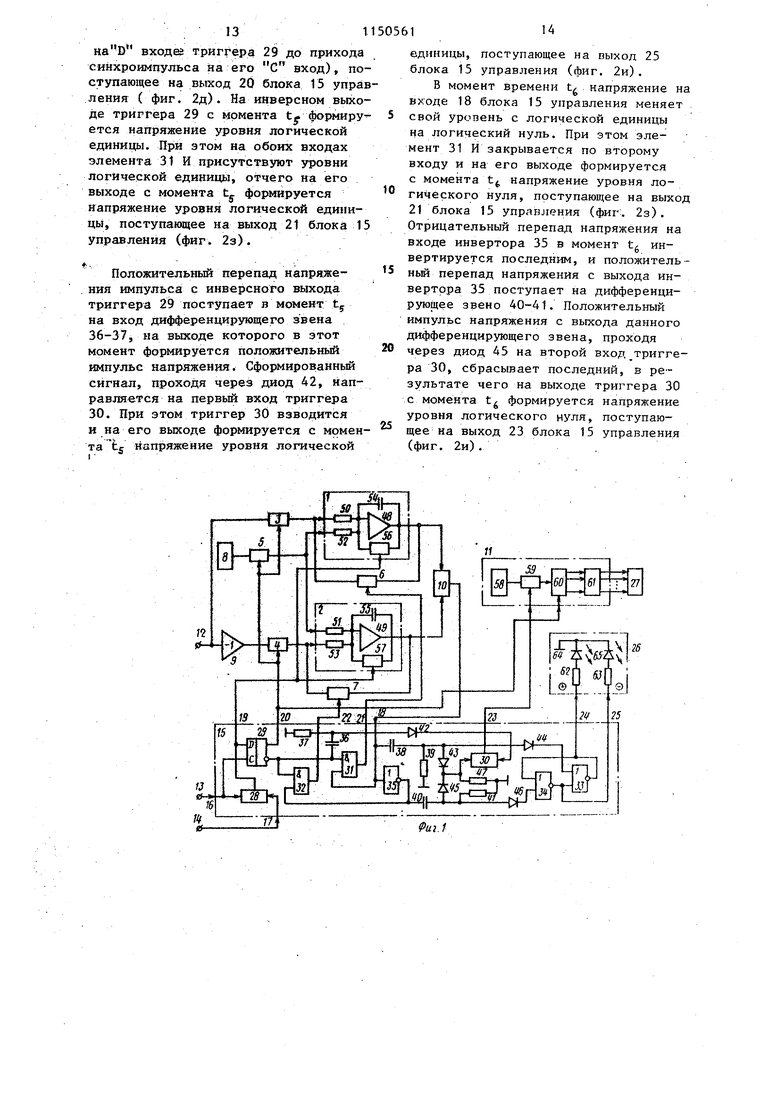

Пусть исследуемый сигнал Ugимеет форму, изображенную на фиг. 2а.

В течение интервала времени Т усреднения интегрируют с нулевыми начальными условиями раздельно сумму опорного 110 и исследуемого Ug

напряжений и их разность (фиг. 2а): Т

I

)..

О.

т , Сэ)

где lo - коэффициент пропорциональности, определяемый видом и параметрами устройств, выполняющих операцию интегрирования. При этом А и В могут быть величины различной физической природы (напряжение, ток, угол поворота, интервал времени) в зависимости от технического средства, реализующего операцию интегрирования. После завершения операции интегрирования результаты интегрирования А и В сравнивают и затем большую из полученных в результате интегрирования величин SUP(Au В) уменьшают по экспоненциальному закону

:-tb

(AuB)e

CM

(где t и f - соответственно момент начала и постоянная времени экспоненциального изменения) до меньшей inf(AoB) в течение времени, опре-г деляемом из выражения

t-tu

SUP()e in(AU6)

(S Отсчитывают интервал времени 4t от начала момента времени t уменьшения большей величины SUP(AUB) до момента ее.сравнения е меньшей inf(AUB): (-. 1 И преобразуют его в цифровой код, являющийся выходной величиной, соответствующей с до.статочно высокой точностью среднему значению входного сигнала Ug за время Т усреднения Величина U выбирается так, что бы отношение бьшо достаточно мальм с тем, чтобы погрешность определения среднего зн чения сигнала не превьш1ала наперед заданной допустимой величины | JI . Так, для получения |jrUO,07% на должна быть в пределах 0,1

Величина минимальной допустимой погрешности определяется путем разложения выражения (6) для л t в ряд

10 ,г

При

членами высших

onTi

степеней данного ряда можно пренебречь. В результате выражение (8) приводится к виду

и

At«2J(

О)

Так как U,

определяется выражением (3), а

г

(10) )

№

и.

on

-

At

где m - коэффициент пропорциональности. Отсюда следует, что величина временного интервала At, преобразованная в цифровой код, пропорциональна среднему значению исследуемого сигнала Ug за время Т усреднения с погрешностью, обусловленной пренебрежением в формуле (8) при разложения функции (6) в степенной ряд членами высших степеней данного ряда. При легко реализуемом отношении погрешность изменения среднего значения напряжения U произ1 ольной формы предложенным способом по превышает удвоенного вторсяо члена ряда и определяется величиной , I - о, 00 1 I -.00 . п 0,07 % Знак сред1Ш)Ч величины исследуемого напряжения и большую из величин SUP(AuB) определяют знаком разности 0 А - В. Если б О, то А В и величина среднего значения напряжения Ug, определяемая величиной интервала At, положительная. Если , то В А и величина среднего значения напряжения отрицательна Устройство функционирует следующи образом. Работа устройства во времени состоит из стадии подготовки, стадии одновременного интегрирования суммы опорного Ujjf, и исследуемого Ug напряжений интегратором 1 и интегрирова ния разности указанйых напряжений ин тегратором 2, из стадии преобразования, заключающейся в изменении по - экспоненциальному закону большего из полученных в предащущей стадии напря до меньшего и одновременного преобразования получающегося временного интервала в цифровой код. При этом отсчет временного интервала начинается с начала стадии преобразования напряжений и заканчивается моментом сравнения выходных напряжений интеграторов 1 и 2. Информацию о знаке среднего значения исследуемого напряжения Uj получают путем сравнения выходных напряжений интеграторов 1 и 2 и индицируют ее регист ратором 26 знака. В исходном состоянии на шине 14 запуска и на шине 13 синхронизации присутствуют напряжения нулевого уровня. При этом на выходах 19-24 блока 15 управления присутствуют напряжения нулевого уровня (фиг. 2г д, 3, и, к), в результате чего ключи 3-5 цепи сброса интеграторов 1 и 2, а также ключи 6 и 7 разомкнуты В момент времени t на шину запуска 14 приходит импульс напряжения Пуск, поступающий на вход 17 блока 15 управления,, в связи с чем с момента Ц блок управления 15 формирует на своем вькоде 19 напряжени уровня логической единицы (фиг. 2г) При этом разрядные цепи интеграторов 1 и 2 (ключи 56 и 57) замыкаются и на выходах интеграторов 1 и 2 устанавливаются напряжения нулевого уровня (фиг. 2е). В момент времени 2 первый синхроимпульс Т поступает с шины синх ронизации 13 на вход 16 блока 15 управле.ния, в связи с чем в момент t напряжение на выходе 19 блока 15 управления устанавливается на нулевом уровне (фиг. 2г). С момента tj, блок 15 управления формирует на своем выходе 20 напряжение уровня логической единицы, которое поступает на управляющие входы ключей 3-5 и на управляющий (сбросовой) вход преобразователя 11 время-код. В результате счетчик 60 удерживается в сброшенном состоянии. В течение времени действия управляющего импульса ключи 3-5 с момента t замыкаются. К первому сигнальному входу интегратора 1 подводится исследуемое напряжение Ug. На первый сигнальньй вход интегратора 2 то же напряжение с учетом действия интегратора 9 поступает в обратной полярности. Вторые сигнальные входы интеграторов 1 и 2 с момента t соединяются с выходом источника 8 опорного напряжения С момента t2 напряжение на выходе интегратора 1 изменяется согласно , Cii) 1-2 постоянные интегрирования интегратора 1 соответственнь по второму и первому сигнальным входам, определяемые выражениями С - D Г которых Ry и R 50 - сопротивлеия масштабных резисторов соответстенно 52 и 50; Cj - емкость конденсатора 54. С момента tj напряжение на выхое интегратора 2 изменяется согласно tj+i - () С, 3 ч i S де bj и - постоянные интегрироания интегратора 2 соответственно ° второму и первому сигнальным вхо определяемые выражениями VR.,C, , ,

в которых Rj и Ryj - сопротивления масштабных резисторов соответственно 51 и 53 j

С-у емкость конденсатора 55.

В момент времени вход 16 блока 15 управления поступает второй синхроимпульс с шины синхронизации 13, в результате чего в момент tg- напряжение на выходе 20 блока 15 управления устанавливается на нулевом уровне. При этом ключи 3-5 размыкаются. Снимается принудительньй сброс с преобразователя 11 время-код (вприведенном примере реализации снимается сброс со счетчика 60). Также с момента tj на выходе 23 блока 15 управления формируется напряжение уровня логической единицы, которое, поступая на информационный вход преобразователя 11 время-код, запускает последний.

Напряжения U:, и U на выходах интеграторов 1 и 2 в момент-i равны величинам интегралов соответственно суммы и разности опорного U и исследуемого Щ напряжения за время Т усреднения:

U, ,T.U5di-KJ.K,U, -, С)

1 2. и

о Т

on. 1

Т.1- п ,U,, . (15)

4i Ч Щ S - коэффициенты пропортдиональности. Компаратор 10 постоянно отслеживает соотношения напряжений на своих двух входах, равных соответственно и Ug;(. При отношении входных напряжений ( /Ugxa выходе компаратора 10 формируется напряжение уровня логической единицы, что обусловливает появление на выходах 21 и 22 блока 15 управления напряжений уровней соответственно ло гической единшды и нуля. При этом интегратор 1 с момента t разряжается по экспоненциальному закону, интегратор 2 с того же момента хранит свое выходное напряжение неизменным,

а на выходах 24 и 25 блока 15 управления формируются уровни напряжений соответственно логической единицы и логического нуля, которые, поступая в регистратор 26 знака, индицируют

При отноп ении входных

знак

Нвхл.

напряжений компаратора 10

: 1

UB,

интегратор 2 разряжается по экспоненциальному закону до напряжения, хранящегося на выходе интегратора 1 и индицируется знак -.

Таким образом, в устройстве всегда обеспечивается во второй ста5 дни его работы с момента tg уменьшение выходного напряжения одного интегратора до неизменно хранящегося напряжения другого.

На временных диаграммах, изображенных на фиг. 2, рассмотрен вариант работы устройства, когда в момент t выходные напряжения интеграторов 1 и 2 находятся в соотношении

5 U-its -irПри этом блок 15 управления формирует с момента tj на своем выходе 21 напряжение уровня логической единицы, отчего ключ 6 с момента t

0 за Фщается и напряжение на выходе интегратора 1 и на первом входе компаратора 10 изменяется по закону

(-.)

-, S

CU) tv/tf ЧгС момента tg- напряжение на выходе интегратора 2 и на втором входе ком-. паратора 10 остается неизменным во времени U2i5В момент времени t/ напряжения на входах компаратора 10 сравниваютсяMil С . 2 U. и,, Чь 4fe уровень выходного напряжения компаратора 10 меняется на противоположный. В момент t смены уровня напряжения по входу 18 блока 15 управления на выходе 23 последнего уровень напряжения меняется о .юг-ической единицы на логический нуль. Таким образом, на выходе 23 блока 25 управления формируется импуль напряжения длительностью 2,, ui.t,-t..- -:r -tJn-V-r - tlM 1 1 При выполнении условия и Л имеем При разложении в выражении (19) логарифмической функции в ряд Тейл ра и пренебрежении в последнем членами высших степеней данного ря Да .. ;. . Величина отношения реализуется соответствующим выборо ot и р для известных границ jUufnax и минимального времени Т усред нения., Так как U,,, определяется выражением (3), а I LJgcfi . из) Отсюда следует, что длительност импульса напряжения с выхода блока 23 блока 15 управления, преобра зованная в цифровой код, отображен ная и сохраняющаяся на цифровом ин дикаторе 27, пропорциональна среднему значению входного сигнала U .за время Т усреднения с погрешностью, обусловленной пренебрежением в (10) при разложении функции (9) в степенный ряд членами высших степеней данного ряда. Работа одного из возможных примеров реализации блока 15 управления, изображенного на фиг, 1, заключается в следующем. В момент времени t, триггер 28 взводится импульсом пуск (фиг. 2в), поступающим на его второй вход с входа 17 блока 15 управления. На выходе триггера 28 с момента t ус- . танавливается напряжение уровня логической единицы, направляющееся на выход 19 блока 15 управления (фиг. .2г) и на вход д триггера 29. В момент времени t- первый синхроимпульс Т поступает с входа 16 блока 15 управления на первый вход триггера 28 и на вход С -триггера 29, на прямом выходе которого в момент t формируется напряжение уровня логической единицы (фиг. 2д). Напряжение уровня логического нуля поступает с момента tg с инверсного выхода триггера: 29 на первые входы элементов 31 и 32 И и на вход дифференцирующего звена 36-37. CHHxpoiiMnynbcoM по первому входу триггер 28 сбрасывается и в момент t- напряжение на его выходе и на выходе 19 блока 15 управления падает до уровня логического нуля (фиг. 2г). Импульсы напряжения, приходящие на вход 18 блока 15 управления в интервале времени , не изменяют состояние уровней напряжений на его выходах 19-23, так как элементы 31 и 32 И в вышеуказанном интервале времени закрыты напряжением уровня ло гического нуля по первому входу, а состояние триггера 29 также остается в этом интервале времени неизменным. В момент времени t на вход 16 лока 15 управления поступает втоой (очередной) синхроимпульс Т . этому моменту времени (а именно момента t) на вьосоде 18 блока 15 правления действует напряжение уровя логической единицы. С поступлением синхроимпульса Tj. на вход С триггера 29 на рямом выходе последнего с момента j. формируется напряжение уровня огического нули (г.е. напряжение ого уровня, которое действовало входег триггера 29 до прихода синхроимпульса на его С вход), по ступающее на выход 20 блока 15 упра ления (фиг. 2д). На инверсном выхо де триггера 29 с момента t ||юрмиру ется напряжение уровня логической единицы. При этом на обоих входах элемента 31 И присутствуют уровни логической единицы, отчего на его выходе с момента tg формируется напряжение уровня логической единицы, поступающее на выход 21 блока 1 управления (фиг. 2з). .. .-. Положительный перепад напряжения импульса с инверсного выхода триггера 29 поступает в момент t на вход дифференцирующего звена 36-37, на выходе которого в этот момент формируется положительный импульс напряжения. Сформированный сигнал, проходя через диод 42, направляется на первый вход триггера 30. При этом триггер 30 взводится и на его выходе формируется с момен та tj напряжение уровня логической

;

Ul.f единицы, поступающее на выход 25 блока 15 управления (фиг. 2и). В момент времени t напряжение на входе 18 блока 15 управления меняет свой уропень с логической единицы на логический нуль. При этом элемент 31 И закрывается по второму входу и на его выходе формируется с момента t напряжение уровня логического нуля, поступающее на выход 21 блока 15 упранлгния (фиг. 2з). Отрицательный перепад напряжения на входе инвертора 35 в момент t инвертируется последним, и положительньй перепад напряжения с выхода инвертора 35 поступает на дифференцирующее звено 40-41. Положительный импульс напряжения с выхода данного дифференцирующего звена, проходя через диод 45 на второй вход триггера 30, сбрасывает последний, в результате чего на выходе триггера 30 с момента t формируется напряжение уровня логического нуля, поступающее на выход 23 блока 15 управления (фиг. 2и).

а % Т Uf${19} 9Ш(2Ш ., tf

Фиг. 2 t2

| Динамический фильтр | 1974 |

|

SU568150A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Справочник по нелинейньв схемам | |||

| Под ред | |||

| Д, Шейнголда, М., Мир, 1977, с | |||

| Способ получения бензидиновых оснований | 1921 |

|

SU116A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1985-04-15—Публикация

1983-06-16—Подача