печения с помощью введенного переключателя 12 режимов и изменения алгоритма рйботы блока управления дополнительной возможности контроля

Изобретение относится к импульсной и измерительной технике и предназначено для контроля цифроаналого- вых преобразователей (ЦАП).

Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля дифференциальной нелинейности и погрешности полно шкалы,

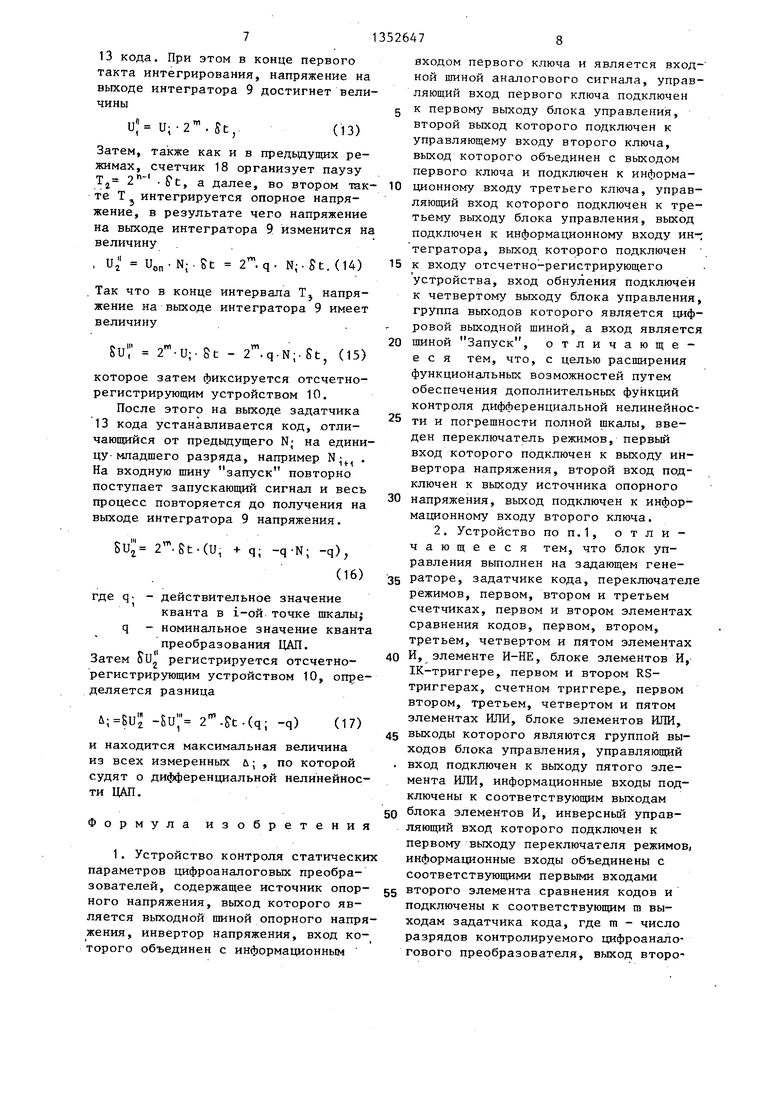

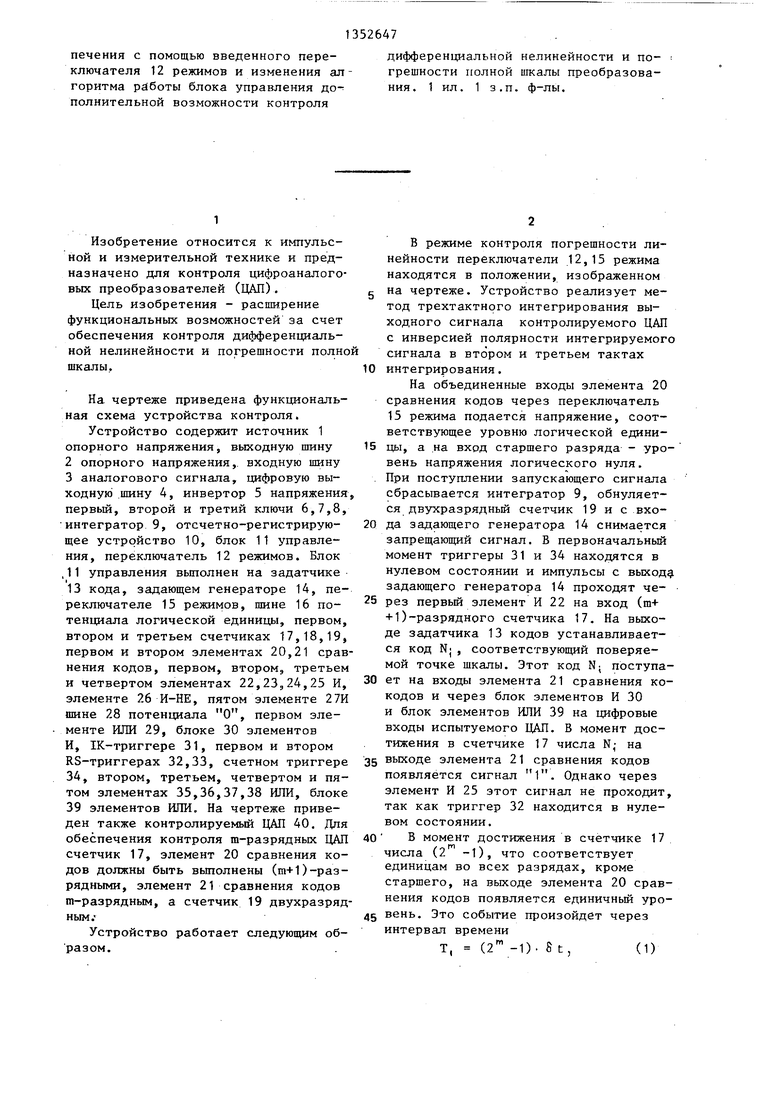

На чертеже приведена функциональная схема устройства контроля.

Устройство содержит источник 1 опорного напряжения, выходную шину

2опорного напряжения,, входную шину

3аналогового сигнала, цифровую выходную .шину 4, инвертор 5 напряжения первый, второй и третий ключи 6,7,8,

интегратор 9, отсчетно-регистрирую- щее устройство 10, блок 11 управления, переключатель 12 режимов. Блок

, 11 управления вьтолнен на задатчике 13 кода, задающем генераторе 14, переключателе 15 режимов, шине 16 потенциала логической единицы, первом, втором и третьем счетчиках 17,18,19, первом и втором элементах 20,21 сравнения кодов, первом, втором, третьем и четвертом элементах 22,23,24,25 И, элементе 26 И-НЕ, пятом элементе 27И шине 28 потенциала О, первом элементе ИЛИ 29, блоке 30 элементов И, 1К-триггере 31, первом и втором RS-триггерах 32,33, счетном триггере 34, втором, третьем, четвертом и пятом элементах 35,36,37,38 ИЛИ, блоке 39 элементов ИЛИ. На чертеже приведен также контролируемый ЦАП 40. Для обеспечения контроля т-разрядных ЦАП счетчик 17, элемент 20 сравнения кодов должны быть выполнены (т+1)-разрядными, элемент 21 сравнения кодов т-разрядным, а счетчик 19 двухразрядным ;

Устройство работает следующим об- разом.

дифференциальной нелинейности и погрешности полной шкалы преобразования. 1 ил. 1 з.п. ф-лы.

0

0 5 0 5

5

В режиме контроля погрешности линейности переключатели 12,15 режима находятся в положении, изображенном на чертеже. Устройство реализует метод трехтактного интегрирования выходного сигнала контролируемого ЦАП с инверсией полярности интегрируемого сигнала в втором и третьем тактах интегрирования.

На объединенные входы элемента 20 сравнения кодов через переключатель 15 режима подается напряжение, соответствующее уровню логической единицы, а на вход старшего разряда - уровень напряжения логического нуля. При поступлении запускающего сигнала сбрасывается интегратор 9, обнуляется двухразрядный счетчик 19 и с входа задающего генератора 14 снимается запрещающий сигнал. В первоначальный момент триггеры 31 и 34 находятся в нулевом состоянии и импульсы с выходу задающего генератора 14 проходят через первьй элемент И 22 на вход (т+ +1)-разрядного счетчика 17. На выходе задатчика 13 кодов устанавливается код NJ , соответствующий поверяемой точке шкалы. Этот код N; поступает на входы элемента 21 сравнения ко- кодов и через блок элементов И 30 и блок элементов ИЛИ 39 на цифровые входы испытуемого ЦАП. В момент достижения в счетчике 17 числа N,- на выходе элемента 21 сравнения кодов появляется сигнал 1. Однако через элемент И 25 этот сигнал не проходит, так как триггер 32 находится в нулевом состоянии.

В момент достижения в счетхшке 17 числа (2 -1), что соответствует единицам во всех разрядах, кроме старшего, на выходе элемента 20 сравнения кодов появляется единичный уровень. Это событие произойдет через интервал времени

Т, (2 -1). 8t, (1)

где St - период импульсов задающего

генератора 14.

На всем интервале времени Т,(1) происходит- интегрирование напряжения U; (выходное напряжение ЦДЛ для.кода NJ) по цепи: входная шина 3 устройства (выход ЦАП), замкнутый ключ 6, замкнутый ключ 8, интегратор 9. Напряжение на выходе интегратора 9 в конце интервала Т, (1) равно

(2)

и, U;

(2 -1).. t,

где St - период импульсов задающего

генератора 14,

Сигнал единичного уровня, появившийся в конце интервала на выходе элемента 20 сравнения кодов приведет 1К-триггер 31 в единичное, состояние. Далее сигнал единичного уровня появляется на выходе элемента ИЛИ 37, на выходе элемента ИЛИ 35, на выходе элемента ИЛИ 38, а также на выходе элемента ИЛИ 29. При этом третий ключ 8 размыкается, на разрядных выходах блока элементов ШШ 39 появляется число, соответствующее максимальному значению преобразуемого кода (Nj 11...1), размыкается первый

ключ 6, тем самым обеспечивается подготовка к второму такту интегрирования. Сигнал с прямого выхода 1К-триг гера 31 пройдет через элемент ИЛИ 35 поступит также на вход второго элемента И 23, отпирая его для поступления импульсов задающего генератора 14 на вход п-разрядного счетчика 18.

Разрядность счетчика 18 длительность интервала Т,

определяет

т i

n-t

. St

Т превышает время установления ЦАП, необходимое для устранения влияния на результат измерения переходных процессов и равен времени заполнения счетчика 18 до появления 1 в его старшем разряде. Появившийся по истечении интервала времени Т сигнал в старшем разряде счетчика 18, возводит RS-триггер 32 в единичное состояние, который в свою очередь поступает на К-вход 1К-триггера 31, подготавливая его переход по синхросигналу в нулевое состояние. Одновременно единичньй сигнал поступает на вход третьего элемента И 24, проходит его, появляясь на вькоде коротким импуль

26474

сом обнуления счетчиков 17,18, тригг- геров 31,33,34. На выходе первого элемента ИЛИ 35 появляется сигнал ну- нулевого уровня, которьй проходит через второй элемент ИЛИ 29 и замыкает ключ 8, а появившийся на выходе элемента И-НЕ 26 единичньй сигнал замыкает второй ключ 7, пропуская 10 на вход интегратора 9 сигнал с выхода инвертора 5, который в данный момент инвертирует напряжение полной шкалы ЦАП 40. Второй такт интегрироТ,

N: . St

(4)

20

заканчивается в момент повторного срабатывания элемента 21 сравнения кодов, сигнал с выхода которой проходит через четвертый элемент И 25-, устанавливает в единичное состояние RS-триггер 33 и поступая на счетньй ВХОД триггера 34, через второй эле25 мент ИЛИ 36, устанавливает его в единичное состояние, закрывая тем самым доступ импульсов задакнцего генератора 14 на вход первого счетчика 17.. Одновременно сигнал единично30 го уровня поступает через элемент ИЛИ 35 на вход второго элемента И 23, открывая поступление счетных импульсов на вход счетчика 18. Одновременно сигнал единичного уровня поступа35 ет с прямого выхода триггера 34 на R-вход триггера 32, переводя его в нулевое состояние.

Время заполнения .счетчика 18 определяет длительность интервала

40 Tj, которьй в свою очередь служит для исключения влияния пер еход- ных процессов выходного сигнала ЦАП, при смене преобразуемого кода N-. В начале интервала Т, по сигналу

45 1 с прямого выхода триггера 33, поступающему через второй переключатель 15 режима на инверсньй вход блока элемента И 30, происходит обнуление сигнала- на цифровом входе

50 ЦАП 40. В интервале Ту Т, - Т, осуществляется третий такт интегрирования выходного сигнала ЦАП 40j представляющего собой проинвертированное напряжение смещения нуля ЦАП 40.

55 После первого такта интегрирования (интервал Т) напряжение на выходе интегратора равно

У, и.-. ( -1).St.

(5)

1352647

После второго такта интегрирования (TJ) напряжение на выходе интегратора 9 определится

как

Su и, - и.

(6)

что

(Z -l).N;.St,

и, q - N,+ SU

)

где q номинальный квант преобразования ЦАП.

И подставляя в (6) и (5) можно записать;

SU C Tj SU; + (Т,- Т)

UoM,(V)

где SU - погрешность линейности

- смещение нуля ЦАП 40; и - значение напряжения на вы- ходе интегратора 9 в конце интервала Т,.

По истечении третьего такта ннтег рирования Tj, напряжение на выходе интегратора 9 станет равно величине

&и С.Т,. Su

1 )

(8)

где С коэффициент преобразования, определяемый постоянной времени интегратора 9, величина, пропорциональная погрешности линейности ЦАП. В конце -интервала Тс -происходит

Ju -возврат всех необходимых логических элементов в нулевое состояние а задающий генератор 14.прекращает сво функционирование, потому что на выходе второго разряда двухразрядного счетчика 19 появляется 1. На выходе интегратора 9 остается запомненое значение S U .

В режиме измерения погрешности полной шкалы ЦАП устройства работает следующим образом.

Переключатели 12515 режима переводятся в состояние противоположное изображенному на чертеже. При этом на опорном входе элемента 20 сравнения кодов выставляется код 10.,.00, где 1 устанавливается в старшем (т+1)-разряде, а на выходе задатчика 13 кодов устанавливается код N. 11... 11, где 1 устанавливается во всех m разрядах.

Логическая часть устройства формирует на выходах цифровых элементов сигналы аналогичные, как и в режиме контроля погрешности линейности. Однако длительность первого такта интегрирования в данном режиме равна

6

t

(9)

На этом интервале с выхода ЦАП 40 снимается напряжение полной шкалы, так как на цифровых входах преобразователя присутствует максимальньй код. Это напряжение, пройдя через клю- ключи 6 и 8, интегрируется. По окончании времени Т на выходе интегратора устанавливается напряжение

и, С-(2 -1). q.St ± C-SV (10)

nui

где S и щ-погрешность полной шкалы ЦАП.

Затем на выходе второго элемента ИЛИ 29 появляется сигнал единичного уровня длительности (3), размыкающий ключ 8.

В интервале времени Т происходит интегрирование опорного напряжения, снимаемого с выхода источника 1 опорного напряжения через переключатель

12 режима, ключи 7 и 8 на вход интегратора 9, Так как напряжение источника 1 опорного напряжения часто противоположно полярности выходного сигнала ЦАП, то в конце интервала Т

напряжение на выходе интегратора 9 уменьшится на величину

и; C.U,,.(). С. 2,.q.

(). . (11

где значение опорного напряжения

После чего на выходе интегратора 9 останется-напряжение

&и и, - и;, ± (12)пропорциональное погрешности полной шкалы ЦАП. Вторично ключ 8 размыкается на интервал времени Т Т, поэтому в этом режиме вьтолняется лишь двухтактное интегрирование.

При измерении дифференциальной нелинейности переключатели 12,15 режима также находятся во втором положении как и в режиме измерения погрешности полной шкалы, а процесс измерения этого параметра осуществляется за четыре такта интегрирования по следующему алгоритму.

В первом такте интегрирования производится интегрирование напряжения U; , которое является аналоговым эквивалентом цифрового кода N; , установленного на выходе задатчика

13 кода. При этом в конце первого такта интегрирования, напряжение на выходе интегратора 9 достигнет величины

и; U;

2. 5t,.

(13)

Затем, также как и в предьщущих режимах, счетчик 18 организует паузу -ft, а далее, во втором -такте Т интегрируется опорное напряжение, в результате чего напряжение на выходе интегратора 9 изменится на величину . .

и .St г

Так

жение на выходе интегратора 9

величину

N;- St. (14)

Т,

что в конце интервала Ij напряимеет

SU , 2 -U;-St - 2.q.N;.St, (15)

которое затем фиксируется отсчетно- регистрирующим устройством 10.

После этого на выходе задатчика 13 кода устанавливается код, .отличающийся от предыдущего N,- на единицу-младшего разряда, например N-. . На входную шину запуск повторно поступает запускающий сигнал и весь процесс повторяется до получения на выходе интегратора 9 напряжения.

SU 2. St-(U, + q; -q-N; -q),

(16)

где

q; действительное значение кванта в i-ой точке шкалы; q - номинальное значение кванта

преобразования ЦАП. Затем и. регистрируется отсчетно- регистрирующим устройством 10, определяется разница

-Su; 2.t.(qi -q) (17)

и находится максимальная величина из всех измеренных л; , по которой судят о дифференциальной нелинейности ЦАП.

Формула изобретения

1. Устройство контроля статических параметров цифроаналоговых преобразователей, содержащее источник опор- ного напряжения, выход которого является выходной шиной опорного напряжения, инвертор напряжения, вход которого объединен с информационным

входом первого ключа и является вход- ной шиной аналогового сигнала, управляющий вход первого ключа подключен к первому выходу блока управления, второй выход которого подключен к управляющему входу второго ключа, выход которого объединен с выходом первого ключа и подключен к информационному входу третьего ключа, управляющий вход которого подключен к третьему выходу блока управления, ВЬЕХОД подключен к информационному входу ин- тегратора, выход которого подключен

к входу отсчетно-регистрирующего

устройства, вход обнуления подключён к четвертому выходу блока управления, группа выходов которого является цифровой выходной шиной, а вход является

шиной Запуск, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения дополнительных функций контроля дифференциальной нелинейности и погрешности полной шкалы, введен переключатель режимов, первый вход которого подключен к выходу инвертора напряжения, второй вход подключен к выходу источника опорного

напряжения, выход подключен к информационному входу второго ключа.

2. Устройство ПОП.1, отличающееся тем, что блок управления выполнен на задающем генераторе, задатчике кода, переключателе режимов, первом, втором и третьем счетчиках, первом и втором элементах сравнения кодов, первом, втором, третьем, четвертом и пятом элементах И, элементе И-НЕ, блоке элементов И, 1К-триггере, первом и втором RS- триггерах, счетном триггере, первом втором, третьем, четвертом и пятом элементах ИЛИ, блоке элементов ИЛИ, выходы которого являются группой выходов блока управления, управляющий вход подключен к выходу пятого элемента ИЛИ, информационные входы подключены к соответствующим выходам блока элементов И, инверсный управляющий вход которого подключен к первому выходу переключателя режимов, информационные входы объединены с соответствующими первыми входами второго элемента сравнения кодов и подключены к соответствуюш им m выходам задатчика кода, где m - число разрядов контролируемого цифроанало- гового преобразователя, выход второ

го элемента сравнения кодов подключен к первому входу четвертого элемента И, вторые входы объединены с соответствующие} m входами младпшх разрядов первой группы входов первого элемента сравнения кодов и подключены к соответствующим m выходам младпшх разрядов первого счетчика, выход (т+1)-го разряда которого подключен к (т+1)-му входу первой группы входов первого элемента сравнения кодов, счетный вход подключен к выходу первого элемента И, первый вход которого подключен к инверсному выходу счетного триггера, второй вход .подключен к инверсному выходу 1К- триггера, третий вход объединен с первым входом второго элемента И, входом синхронизации 1К-триггера и подключен к выходу задающего генератора,, управляющий вход которого подключен к выходу второго разряда тре- тъего счетчика, вход обнуления которого является входом и четвертым выходом блока управления, счетный вход объединен с первым входом третьего элемента И, 1-входом 1К-триг- гера и подключен к выходу перво.го элемента сравнения кодов, m входов младших разрядов второй группы входов которого объединены и подклйчены к второму выходу переключателя режимов, (т+1)-й вход второй группы входов подключен к третьему выходу переключателя режимов, первый вход которого подключен к шине потенциала логической единицы, второй вход подключен к шине потенциала логического нуля, третий вход объединен с первым входом пятого элемента И и подключен к прямому выходу второго RS-тригге- ра, четвертый выход подключен к перРедактор М, Товтин

Составитель В. Першиков

Техред Л.Сердюкова Корректор В.Гирняк

.Заказ 5576/56 Тираж 900 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

вому входу первого элемента ИЛИ, выход которого является третьим выходом блока управления, второй вход объе-

динен с вторым .входом второго элемента И и подключен к выходу второго элемента ИЛИ, первый вход которого объединен с первыми входами четвертого и пятого элементов ИЛИ и подклю- чен к прямому выходу IK-триггера,

второй вход объединен с R-входом первого RS-триггера и подключен к прямому выходу счетного .триггера, вход обнуления которого объединен с входами обнуления первого и второго счетчиков, входом обнуления 1К-триггера, К-входом второго RS - триггера и подключен к выходу третьего элемента И, счетный вход счетного триггера подключен к выходу третьего элемента ИЛИ,- первый вход которого объединен с S-входом второго RS-триггера и подключен к выходу четвертого элемента И, второй вход подключен к выходу

пятого элемента И, второй вход которого объединен с S-входом -первого RS-триггера и подключен к выходу второго счетчика, счетный вход которого подключен к выходу второго элемента

И, прямой выход первого RS-триггера подключен к К-входу 1К-триггера второму входу третьего элемента И, второму входу четвертого элемента И и второму входу пятого элемента ИЛИ,

,инверсный выход подключен к первому . входу элемента И-НЕ, второй:вход ко- торого подключен к инверсному вьЬсоду RS-триггера-, выход подключен к второму входу четвертого элемента ИЛИ

и является вторым выходом блока управления, выход четвертого элемента ШШ является первым вькодом блока управления«

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой низкочастотный фазометр | 1990 |

|

SU1780042A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1986 |

|

SU1473083A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Логарифмический аналого-цифровой преобразователь | 1985 |

|

SU1277146A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

Изобретение относится к. импульс- ной и измерительной технике и предназначено для контроля цифроаналого- вьгх преобразователей (ЦАП) . Цель - расширение функциональных возможное- тей. Устройство контроля содержит источник 1 опорного напряжения, выходную шину опорного сигнала, входную шину 3 аналогового сигнала, цифровую выходную шину 4, инвертор 5 напряжения, первый, второй и третий ключи 6,7,8, интегратор 9, отсчетно- регистрирующее устройство 10, блок 11 управления, переключатель 12 режимов. Цель достигается за счет обесСЛ

| Устройство контроля коэффициента передачи цифро-аналоговых преобразователей | 1982 |

|

SU1061259A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Измерения и контроль в микроэлектронике | |||

| /Под ред | |||

| А.А | |||

| Сазонова- М.: Высшая школа, 1984, с.311. | |||

Авторы

Даты

1987-11-15—Публикация

1986-03-11—Подача