Изобретение относится к вычислительной технике и может быть использовано для распределения заявок по процессорам в мультипроцессорных системах.

Цель изобретения - повышение надежности функционирования устройства за счет обслуживания заявок при отказе двух и более процессоров, назначенных на их решение, во время распределения текущей заявки.

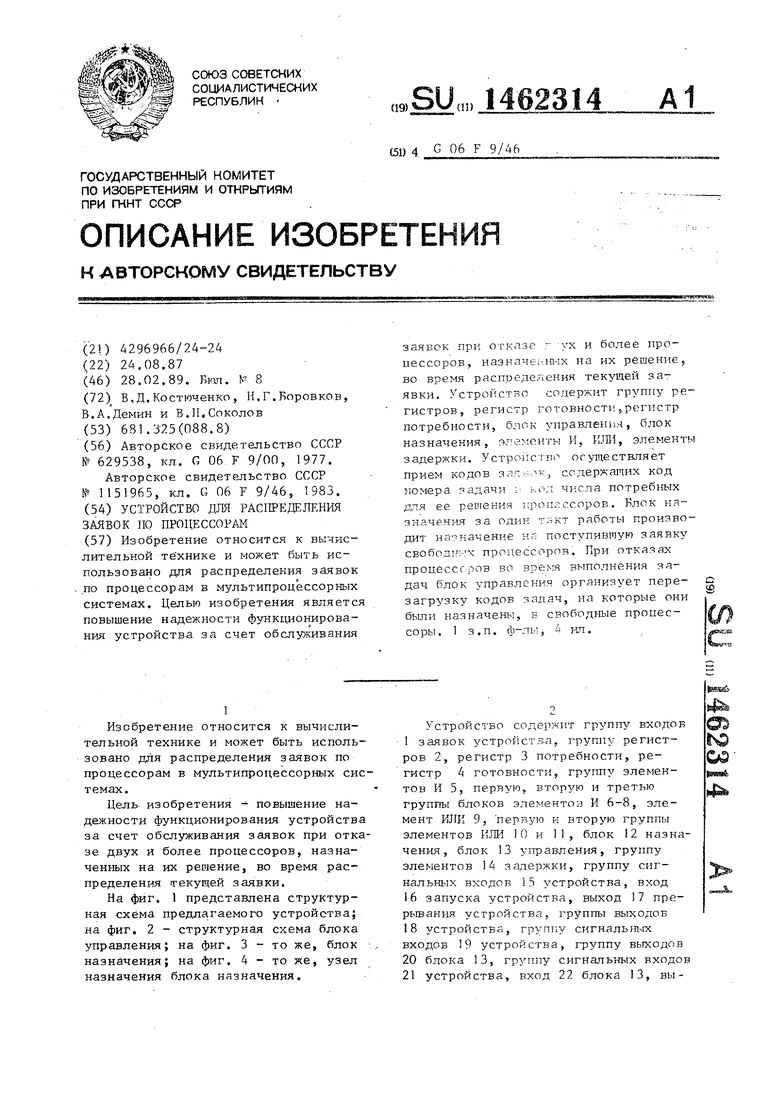

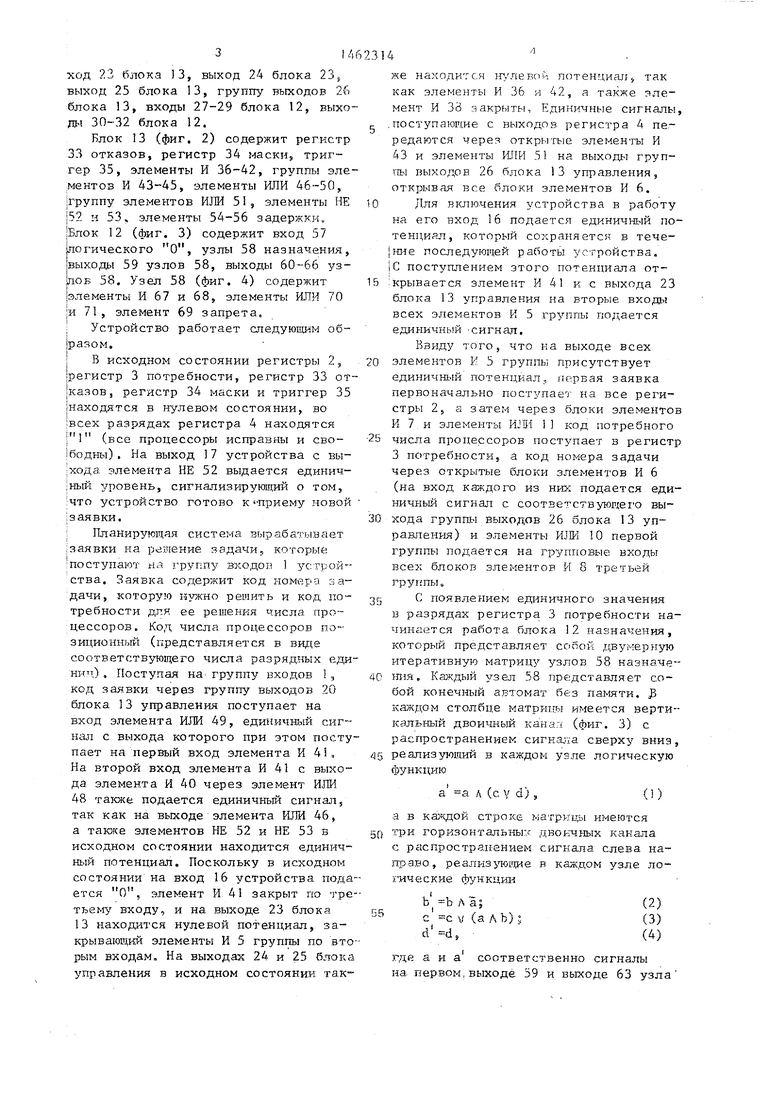

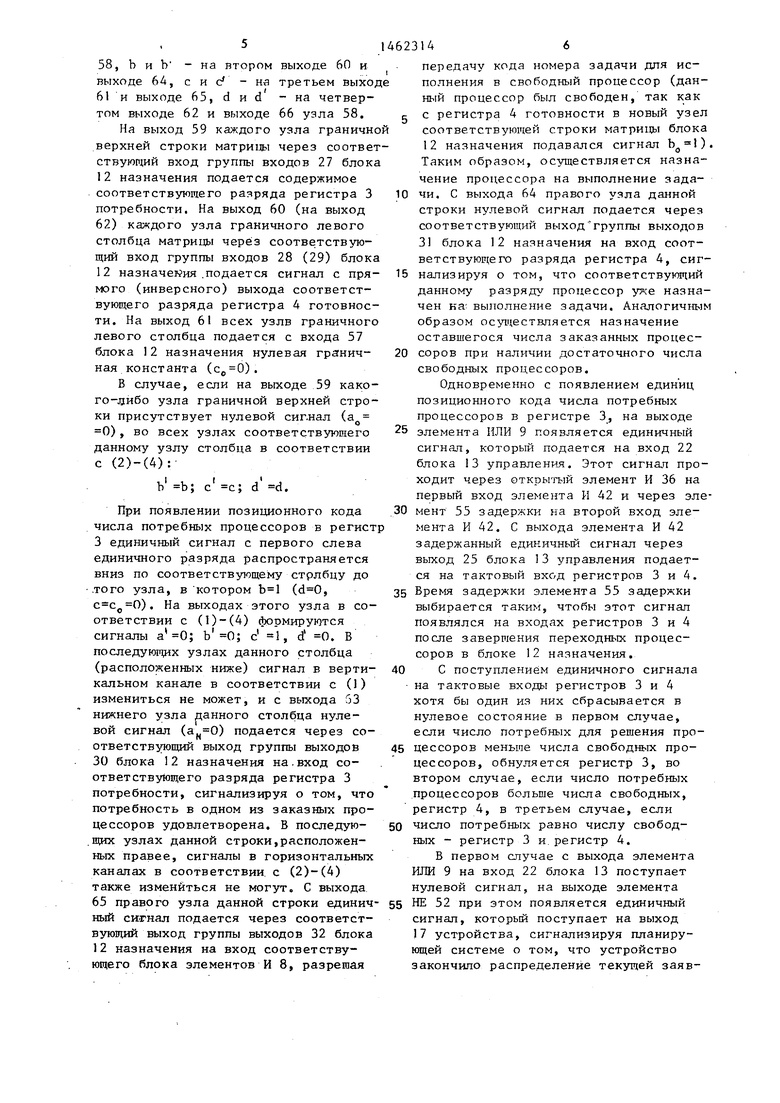

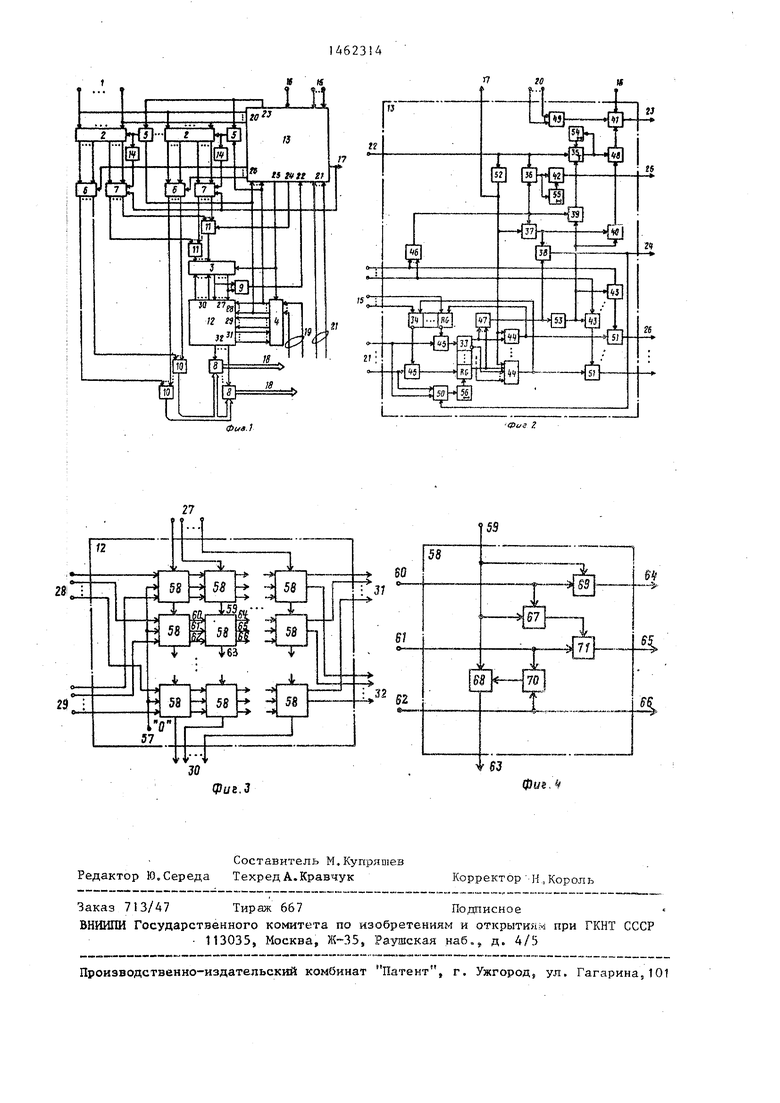

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема блока управления; на фиг. 3 - то же, блок :.. назначения; на фиг. 4 - то же, узел назначения блока назначения.

Устройство содержит группу входов 1 заявок устройства, группу регистров 2, регистр 3 потребности, регистр 4 готовности, группу элементов И 5, первую, вторую и третью группы блоков элементов И 6-8, элемент ИЛИ 9, первую и вторую группы элементов ИЛИ 10 и 11, блок 12 назначения, блок 13 управления, группу элементов 14 задержки, группу сигнальных входов 15 устройства, вход 16 запуска устройства, выход 17 пре- рьгоания устройства, группы выходов 18 устройства, группу сигнальт гх входов 19 устройства, группу выходов

20блока 13, группу сигнштылгх входов

21устройства, вход 22 блока 3, выО9

314

ход 23 блока )3, выход 24 блока 23 выход 25 блока 13, группу выходов 26 блока 13, входы 27-29 блока 12, выходы 30-32 блока 12.

Блок 13 (фиг, 2) содержит регистр 33 отказов, регистр 34 маскиа триггер 35, элементы И 36-42, группы элементов И 43-45, элементы ИЛИ 46-50,, группу элементов ИЛИ 51, элементы НЕ 152 н 53, элементы 54-56 задержки. 1Блок 12 (фиг. 3) содержит вход 57 логического О, узлы 58 назначения, |выходы 59 узлов 58, выходы 60--66 узрев 58. Узел 58 (фиг. 4) содержит элементы И 67 и 68, элементы ИЛИ 70 ;и 71, элемент 69 запрета. : Устройство работает следующим об- jpasoM.

; В исходном состоянии регистры 2, |регистр 3 потребности, регистр 33 отказов, регистр 34 маски и триггер 35 (находятся в нулевом состоянии, во ;Всех разрядах регистра 4 находятся (все продессоры исправны и сво- |бодны). На выход 17 устройства с вы- ;хода элемента НЕ 52 выдается единич- ;ный уровень, сигнализирующий о том, -что устройство готово К -приему новой заявки.

; Планирующая система вырабатывает .заявки на регюние задачи, которые поступают на группу входом 1 устройства. Заявка содержит код номера задачи, котору о нужно решить и код по- требности для ее решения числа про-- дессоров. Код числа процессоров по-- зидионный (представляется в виде соответствующего числа разрядных еди ни т,) . Поступая на группу входов 1 ,

код заявки через группу выходов 20 блока 13 управления поступает на вход элемента ИЛИ 49, единичный сиг-нал с выхода которого при этом поступает на первый вход элемента И На второй вход элемента И 41 с выхода элемента И 40 через элемент ИЛ14 48 также подается единичньш сигнал, так как на выходе элемента ИЛИ 46, а таюке элементов НЕ 52 и НЕ 53 в исходном состоянии находится единич- т.1Й потендиал. Поскольку в исходном состоянии на вход 16 устройства пода

же находится т левой потенциал так как элементы И 36 и 42, а также элемент И 33 закрыты. Единичные сигналы .поступающие с выходов регистра 4 передаются через открытые элементы И 43 и элементы ИЛИ 51 на выходы груп- 1ТЫ выходов 26 блока 13 управления, открывая все блоки элементов И 6.

Для включения устройства в работу на его вход 16 подается единичный потенциал, который сохраняется в тече- |ние последующей работы устройства. JC поступлением этого потенциала открывается элемент И 4 не выхода 23 блока 13 управления на вторые входы всех элементов И 5 группы подается единичный -сигнал.

Ввиду того, что на выходе всех элементов И 5 группы присутствует единичный потенциал,, первая заявка первоначально поступает на все регистры 2, а затем через блоки элементо И 7 и элементы ИЛИ 1 1 код потребного числа процессоров поступает в регист 3 потребности, а код номера задачи через открытые блоки элементов И 6 (на вход каждого из них подается единичный сигнал с соответствующего выхода группы выходов 26 блока 13 управления) и элементы ИЛИ 10 первой группы подается на групповые входы всех блоков элементов И 8 третьей группы,

С появлением единичного значения Б разрядах регистра 3 потребности начинается работа блока 12 назначения, который представляет собой двумерную итеративную матрицу узлов 58 назначе Ш1Я. Каждый узел 58 представляет собой конечный автомат без пажити. 3 каждом столбце матрицы имеется вертикальный двоичный кана;-. (фиг. 3) с распространением сигнала сверху вниз реализующий в каждом узле логическую функцию

а а л (су d) ,()

а в каакдой строке матрицы имеются три горизонтальны: двокгчных канала с распространением сигнала слева направо, реализт,тою;ие в каждом узле ло- А ические функции

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1246096A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1151966A1 |

| Устройство для распределения групповых заявок по процессорам | 1985 |

|

SU1254485A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1290324A1 |

| Устройство для диспетчеризации заявок | 1985 |

|

SU1247873A1 |

| Многоканальное устройство диспетчеризации | 1989 |

|

SU1689950A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1481762A2 |

| Устройство для распределения заданий процессорам | 1986 |

|

SU1310821A1 |

Изобретение относится к вычислительной т е хнике и может быть использовано для распределения заявок ,по процессорам в мультипроцессорных системах. Целью изобретения является повышение надежности функдионирова- ни-я устройства за счет обслуживания заявок при отказе j ух и более процессоров, назначеьллчх на их решение, во время распределения текущей заявки. Устройство солержит группу регистров, регистр roTOBHOCTi-sрегистр потребности, блок управлеш-.я, блок назначения, элементы И, ИЛИ, элементы задержки. Устройство осуществляет прием кодов зл5:-:-от.г, содержащих код номера зггдачи ; кол числа потребных пття ее peuieHHH пропкссоров. Блок назначения за один тйкт работы производит назначение нг: поступившую заявку свобод нх процессоров. При отказах продессг Г Ов во вреь-я выполнения задач блок управления организует перезагрузку кодов задач, на которые они были назначены, в свободные процессоры. 1 з.п. ф-лы, Д i-m. OS

элемент И 41 закрыт по тре-ется О

входу, и на выходе 23 блока

13 находится нулевой потенциал, закрывающий элементь И 5 группы по вто-- рым входам. На выходах 24 и 25 блока управления в исходном состоянии такb Ь Л а;

с с V (а Л Ь);;

(2) (3) (4)

где а и а соответственно сигналы на. ггервом, выходе 59 и выходе 63 узла

51462314

58, b и b - на втором выходе 60 и выходе 64, с и с - ня третьем выходе

61 и выходе 65, d и d - на четвертом выходе 62 и выходе 66 узла 58,

На выход 59 каждого узла граничной верхней строки матрицы через соответствующий вход группы входов 27 блока 12 назначения подается содержимое соответствующего разряда регистра 3 потребности. На выход 60 (на выход 62) каждого узла граничного левого столбца матрицы через соответствующий вход группы входов 28 (29) блока 12 назначения.подается сигнал с прямого (инверсного) выхода соответствующего разряда регистра 4 готовности. На выход 61 всех узлв граничного левого столбца подается с входа 57 блока 12 назначения нулевая граничная константа ().

В случае, если на выходе 59 какого-либо узла граничной верхней строки присутствует нулевой сиг.нал (а 0), во всех узлах соответствующего данному узлу столбца в соответствии с (2)-(4):

b b; с с; d d.

При появлении позиционного кода числа потребных процессоров в регистр 3 единичный сигнал с первого слева единичного разряда распространяется вниз по соответствующему стрлбцу до ого узла, в котором (, ). На выходах этого узла в сответствии с (1)-(4) формируются сигналы d 1, d 0. В оследую1 95Х узлах данного столбца (расположенных ниже) сигнал в вертиальном канале в соответствии с (I) змениться не может, и с выхода 53 ижнего узла данного столбца нулеой сигнал () подается через сответствующий выход группы выходов 0 блока 12 назначения на.вход сответствующего разряда регистра 3 отребности, сигнализируя о том, что отребность в одном из заказных проессоров удовлетворена. В последую- их узлах данной строки,расположеных правее, сигналы в горизонтальных аналах в соответствии, с (2)-(4) акже измениться не могут. С выхода

пе по ны с со 12 Та чен 10 чи стр соо 3 вет 15 нал дан чен обр ост 20 сор сво

поз про 25 эле сиг бло ход пер .30 мен мен зад вых ся 35 Вре выб поя пос сор 40 на хот нул есл 45 цес цес вто про рег 50 чис ных

ИЛИ нул

65 правого узла данной строки единич- 55 НЕ 52 при этом появляется единичный ный снгнал подается через соответст-сигнал, которьй поступает на выход

вующий выход группы выходов 32 блока 12 назначения на вход соответству17 устройства, сигнализируя планиру ющей системе о том, что устройство закончило распре.деление текущей заяв

ющего блока элементов И В, разрешая

передачу кода номера задачи для исполнения в свободный процессор (данный процессор был свободен, так как с регистра 4 готовности в новый узел соответствующей строки матрицы блока 12 назначения подавался сигнал ). Таким образом, осуществляется назначение процессора на выполнение зада- 10 чи. С выхода 64 правого узла данной строки нулевой сигнал подается через соответствующий выход группы выходов 3 блока 12 назначения на вход соответствующего разряда регистра 4, сиг- 15 нализируя о том, что соответствующий данному разряду процессор ухе назначен ка- выполнение задачи. Аналогичным образом осуществляется назначение оставшегося числа заказанных процес- 0 соров при наличии достаточного числа свободньЕх процессоров.

Одновременно с появлением единиц позиционного кода числа потребных процессоров в регистре 3, на выходе 5 элемента ИЛИ 9 появляется единичный сигнал, который подается на вход 22 блока 13 управления. Этот сигнап проходит через открытый элемент И 36 на первый вход элемента И 42 и через эле- 0 мент 55 задержки на второй вход элемента И 42. С выхода элемента И 42 задержанный единичный сигнал через выход 25 блока 13 управления подается на тактовый вход регистров 3 и 4. 5 Время задержки элемента 55 задержки выбирается таким, чтобы этот сигнал появлялся на входах регистров 3 и 4 после завершения переходных процессоров в блоке 12 назначения. 0 С поступлением единичного сигнала на тактовые входы регистров 3 и 4 хотя бы один из них сбрасывается в нулевое состояние в первом случае, если число потребных для решения про- 5 цессоров меньше числа свободных процессоров, обнуляется регистр 3, во втором случае, если число потребных процессоров больше числа свободных, регистр 4, в третьем случае, если 0 число потребных равно числу свободных - регистр 3 и.регистр 4.

В первом случае с выхода элемента ИЛИ 9 на вход 22 блока 13 поступает нулевой сигнал, на выходе элемента

17 устройства, сигнализируя планирующей системе о том, что устройство закончило распре.деление текущей заяв714

ки и готово к приему следующей. Полу чив этот сигнал, планирующая система выдает на входы 1 устройства код еле дующей заявки, а в случае отсутствия в данный момент заявок, выставляет на входах 1 заявок нулевой код. При отсутствии отказов процессоров (на выходе элемента НЕ 53 присутствует единичный потенциал) единичный сигнал с вьЕХОда элемента ИЛИ 46 проходит через открытые элементы И 37, И 40 и элемент ИЛИ 48 на второй вх.од элемента И 41, При отсутствии новых заявок нулевой сигнал с выхода элемен- та ИЛИ 49 удерживает элемент И 41 в закрытом состоянии и на выходе 23 блока 13 сохраняется нулевой потенциал, устройство переходит в режим ожидания новых заявок. Если плани- рующая система выставила на вход 1 код новой заявки, элемент И 41 открывается и с выхода 23 блока 13 единичный сигнал поступает на вторые входы элементов И 5 группы. При этом открываются те элементы И 5 группы, на первые входы которых поступают единичные сигналы с выходов регистра 4, и разрешают запись в соответствующие свободным процессорам регистры 2 кода новой заявки. Единичные- сигналы с выходов элементов И 5, задержанные соответствующими элементами 14 задержки групш на время, достаточное для завершения переходных процессов в регистрах 2, открывают соответствующие блок элементов И 7, по первому входу (на второй вход этих блоков поступает единичи,й сиг- tat ал с выхода 17 блока 13 управления), разрешая запись в регистр 3 кода числа процессоров, потребных для решения данной задачи. Назначение процессоров на эту задачу производится аналогично рассмотренному,

Во втором случае нулевой потенциал с выхода элемента ИЛИ 46 закрывает элемент И .36, 37 и 39. Единичньй сигнал с выхода элемента ИЛИ 9 подается н-а вход 22 блока 13. На выходах 17, 23, 24 и 25 и группе выходов 26 блока 13 управления присутствуют нулевые потенциалы. Устройство переходит в режим ожидания- свободных процессоров. При освобождении хотя бы одног о процессора на выходе элемента ИЛИ 46 ri на выходах группы н 1ходов 26 блока 13, соответствующих освободившимся процессорам, появляется единич-

148

ный потенциал, так как при отсутствии отказов на выходе элемента НЕ 53 присутствует единичный потенциал. При этом открывается элемент И 39, и передним фронтом единичного сигнала с его выхода, поступающим на тактовый вход триггера 35, триггер 35 переводится в единичное состояние, так как на его информационном входе единичный потенциал. Единичный сигнал с единичного выхода триггера 35, длительность которого определяется элементом 55 задержки, поступает через элемент ИЛИ 48 на второй вход элемента И 41. На его первый вход поступает единичный потенциал с выхода элемента ИЛИ 49,- на вход которого поступает код заявки, распределение которой еще не закончено, так как единичный сигнал на выходе 17 блока 13 не вырабатывался. Сигнал с выхода 23 блока 13 поступает на элементы И 5 группы, организуя запись в регистрах 2, соответствующих освободив1чимся процессорам кода заявки. Код числа потребных процессоров из этих регистров в регистр 3 не переписывается, так как блоки элементов И 7 остаются закрытыми нулевым потенциалом, поступающим с выхода элмента НЕ 52. Дона- значение процессоров на данную задачу производится аналогично описанному.

Если в ходе решения задачи откажет какой-либо из назначенных процессоров, на соответствующем входе группы входов 21 блока 13 появляется единичный потенциал, который поступает на первьй вход соответствующего эле- мента И 45 группы; На второй вход этого элемента с соответствующего выхода группы инверсных выходов регистра 34 первоначально также поступает единичный потенциал,. С выхода этого элемента единичный сигнал поступает на информационный вход соответствующего разряда регистра 33. С входа группы входов 21 единичный сигнал одновременно поступает через элемент ИЛИ 50 и элемент 56 задержки на тактовый вход регистра 33. Таким обра- зом, в регистр 33 заносится информация об отказавг шх процессорах. С появле- нием единичного значения хотя бы в одном разряде регистра 33 на выходе элемента ИЛИ 47 появляется единичный потенциал, а на выходе элемента НЕ 53 - нулевой потенциал, котор-щ за10

15

20

25

91462314

крывает элементы И 40 и элементы И 43 первой группы. В момент окончания распределения текущей заявки на выходе элемента НЕ 58 появляется единичный сигнал, который при наличии свободных процессоров проходит через элементы И 37 и 38 на выход 24 блока 13. Одновременно единичный сигнал с выхода элемента НЕ 53 поступает на первый вход каждого элемента И 44 группы. При этом открывается только один элемент И 44, соответствующий единичному разряду регистра 33, с минимальным номером, поскольку нулевой потецниал с его инверсного выхода закрывает элементы И 44, соответст-г-- вующие разрядам с большим номером. Единичный сигнал с выхода элемента . И 44 устанавливает соответствующий разряд регистра 34 и через элемент ИЛИ 51 группы поступает на соответствующий выход группы выходов 26 блока 13, открывая соответствующий отказавшему процессору блок элементов И 6 группы. Единичный сигнал с выхода 24 блока 13 через первый элемент ИЛИ 11 группы записывает единицу в первый разряд регистра 3. После этого аналогично изложенному осуществляется назначение свободного процессора на задачу, кторую выполнял отказавщий процессор. Единичный сигнал с выхода элемента И 38 уерез

элемент ИЛИ 50 и элемент 56 задержки поступает также на вход синхронизаии триггеров регистра 33. Так как элемент И 45, соответствующий отказавшему процессору, переназначение которого, уже состоялось (в соответствующем разряде регистра 33 записана 1), закрыт нулевым сигналом с инверсного выхода соответствующего разряда регистра 34, соответствующий азряд регистра 33 обнуляется. Если меются еще необработанные отказы (имеются единичные разряды в регистре 33) процедура переназначения повторяется до тех пор, пока не будут бработаны все имеющиеся отказы.

олько после этого устройство перейет к приему следующей новой заявки т планирующей системы. С восстановением отказавщего процессора на сответствующий вход группы сигнальных ходов 15 устройства подается едиичный сигнал, который сбрасьшает в О соответствующий разряд регистра 4 (подача единичного потенциала с

вы вх ро ся вы по пе ро ст

Ф

30

за гр ти ру И, пы со эл эл ты и ин пы вх щи со ме до на бл 3g ра гру одн гру эле 40 с г та каж гру одн 45 пы пы го пы, соо рой с в вым упр вхо 55 пой гот мых дин

50

эле

4

10

выхода отказавшего процессора на вход группьт сигнальных входов 21 устройства к этому моменту прекращается), единичный сигнал готовности с выхода восстановленного процессора поступает на соответствующий вход первой группы сигнальных входов устройства, устанавливая в 1 соответствующий разряд регистра 4.

Формула изобретения

15

0

5

0

0

элемента И группы, с соответствующим

входом первого элемента ИЛИ и с первым входом одноименного элемента И первой группы блока управления, выход второго элемента И блока управ- ления соединен с вторыми входами элементов И группы, выход третьего эле- мента И блока управления соединен с (ВХОДОМ первого элемента ИЛИ второй группы, в блоке управления выход пер JBoro элемента ИЛИ соединен с вторым входом первого элемента И, выход пер вого элемента НЕ соединен с первыми |входами элементов И второй группы яблока управления, выход второго эле- |мента ИЛИ блока управления соединен 1с входом второго элемента НЕ и с (первым входом третьего элемента Rj в яблоке управления выход второго эле- 1мента НЕ соединен с вторым входом каждого элемента И первой группы, ;Выход которого соединен с первым входом одноименного элемента ИЛИ груп- пы, второй вход которого соединен с ;выходом одноименного элемента И второй группы,, а выход каждого элемента ИЛИ группы блока управления соединен с управляющим входом одноименного блока элементов И первой группы, отличающееся тем, что, с целью повышения надежности функгдио- нирования устройства за счет обслу- живания заявок при отказе двух и более процессоров, назначенных на их

решение, .во время распределения теку- 35 Р входом третьего элемента И и щей заявки, в устройство введены ре- первым входом шестого элемента И,

гистр потребности, г руппа элементов задержки, блок назначения, содержащий К групп узлов назначения (К - количество выходов грегистра потребности) , а в блок управления введены регистр отказов, регистр маски, триггер, четвертый, пятый, шестой и седьмой элементы И, третья группа элементов И, третий, четвертый; и пятый элементы ИЛИ, первый, второй и третий элементы задержки, причем каждый вход группы информационных входов регистра потребности соединен с выходом соответствующего элемента ИЛИ второй группы, каждый группы выходов регистра потребности соединен с соответствующим входом, элемента ИЛИ и с соответствующим входом первой группы входов блока назначения, вторая группа входов которого соединена с группой прямь1х выходов регистра готовности, третья группа входов бло

ка назначения соединена с группой инверсных выходов регистра готовности, первая группа выходов блока назначения соединена с группой установочных входов регистра потребности, каждый выход второй группы выходов блока назначения соединен с управляющим входом одноименного блока элементов И третьей группы, третья группа выходов блока назначения соединена с группой установочных входов регистра готовности, управляющий вход которого соединен с управляющим входом

регистра потребности и с выходом четвертого элемента И блока управления, rpiynna входов третьего элемента ИШ которого соединена с группой входов заявок устройства, первый управляющий вход каждого блока элементов И второй группы соединен с выходом одноименного элемента задержки группы, вход каждого из которых соединен с выходом одноименного элемента И группы, второй управляющий вход каждого блока элементов И второй группы соединен с выходом первого элемента НЕ блока управления, в блоке управления первый вход четвертого элемента И соединен с выхо(п;ом первого элемента И, второй вход четвертого элемента И соединен через первый элемент задержки с выходом первого элемента И, выход пятого элемента И соединен с

выход третьего элемента И соединен с первым входом четвертого элемента ИЛИ, первый вход пятого элемента ИЛИ

соединен с единичным выходом триггера и через второй элемент задержки - с входом сброса триггера, информационный вход которого соединен с первым входом первого элемента И блока управления, тактовый вход триггера соединен с выходом седьмого элемента И, группа входов четвертого элемента ИЛИ соединена с второй группой сигнальных входов устройства,

выход четвертого элемента ИЛИ соединен через третий элемент задержки с управляющим входом регистра отказов, входы которого соединены с выходами элементов И третьей группы, первый вход каждого элемента И третьей груп-. пы соединен с одноименным инверсным выходом регистра маски, второй вход каждого элемента И третьей группы соединен с одноименным входом второй

О

группы сигнальн1з1Х входов устройства, первый вход седьмого элемента И соединен с выходом первого элемента ИЛИ, с вторым входом первого элемента И и с первым входом пятого элемента И, вторые Bxopi-i шестого и седьмого элементов И соединены с выходом второго элемента НЕ, выход седьмого элемента И соединен с тактовым входом триггера, второй вход пятого элемента ИЛИ соединен с выходом шестого элемента И, выход пятого элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ, второй управляющий вход каждого блока элементов И второй группы соединен с выходом первого элемента НЕ блока

управления, с вторым входом пятого

30

элемента И блока управления и является выходом прерывания устройства, вход сброса каждого разряда регистра маски соединен с одноименным входом третьей группы сигнальных входов уст- 25 ройства, вход запуска которого соединен с вторым входом второго элемента И блока управления, единичный йход каждого разряда регистра маски соединен с выходом одноименного элемента И второй группы, прямой вход каждого разряда регистра отказав соединен с соответствующим входом одноименного элемента И второй группы, инверсный выход каждого разряда регистра отказов соединен с соответствующими входами всех последующих элементов И .второй группы, прямые выходы регистра отказов соединены с входами второго элемента ИЛИ, причем в блоке назначения первые входы узлов назначения первой группы соединены с входом логического нуля устройства, второй вход каждого i-ro узла назначения

пы входов блока назначения, первый, второй и третий выходь i-ro. узла назначения каждой группы, кроме последней, соедине:- ы соответственно с первым, вторым и третьим входами i-ro узла назначения следующей группы, четвертый вход первого узла назначения каждой группы соединен с одно - именным входом первой группы входов блока назначения, третьи выходы узлов назначения последней группы не используются, четвертый выход каждого узла назначения группы, кроме последнего узла группы, соединен с четвертым входом, саедующего узла назначения данной группы, четвертые выходы последних узлов назначения каждой группы являются группой выходов блока назначения, первые выходы узлов назначения последней группы являются третьей группой выходов блока назначения, вторые выходы уз-« лов назначения последней- iруппы являются второй группой выходов блока назначения.

35 узла, второй вход которого соединен с первыми входами первого и второго элементов ИЛИ, второй вход и выход первого элемента ИЛИ соединены соответственно с выходом первого элемента

40 И и с вторым выходом узла, третий вход которого является его третьим шгходом и соединен с вторым входом второго элемента ИЛИ, выход которого

соединен с первым входом второго эле- первой группы (...n, п - число уз- 45 мента И, второй вход которого соеди- лов назначения в группе) соединен с„ей с вторым входом первого элемента

1-ЫМ входом второй группы входов бло- и с инверсным входом элемента запре- ка назначения, третий вход каждогота и с четвертым входом узла, чет1-го узла назначения первой группывертый выход которого соединен с высоединен с i-ым входом третьей груп- 50 ходом второго элемента И.

5

10

2562314 -14

пы входов блока назначения, первый, второй и третий выходь i-ro. узла назначения каждой группы, кроме последней, соедине:- ы соответственно с первым, вторым и третьим входами i-ro узла назначения следующей группы, четвертый вход первого узла назначения каждой группы соединен с одно - именным входом первой группы входов блока назначения, третьи выходы узлов назначения последней группы не используются, четвертый выход каждого узла назначения группы, кроме последнего узла группы, соединен с четвертым входом, саедующего узла назначения данной группы, четвертые выходы последних узлов назначения каждой группы являются группой выходов блока назначения, первые выходы узлов назначения последней группы являются третьей группой выходов блока назначения, вторые выходы уз-« лов назначения последней- iруппы являются второй группой выходов блока назначения.

15

20

30

25

35 узла, второй вход которого соединен с первыми входами первого и второго элементов ИЛИ, второй вход и выход первого элемента ИЛИ соединены соответственно с выходом первого элемента

40 И и с вторым выходом узла, третий вход которого является его третьим шгходом и соединен с вторым входом второго элемента ИЛИ, выход которого

Фиа. 1

га

гз

Фиг г

..Oii

| Устройство для распределения заданий процессорам | 1977 |

|

SU629538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заявок по процессорам | 1983 |

|

SU1151965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-08-24—Подача