Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи и обработки информации, при построении цифровых фильтров и функциональных преобразований, в системах управления, а также при построении анализаторов и синтезаторов сигналов.

Известен генератор дискретных базисных функций, содержащий два счетчика, группу элементов И и группу сумматоров по модулю два, а также многовходовый сумматор по модулю два.

Недостатком известного генератора, как и других генераторов функций Уолша, генераторов функций Хаара являются узкие функциональные возможности, заключающиеся в том, что число базисных функций не может быть отличным от 2т (где го - натуральное число.

Кроме этого, указанные генераторы имеют бедный набор значений периодов ге

и сотыхвариов

ска, по аа, а, ие юнетурыгенерируемых функций и малое число значений базисных функций./

Известно также устройство для операций над матрицами, содержащее N2 операционных блоков, N-1 элементов задержки и распределитель импульсов.

Однако известное устройство осуществляет только решение систем линейных уравнений и обращение матриц. Это устройство обладает ограниченными функциональными возможностями, поскольку не может генерировать дискретные базисные функции.

Наиболее близким к предлагаемому по технической сущности является устройство для операций над матрицами, содержащее матрицу из Р х Р вычислителей (где Р - порядок квадратной матрицы) и группу из (Р-1) блоков деления, причем каждый вычислитель матрицы содержит сумматор и блок умножения, выход которого подключен к входу первого слагаемого сумматора того же вычислителя матрицы, вход задания чиссо

с

-ч ел

О) N

сь

;

i

левого компонента k-ro элемента М-й строки матрицы устройства (k 1,..., Р; М 1

Р) подключен к входу первого сомножителя блока умножения k-ro вычислителя М-й строки матрицы, выход сумматора k-ro вычислителя (k Ј Р) М-й строки матрицы подключен к входу второго слагаемого сумматора (k + 1)-го вычислителя М-й строки матрицы, выход сумматора Р-го вычислителя Р-го столбца матрицы является выходом србственного числа устройства и подключен к входу делителя всех блоков деления группы, выход сумматора М-го вычислителя (М Р) Р-го столбца матрицы подключен к входу делимого М-ro блока деления группы, выход которого подкл юн к входам вторых сомножителей блоков умножения всех вычислителей М-ro столбца матрицы и является выходом М-й компоненты собственного вектора числа устройства, входы вторых слагаемых сумматоров всех вычислителей первого столбца матрицы являются входами задания кода единицы устройства.

Однако известное устройство имеет узкую область применения, поскольку вычисляет только доминирующее собственное число и соответствующий ему один собственный вектор. Известное устройство не может вычислять все собственные векторы положительно определенной симметрической матрицы, что не позволяет использовать его в качестве генератора функций.

Целью изобретения является расширение области применения устройства путем генерирования дискретных базисных функций.

Поставленная цель достигается тем, что в устройство, содержащее матрицу вычислителей, первую группу блоков деления и блок синхронизации, причем входы задания начального приближения группы тенерато- ра соединены с первыми информационными входами соответствующих вычислителей первой строки матрицы, первый вход вычислителя i-й (I 1-P-1, Р - порядок квадратной матрицы коэффициентов) строки матрицы соединен с первым информационным входом соответствующего вычислителя (1 + 1)-й строки матрицы, второй выход вычислителя 1-го столбца матрицы соединен с вторым информационным входом соответствующего вычислителя (i + 1)-го столбца матрицы, вторые информационные входы вычислителей первого столбца матрицы соединены с входом логического нуля генератора, вход запуска которого соединен с входом блока синхронизации, введены регистр сдвига, с первой по (Р-1)-ю группы блоков элементов И, с второй по (п-1)-ю группы блоков деления, первый и второй блоки памяти, матрицу операционных блоков, с первого по (п-2)- й элементы задержки и кольцевой регистр сдвига, причем второй выход вычислителя (i + 1)-й строки (I + 1)-го столбца матрицы соединен с входами делителя блоков деления (Р-1)-й группы, вход делимого j-ro блока деления (j 1-P-1) 1-й группы соединен с вторым входом вычислителя J-й строки (P-i + 1)-го столбца матрицы, выход j-ro блока де0 ления 1-й группы соединен с первым входом j-ro блока элементов И 1-й группы, вторые входы блоков элементов И 1-й группы соединены с выходом 1-го разряда регистра сдвига, выходы блока синхронизации соединены

5 соответственно с тактовыми входами операционных блоков матрицы, с тактовыми входами с первого по (Р-2)-й элементов задержки, с входом разрешения сдвига регистра сдвига, с входами разрешения запи0 си первого блока памяти, с входами разрешения записи второго блока памяти, с тактовыми входами первого и второго блоков памяти, с входами разрешения считывания первого и второго блоков памяти и

5 входом разрешения сдвига кольцевого регистра сдвига, выходы j-x блоков элементов И с первой по (Р-1)-ю групп соединены с первым информационным входом вычислителя (J + 1)-й строки j-ro столбца матрицы,

0 выходы вычислителей последней строки матрицы соединены с соответствующими информационными входами второго блока памяти, первый информационный вход операционного блока 1-й строки первого столб5 ца матрицы соединен с i-м выходом второго блока памяти, первые выходы операционных блоков 1-й строки S-x (S I-P-1) столбцов матрицы соединены с (P-i + 1)-м информационным входом группы второго

0 блока памяти, первый информационный вход операционного блока k-й (k 1-P-2) строки М-го (М 2-Р-1) столбца матрицы соединен с первым выходом операционного блока (k + 1)-й строки (М-1)-го столбца мат5 рицы, первый информационный вход операционного блока (Р-2)-й строки М-го столбца матрицы подключен к выходу М-го элемента задержки, информационный вход которого подключен к второму выходу опе0 рационного блока (Р-1)-й строки (М-1)-го столбца матрицы, второй информационный вход операционного блока М-й строки i-ro столбца матрицы подключен к второму выходу операционного блока (М-1)-й строки

5 1-го столбца матрицы, входы значения компонент исходной матрицы группы генератора соединены соответственно с информационными входами группы первого блока памяти, выходы которого соедине- ны С третьими информационными входами

вычислителей соответствующих строк матрицы, k-й выход второго блока памяти соединен с k-м дополнительным информационным входом группы первого блока памяти, выходы разрядов кольцевого регистра сдвига соединены с соответствующими входами разрешения считывания второго блока памяти, выходы которого являются выходами группы генератора.

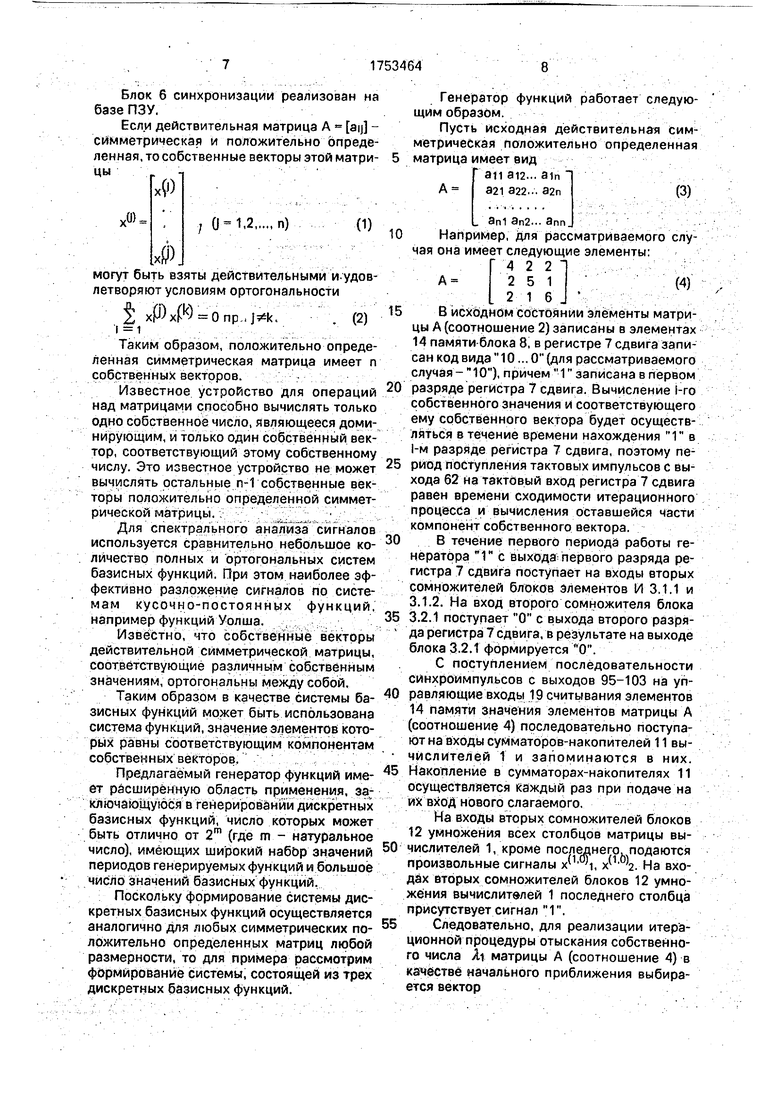

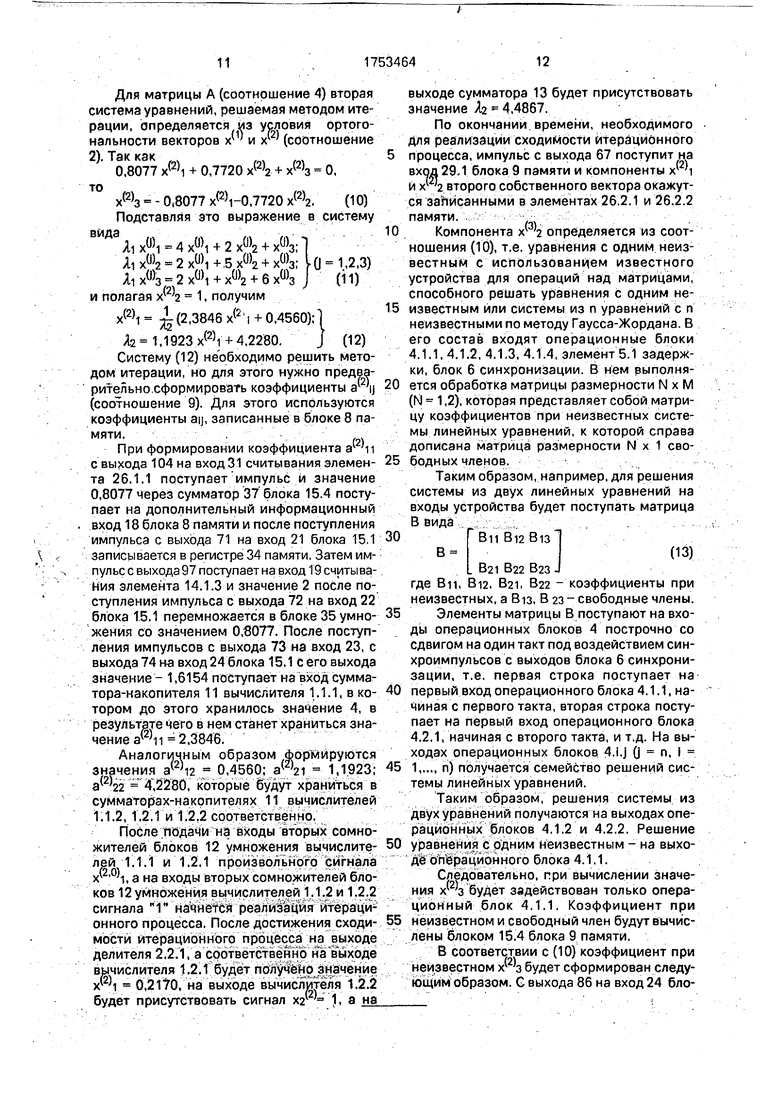

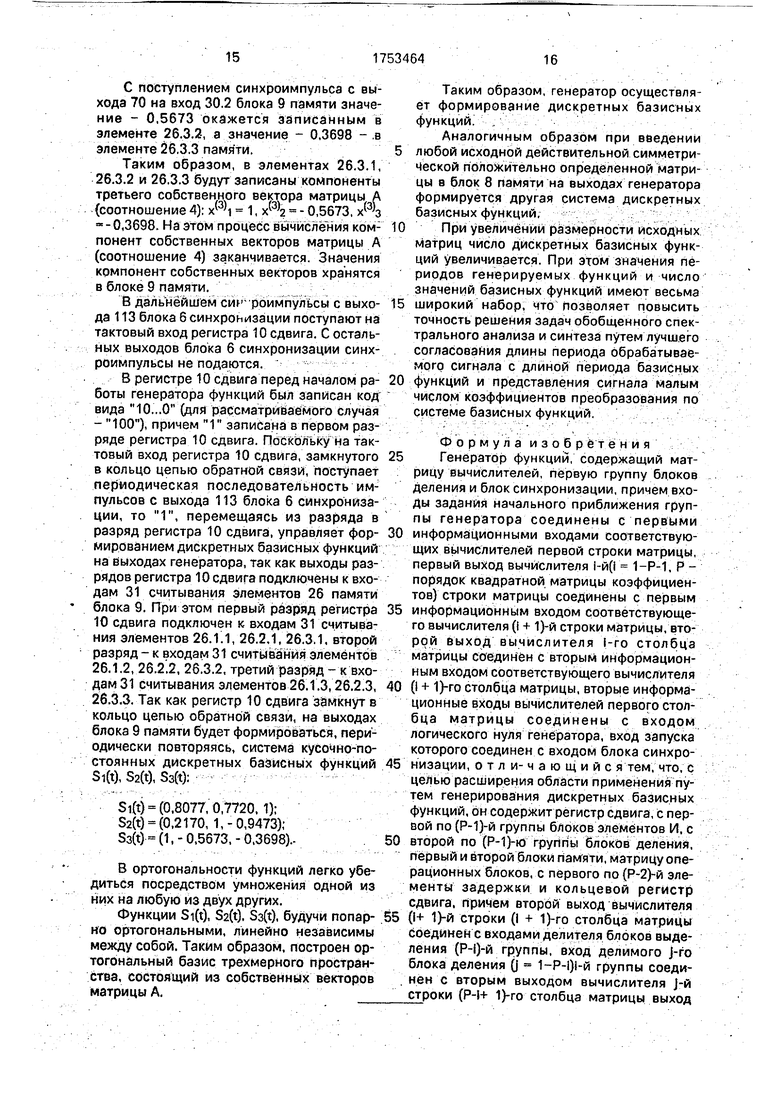

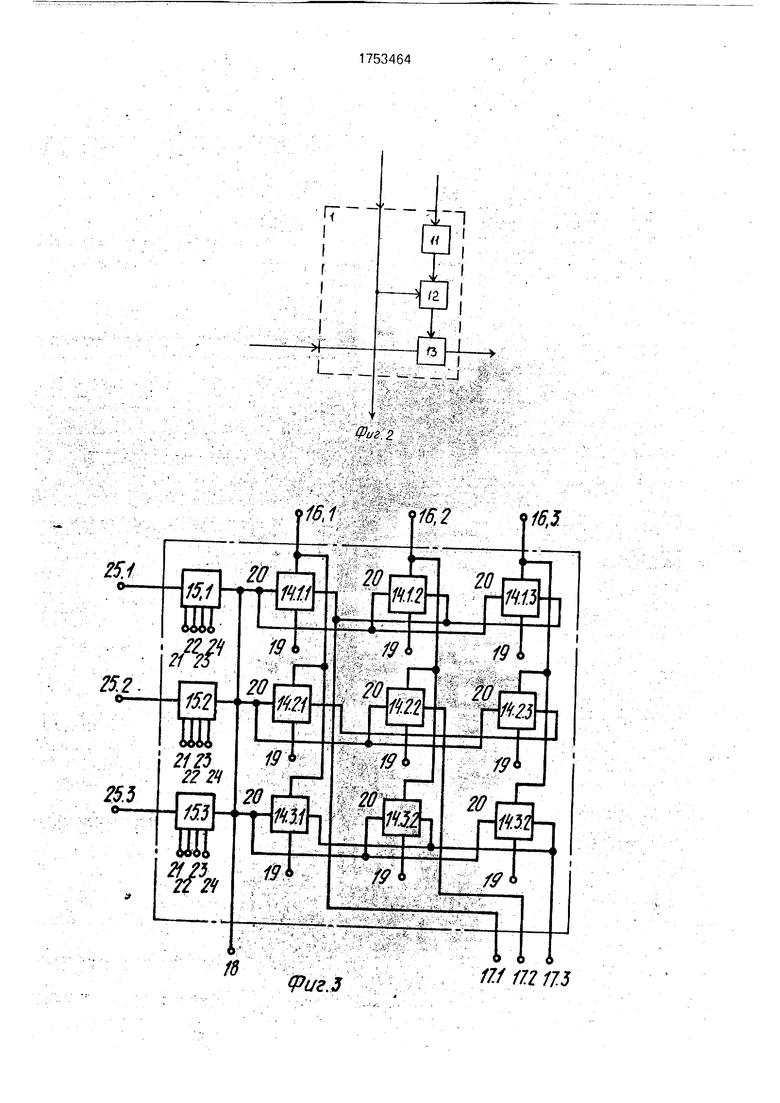

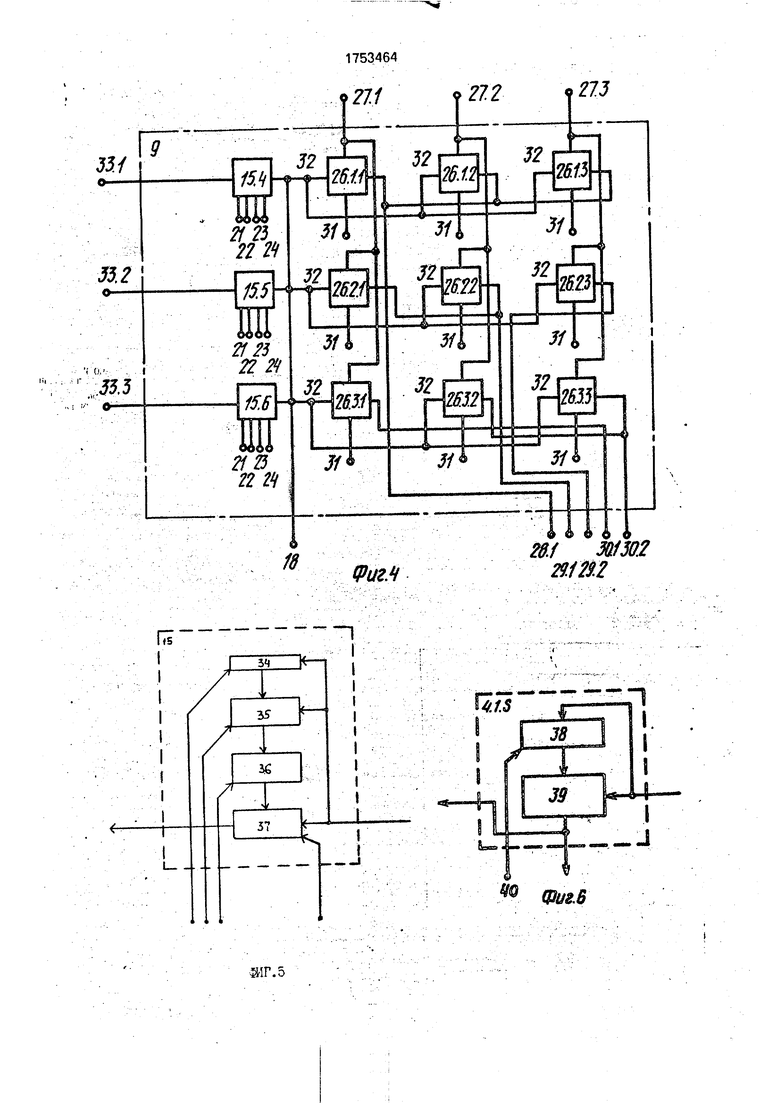

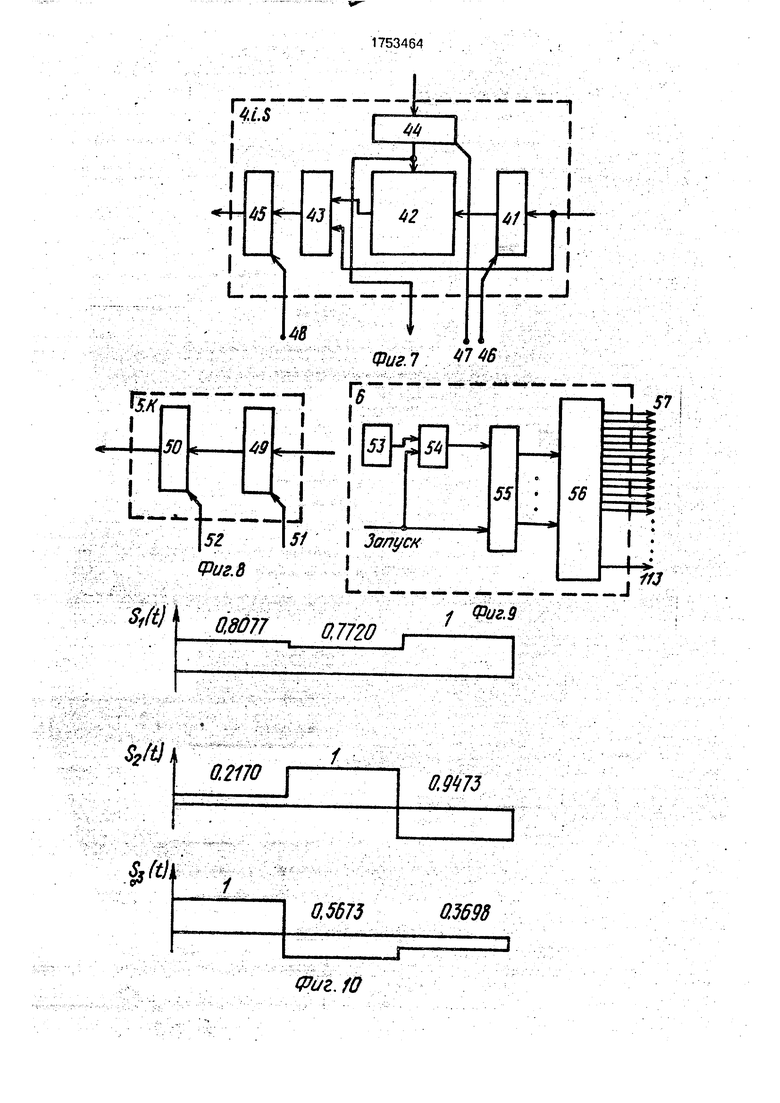

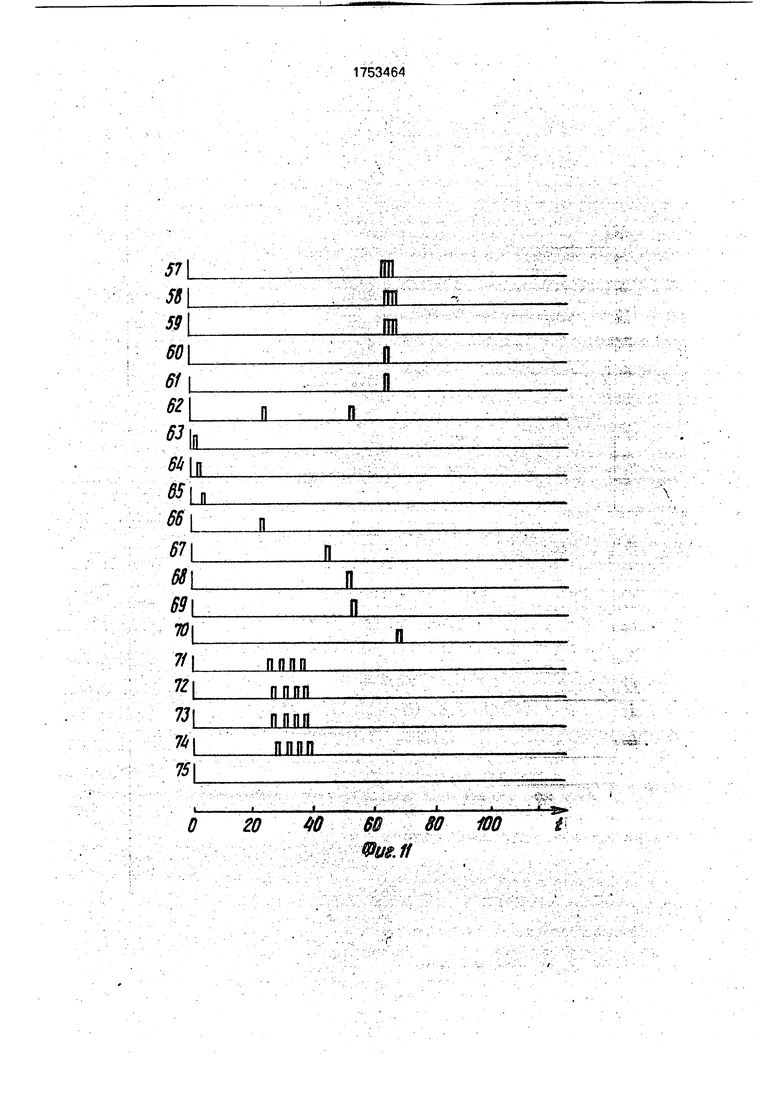

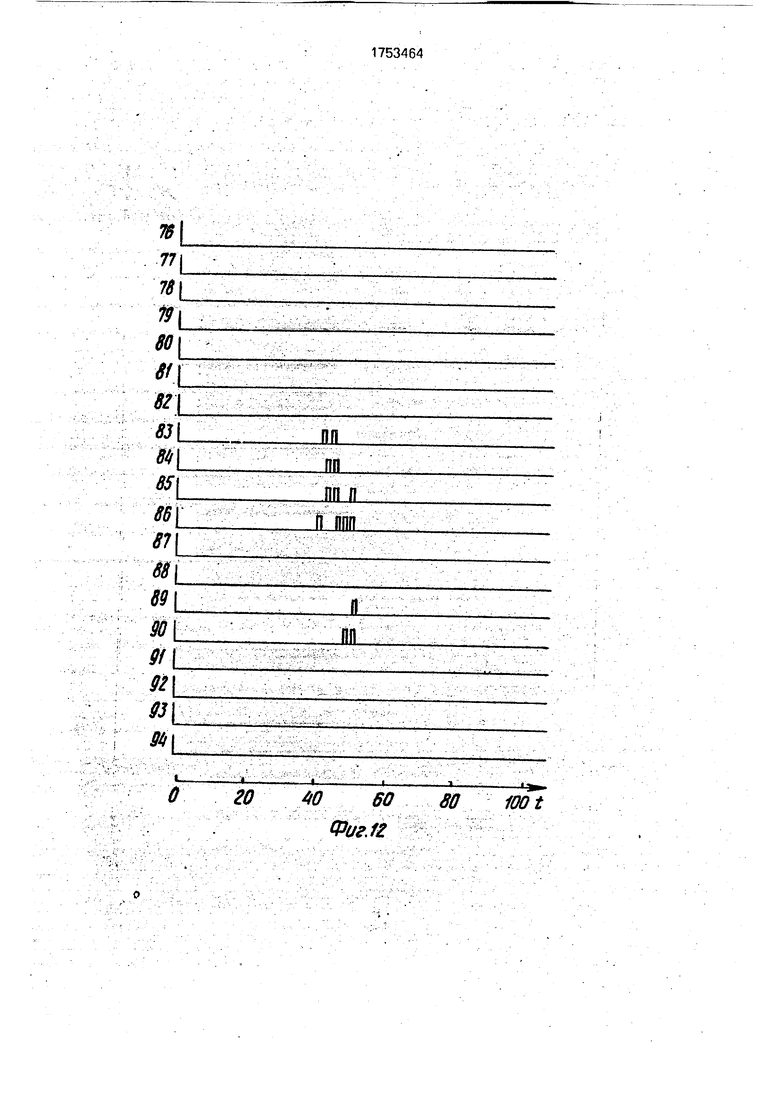

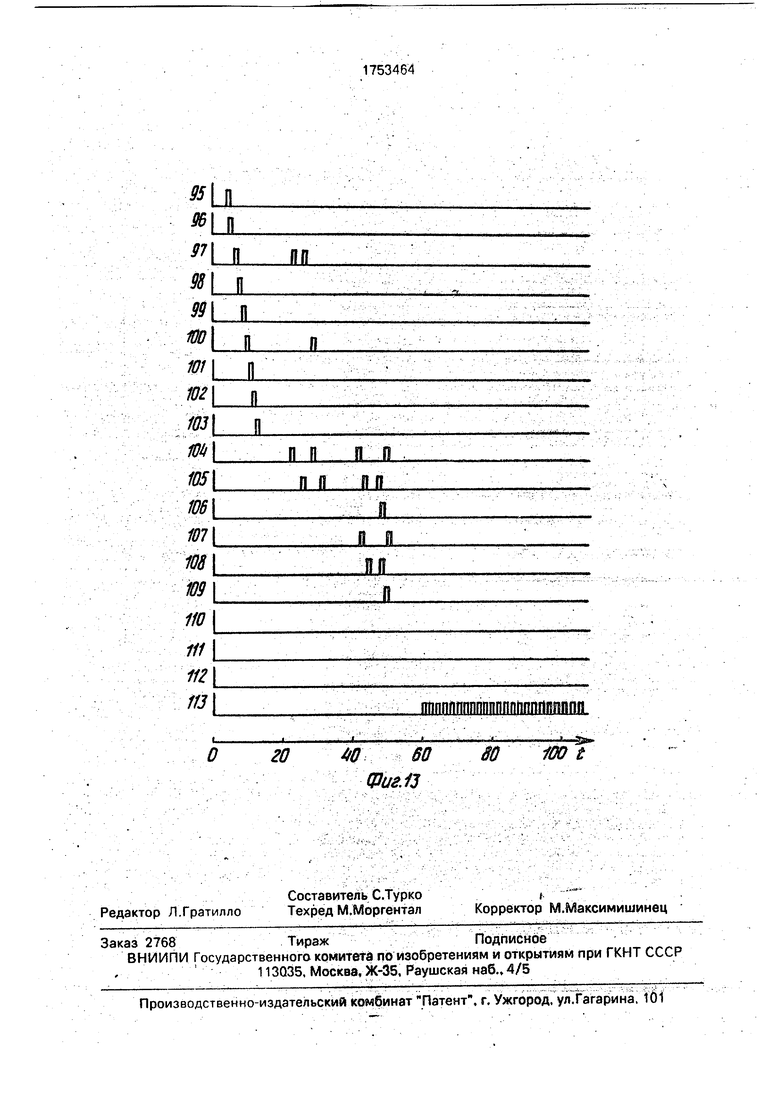

На фиг. 1 представлена функциональная схема предлагаемого генератора функций, формирующего 3 дискретные базисные функции; на фиг. 2 - функциональная схема вычислителя; на фиг. 3 - функциональная схема блока памяти; на фиг. 4 - функциональная схема блока памяти; на фиг. 5 - функциональная схема блока формирования коэффициентов системы линейных уровнений; на фиг. 6 - функциональная схема операционного блока; на фиг, 7 - функциональная схема операционного блока; на фиг. 8 - функциональная схема элемента задержки; на фиг. 9 - функциональная схема блока синхронизации; на фиг. 10 - временные диаграммы дискретных базисных функций для рассматриваемого случая; на фиг. 11-13- временные диаграммы изменения сигналов на выходах блока памяти микрокоманд.

Генератор функций содержит вычислители 1, блоки 2 деления, блоки элементов И 3, операционные блоки 4, элемент 5 задержки, блок 6 синхронизации, регистр 7 сдвига, блок 8 памяти, блок 9 памяти и регистр 10 сдвига.

Вычислитель 1 содержит сумматор-накопитель 1,1, блок 12 умножения, сумматор 13.

Блок 8 памяти содержит элементы 14 памяти, блоки 15 формирования коэффициентов системы линейных уравнений, информационные входы 16, шины 17 управления записью соответствующих строк, дополнительный информационный вход 18, входы 19 управления считыванием, информационные выходы 20 элементов 14 памяти, информационные выходы 25 блока 8 памяти.

Блок 9 памяти содержит элементы. 26 памяти, блоки 15 формирования коэффициентов системы линейных уравнений, информационные входы 27, шины 28-30 управления записью соответствующих строк, входы 31 управления считыванием; информационные выходы 32 элементов 26 памяти, информационные выходы 33 блока 9 памяти,

Блок 15 формирования коэффициентов системы линейных уравнений содержит регистр 34 памяти, блок 35 умножения, управляемый инвертор 36, сумматор-накопитель

37, синхровходы 21-24. У блока 15 формирования коэффициентов синхровход 21 - вход разрешения записи регистра 34 памяти, синхровход 22 - вход разрешения работы

блока 35 умножения, синхровход 23 - вход управления инвертированием входного сигнала управляемого инвертора 36, синхровход 24 - вход разрешения работы сумматора-накопителя 37.

Операционный блок4.1.5(фиг. 6) содержит входной регистр 38, блок 39 деления, синхровход 40. V операционных блоков 4.1.S синхровход 40 - вход разрешения записи входного регистра 38.

Операционный блок 4.I.S (фиг. 7) содержит регистр 41 первого сомножителя, умножитель 42, вычитатель 43, регистр 44 второго сомножителя, выходной регистр 45, синхровходы 46-48. У операционных блоков

4.I.S синхровход 46 - вход разрешения записи регистра 41 первого сомножителя, синхровход 7 - вход разрешения записи регистра 44 второго сомножителя, синхровход 48- вход разрешения записи выходного

регистра 45.

Элемент 5 задержки содержит регистры 49 и 50, синхровходы 51 и 52.

Блок 6 синхронизации содержит генератор 53 синхроимпульсов, элемент И 54,

счетчик 55 тактов, блок 56 памяти микрокоманд, выходы 57-113 распределителя.

Выход 57 подключен к управляющему входу 40 блока 4.1.1, выход 58 - к управляющему входу 46 блока 4.2.1, выход 59 - к

входу 40 блока 4.1.2, выход 60 - к входу 46 блока 4.2.2, выход 61 - к управляющим входам 47 блоков 4.2.1, 4.2,2, к управляющим входам 48 блоков 4.2.1, 4.2.2, к синхровходу 51 и синхровходу 52 блока 5.1 задержки,

выход 62 - к тактовому входу регистра 7 сдвига, выход 63 - к управляющей шине

17.1,выход 64 - к управляющей шине 17.2, выход 65-к управляющей шине 17,3, выход 66- к управляющей шине 28.1, выход 67 - к

управляющей шине 29.1, выход 68 - к шине

29.2,выход 69 - к шине 30.1, выход 70 - к шине 30.2, выходы 71-74 - к управляющим входам блока 15.1; выходы 75-78 - к управляющим входам блока 15.2; выходы 79-82 к управляющим входам блока 15.3; выходы 83-86 - к управляющим входам блока 15.4; Выходы 87-90 - к управляющим входам блока 15.5; выходы 91-94 - к управляющим вхо- дам блока 15.6; выходы 95-103 - к

управляющим входам 19 считывания элементов 14 памяти, выходы 104-112 к управляющим входам 31 считывания элементов 26 памяти; выход 113 - к тактовому входу регистра 10 сдвига.

Блок 6 синхронизации реализован на базе ПЗУ.

Если действительная матрица А aij - симметрическая и положительно определенная, то собственные векторы этой матрицы

(0

Генератор функций работает следующим образом.

Пусть исходная действительная симметрическая положительно определенная матрица имеет вид

an ai2... ain

321 322... 32п

А

(3)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| ГЕНЕРАТОР СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ | 2016 |

|

RU2615322C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ | 2021 |

|

RU2773107C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ НА ОСНОВЕ ХАОТИЧЕСКИ ФОРМИРУЕМЫХ АНСАМБЛЕЙ ДИСКРЕТНЫХ МНОГОУРОВНЕВЫХ ОРТОГОНАЛЬНЫХ СИГНАЛОВ | 2010 |

|

RU2428795C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ С ПРИМЕНЕНИЕМ СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ | 2021 |

|

RU2780418C1 |

| СИСТЕМА НЕПРЕРЫВНОЙ ПЕРЕДАЧИ ИНФОРМАЦИИ АНСАМБЛЯМИ СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ | 2022 |

|

RU2801172C1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Цифровой интегратор | 1988 |

|

SU1580359A1 |

| Цифровой функциональный генератор | 1989 |

|

SU1686427A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах передачи и обработки информации, при построении цифровых фильтров и функциональных преобразователей, в системах управления, а также при построении анализаторов и синтезаторов сигнапов. Целью изобретения является расширение области применения за счет генерирования дискретных базисных функций. Генератор функций содержит матрицу вычислителей, группы блоков деления, группы блоков элементов И, матрицу операционных блоков, элементы задержки, блок синхронизации, регистр сдвига, блоки памяти и кольцевой регистр сдвига. 13 ил.

Л).

7 0 1-2п)

WP

могут быть взяты действительными и-удов- летворяют условиям ортогональности

5 хР х(К) о пр 1

(2)

Таким образом, положительно определенная симметрическая матрица имеет п собственных векторов.

Известное устройство для операций над матрицами способно вычислять только одно собственное число, являющееся доминирующим, и только один собственный вектор, соответствующий этому собственному числу. Это известное устройство не может вычислять остальные п-1 собственные векторы положительно определенной симметрической матрицы.

Для спектрального анализа сигналов используется сравнительно небольшое количество полных и ортогональных систем базисных функций. При этом наиболее эффективно разложение сигналов по системам кусочно-постоянных функций, например функций Уолша.

Известно, что собственные векторы действительной симметрической матрицы, соответствующие различным собственным значениям, ортогональны между собой.

Таким образом в качестве системы базисных функций может быть использована система функций, значение элементов которых равны соответствующим компонентам собственных векторов.

Предлагаемый генератор функций имеет расширенную область применения, за; ключающуюся в генерировании дискретных базисных функций, число которых может быть отлично от 2т (где т - натуральное число), имеющих широкий набор значений периодов генерируемых функций и большое число значений базисных функций.

Поскольку формирование системы дискретных базисных функций осуществляется аналогично для любых симметрических положительно определенных матриц любой размерности, то для примера рассмотрим формирование системы, состоящей из трех дискретных базисных функций.

10

15

20

25

30

35

40

45

50

55

. Эп1 Эп2... Эпп.

Например, для рассматриваемого случая она имеет следующие элементы: 422

А 251 (4)

I 2 1 6 J

В исходном состоянии элементы матрицы А (соотношение 2) записаны в элементах 14 памяти-блока 8, в регистре 7 сдвига записан код вида 10... О (для рассматриваемого случая - 10), причем 1 записана в первом разряде регистра 7 сдвига. Вычисление 1-го собственного значения и соответствующего ему собственного вектора будет осуществляться в течение времени нахождения 1 в 1-м разряде регистра 7 сдвига, поэтому период поступления тактовых импульсов с выхода 62 на тактовый вход регистра 7 сдвига равен времени сходимости итерационного процесса и вычисления оставшейся части компонент собственного вектора.

В течение первого периода работы генератора 1 с выхода первого разряда регистра 7 сдвига поступает на входы вторых сомножителей блоков элементов И 3.1.1 и 3.1.2. На вход второго сомножителя блока 3.2.1 поступает О с выхода второго разряда регистра 7 сдвига, в результате на выходе блока 3.2.1 формируется О.

С поступлением последовательности синхроимпульсов с выходов 95-103 на управляющие входы 19 считывания элементов 14 памяти значения элементов матрицы А (соотношение 4) последовательно поступают на входы сумматоров-накопителей 11 вы- числителей 1 и запоминаются в них. Накопление в сумматорах-накопителях 11 осуществляется каждый раз при подаче на их вход нового слагаемого.

На входы вторых сомножителей блоков 12 умножения всех столбцов матрицы вычислителей 1, кроме последнего, подаются произвольные сигналы . На входах вторых сомножителей блоков 12 умножения вычислителей 1 последнего столбца присутствует сигнал 1.

Следовательно, для реализации итерационной процедуры отыскания собственного числа AI матрицы А (соотношение 4) в качестве начального приближения выбирается вектор

.Л 1).

На выходе сумматора t3 последнего вычислителя 1 последней строки матрицы при этом образуется сигнал

A()JЈ anj + ann,(5)

1 1

который является первым приближением собственного числа AI .

На выходе сумматора 13 последнего вычислителя 1 1-й строки (I 1,..., п-1) образу- ется сигнал

„ОДп -1

1 1

aij xao)j + am,

(где 1 1, 2п-1). Этот сигнал является l-м

компонентом первого ненормированного приближения первого собственного вектора матрицы А (соотношение 4) Х(1,1),(Х(1.1)1)Х(1.1)2 я(1)}

Нормирование первого приближения первого вектора осуществляется путем деления всех его компонентов на величину

последнего компонента AV . Так как в результате нормирования последняя компо- нента равна 1, то ее деление не производится и 1 поступает на входы вторых сомножителей всех блоков 12 умножения последнего столбца матрицы вычислителей 1. Нормирование остальных компонент осуществляется при помощи блоков 2.1.1 и 2.1.2 путем деления компонент на величину последней компоненты

AW . Сигнал с выхода блока 2.1.1 деления через блок 3.1.1 поступает на входы вторых сомножителей блоков 12 умножения вычислителей 1.2.1 и 1.3.1, т.е. вычислителей 1 первого столбца матрицы. Сигнал с выхода блока 2.1.2 деления через блок 3.1.2 поступает на вход второго сомножителя блока 12 умножения вычислителя 1.3.2, т.е. вычислителя 1 второго столбца матрицы.

Таким образом, в соответствии с соотношением

хР 1)Т7П(Ё1аихР +а,„)(7)

A1j 1

где Г 1,2п-1) после окончания первой

итерации на выходах вычислителей 1.3.1, 1 3.2, 1.3 3 присутствуют сигналы, соответствующие компонентам первого нормированного приближения первого собственного вектора

Х Чх0 1 ).

Затем итерационный процесс повторяется и после окончания второй итерации на выходах вычислителей 1.3.1,1.3.2,1.3.3 присутствуют сигналы, соответствующие компонентам второго нормированного

J5

20

«с«Q

35 4045

зд

55

(8)

приближения первого собственного вектора

Х(1.2) (Х(1,2)1Х2(12)ИЬ

Повторение итераций будет осуществляться до полной сходимости итерационного процесса. В результате на выходах вычислителей 1.3.1, 1.3.2, 1.3.3 присутствуют сигналы, соответствующие компонентам нормированного первого собственного вектора

,

а на выходе сумматора 13 вычислителя 133 присутствует сигнал, соответствующий собственному значению AI .

Таким образом, для матрицы А (соотношение 4) система уравнений, решаемая методом итерации, в соответствии с соотношениями (5( и (7) следующая:

х(1);1т(4х(1)+2х)+2) .(2х(0+ + 1);

(1)+xЈ1) + 6.

После реализации сходимости итерационного процесса на выходах вычислителей 1.3.1, 1.3.2, 1 3.3 будут получены значения компонент первого собственного вектора х(1)1 0,8077, х(1)2 0,7720, х(1)з 1, а на выходе сумматора 13 вычислителя 1.3.3 будет получено значение AI 8,3874

По окончании времени, необходимого для реализации сходимости итерационного процесса, импульс с выхода 66 поступит на вход 28.1 блока 9 памяти и компоненты первого собственного вектора окажутся записанными в элементах 26.1.1, 26.1.2, 26.1 3 памяти. В следующий момент времени на тактовый вход регистра 7 сдвига поступает тактовый импульс с выхода 62, под воздействием которого 1 из первого разряда регистра 7 сдвига сдвигается во второй разряд. .

Таким образом, 1 с выхода второго разряда регистра 7 сдвига поступает на вход второго сомножителя блока 3.2.1 умножения. На входы вторых сомножителей блоков 3.1.1 и 3.1.2 умножения поступает 0м с выхода первого разряда регистра 7 сдвига, в результате на выходах блоков 3.1 1 и 3.1 2 формируется О.

Для определения второго собственного значения и компонент , второго собственного вектора необходимо методом итерации решить систему уравнений

, Е аЯихр, J 1)

(9)

Для матрицы А (соотношение 4) вторая система уравнений, решаемая методом итерации, определяется из условия ортогональности векторов и (соотношение 2). Так как

0.8077 х(2)1 + 0,7720 х(2)2 + х(2)з - О,

то

х(2)з - - 0,8077 х(2)1-0,7720 х(2)2. (10) Подставляя это выражение в систему

вида

Ai х0)1 - 4 х0)1 + 2 х0)2 + х0)з; Ai - 2 + 5, А + V 0 1,2,3) Ai х№з 2 x0)i + х0)2 + 6 х0)з J (11) и полагая х®2 1, получим

(2,3846 x(2i +0,4560);

А2 1,1923 x(2)i + 4,2280. J (12)

Систему (12) необходимо решить методом итерации, но для этого нужно предварительно сформировать коэффициенты (соотношение 9). Для этого используются коэффициенты aij, записанные в блоке 8 памяти.

При формировании коэффициента awn с выхода 104 на вход 31 считывания элемента 26.1.1 поступает импульс и значение 0,8077 через сумматор 37 блока 15.4 поступает на дополнительный информационный вход 18 блока 8 памяти и после поступления импульса с выхода 71 на вход 21 блока 15 1 записывается в регистре 34 памяти. Затем импульс с выхода 97 поступает на вход 19 считывания элемента 14.1.3 и значение 2 после поступления импульса с выхода 72 на вход 22 блока 15.1 перемножается в блоке 35 умножения со значением 0,€077. После поступления импульсов с выхода 73 на вход 23, с выхода 74 на вход 24 блока 15.1 с его выхода значение - 1,6154 поступает на вход сумматора-накопителя 11 вычислителя 1.1.1, в котором до этого хранилось значение 4, в результате чего в нем станет храниться значение а(2)ц 2.3846.

Аналогичным образом Формируются значения а(2)12 - 0,4560; а 21 1,1923; 4,2280. которые будут храниться в сумматорах-накопителях 11 вычислителей 1.1.2, 1.2.1 и 1.2.2 соответственно.

После подами на входы вторых сомножителей блоков 12 умножения вычислителей 1.1.1 и 1.2.1 произвольного сигнала , а на входы вторых сомножителей блоков 12 умножения вычислителей 1.1.2 и 1.2.2 сигнала 1 начнется реализация итерационного процесса. После достижения сходимости итерационного процесса на выходе делителя 2.2.1, а соответственно невыходе вычислителя 1.2.1 будет получено значение x®i 0,2170, на выходе вычислителя 1.2.2 будет присутствовать сигнал х2 2 1, а на

выходе сумматора 13 будет присутствовать значение Я2 4.4867.

По окончании времени, необходимого для реализации сходимости итерационного

процесса, импульс с выхода 67 поступит на вход 29.1 блока 9 памяти и компоненты x 2 i и х™г второго собственного вектора окажутся записанными в элементах 26 2.1 и 26.2.2 памяти.

Компонента определяется из соотношения (10), т.е. уравнения с одним неизвестным с использованием известного устройства для операций над матрицами, способного решать уравнения с одним неизвестным или системы из п уравнений с п неизвестными по методу Гаусса-Жордана. В его состав входят операционные блоки 4.1.1, 4.1.2, 4.1.3, 4.1.4, элемент 5.1 задержки, блок 6 синхронизации. В нем выполняется обработка матрицы размерности N х М (N 1,2), которая представляет собой матрицу коэффициентов при неизвестных системы линейных уравнений, к которой справа дописана матрица размерности N х 1 свобедных членов.

Таким образом, например, для решения системы из двух линейных уравнений на входы устройства будет поступать матрица В вида

|BiiBi2Bi3l

(13)

. В21 В22 В23 J

где Вп, 812, 621, 622 - коэффициенты при неизвестных, a Bis, В аз - свободные члены.

Элементы матрицы В поступают на входы операционных блоков 4 построчно со сдвигом на один такт под воздействием синхроимпульсов с выходов блока 6 синхронизации, т.е. первая строка поступает на

первый вход операционного блока 4.1.1, начиная с первого такта, вторая строка поступает на первый вход операционного блока 4.2.1, начиная с второго такта, и т.д. На выходах операционных блоков 4.I.J (j n, i

1,..., п) получается семейство решений системы линейных уравнений.

Таким образом, решения системы из двух уравнений получаются на выходах операционных блоков 4.1.2 и 4.2.2. Решение

уравнения с одним неизвестным - на выходе операционного блока 4.1,1.

Следовательно, гри вычислении значения х®з будет задействован только операционный блок 4.1.1. Коэффициент при

неизвестном и свободный член будут вычислены блоком 15.4 блока 9 памяти.

В соответствии с (10) коэффициент при неизвестном х з будет сформирован следующим образом. С выхода 86 на вход 24 блока 15.4 блока 9 памяти поступает Г, в результате чего через сумматор 37 блока 15.4 она поступает на вход операционного блока 4.1.1.

Затем вычисляется свободный член в соответствии с (10). Синхроимпульс с выхода 104 поступает на вход 31 считывания элемента 26.1.1 памяти, с выхода 83 -на синхровход 21 блока 15.4 и значение х записывается в регистр 34 памяти блока 15.4. Синхроимпульс с выхода 107 поступает на вход 31 считывания элемента 26.2.1 памяти, с выхода 84 - на синхровход 22 блока 15.4 и значение перемножается с в блоке 35 перемножения блока 15.4. Синхроимпульс с выхода 85 поступает на синхровход 23 блока 15.4 и результат перемножения . инвертируется в управляемом мверторе 36 блока 15.4, после чего значение - (. поступает на вход сумматора-накопителя 37 блока 15.4. Синхроимпульс с выхода 105 поступает на вход 31 считывания элемента 26.1.2, с выхода 83 - на синхровход 21 блока 15.4 и значение записывается в регистр 34 памяти блока 15.4. Синхроимпульс с выхода 108 поступает на вход 31 считывания элемента 26.2.2 памяти, с выхода 84 на синхровход 22 блока 15.4 и значение перемножается с в блоке 35 перемножения блока 15.4. Синхроимпульс с выхода 85 поступает на синхровход 23 блока 15.4 и результат перемножения х 1 2-х®2 инвертируется в управляемом инверторе 36 блока 15.4, после чего значение (х 2. поступает на вход сумматора-накопителя 37 блока 15.4. Синхроимпульс С выхода 86 поступает на вход 24 блока 15.4 и значение, находящееся в сумматоре-накопителе 37 блока 15.4, поступает на вход операционного блока 4.1.1.

Значение х 2 з - - 0,9473 с выхода операционного блока 4.1.1 поступает на информа- ционный вход 27.3 блока 9 памяти и с поступлением синхроимпульса с выхода 68 на вход 29.2 оказывается записанным в элементе 26.2 3 блока 9 памяти.

Таким образом, в элементах 26.2.1, 26.2.2, 26.2.3 будут записаны компоненты второго собственного вектора матрицы А (соотношение 4): х(2)1 0,2170, х2)2 - t, х(2 з - 0,9473.

По окончании времени, необходимого для вычисления компонент второго собственного вектора, с выхода 62 на тактовый вход регистра 7 сдвига поступает тактовый импульс, в результате чего второй разряд регистра 7 сдвига обнуляется. Так как на вход второго сомножителя блока 3.2.1 поступает О с выхода второго разряда реги

0 5

стра 7, то на выходе блока 3 2.1 формируется 0я.

Вычисление компонент третьего собственного вектора производится следующим образом. На входы вторых сомножителей блоков 12 умножения вычислителей 1.1.1, 1.2.1, 1.3.1 подается сигнал 1. С выхода блока 1.3.1 значение х 1 з 1 поступает на информационный вход 27.1 блока 9 памяти. С поступлением синхроимпульса с выхода 69 на вход 30,1 блока 9 памяти значение 1 записывается в элемент 26.3.1 памя0

5

69 /1

Xх 3

тиПосле этого осуществляется вычисление компонент х 3 2 и х™з с использованием соотношений ортогональности:

0,8077 х(3)1 + 0 7720 х(3)2 + х(3)з 0,1 0,2170 )1 + х(3)2-0.9473 х(3)з - 0. /(14) Так как значение х ч 1 вычислено и записано в элементе 26.3.1 памяти, ю систему уравнений (14) можно представить в виде

US. ( I A. VS X2 О SfWII

х(3)2-0,9473 х(3)з -0,2170

0,7720 + - - 0,8077; 1

(15)

Эта система линейных уравнений легко решается методом Гаусса-Жордана. Поскольку коэффициенты при неизвестных и свободные члены записаны в блоке 9 памяти, то уравнение (15) решается следующим

0 образом.

При поступлении синхроимпульса с выхода 105 на вход 31 считывания элемента 26.1.2 памяти значение 0,7720 считывается с него и при поступлении синхроимпульса с

5 выхода 86 на вход 24 блока 15.4 через сумматор 37 блока 15.4 значение 0,7720 поступает на вход операционного блока 4.1.1.

При поступлении синхроимпульса с выхода 108 на вход 31 считывания элемента

0 26,2.2 памяти значение 1 считывается с него и при поступлении синхроимпульса с выхода 90 на вход 24 блока 15.5 через сумматор 37 блока 15.5 значение 1 поступает на вход операционного блока 4.2.1.

5 Аналогичным образом считываются значения 1 из блока 26.1.3 памяти и значение - 0,9473 из блока 26.2.3 памяти и поступает на входы операционных блоков 4.1.1 и 4.2.1. Аналогично считываются значе0 ния 0,8077 и 0,2170 и после инвертирования в управляемых инверторах 36 блоков 15.4 и 15.5 поступают на входы операционных блоков 4.1.1 и 4.2.1 соответственно.

В соответствии с алгоритмом работы

5 операционных блоков 4 на выходах блоков 4.1.2 и 4,2.2 будут сформированы соответственно значения х™2 - - 0,5673 и х(3)3 , - 0,3698, поступающие на входы 27 2 и 27.3 соответственно блока 9 памяти.

С поступлением синхроимпульса с выхода 70 на вход 30.2 блока 9 памяти значение - 0,5673 окажется записанным в элементе 26.3.2, а значение - 0,3698 - в элементе 26.3.3 памяти.

Таким образом, в элементах 26.3.1, 26.3.2 и 26.3.3 будут записаны компоненты третьего собственного вектора матрицы А (соотношение 4): x(3)i 1, х(3)2 - 0,5673, х(3)з -0,3698. На этом процесс вычисления компонент собственных векторов матрицы А (соотношение 4) заканчивается. Значения компонент собственных векторов хранятся в блоке 9 памяти.

В дальнейшем сии роимпульсы с выхода 113 блока 6 синхронизации поступают на тактовый вход регистра 10 сдвига. С остальных выходов блока 6 синхронизации синхроимпульсы не подаются.

В регистре 10 сдвига перед началом работы генератора функций был записан код вида 10...О (для рассматриваемого случая - 100), причем 1 записана в первом разряде регистра 10 сдвига. Поскольку на тактовый вход регистра 10 сдвига, замкнутого в кольцо цепью обратной связи, поступает периодическая последовательность импульсов с выхода 113 блока 6 синхронизации, то 1, перемещаясь из разряда в разряд регистра 10 сдвига, управляет формированием дискретных базисных функций на выходах генератора, так как выходы разрядов регистра 10 сдвига подключены к входам 31 считывания элементов 26 памяти блока 9. При этом первый разряд регистра 10 сдвига подключен к входам 31 считывания элементов 26.1.1, 26.2,1, 26.3.1, второй разряд - к входам 31 считывания элементов

Si(t) (0.8077,0,7720,1); S2(t) (0,2170, 1, - 0,9473); S3(t) (1,-0,5673,-0,3698),

В ортогональности функций легко убедиться посредством умножения одной из них на любую из двух других.

Функции Si(t), 82(1), Ss(t), будучи попарно ортогональными, линейно независимы между собой. Таким образом, построен ортогональный базис трехмерного пространства, состоящий из собственных векторов матрицы А.

Таким образом, генератор осуществляет формирование дискретных базисных функций.

Аналогичным образом при введении

любой исходной действительной симметрической положительно определенной матрицы в блок 8 памяти на выходах генератора формируется другая система дискретных базисных функций,

При увеличении размерности исходных матриц число дискретных базисных функций увеличивается. При этом значения периодов генерируемых функций и число значений базисных функций имеют весьма

широкий набор, что позволяет повысить точность решения задач обобщенного спектрального анализа и синтеза путем лучшего согласования длины периода обрабатываемого сигнала с длиной периода базисных

функций и представления сигнала малым числом коэффициентов преобразования по системе базисных функций.

Формула изобретения

Генератор функций, содержащий матрицу вычислителей, первую группу блоков деления и блок синхронизации, причем входы задания начального приближения группы генератора соединены с первыми

информационными входами соответствующих вычислителей первой строки матрицы, первый выход вычислителя 1-й(1 1-Р-1, Р - порядок квадратной матрицы коэффициентов) строки матрицы соединены с первым

информационным входом соответствующего вычислителя (i + 1)-й строки матрицы, второй выход вычислителя i-ro столбца матрицы соединен с вторым информационным входом соответствующего вычислителя

(I + 1)-г° столбца матрицы, вторые информационные входы вычислителей первого столбца матрицы соединены с входом логического нуля генератора, вход запуска которого соединен с входом блока синхронизации, отл и-чающийся тем, что, с целью расширения области применения путем генерирования дискретных базисных функций, он содержит регистр сдвига, с первой по (Р-1)-й группы блоков элементов И, с

второй по (Р-1)-Ю группы блоков деления, первый и второй блоки памяти, матрицу операционных блоков, с первого по (Р-2)-й элементы задержки и кольцевой регистр сдвига, причем второй выход вычислителя

(I+ 1)-й строки (I + 1)-го столбца матрицы соединен с входами делителя блоков выделения (Р-1)-й группы, вход делимого j-ro блока деления 0 1-Р-1)1-й группы соединен с вторым выходом вычислителя j-й строки (P-I+ 1)-го столбца матрицы выход

j-ro блока деления 1-й группы соединен с первым входом элементов И J-ro блока 1-й группы, вторые входы блоков элементов И 1-й группы соединены с выходом t-ro разряда регистра сдвига, выходы блока синхрони- зации соединены соответственно .с тактовыми входами операционных блоков .матрицы, с тактовыми входами с первого по (Р-2)-й элементов задержки, с входом разрешения сдвига регистра сдвига, с входами разрешения записи первого блока памяти, с входами разрешения записи второго блока памяти, с тактовыми входами первого и второго блоков памяти, с входами разрешения считывания первого и второго блоков памяти и с входом разрешения сдвига кольцевого регистра сдвига, выходы j-x блоков элементов И с первой по (Р-1)-ю групп соединены с первым информационным входом вычислителя (j + 1)-й строки j-ro столбца мат- рицы, выходы вычислителей последней строки матрицы соединены с соответствующими информационными входами второго блока памяти, первый информационный вход операционного блока 1-й строки перво- го столбца матрицы соединен с 1-м выходом второго блока памяти, первые выходы операционных блоков 1-й строки S-x (S I-P-1) столбцов матрицы соединены с (Р-1 1)-м информационным входом группы второго

X, X,

блока памяти, первый информационный вход операционного блока К-й и (К 1-Р-2) строки M-ro (M 2-Р-1) столбца матрицы соединен с первым выходом операционного блока (К + 1)-й строки (М-1)-го столбца матрицы, первый информационный вход операционного блока (Р-2)-й строки М-ro столбца матрицы подключен к выходу элемента задержки, информационный вход которого подключен к второму выходу операционного блока (Р-1)-й строки (М-1)-го столбца матрицы, второй информационный вход операционного блока М-й строки 1-го столбца матрицы подключен к второму выходу операционного блока (М-1)-й строки 1-го столбца матрицы, входы значения компонент исходной матрицы группы генератора соединены соответственно с информационными входами группы первого блока памяти, выходы которого соединены с третьими информационными входами вычислителей соответствующих строк матрицы, К-й выход второго блока памяти соединен с (К-М)-м дополнительным информационным входом группы первого блока памяти, выходы разрядов кольцевого регистра сдвига соединен с соответствующими входами разрешения считывания второго блока памяти, выходы которого являются выходами группы генератора,

« °Ч

LL1

Фиг.1

L

1

Jj

в

i

ТЗ

я

Е

I

«SJ

s

ES

I . I

ICsj I

b-i К ibvb -aij|

tj

т

esi CN

w%

t5

«Si

«S|

-i

M i

0

s

ж

L

Г

L

r

ja1

Ю

«g- «э ч- со in

#lL

Ј51

fl

Щn

Щпппп

73 ПППИ

7 |ПППП.

40 68 80 100

%Ј //

,Vi

771 781 79

#1

ML

П

п

ft flflfl

щ

| и

90 Щ

91

Щ

|

ZO 40 60 80 1001 ФигМ

LJL

ПП

L в

MY n

./toi n

.$HП П ПО

flffln n fin

Itmnnfinnnnnnnnnnnnnnnnnn

-ь-5

Л7 40 $0 80 100 t Фиг.13

-ь-5

0 t

| Устройство для операций над матрицами | 1987 |

|

SU1443003A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Генератор функций Уолша | 1987 |

|

SU1501019A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивное устройство для вычисления среднего | 1986 |

|

SU1348856A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-08-07—Публикация

1990-03-06—Подача