1

Изобретение относится к аналоговой и аналого-цифровой (гибридной) вычислительной технике и может быть применено при моделировании систем автоматического управления.

Целью изобретения является повышение точности воспроизведения функции за счет увеличения числа участков аппроксимации без существенного увеличения количества элементов схемы.

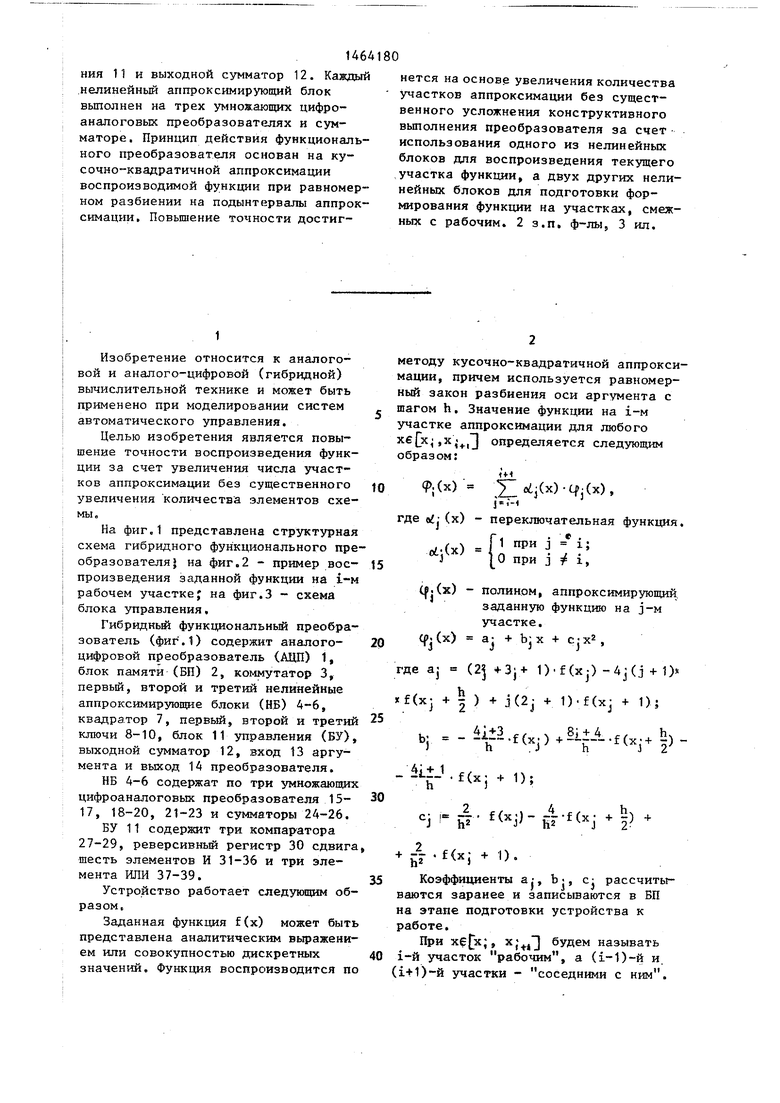

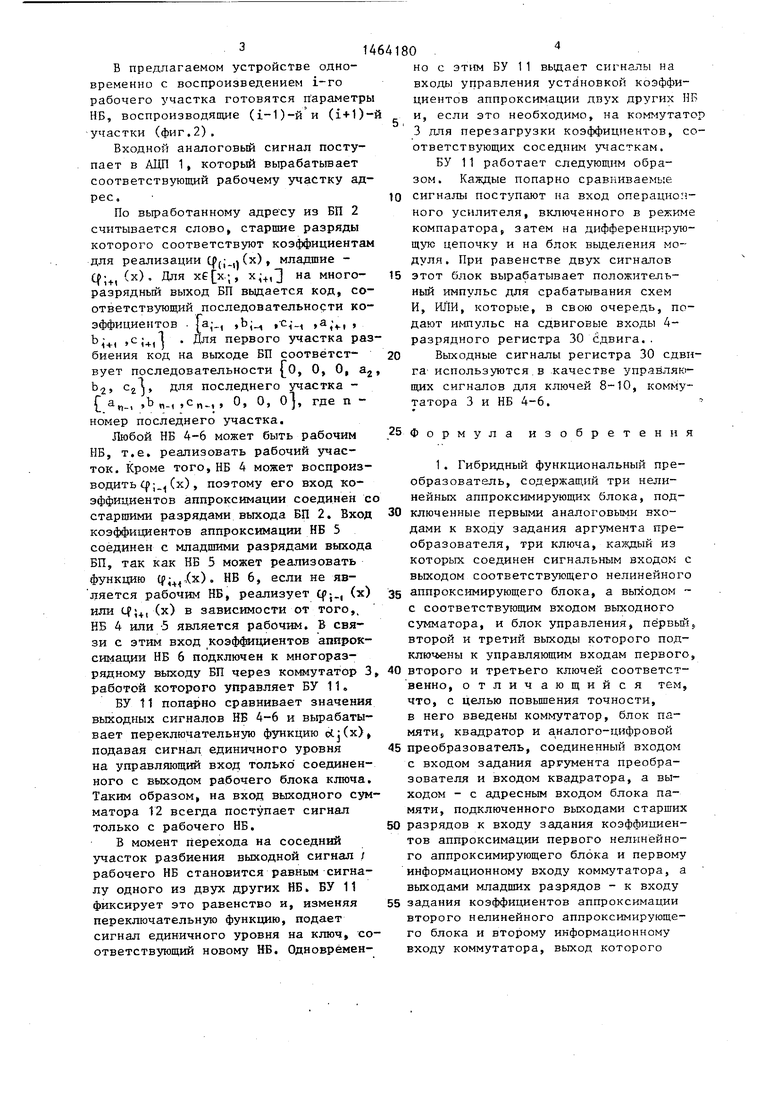

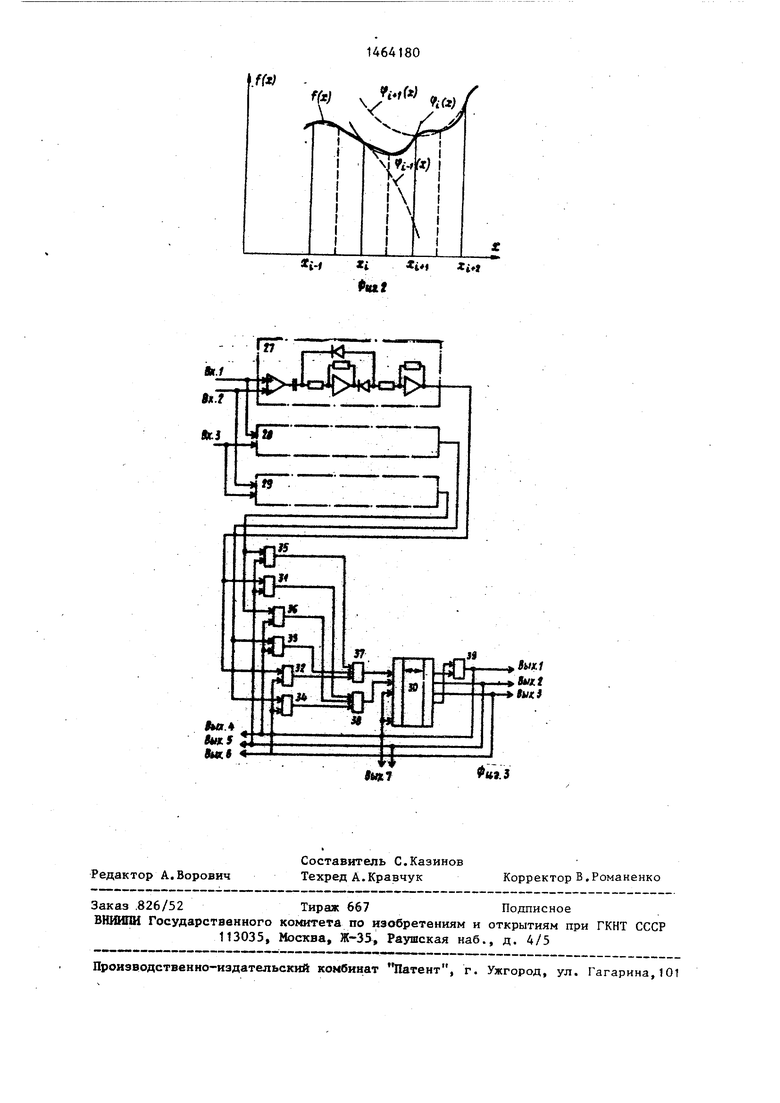

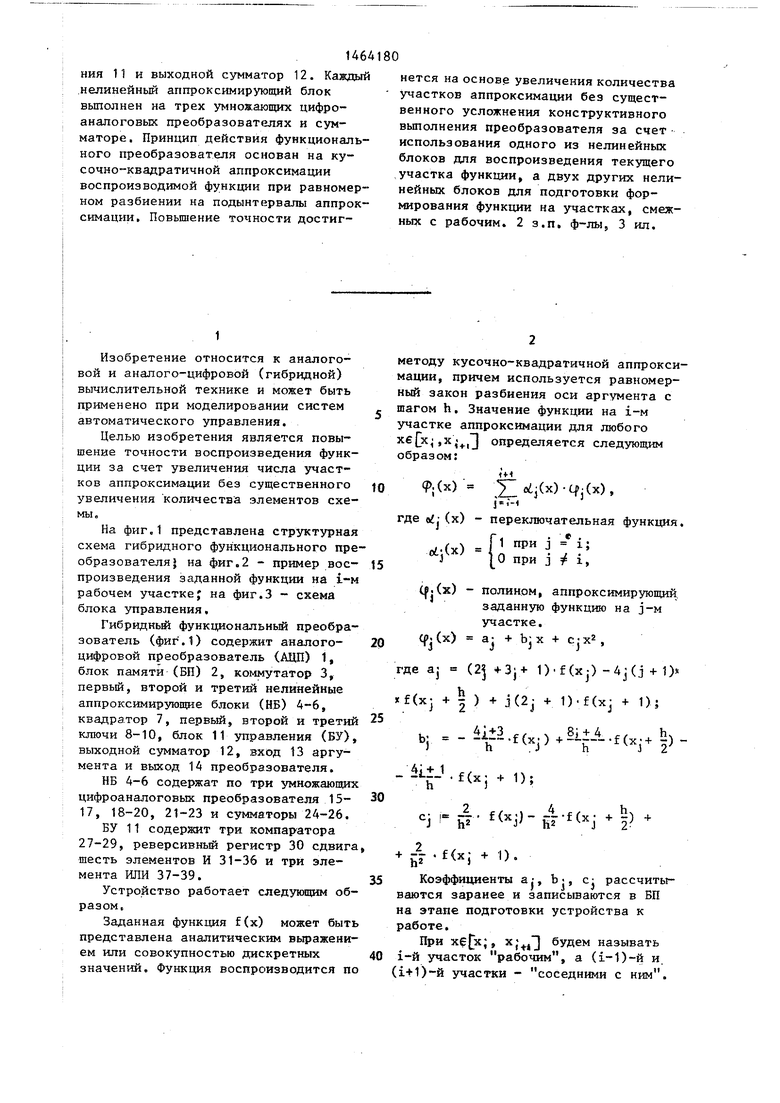

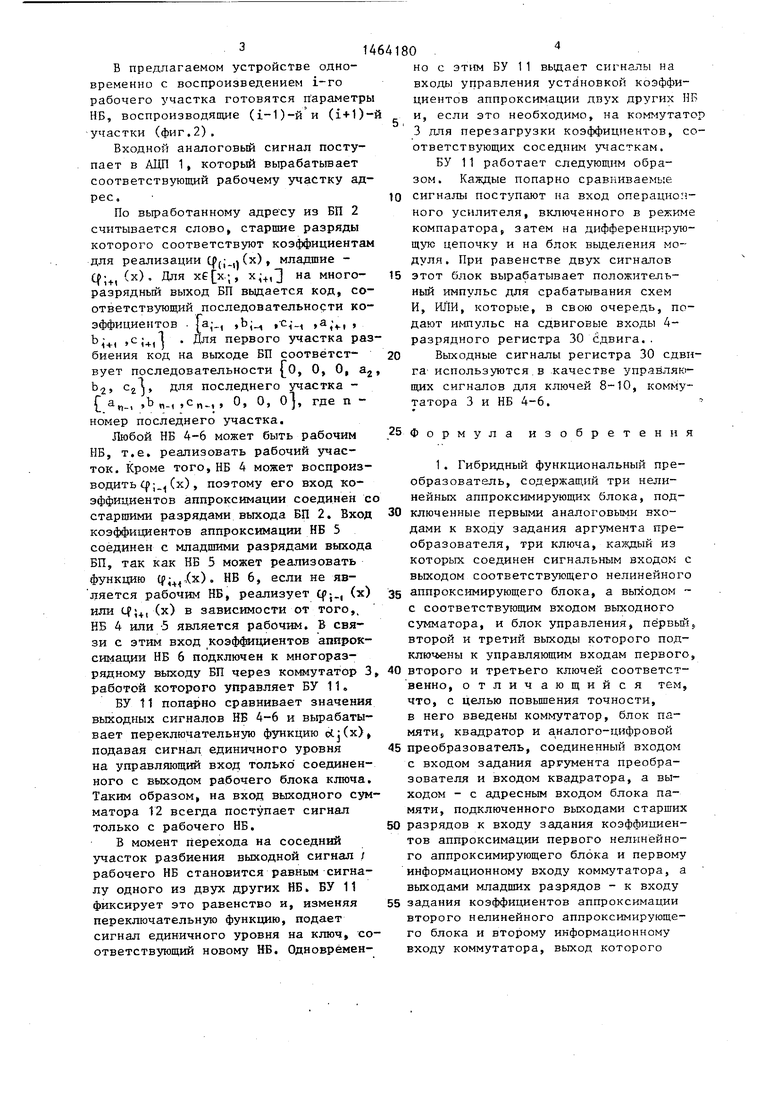

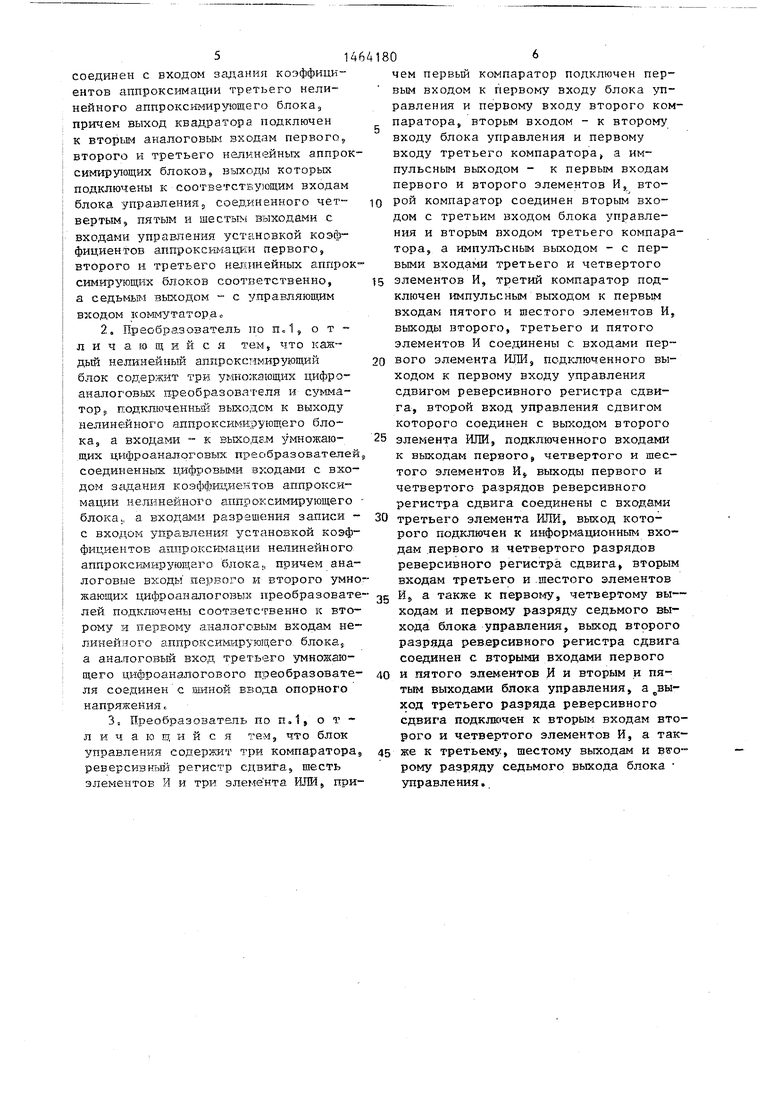

На фиг,1 представлена структурная схема гибридного функционального преобразователя на фиг.2 - пример вое- произведения заданной функции на i-м рабочем участке; на фиг.З - схема блока управления.

Гибридньй функциональный преобразователь (фиг .О содержит аналого- цифровой преобразователь (АЦП) 1, блок памяти (БП) 2, коммутатор 3, первый, второй и третий нелинейные аппроксимирующие блоки (НБ) 4-6, квадратор 7, первый, второй и третий ключи 8-10, блок 11 управления (БУ), выходной сумматор 12, вход 13 аргумента и выход 14 преобразователя.

НБ 4-6 содержат по три умножающих цифроаналоговых преобразователя 15- 17, 18-20, 21-23 и сумматоры 24-26.

БУ 11 содержит три компар атора 27-29, реверсивный регистр 30 сдвига шесть элементов И 31-36 и три элемента РШИ 37-39.

Устройство работает следующим образом.

Заданная функция f(x) может быть представлена аналитическим выражением или совокупностью дискретных значений, функтдия воспроизводится по

методу кусочно-квадратичной аппроксимации, причем используется равномерный закон разбиения оси аргумента с шагом h. Значение функции на i-м участке аппроксимации для любого x€LX,x, определяется следующим образом:

Ф;(Х) (x)-(.(x),

J.;M где ofj (х) - переключательная функция.

ct.,(x) f f i О при J ь 1,

(f. (х) - полином, аппроксимирующий заданную функцию на j-м участке.

(fj (х) aj + bj X + Cj х2 ,

где aj (25 +3j+ l) f(xj)-4j(j + О« xfCxj + I ) + j(2j + 1).f(xj + 1);

.f(x.).§.iA,,...|, .L±J.f(. ., 1).

cjr j. f(xjj- A.f(,. |)

jj|.f(x; -f 1).

Коэффициенты a.-, Ъ-, с- рассчитываются заранее и записываются в БП на этапе подготовки устройства к работе.

При xejjsc;, будем называть i-й участок рабочим, а (1-1)-й и (1+1)-й участки - соседними с ним.

В предлагаемом устройстве одновременно с воспроизведением i-ro рабочего участка готовятся параметры НБ, воспроизводящие (i-1)-ft и (1+1)участки (фиг.2).

Входной аналоговый сигнал поступает в АЦП 1, который вырабатьгоает соответствующий рабочему участку адрес.

По выработанному адресу из БП 2 считывается слово, старшие разряды которого соответствуют коэффициентам для реализации Cf (;., (х) , младшие - , (х). Для .;, х-+,3 на многоразрядный выход БП выдается код, соответствующий последовательности коэффициентов

,

Ь;

.-Cl-1

3j, (- -1-1 . Для первого участка раз20

БУ 11 работает следующим образом. Каждые попарно сравниваемые сигналы поступают на вход операцион ного усилителя, включенного в режим компаратора, затем на дифференцирую щую цепочку и на блок выделения модуля. При равенстве двух сигналов этот блок вырабатывает положительный импульс для срабатывания схем И, ИЛИ, которые, в свою очередь, по дают иьшульс на сдвиговые входы 4- разрядного регистра 30 Сдвига..

Выходные сигналы регистра 30 сдв га- используются. в качестве упрайляк) щих сигналов для ключей 8-10, комйу татора 3 и НБ 4-6.

биения код на выходе БП соответствует последовательности , О, О, а, Ь, Cj, для последнего участка - а„, ,Ъ„., ,с„., , О, О, о, где п - номер последнего участка.

Любой НБ 4-6 может быть рабочим НБ, т.е. реализовать рабочий ток. Кроме того, НБ 4 может воспроизводить . (х) , поэтому его вход коэффициентов аппроксимации соединен со старшими разрядами выхода БП 2. Вход коэффициентов аппроксимации НБ 5 соединен с младшими разрядами выхода БП, так как НБ 5 может реализовать функцию (f;,(x), НБ 6, если не яв- ляется рабочим НБ, реализует ., (х) или , (х) в зависимости от того,. НБ 4 или -5 явянется рабочим. В связи с этим вход коэффициентов аппроксимации НБ 6 подключен к многоразрядному выходу БП через коммутатор 3, 40 второго и третьего ключей соответст25 Формула изобретени

1. Гибридный функциональный преобразователь, содержащий три нелинейных аппроксимирующих блока, под30 ключенные первыми аналоговыми входами к входу задания аргумента преобразователя, три ключа, ка5кдый из которых соединен сигнальным входом с выходом соответствующего нелинейного

35 аппроксимирующего блока, а выходом с соответствующим входом выходного сумматора, и блок управления, первый второй и третий выходы которого подключены к управляющим входам первого

работой которого управляет БУ 11.

БУ t1 попарно сравнивает значения выходных сигналов НБ 4-6 и вьфабаты- вает переключательную функцию ctjCx) подавая сигнал единичного уровня на управляющий вход только соединенного с выходом рабочего блока ключа. Таким образом, на вход выходного сумматора 12 всегда поступает сигнал только с рабочего НБ.

В момент перехода на соседний участок разбиения выходной сигнал ; рабочего НБ становится равным сигналу одного из двух других НБ. БУ 11 фиксирует это равенство и, изменяя переключательную функцию, подает сигнал единичного уровня на ключ, соответствующий новому НБ. Одноврёменвенно, отлич ающийся тем, что, с целью повьппения точности, в него введены коммутатор, блок памяти, квадратор и аналого-цифровой

45 преобразователь, соединенный входом с входом задания аргумента преобразователя и входом квадратора, а выходом - с адресным входом блока памяти, подключенного выходами старших

50 разрядов к входу задания коэффициентов аппроксимации первого нелинейного аппроксимирующего блока и первому информационному входу коммутатора, а выходами младщих разрядов - к входу

55 задания коэффициентов аппроксимации второго нелинейного аппроксимирующего блока и второму информационному входу коммутатора, выход которого

0

5

0

но с этим БУ 11 выдает сигналы на входы управления установкой коэффициентов аппроксимации двух других НБ и, если это необходимо, на коммутатор 3 для перезагрузки коэффициентов, соответствующих соседним ут-шсткам.

БУ 11 работает следующим образом. Каждые попарно сравниваемые сигналы поступают на вход операционного усилителя, включенного в режиме компаратора, затем на дифференцирующую цепочку и на блок выделения модуля. При равенстве двух сигналов этот блок вырабатывает положительный импульс для срабатывания схем И, ИЛИ, которые, в свою очередь, подают иьшульс на сдвиговые входы 4- разрядного регистра 30 Сдвига..

Выходные сигналы регистра 30 сдвига- используются. в качестве упрайляк)- щих сигналов для ключей 8-10, комйу- татора 3 и НБ 4-6.

40 второго и третьего ключей соответст25 Формула изобретения

1. Гибридный функциональный преобразователь, содержащий три нелинейных аппроксимирующих блока, под30 ключенные первыми аналоговыми входами к входу задания аргумента преобразователя, три ключа, ка5кдый из которых соединен сигнальным входом с выходом соответствующего нелинейного

35 аппроксимирующего блока, а выходом с соответствующим входом выходного сумматора, и блок управления, первый второй и третий выходы которого подключены к управляющим входам первого.

40 второго и третьего ключей соответственно, отлич ающийся тем, что, с целью повьппения точности, в него введены коммутатор, блок памяти, квадратор и аналого-цифровой

45 преобразователь, соединенный входом с входом задания аргумента преобразователя и входом квадратора, а выходом - с адресным входом блока памяти, подключенного выходами старших

50 разрядов к входу задания коэффициентов аппроксимации первого нелинейного аппроксимирующего блока и первому информационному входу коммутатора, а выходами младщих разрядов - к входу

55 задания коэффициентов аппроксимации второго нелинейного аппроксимирующего блока и второму информационному входу коммутатора, выход которого

5146

соединен с входом задания коэффициентов аппроксимации третьего нелинейного аппрокс,имирующего блока, причем выход квадратора подключен к вторш аналоговым входам первого, второго и третьего н алкнейньгх аппроксимирующих блоков, ВГаПСОДЫ КОТОрЫХ

подключены к соответствующим входам блока управления, соединенного четвертым, пятым и шестым выходами с входами управления установкой коэффициентов аппроксимацк:и первого, второго и третьего нелинейных аппроксимирующих блоков соответственно, а седьмы - выходом с управляющим входом коммутатора о

2. Преобразователь по n.l, о т - л и ч а ю щ и и с я тем, что каждый нелинейный алпроксммирующий блок содержит три умножающих цифро- аналоговых преобразователя и сумматор подключенный вькодом к выходу нелинейного аппроксимирующего блока, а входами - к вьшодам умножаю- щих цифроанапоговых преобразователей соединенных цифровыми входа -ш с входом задания коэффш-щектов аппроксимации нелинейного аппроксимирующего блока;, а входа йи разрешения записи - с входом управления установкой коэффициентов аппроксимации нелинейного аппроксимирующего блока,, причем аналоговые входы первого к второго умножающих цифроаналоговыз преобразовате лей подключены соответственно к второму и первому аналоговым входам не линейного аппроксимирующего блока, а аналоговый вход третьего умножающего дифроаналогового п:оеобразовате- ля соединен с шиной ввода опорного напряжения.

3s Преобразователь по п.1, о т - л и ч а ю щ и и с я тем, что блок управления содержит три компараторЯ реверсивньш регистр сдвига, шесть элементов И и три элеме нта ИЛИ, при

0

5 ЗО 5 40

чем первьш компаратор подключен первым входом к первому входу блока управления и первому входу второго компаратора, вторым входом - к второму входу блока управления и первому входу третьего компаратора, а импульсным выходом - к первым входам первого и второго элементов И, второй компаратор соединен вторым входом с третьим входом блока управления и вторым входом третьего компаратора, а импульсным вькодом - с первыми входами третьего и четвертого

5 элементов И, третий компаратор подключен импульсным выходом к первым входам пятого и шестого элементов И, выкоды второго, третьего и пятого элементов И соединены с входами пер0 вого элемента ИЛИ, подключенного выходом к первому входу управления сдвигом реверсивного регистра сдвига, второй вход управления сдвигом которого соединен с выходом второго элемента ИЛИ, подключенного входами к выходам первого, четвертого и шестого элементов И выходы первого и четвертого разрядов реверсивного регистра сдвига соединены с входами третьего элемента ИЛИ, выход которого подключен к информационным входам .первого и четвертого разрядов реверсивного регистра сдвига, вторым входам третьего и .шестого элементов Hj а также к первого, четвертому вы- кодам и первому разряду седьмого выхода блока управления, выход второго разряда реверсивного регистра сдвига соединен с вторыми входами первого и пятого элементов И и вторым и пятым выходами блока управления, а выход третьего разряда реверсивного сдвига подклк«чен к вторым входам второго и четвертого элементов И, а также к третьему, шестому выходам и второму разряду седьмого выхода блока управления.

i-f i Xi,i 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1978 |

|

SU805337A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1076918A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Функциональный преобразователь | 1979 |

|

SU830430A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Устройство для регулирования температуры | 1981 |

|

SU980076A1 |

| Квадратор | 1986 |

|

SU1405053A1 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - повышение точности. Гибридный функциональный преобразователь содержит аналого-цифровой преобразователь t, блок памяти 2, коммутатор 3, три нелинейных аппрок- симирунщих блока 4, 5 и 6, квадратор 7, три ключа 8, 9 и 10, блок управле

Ar.f

ЙМ« 4

Jugt

ttt.3

| Функциональный преобразователь | 1978 |

|

SU805337A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Смолов В.Б, Функциональные преобразователи информации | |||

| Л.: Энерго- издат, 1981, с | |||

| Искусственный двухслойный мельничный жернов | 1921 |

|

SU217A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-07—Публикация

1987-07-06—Подача