(54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для воспроизведения функций | 1985 |

|

SU1273955A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Аналого-цифровой функциональный преобразователь | 1988 |

|

SU1508249A1 |

| Функциональный преобразователь | 1979 |

|

SU842852A1 |

| Функциональный генератор | 1985 |

|

SU1262533A1 |

| Устройство для передачи телеизмерений с адаптивной коммутацией | 1984 |

|

SU1267459A1 |

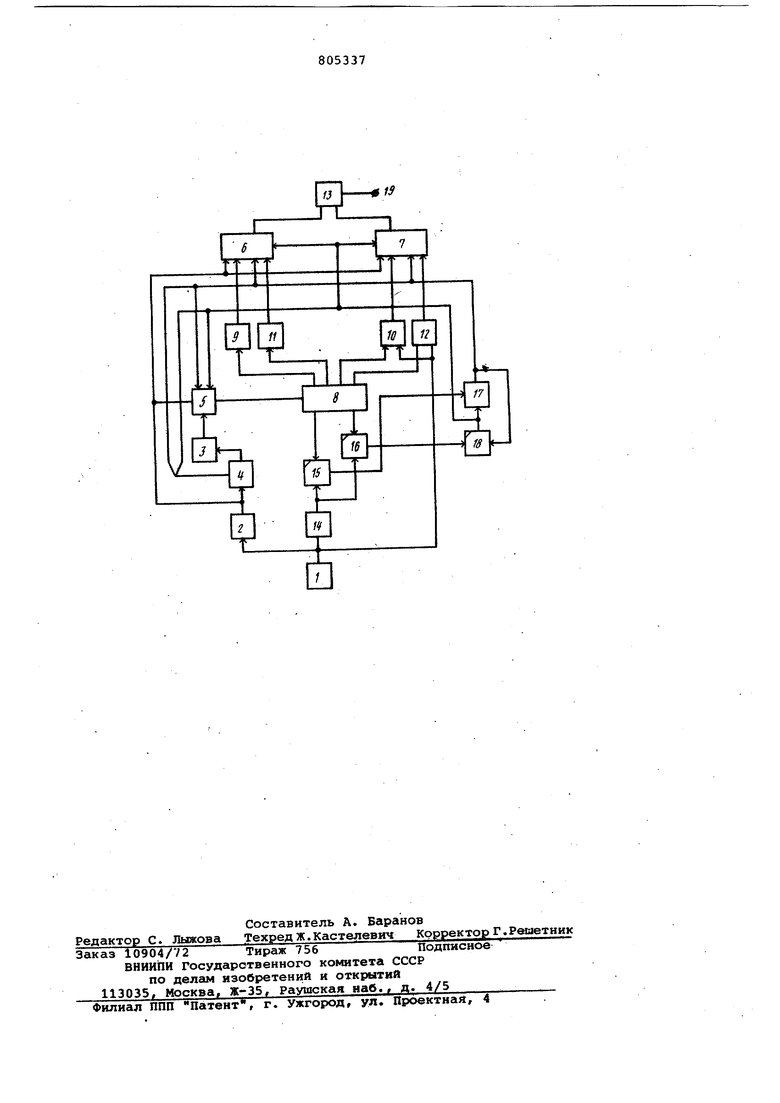

Изобретение относится к вычислительной технике ri может быть примене но в аналого-цифровых вычислите.льных машинах, в приборах.и устройствах автоматики и измерительной техни ки, а также в ряде других устройств, в которых возникает необходимость воспроизведения нелинейных функций. Известны функционсшьные преобразователи, которые содержат выходной усилитель, преобразователи цифроаналог, компараторы,.логическую схему, счетчик адреса и запоминакяций блок. Данные преобразователи позволя ют автоматизировать набор характера нелинейной зависимости . Недостатками преобразователя являются ограниченность класса воспроизводимых функций, невысокие показатели точности надежности г быстродействия и т.д. Наиболее близким к изобретению по технической сущности является уст ройство, содержсодее устройство определения знака производной, подключен ное к выходу источника входного сигнала, запоминающее устройство, счетчик адреса, выход которого соединен со входом запоминающего устройства, коммутаторы, управляющие входы кото рых соединены с выходом устройства определения знака производной, буферный регист, подключенный через коммутатор к выходу запоминающего устройства, цифроаналоговые преобразователи , входы которых соединены с выходами определенных разрядов буферного регистра, а выходы - со входами . других коммутаторов, сумматор, входы которого .подключены к выходам соответствующих коммутаторов, компараторы, входы которых соединены с выходами источника входного сигнала и соответствукяцих цифроаналоговых преобразователей, а выходы подключены ко входам коммутаторов и счетному входу счетчика адреса, и при этом выход источника входного сигнала соединен со входами двух цифроаналоговых преобразователей 2. Однако устройство обладает существенным недостатком - сравнительно низкой точностью, которая обусловлена применением компараторов для сравнения входного сигнала с заданными его значениями в узлс1Х аппроксимации. Компараторы вследствие наличия зоны нечувствительности и гистерезиса не позволяют производить сравнение сигналов, незначительно отличающихся .друг отхдруга. Это приводит к рграни . чению числа участков аппроксимации и к ограничению снизу длины каждого из участков аппроксимации (длина участка аппроксимации не может быть :выбрана меньше удвоенного значения . зоны нечувствительности компаратора)) что ведет в свою очередь к пониженик) точности воспроизведения функций из вестным устройством. Понижение точнос ти устройства связано также с необхо димостью преобразования значений аргумента в узлах аппроксимации, эада- ваемых с некоторой погрешностью цифровым кодом, в аналоговую форму. Последнее обуславливает неэффективность применения для сравнения аналоговых сигналов, один из которых является аргументом функции, а другой - его значением в узле аппроксимации, высс;ко чувствительных компараторов, которые приводят к значительным усложнениям схемы устройства. Цель изобретения - повышение точности функционального преобразователя. Поставленная цель достигается тем что в устройство, содержащее сумматор, три коммутатора, четыре цифроаналоговых преобразователя, буферный регистр, блок памяти, счетчик адреса блок определения знака производной, выход которого соединен с первыми входами трех коммутаторов и вводом счетчика адреса, выход счетчика адреса соединен со входом блока памяти выход которого соединен со вторым входом первого коммутатора, выход которого подключен ко входу буферноt-o регистра, первый, второй, третий и четвертый выходы которого соединены соответственно со входами первого и второго и первыми входами третьего и четвертогоцифроаналоговых преобразователей, выходы первого и второго цифроаналоговых преобразователей подключены соответственно ко второму и третьему входу второго коммутатора, а выходы третьего и четвертого цифроаналогоБглх преобразователей соединены соответственно со вторым и третьим входом третьего коммутатора, выходы второго и третьего коммутаторов соединены соответственно с первым и вторым входами сумматора, выход которого является выходом преобразова теля, причем вторые входы третьего и четвертого цифроаналоговых преобразователей и вход блока определения знака производной объединены и являются входом преобразователя, введены аналого-цифровой преобразователь, два блока сравнения и два триггера, при этом выход аналого-цифрового преобразователя соединен с пёрвьвли входами первого и второго блоков сравнения, выходы которых подключенык установоч ным входам соответственно первого и второго триггеров, причем выход первого триггера соединен со счетным входом второго триггера, третьим входом первого коммутатора и четвертыми входами второго и третьего коммутаторов, выход второго триггера подключен к счетному входу первого тригjrepa,. четвертому входу первого и пя-тым входам второго и третьего коммутаторов, вторые входы первого и второго блоков сравнения соединены соответственно с пятым и шестым выходами буферного регистра, а вход аналого-цифрового преобразователя является входом функционального преобразователя. На чертеже приведена блок-схема устройства. Схема содержит источник 1 входного сигнала, блок 2 определения знака производной, блок 3 памяти, счетчик 4 адреса, коммутаторы 5-7, буферный регистр , цифроаналоговые преобразователи 9-12, сумматор i-3, аналого-цифровой преобразователь 14., блоки 15 и 16 сравнения, триггеры 17 и 18, выход устройства 19. Устройство работает следующим об разом. Воспроизводимую функцию аппроксимируют кусочным полиномом первой степени, так что , где - номер интервала аппроксимации 0(/Ь полиноминальные коэффициенты, которые .известны для всех участков аппроксимации и хранятся в блоке 3 памяти. в буферный регистр 8 занесены начальные значения точек квантования аргумента, полиноминальных коэффициентов на двух соседних; (обычно в начале области изменения аргумента) участках аппроксимации, что достигнуто установкой счетчика 4 адреса в оп-. ределенное состояние. Значения аргумента в точках квантования х и . с буферного регистра 8 поданы на входы блоков 15 и 16 сравнения соответственно, и значения коэффициентов 4 4( соответствующих разрядов буферного регистра 8 через цифроаналоговЫе преобразователи 9-12 подаются на входы коммутаторов 6 и 7. Входной сигнал, преобразуемый в цифровую форму аналого-цифровым преобразователем 14, подается на вторые входы блоков 15 и 16 сравнения. Точность выполнения операции сравнения кодов и Х определяется выбором длины разрядной сетки буферного регистра 8, в которых хранятся значения , Х,, и точностью представления входного сигнала х цифровым кодом и во много раз превышает аналогичные показатели при сравнении х х с помощью компараторов. Для управления работой коммутаторов 5-7 к ним подключены выходы триггеров 17 и 18 и блока 2 определения знака производной. Коммутатором 5 осуществляется подключение ячейки блока 3 памяти к определенным входным цепям буферного регистра 8. Триггеры 17 и 18 устанавливаются в определенное состояние О или 1 сигнаЬами, подаваемыми на них с выходов 5локов 15 и 16 сравнения кодов. Переход одного из триггеров 17 и 18 из состояния О в состояние 1 приводит к переключению по счетному входу другого триггера из состояния 1 в состояние О. Счетный вход счетчика адреса и подключен к выходам триггеров 17 и 18, а управляющий -к выходу блока 2 определения знака производной и переход одного из этих триггеров из состояния О в состояние 1 приводит к увеличентию на 1 содержимого счетчика 4 адреса при положительной производной аргумента X и уменьшению на 1 содержимого счетчика 4 адреса при отрицательной прюизводной. На выходе аналого-цифровых преобразователей 9 и 11 получаем сигналы, пропорциональные коэффициентам а на выходе преобразо атеа; и а лей 10 и 12 - пропорциональные произведениям Ъ х H})J.X соответственно В зависимости от состояния триггеров 17 и 18 и знака производной входного сигнала на выходе коммутатора 6 получаем сигналы, пропорциональные а или положительной производной и , или а при отрицательной производной, а на выходе коммутатора 7ЬХ или Ь,при положительной производной иЪ.х или b X при отрицательной про изводной Пусть значение переменной х таковс), что его производная положительна и на выходе блока 16 сравнения сигнал равен нулю (соответствует выполнению условия - выходной сигнал преобразова теля 14 меньше сигнала, подаваемого с выхода буферного регистра 8), а сигнал на выходе блока 15 сравнения равен единице. Этим сигналом триггер 17 переключается из состояния О в состояние и переводит триг гер 18 в состояние О. В этом случае на выходе коммутаторов 6 и 7 появляются сигналы, пропорциональные a.j и соответственно (к - число, хранимое в счетчике 4 адреса до переключения триггера 17, равное номеру интервала аппроксимации), суммирование которых приводит к появлению на выходе сигнала , которым на к-ом интервале аппроксима ции и определяется воспроизводимая функция. При этом переход триггера 1 в состояние 1 обуславливает увепич - ние числа, хранимого в счетчике 4 адреса на 1, и из блока 3 памяти, ко входгш коммутатора 5 подключаются чейки, содержащие информацию о хаактеристиках К-1-ГО участка аппроксиации х, ац,,,которые заносятся те разряды буферного регистра 8, в оторых хранилась информация о харакеристиках К-1-ГО участка аппроксиации х., а., Ь.. При достижении еременной х величины, равной значе-j нию к., на выходе блока 16 сравнения ырабатывается сигнал, которым тригер 18 перевЬдится из состояния О состояние 1, что в свою очередь риводит к переключению триггера 17 з состояния 1 в состояние О. ледствием этого переключения триггеров 17 и 18 является появления на выходе коммутаторов 6 и 7 сигналов, пропорциональных значениям а.- и ; ц, что приводит к формированию на выходе 19 сумматора 13 сигнала к+и .л которым определяется функция на к+1-Ом участке аппроксимации. Одновременно состояние счетчика 4 адреса увеличивается на 1 в разряды буферного регистра 8, в которых хранилась информация о характеристиках к-го участка гтпроксимации х через открывшиеся цепи коммутатора 5 заносится информации о характеристиках к-ь2-го участка аппроксимации «42 Ь(ц,;2 Дальнейшее увеличение входного сигнала х приводит к повторению описанного цикла. В случае изменения знака производной входного сигнала х счетчик 4 адреса переводится сигналом, снимаемым с выхода блока 2 определения знака производной, в режим вычитания и теперь ко входам коммутатора 5 подключается ячейка блока 3 памяти, в которой хранится информация о характеристиках не последующего, а предыдущего интервала аппроксимации, которая,как и ранее, по переключению триггеров 17 и 18 заносится в соответствующие разряды буферного регистра 8. Уменьшение входного сигнала х до величины XK-I приведет к изменению состояния счетчика 4 адреса и триггеров 17 и 18, в результате чего на выходе коммутаторов 6 и 7 образуются сигналы, пропорционсшьные значениям а.иЪ.;(Х, что приводит к появлению на выходе 19 сумматора 13 сигнала i|x) Одновременно в буферный регистр 8 заносятся значения х. а., цикл повторяется. Таким образом, введение аналогоцифрового преобразователя, блоков сравнения и триггеров для управления |работой коммутаторов за счет отсутствия цифроаналогового преобразователя и выполнения сравнения входного сигнала с его значением в узлах аппроксимация, представляемых цифровым кодом, позволяет при определенном выборе количества разрядов кода производить сравнение сигналов, отстоящих друг от друга на сколь угодно малое расстояние, а следовательно, повысить TOiHOcTb функционального преобразователя за счет увеличения числа участков аппроксимации при их рроизяояьной длине. Формула изобретения 51 ун кциональный преобразователь, содержащий сумматор, три коммутатора четыре цифроаналоговых преобразовате ля, буферный регистр, блок памяти, счетчик адреса, блок определения знака производной, выход которого соеди иен с первыми входами трех коммутаторов и вводом счетчика адреса, выход счетчика адреса соединен со входом блока памяти, выход которого соединен со вторым входом первого коммутатора выход которого подключен ко входу бу ферного регистра, первый, второй, третий и четвертый выходы которого со единены соответственно со входами .первого и второго и первыми входами третьего и четвертого цифроаналоговых .преобразователей, выходы первого и второго цифроаналоговых преобразователей подключе.ны соответственно ко второму и третьему входу второго коммутатора, а выходы третьего и четвер того цифроаналоговых преобразователей соединены, соответственно со вторым и третьим входом третьего коммутатора, выходы второго и третьег.о коммутаторов соединены соответственно с первым и вторнлм входами сумматора, выход которого является выходом преобразователя, причем вторые входы третьего и четвертого цифроаналоговых преобразователей и вход блока определения знака производной объединены и являются входом преобразователя, отличающийся тем, что, с целью повышения точности, в него введены аналого-цифровой пресзбразователь, два блока сравнения и два триггера, при этом выход аналогоцифрового преобразователя соединен с первыми входами первого и второго блоков сравнения, выходы которых подключены к установочным входам соот-. ветственно первого и второго триггеров, причем выход первого триггера соединен со счетным входом второго триггера, третьим входом первого коммутатора и четвертыми входами второго и третьего коммутаторов, выход второго триггера подключен к счетному входу первого триггера, четвертому входу первого и .пятым входам второго и третьего коммутаторов, вторые входы первого и второго блоков сравнения соединены соответственно с пятым и шестым выходами буферного регистра, а вход аналого-цифрового преобразователя является входом функционального преобразователя. Источники информации, принятые во внимание при экспертизе 1.Гинсбург С. А. и Либарский Ю.Я. функциональные преобразователи с аналого-цифровьм представлением информации. М., Энергия, 1973. 2.Авторское свидетельство СССР W 459777, кл. С, 06 Р 15/20, 1973 (прототип).

Авторы

Даты

1981-02-15—Публикация

1978-11-20—Подача