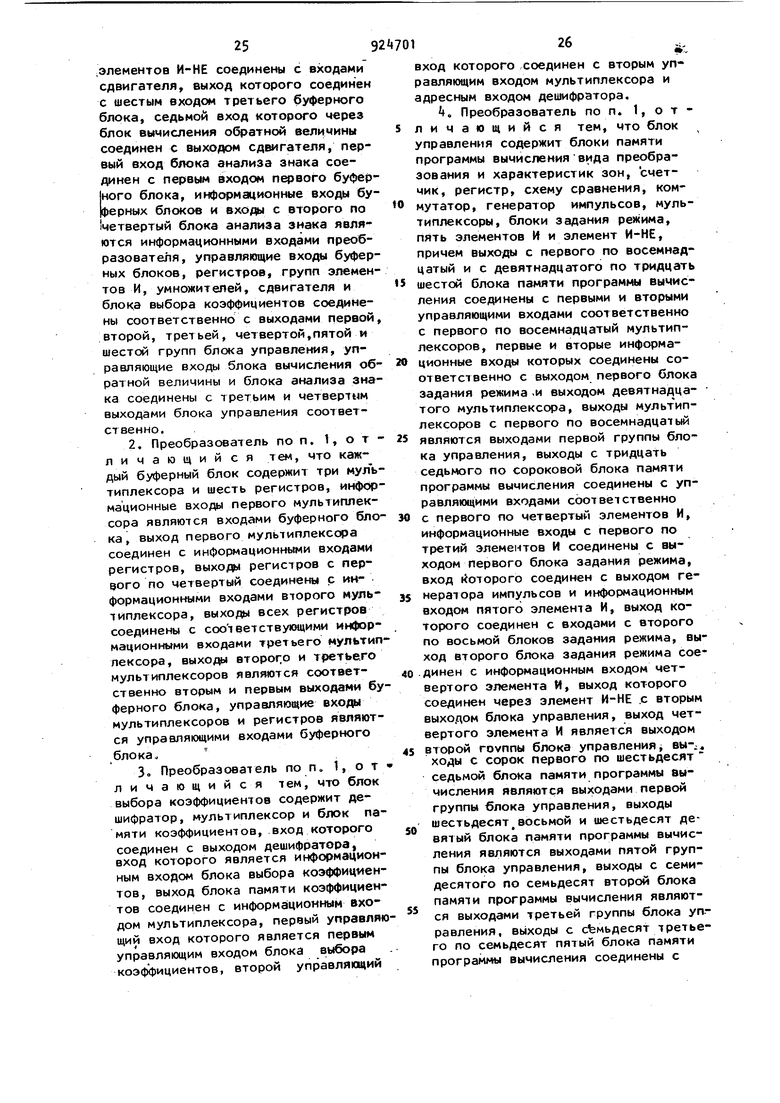

и с первыми входами еоо1ветственно первого, второго и третьего сумматоров, вторые входы которых соединены с вторыми выходами соответствующих буферных блоков, выходы сумматоров соединены с первыми входами соответствующих буферных блоков, выходы первого, второго и третьего регистров соединены с информационными входами элементов И-НЕ соответствующих групп, выходы элементов И-Н которых соединены с первыми входами соответствующих умнс кителей, вторые входы которых соединены с вторыми выходами соответствующ 1х буферных блокс)в, третьи входы умноя ителей соединены с первыми выходами соответствующих буферных блоков, первые выходы умножителей соединены с соответствующими входами блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые выходы умножителей соединены с вторыми, третьими и четвертыми входами каждого буферного блока, выход блока элементов ИСКЛЮЧАЩЕЕ ИЛИ соединен с управляющим входом блока управления первым управляющим входом блока выбора коэффициентов и с информационным входом четвертого регистра, выход которого соединен с первым информационным входом дешифратс| а и с информационном входом блока выбора коэффициентов, второй управляющий вход которого соединен с первым выходом блока управления и адресным входом дешифратора, второй информационный вход которого соединен с вторым выходом блока управления, йыход дешифратора подключен к входу блока памяти зон, выход которого соединен с чет вертыми входами умножителей, выход блока выбора коэффициентов подключен к пятым входам буферных блоков, первый выход третьего буферного блока и выходы третьей ( элементов И-НЕ соединены с входами сдвигателя, выход которого соединен с шестым входом третьего буферного блока, седьмой вход которого через блок вычисления обратной величины соединен с выходом сдвигателя, первый вход блока анализа знака соединен с первым входом первого буферного блока, информационные входы буферных блоков и входы с второТо по четвертый блока анализа знака являются информационными входами преобразователя, управляющие входы буферных регистров, групп элеменtoB И, умножителей, сдвигателя и блока выбора коэффициентов соединены соответственно с выходами первой, второй, третьей, четвертой,пятой и шестой групп блока управления, управляющие входы блока вычисления обратной величины и блока аЯализа знака соединены с третьим и четвертым выходами блока управления соответственно.

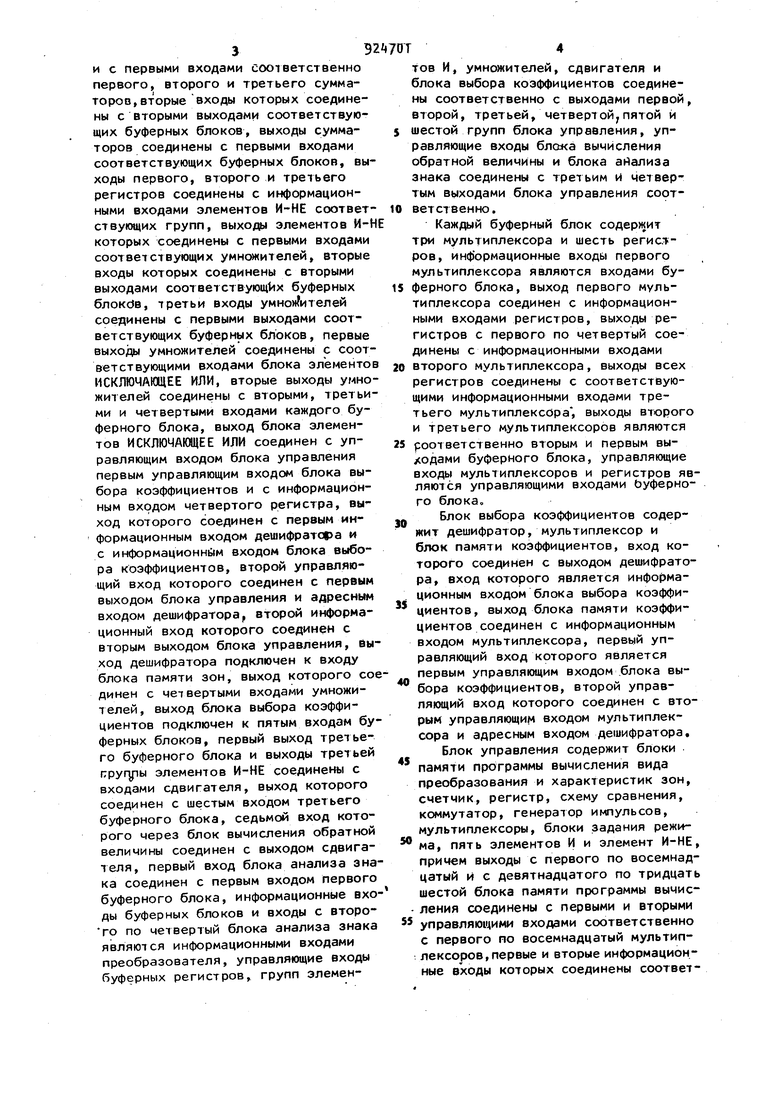

Каждый буферный блок содержит три мультиплексора и шесть регистров, информационные входы первого мультиплексора являются входами буферного блока, выход первого мульSтиплексора соединен с информационными входами регистров, выходы регистров с первого по четвертый соединены с информационными входами второго мультиплексора, выходы всех

0 регистров соединены с соответствующими информационными входами третьего мультиплексора, выходы второго и третьего мультиплексоров являются

S роответственно вторым и первым выходами буферного блока, управляющие

входь4 мультиплексоров и регистров являются управляющими входами Ьуферного блока.

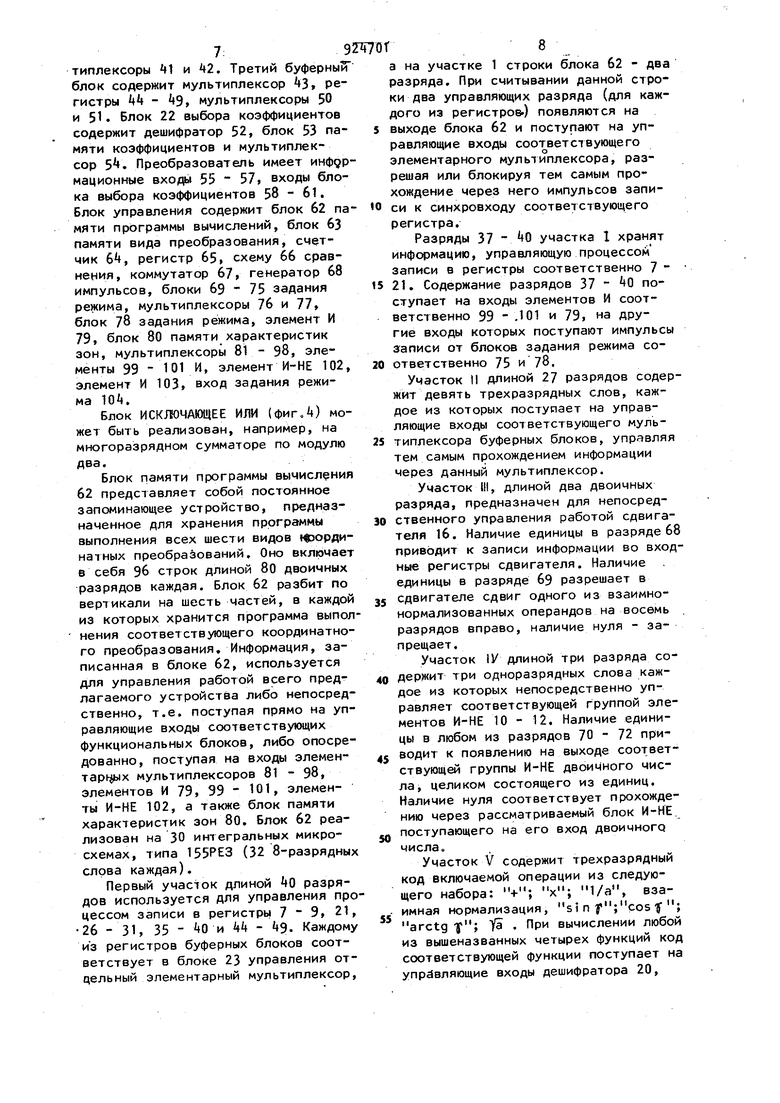

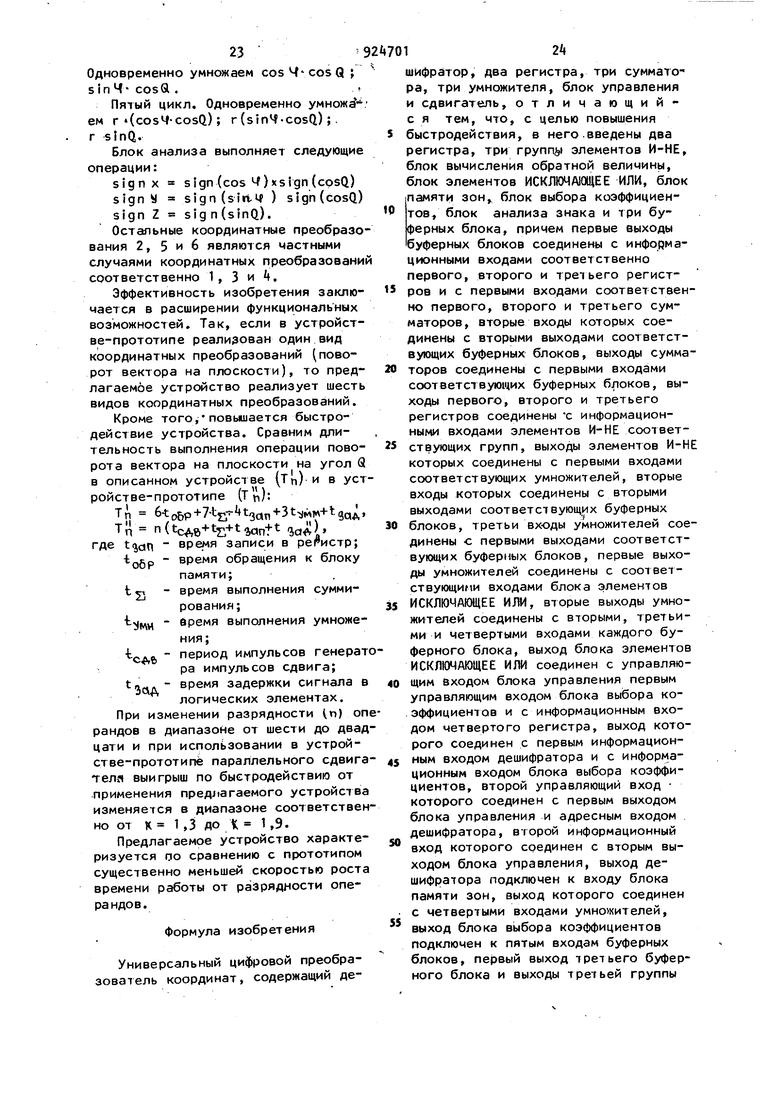

Блок выбора коэффициентов содер0жит дешифратор, мультиплексор и блок памяти коэффициентов, вход которого соединен с выходом дешифратора, вход которого является информационным входом блока выбора коэффи5циентов, выход блока памяти коэффициентов соединен с информационным входом мультиплексора, первый управляющий вход которого является первым управляющим входом блока вы0бора коэффициентов, второй управляющий вход которого соединен с вторым управляющим входом мультиплексора и адресным входом дешифратора.

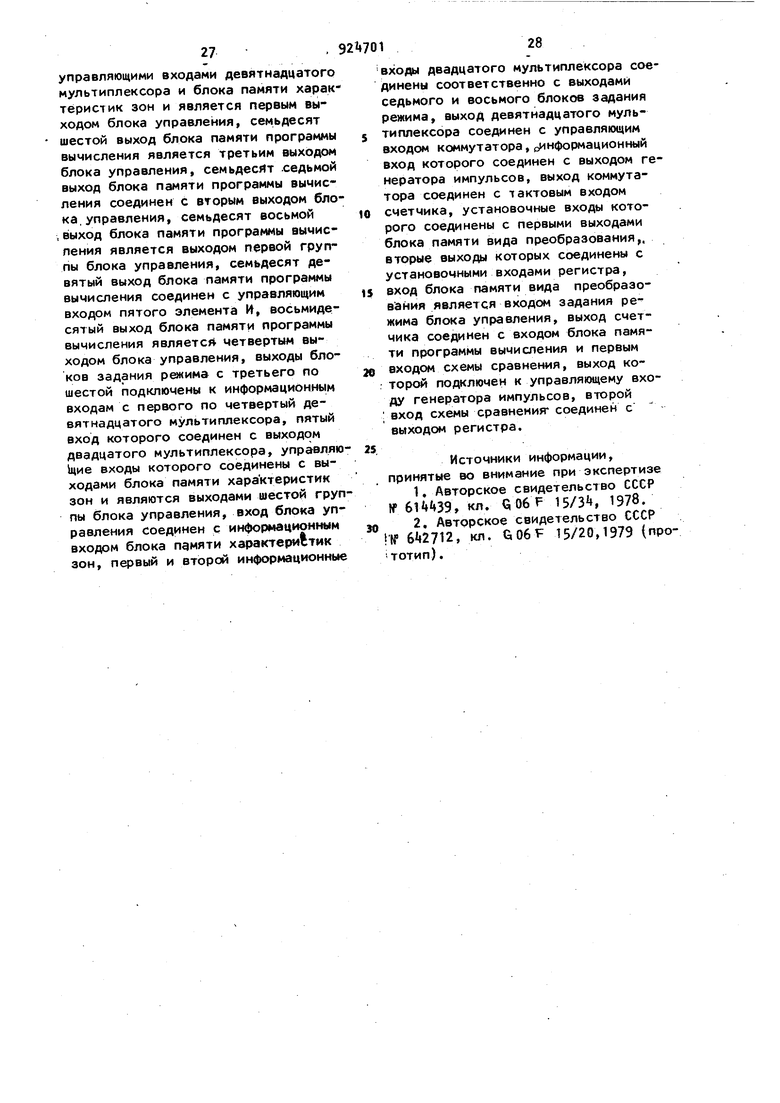

Блок управления содержит блоки

5 памяти программы вычисления вида преобразования и характеристик зон, счетчик, регистр, схему сравнения, коммутатор, генератор импульсов, мультиплексоры, блоки задания режи0ма, пять элементов И и элемент И-НЕ, причем выходы с первого по восемнадцатый и с девятнадцатого по тридцать шестой блока памяти программы вычисления соединены с первыми и вторыми

5 управляющими входами соответственно с первого по восемнадцатый мультиплексоров, пер вые и вторые информационные входы которых соединены соответственно с выходом первого блока задания режима и выходом девятнадцатого мультиплексора, выходы мультиплексоров с первого по восемнадцатый являются выходами nepBovi группы 6ло ка управления, выходы с тридцать седьмого по сороковой блока памяти программы вычисления соединены с управляющими входами соответственно с первого по четвертый элементов И, информационные входы с первого по третий элементов И соединены с выходом пе|Ьвого блока задания режима, вход которого соединен с выходом генератора импульсов и информационным входом пятого элемента И, выход которого соединен с входами с второго по восьмой блоков задания режима, выход второго блока задания режима соединен с информационным входом четвертого элемента И, выход которого соединен через элемент И-НЕ с вторым выходом блока управления , выход четвертого элемента И является выходом второй группы блока управления, выходы с сорок первого по шестьдесят седьмой блока памяти программы вычисления являются выходами первой группы блока управления, выходы шестьдесят и шестьдесят девятый блока памяти программы вычисления являются выходами пя;той группыблока управления, выходы ; с семидесятого по семьдесят второй блока памяти программы вычисления являются выходами третьей группы блока управления, выходы с семьдесят третьего по семьдесят пятый блока памяти программы вычисления соединены с управляющими входами девятнадцатого мультиплексора и блока памяти характеристик зон и является первым выходом блока управления, семьдесят шестой выход блока памяти программы вычисления является третьим выходом блока управления семьдесят седьмой выход блока памяти программы вычисления соединен с вторым выходом блока управления, семьдесят восьмой выход блока памяти программы вычисления является выходом первой группы блока управления, семьдесят девятый выход блока памяти программы вычисления соединен с управляющим входом пятого элемента И, восьмидесятый выход блока памяти программы вычисления является четвертым выходом блока управления, выходы блоков задания .режима с

третьего по шестой подключены к информационным входам с первого по четвертый девятнадцатого мультиплексора, пятый вход которого соединен с выходом двадцатого мультиплексора, управляющие входы которого соединены с выходами блока памяти характерис тик зон и являются выходами ufecтoй группы блока управления, вход блоке

управления соединен с информационным входом блока памяти характеристик зон, первый и второй информационные- входы двадцатого мультиплексора соединены соответственно с выходами седьмого и восьмого блоков задания режима, выход дeвяtнaдцaтo го мультиплексора соединен с управляющим входом коммутатора, информационный вход которого соединен с

выходом генератора импульсов, выход йоммутатора соединен с тактовым входом счетчика, установочные входы которого соединены с первыми выходами блока памяти вида преобразования,

вторые выходы которых соединены с установочными входами регистра, вход блока памяти вида преобразования является входом задания режима блока управления, выход счетчика соединен

с входом блока памяти программы вычисления и первым входом схемы сравнения, выход которой подключен к управлякяцему входу генератора импульсов, второй вход схемы сравнения соединей с выходом регистрао

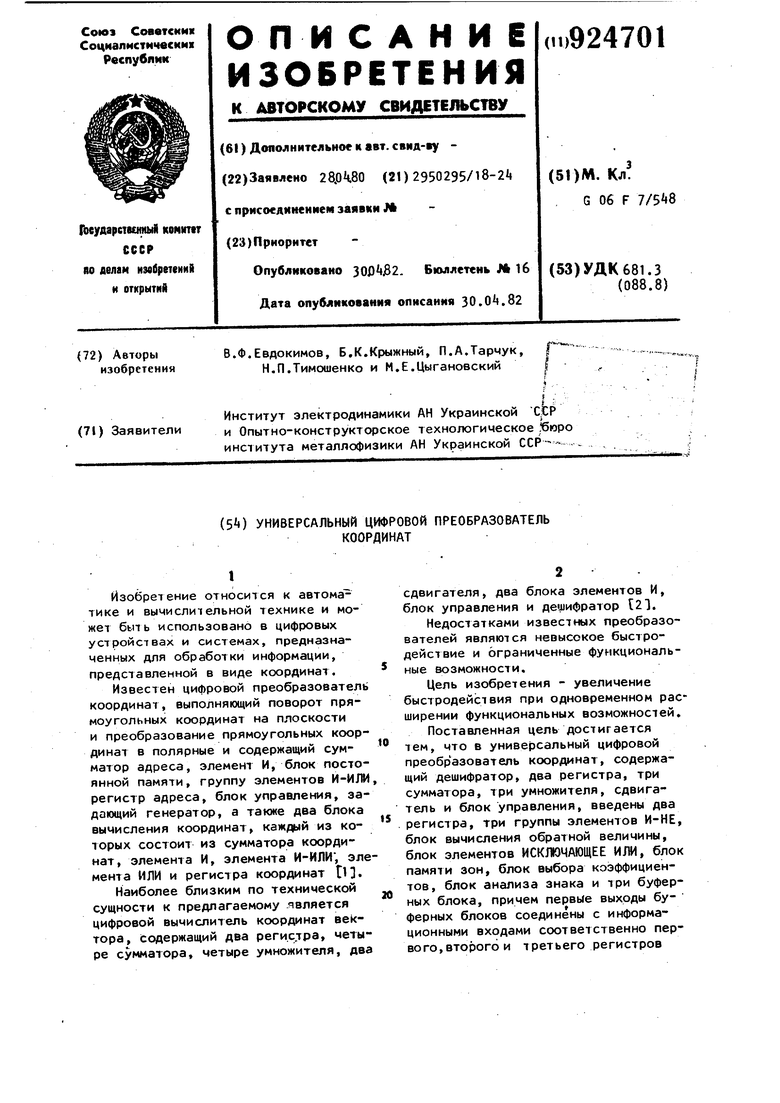

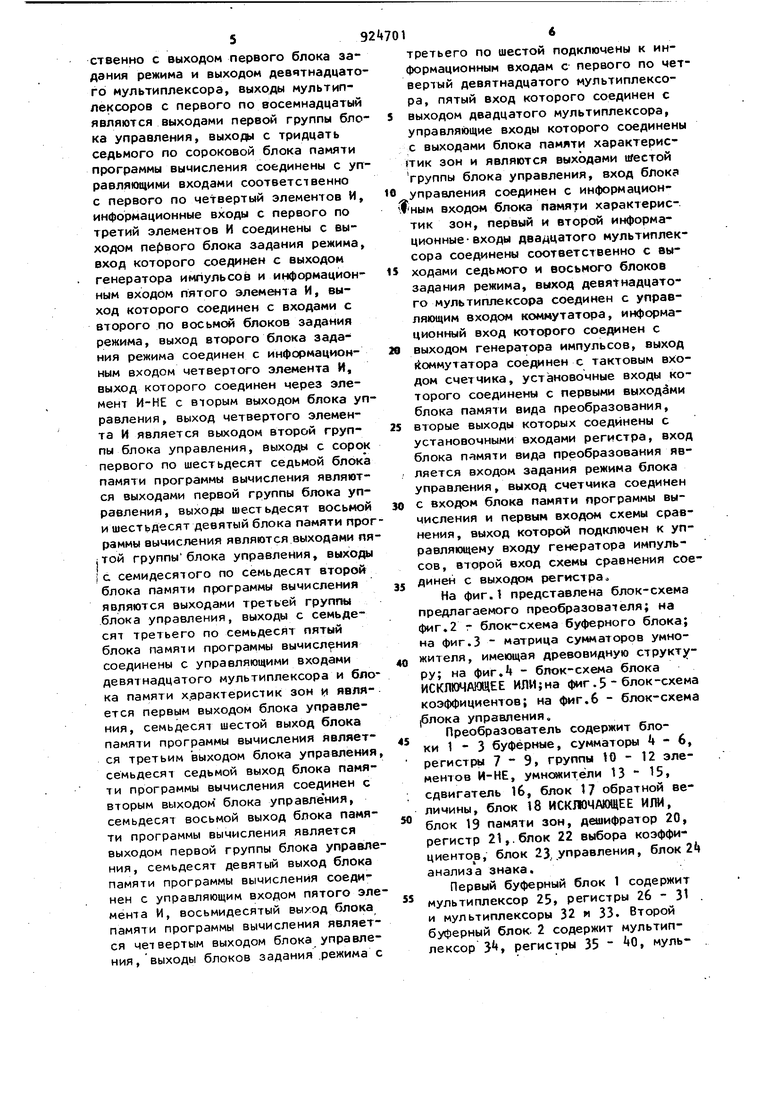

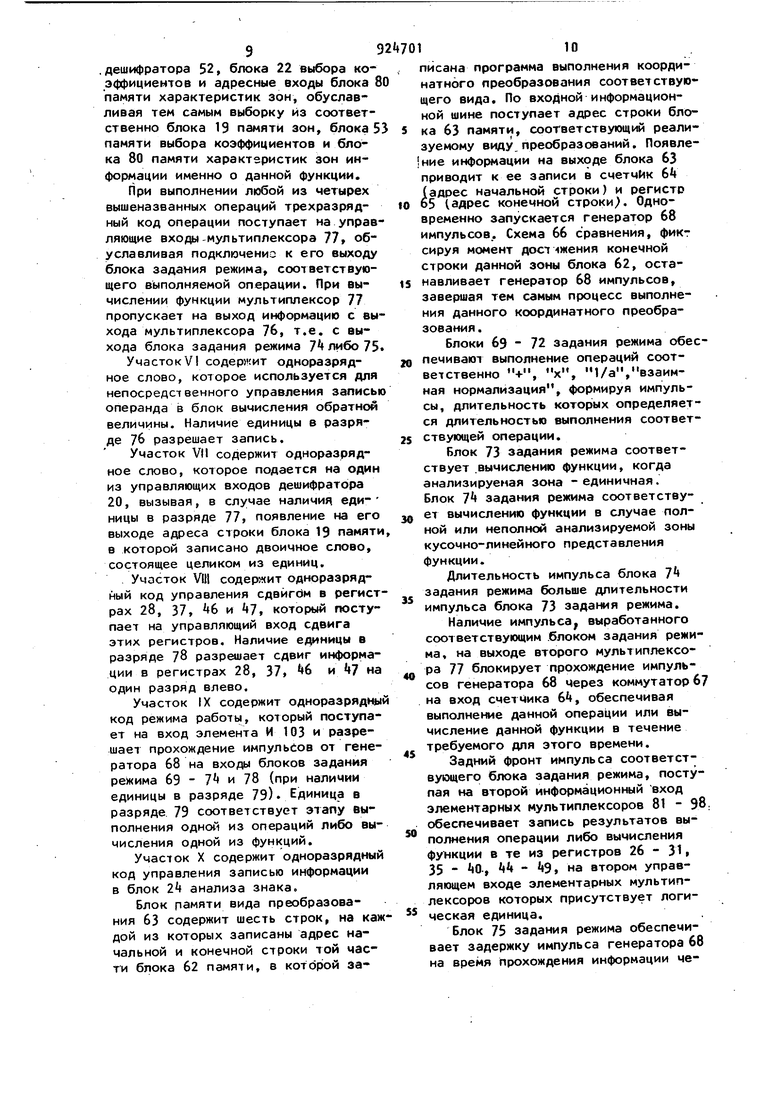

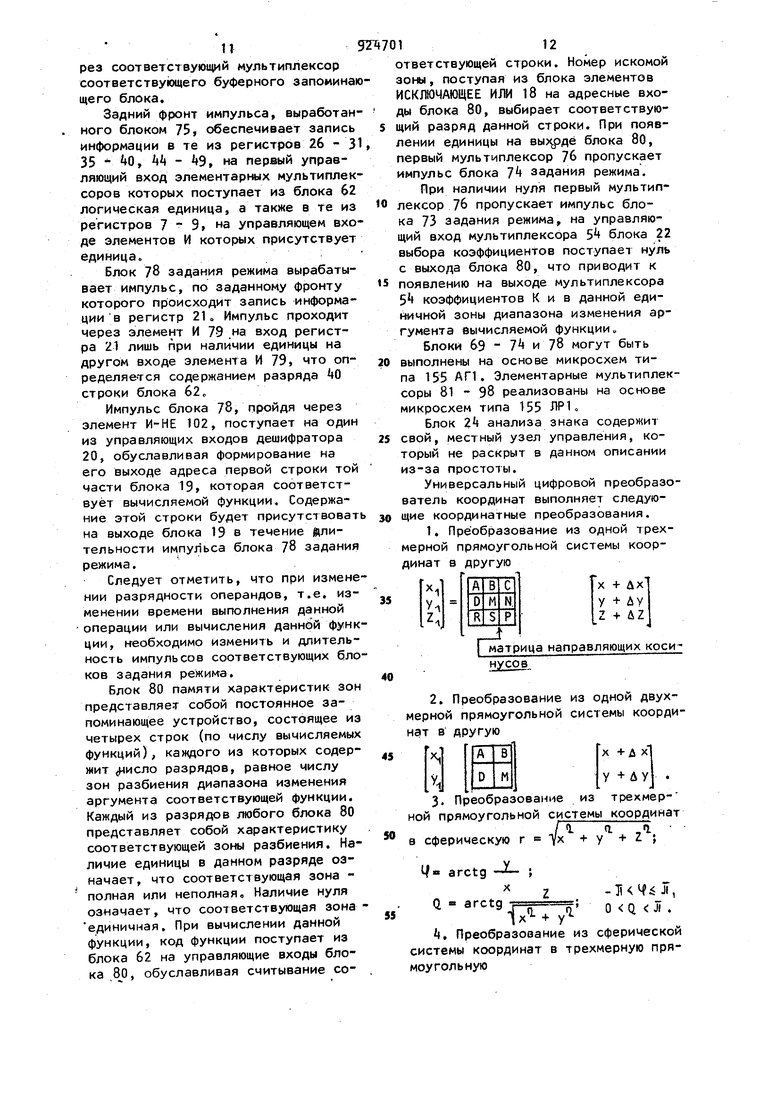

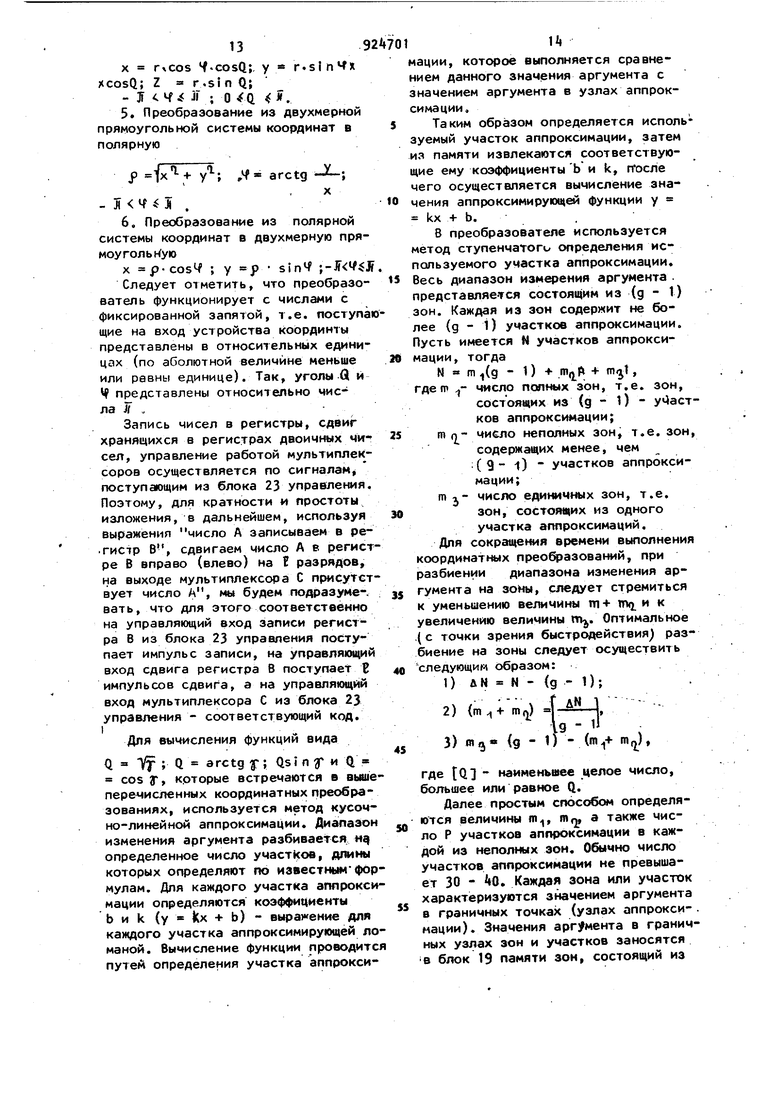

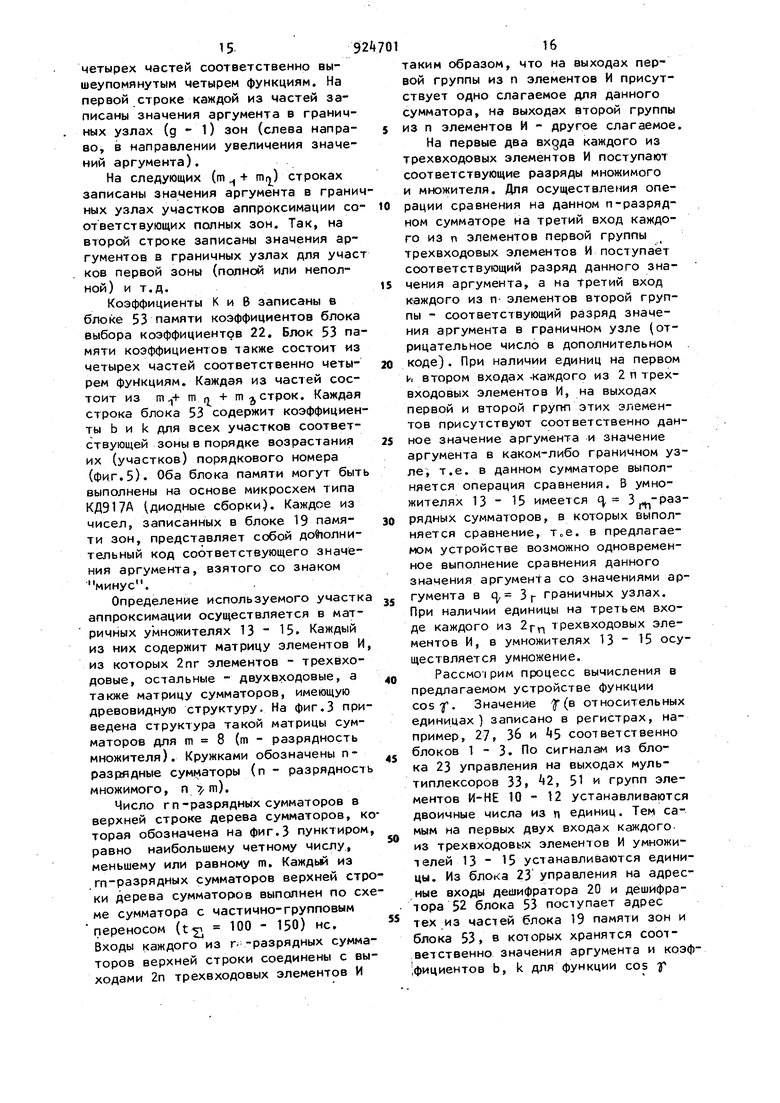

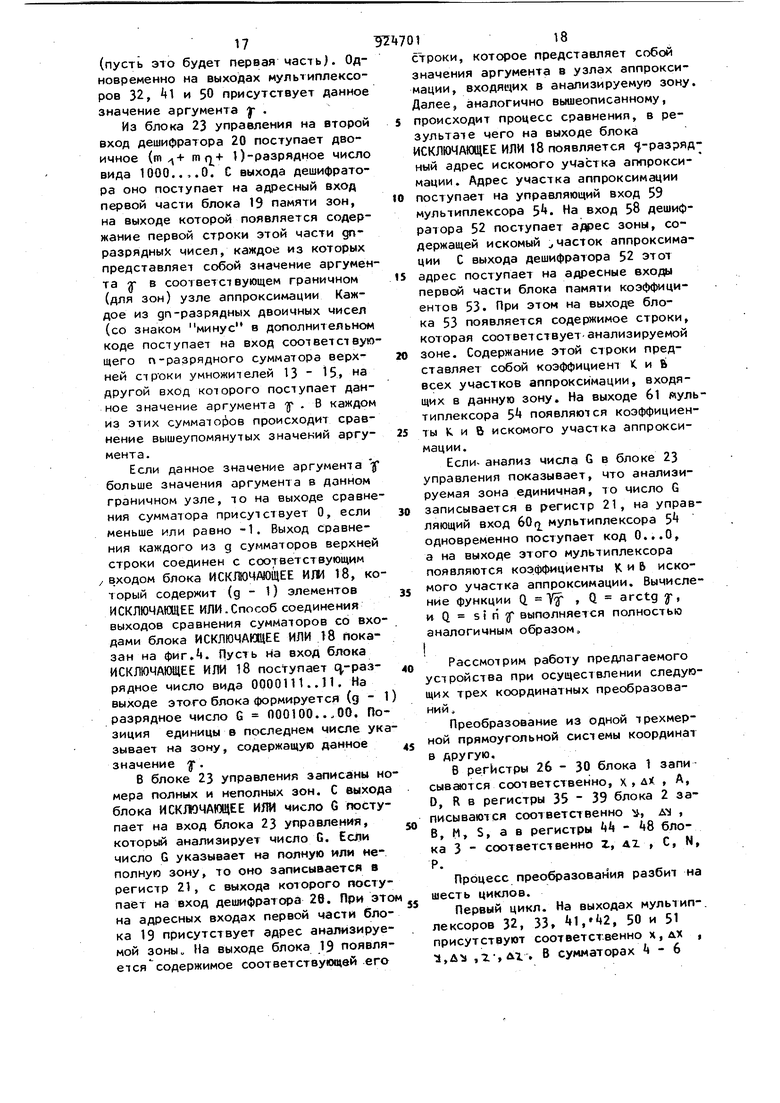

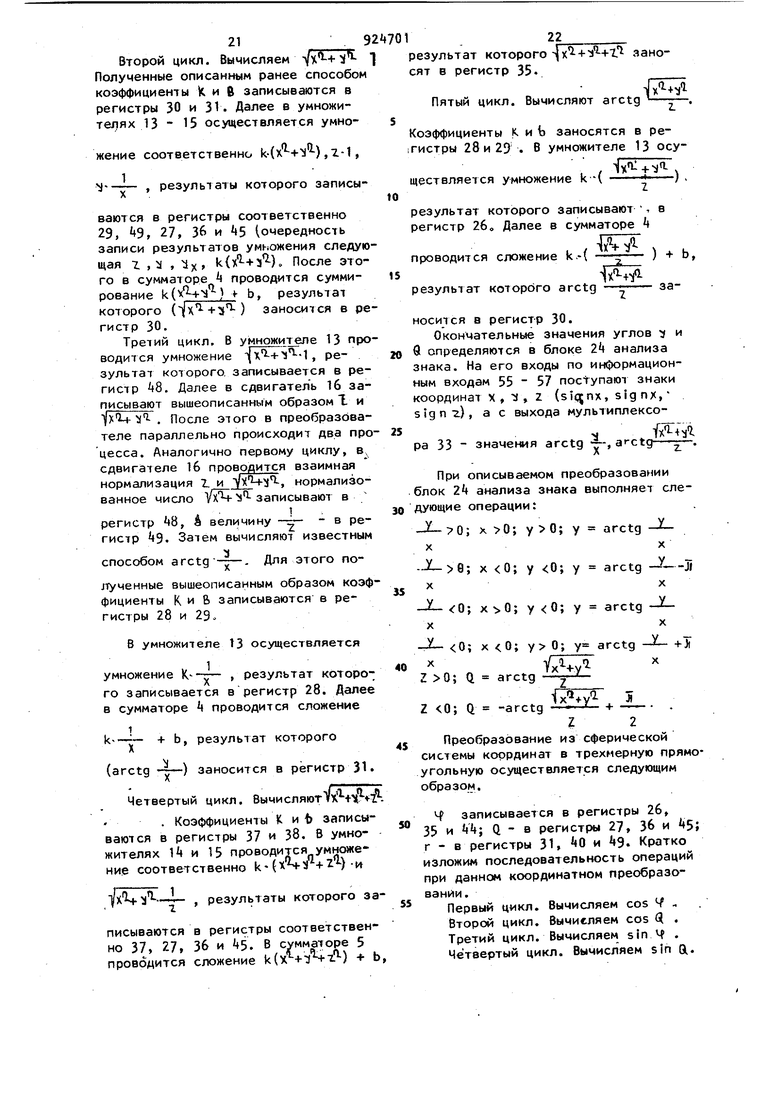

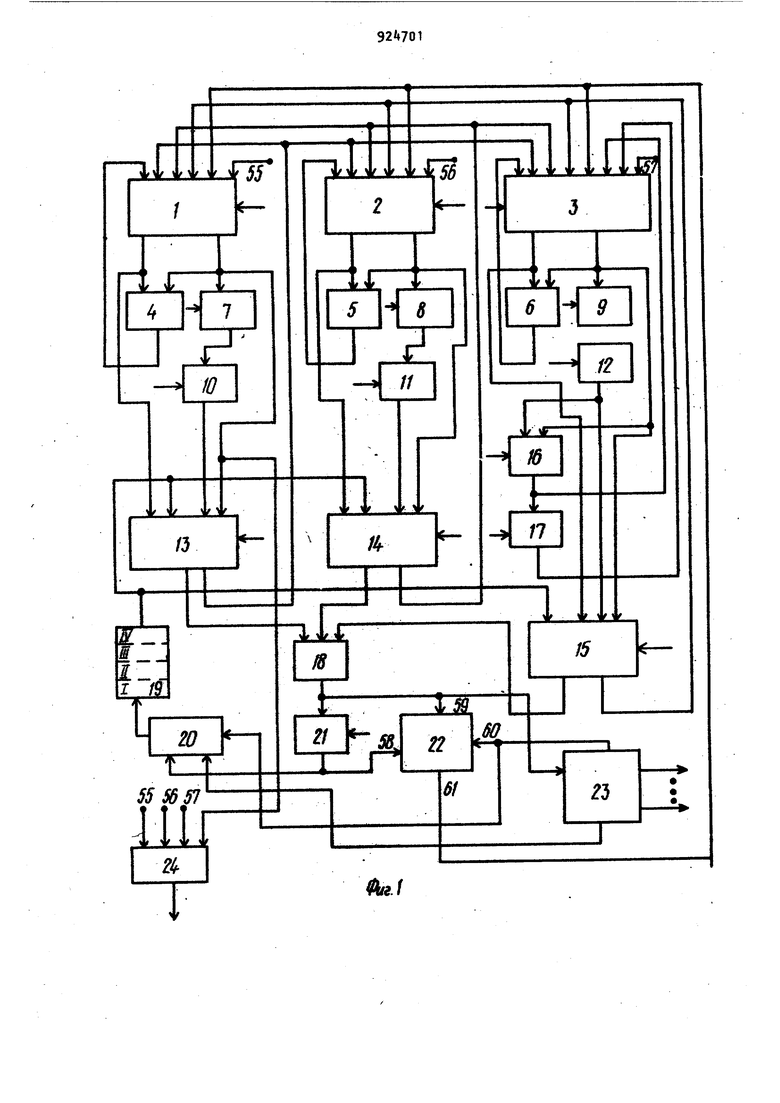

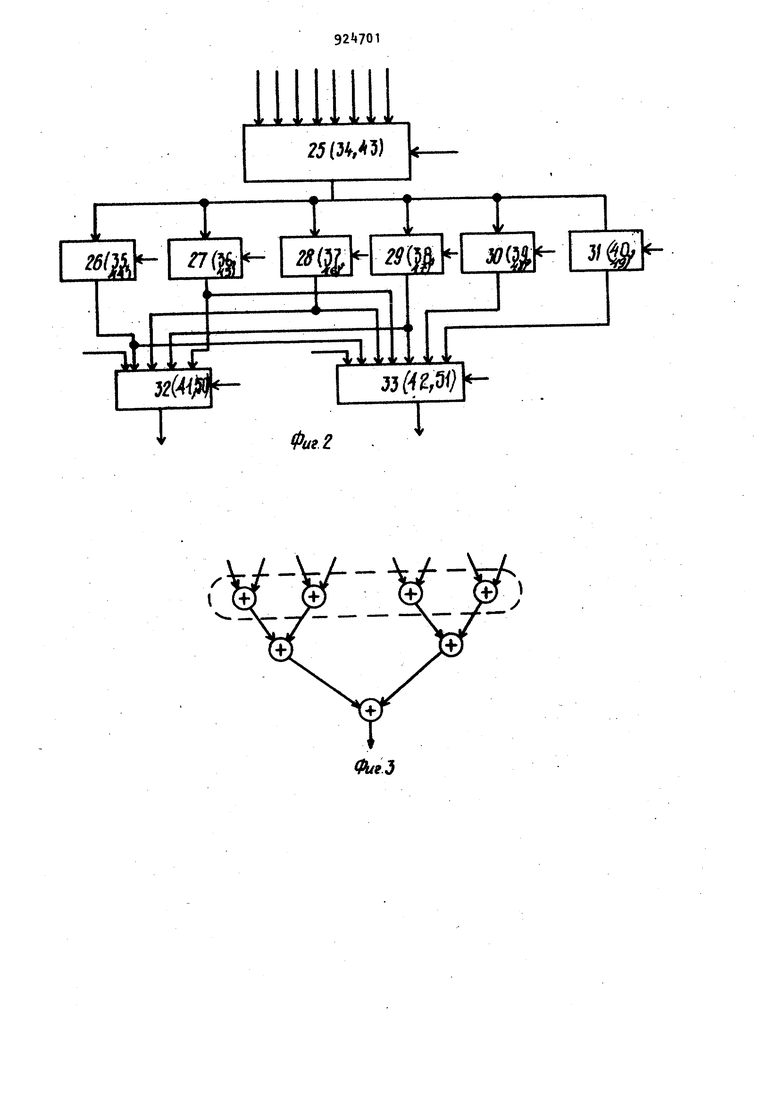

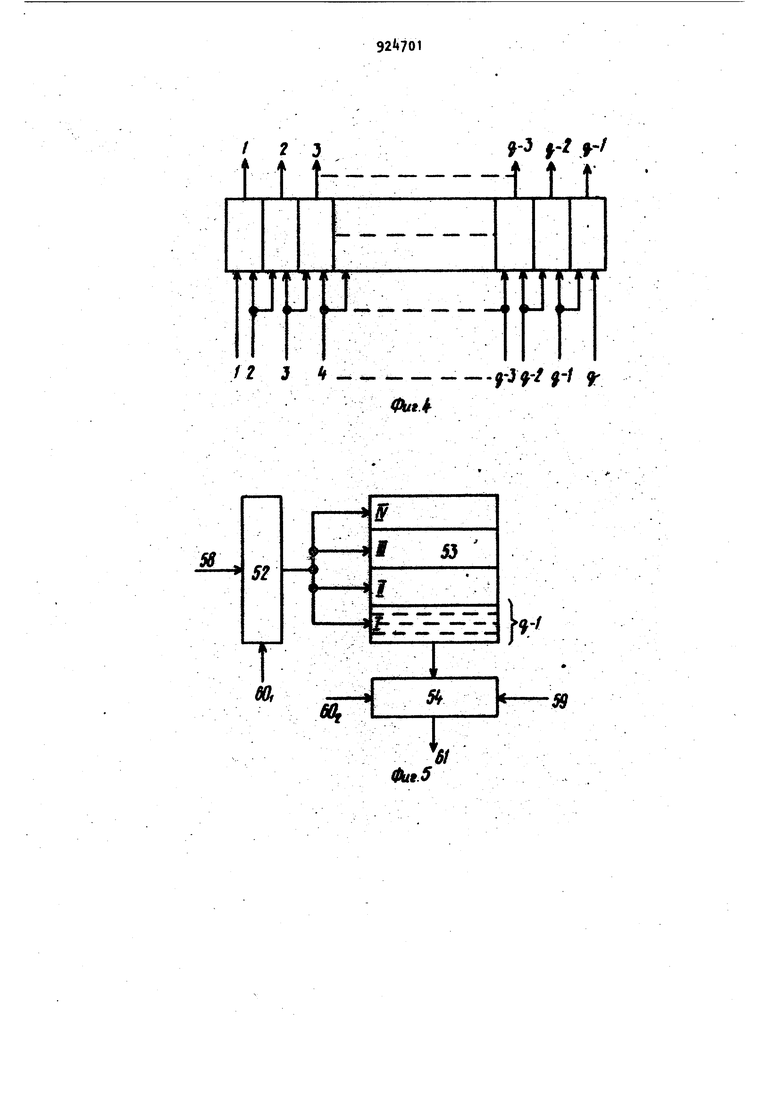

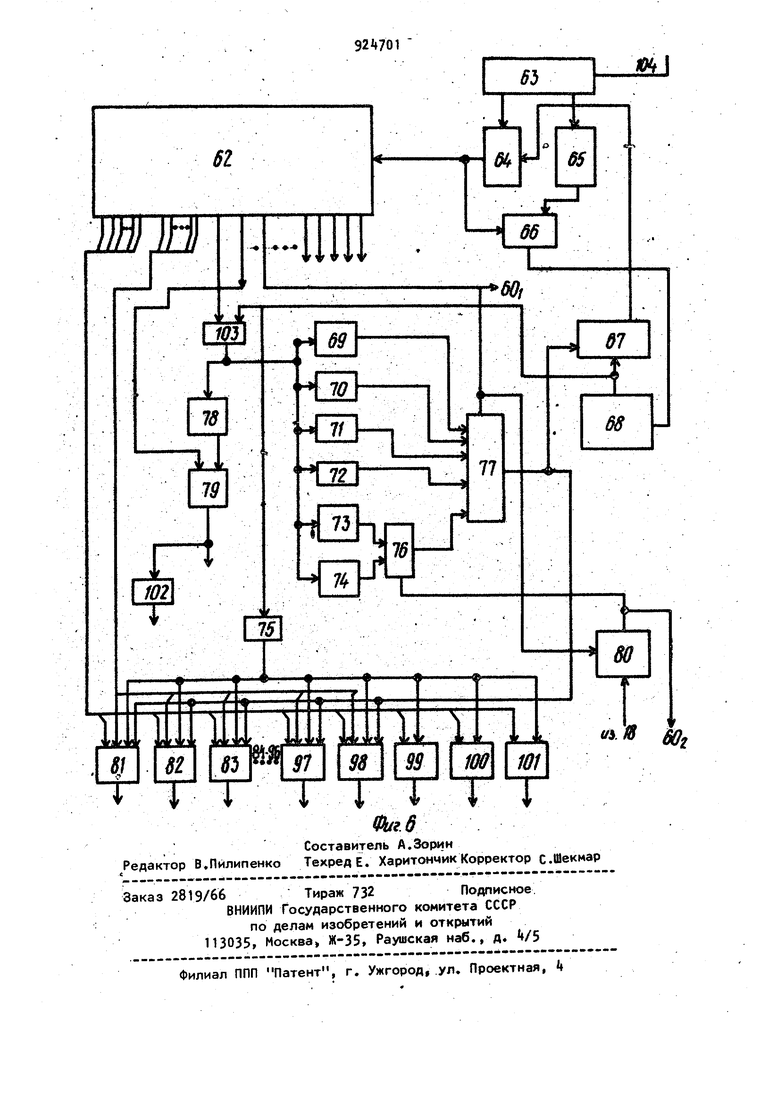

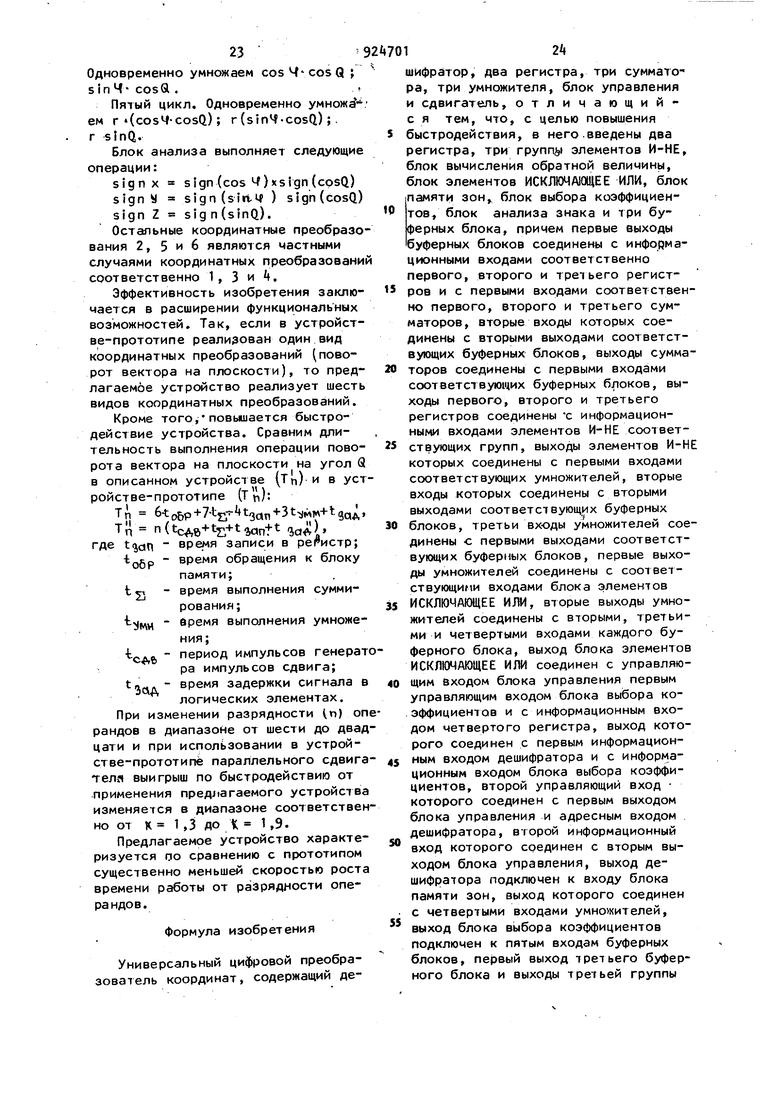

На фиг.1 представлена блок-схема предлагаемого преобразователя; на фиг.2 г блок-схема буферного блока; на фиг.З - матрица сумматоров умножителя, имеющая древовидную структуру; на фиг.и - блок-схема блока ИСКЛЮЧАЮЩЕЕ ИЛИ;на фиг.5 - блок-схема коэффициентов; на фиг.6 - блок-схема |блока управления.

Преобразователь содержит блоки 1 - 3 буферные, сумматоры 4-6, регистры 7-9, группы 10-12 элементов И-НЕ, умножит;ели 13 15, сдвигатель 16, блок 17 обратной величины, блок 18 ИСКЛЮЧАЮЩЕЕ ИЛИ,

блок 19 памяти зон, даиифратор 20, регистр 21,. блок 22 выбора коэффициентов, блок 23, управления, блок 2 анализа знака,

Первый буферный блок 1 содержит

мультиплексор 25, регистры 26-31 . и мультиплексоры 32 и 33. Второй буферный блок. 2 содержит мультиплексор 3, регистры 35 «О, мультиплексоры I и 42. Третий буферный блок содержит мультиплексор tS, регистры k - kS, мультиплексоры 50 и 5К Блок 22 выбора коэффициентов содержит дешифратор 52, блок 53 памяти коэффициентов и мультиплексор 5. Преобразователь имеет инф9Рмационные входа 55 57 входы блока выбора коэффициентов 58-61. Блок управления содержит блок 62 памяти программы вычислений, блок 63 памяти вида преобразования, счетчик 6, регистр б5, схему 66 сравнения, коммутатор 67, генератор 68 импульсов, блоки 69 75 задания режима, мультиплексоры 76 и 77, блок 78 задания режима, элемент И 79, блок 80 памяти характеристик зон, мультиплексоры 81 - 98, элементы 99-101 И, элемент И-НЕ 102, элемент И 103, вход задания режима lOt.

Блок ИСКЛОЧАЮЩЕЕ ИЛИ (фиг«4) может быть реализован, например, на многоразрядном сумматоре по модулю два.

Блок памяти программы вычисления 62 представляет собой постоянное запоминающее устройство, предназначенное для хранения программы выполнения всех шести видов 1фординатных преобразований. Оно включает в себя 96 строк длиной 80 двоичных разрядов каждая. Блок 62 разбит по вертикали на шесть частей, в каждой из которых хранится программа выполнения соответствующего координатного преобразования. Информация, записанная в блоке 62, используется для управления работой всего предлагаемого устройства либо непосредственно, т.е. поступая прямо на управляющие входы соответствующих функциональных блоков, либо опосредованно, поступая на входы элеменTaphjMx мультиплексоров 81 - 98, элементов И 79, 99 - 101, элементы И-НЕ 102, а также блок памяти характеристик зон 80. Блок 62 реализован на 30 интегральных микросхемах, типа 155РЕЗ (32 8-разрядных слова каждая).

Первый участок длиной Q разрядов используется для управления процессом записи в регистры 7-9, 21, 26-31, 35 - Ю и 44 - 49. Каждому из регистров буферных блоков соответствует в блоке 23 управления отцельный элементарный мультиплексор.

а на участке 1 строки блока 62 - два разряда. При считывании данной строки два управляющих разряда (для каждого из регистров.) появляются на 5 выходе блока б2 и поступают на управляющие входы соответс1вующего элементарного мультиплексора, разрешая или блокируя тем самым прохождение через него импульсов записи к синхровходу соответствующего регистра.

Разряды 37 участка I хранят инфсчэмацию, управляющую процессом записи в регистры соответственно 7 5 21. Содержание разрядов 37 - поступает на входы элементов И соответственно 99 - ,101 и 79, на другие входы которых поступают импульсы записи от блоков задания режима соответственно 75 и 78.

Участок 11 длиной 27 разрядов содержит девять трехразрядных слов, каждое из которых поступает на управляющие входы соответствующего мультиплексора буферных блоков, управляя тем самым прохождением информации через данный мультиплексор.

Участок 111, длиной два двоичных разряда, предназначен для непосредственного управления работой сдайгателя 16. Наличие единицы в разряде 68 приводит к записи информации во входные регистры сдвигателя. Наличие . единицы в разряде 69 разрешает в

сдвигателе сдвиг одного из взаимнонормализованных операндов на восемь разрядов вправо, наличие нуля - запрещает.

Участок 11 длиной три разряда содержит три одноразрядных слова каждое из которых непосредственно управляет соответствующей группой элементов И-НЕ 10 - 12. Наличие единицы в любом из разрядов 70 - 72 приводит к появлению на выходе соответствующей группы И-НЕ двоиМного числа, целиком состоящего из единиц. Наличие нуля соответствует прохождению через рассматриваемый блок И-НЕ. поступающего на его вход двоичного числа.

Участок V содержит трехразрядный код включаемой операции из следую х ; 1/а,

Mill.

щего набора: +

взаII. ,

имная нормализация, siп arctg I/a . При вычислении любой из вышеназванных четырех функций код соответствующей функции поступает на управляющие входы дешифратора 20, .дешифратора 52, блока 22 выбора )фициентов и адресные входы блока памяти характеристик зон, обуславливая тем самым выборку из соответственно блока 19 памяти зон, блока 5 памяти выбора коэффициентов и блока 80 памяти характеристик зон информации именно о данной функции. При выполнении любой из четырех вышеназванных операций трехразрядный код операции поступает на управ ляющие входы-мультиплексора 77, обуславливая подключение к его выходу блока задания режима, соо1ветствующего выполняемой операции. При вычислении функции мультиплексор 77 пропускает на выход информацию с вы хода мультиплексора 76, т.е. с выхода блока задания режима 7 либо 75 Участок V содержит одноразрядное слово, которое используется для непосредственного управления запись операнда в блок вычисления обратной величины. Наличие единицы в разряде 7б разрешает запись. Участок VII содержит одноразрядное слово, которое подается на один из управляющих входов дешифратора 20, вызывая, в случае наличия еди- ницы в разряде 77, появление на его выходе адреса строки блока 19 памяти в которой записано двоичное слово, состоящее целиком из единиц. Участок VIII содержит одноразрядный код управления сдвигам в регист рах 28, 37, tS и , который поступает на управляющий вход сдвига этих регистров. Наличие единицы в разряде 78 разрешает сдвиг информации в регистрах 28, 37, и на один разряд влево. Участок IX содержит одноразрядны код режима работы, который поступает на вход элемента И 103 и разрешает прохождение импульсов от генератора 68 на входы блоков задания режима 69 - 7 и 78 (при наличии единицы в разряде 79). Единица в разряде 79 соответствует этапу выполнения одной из операций либо вычисления одной из функций. Участок X содержит одноразрядный код управления записью информации в блок 2 анализа знака. Блок памяти вида преобразования 63 содержит шесть строк, на каж дои из которых записаны адрес начальной и конечной строки той части блока 62 памяти, в которой записана программа выполнения координатного преобразования соответствующего вида. По входной информационной шине поступает адрес строки блока 63 памяти, соответствующий реализуемому виду преобразований. Появле|ние информации на выходе блока 63 приводит к ее записи в счетчИк 6 (адрес начальной строки) и регистр 65 (адрес конечной строки. Одновременно запускается генератор 68 импульсов. Схема 66 сравнения, фикт сируя момент дост 1жения конечной строки данной зоны блока 62, останавливает генератор 68 импульсов, завершая тем самым процесс выполнения данного координатного преобразования . Блоки б9 - 72 задания режима обеспечивают выполнение операций соот1/а,взаим11.11 |1„И II ветственно ная нормализация , формируя импульсы, длительность которых определяется длительностью выполнения соответствующей операции. Блок 73 задания режима соответствует .вычислению функции, когда анализируемая зона -единичная. Блок 7 задания режима соответствует вычислению функции в случае полной или неполной анализируемой зоны кусочно-линейного представления функции. Длительность импульса блока 7 задания режима больше длительности импульса блока 73 задания режима. Наличие импульса, выработанного соответствующим .блоком задания режима, на выходе второго мультиплексора 77 блокирует прохождение импульсов генератора 68 через коммутатор 67 на вход счетчика 6, обеспечивая выполнение данной операции или вычисление данной функции в течение требуемого для этого времени. Задний фронт импульса соответствующего б.лока задания режима, поступая на второй информационный вход э.лементарных мультиплексоров 81 - 98; обеспечивает запись результатов выполнения операции либо вычисления в те из регистров 26 - 311 35 - , « - 49, на втором управляющем входе элементарных мультиплексоров которых присутствует логическая единица. Блок 75 задания режима обеспечивает задержку импульса генератора 68 на время прохождения информации через соответствующий мультиплексор соответствующего буферного запомина щего блока. Задний фронт импульса, выработан ного блоком 75, обеспечивает запись информации в те из регистров 26 - 3 35 - 0, kk - kS, на первый управляющий вход элементарных мультиплек соров которых поступает из блока 62 логическая единица, а также в те из регистров 7 - 9, на управляющем вхо де элементов И которых присутствует единица. Блок 78 задания режима вырабатывает импульс, по заданному фронту которого происходит запись информации в регистр 21 о Импульс проходит через элемент И 78 .на вход регистра 21 лишь при наличии единицы на другом входе элемента И 79, что определяе-тся содержанием разряда 0 строки блока 62,, Импульс блока 78, пройдя через элемент И-НЕ 102, поступает на один из управляющих входов дешифратора 20, обуславливая формирование на его выходе адреса первой строки той части блока 19, которая соответствует вычисляемой функции. Содержание этой строки будет присутствоват на выходе блока 19 в течение длительности импульса блока 78 задания режима. Следует отметить, что при измене нии разрядности операндов, т.е. изменении времени выполнения данной операции или вычисления данной функ ции, необходимо изменить и длительность импульсов соответствующих бло ков задания режима. Блок 80 памяти характеристик зон представляет собой постоянное запоминающее устройство, состоящее из четырех строк (по числу вычисляемых функций), каждого из которых содержит исло разрядов, равное числу зон разбиения диапазона изменения аргумента соответствующей функции. Каждый из разрядов любого блока 80 представляет собой характеристику соответствующей зоны разбиения. Наличие единицы в данном разряде означает, что соответствующая зона полная или неполная. Наличие нуля означает, что соответствующая зона единичная. При вычислении данной функции, код функции поступает из блока 62 на управляющие входы блока 80, обуславливая считывание соответствующей строки. Номер искомой зоны, поступая из блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 18 на адресные входы блока 80, выбирает соответствующий разряд данной строки. При появлении единицы на блока 80, первый мультиплексор 76 пропускает импульс блока 7 задания режима. При наличии нуля первый мультиплексор 76 пропускает импульс блока 73 задания режима, на управляющий вход мультиплексора 5 блока 22 выбора коэффициентов nocrynaei нуль с выхода блока 80, что приводит к появлению на выходе мультиплексора 5 коэффициентов К и в данной единичной зоны диапазона изменения аргумента вычисляемой функции Блоки б9 - 7 и 78 могут быть выполнены на основе микросхем типа 155 АГ1. Элементарные мультиплексоры 81 - 98 реализованы на основе микросхем типа 155 ЛР1, Блок 2 анализа знака содержит свой, местный узел управления, который не раскрыт в данном описании из-за простоты. Универсальный цифровой преобразователь координат выполняет следующие координатные преобразования. 1. Преобразование из одной трехмерной прямоугольной системы координат в другую X + лх У + ДУ Z + UZ f матрица направляющих косинусов2. Преобразование из одной двухмерной прямоугольной системы координат в другую 3. Преобразование из трехмерной прямоугольной системы координат Гг о Га в сферическую г х + у + Z ; Ч arctg - ; JF, Q- arctg о Q Ji. ix- + Преобразование из сферической системы координат в трехмерную прямоугольную139 X гчсоз Ч-cosQ;. у « r.sin4x xcosQ; Z г.si n Q; - Л Ч JF ; 0 Q . 5. Преобразование из двухмерной прямоугольной системы координат в полярную J5 Л-arctg-i ; - Ji f Л . 6. Преобразование из полярной системы координат в двухмерную прямоугольИуюX p-cos4 ; у -р , Следует отметить, что преобразователь функционирует с числами с фиксированной запятой, т.е. поступа щие на вход устройства координты представлены в относительных единицах (по аболютной величине меньше или равны единице). Так, уголы (И и представлены относительно числа JT . Запись чисел в регистры, сдвиг хранящихся в регистрах двоичных чи сел, управление работой мультиплексоров осуществляется по сигналам поступающим из блока 23 управления. Поэтому, для кратности и простоты изложения, в дальнейшем, используя выражения число А записываем в ре гистр В , сдвигаем число А в регист ре В вправо (влево) на f разрядов, на выходе мультиплексора С присутст вует число А, мы будем подразуме-. вать, что для этого соответственно на управляющий вход записи регистра В из блока 23 управления поступает импульс записи, на управляющий вход сдвига регистра В поступает В импульсов сдвига, а на управляющий вход мультиплексора С из блока 23 управления - соответствующий код. I. , Для вычисления функций вида Q tf ; Q arctgy; Qsinf и Q cos Г, которые встречаются в вьвие перечисленных координатных преобразованиях, используется метод кусочно-линейной аппроксимации. Диапазон изменения аргумента разбивается щ определенное число участЦов, дтны которых определяют по известным фор мулам. Для каждого участка аппрокси мации определяются козффи14Иеиты b и k (у Кх + b) - выражение для каждого участка аппроксимирующей ло маной. Вычисление функции проводитс путем определения участка аппроксимации, которое выполняется сравнением данного значения аргумента с значением аргумента в узлах аппроксимации. Таким образом определяется исполь зуемый участок аппроксимации, затем из памяти извлекаются соответствующие ему коэффициенты Ъ и k, rfoctie чего осуществляется вычисление значения аппроксимирующей функции у kx + Ь. В преобразователе используется метод ступенчатого определения используемого участка аппроксимации. Весь диапазон измерения аргумента . представляется состоящим из (д - 1) зон. Каждая из зон содержит не более (д - 1) участков аппроксимации. Пусть имеется Н участков аппроксимации, тогда N m (g - 1) + .1Чп f + i гдеm - число полных зон, т.е. зон, состоящих из (д - 1) - у 4астков аппроксимации; m n- число неполных зон, т.е. зон, содержащих менее, чем (9- 1) участков аппроксимации;m J- число единичных зон, т.е. зон, состоящих из одного участка аппроксимаций. Для сокращения времени выполнения координатных преобразований, при разбиении диапазона изменения аргумента на зоны, следует стремиться к уменьшению величины m + nv. и к увеличению величины т. Оптимальное ,{с точки зрения быстродействия) разбиение на зоны следует осуществить следующим образом: 1) Д N N - (д - 1); 2)(m + m,) .9 - 1 - ( mj. 3)ma {g - 1 где tQl наименьшее целое число, бояьшее или равное Q. Далее простым способом определяются величины т, т а также число Р участков аппроксимации в каждой из неполных зон. Обычно число участков аппроксимации не превышает 30 - lO. Каждая зона или участок характеризуются значением аргумента в граничных точках (узлах аппрокси мации). Значения аргумента в граничных узлах зон и участков заносятся в блок 19 памяти зон, состоящий из 159 четырех частей соответственно вышеупомянутым четырем функциям. На первой строке каждой из частей записаны значения аргумента в граничных узлах (д - 1) зон (слева направо, в направлении увеличения значений аргумента). На следующих (т + т, строках записаны значения аргумента в грани ных узлах участков аппроксимации со ответствующих полных зон. Так, на второй строке записаны значения аргументов в граничных узлах для учас ков первой зоны (полной или неполной) и т.д. Коэффициенты К и В записаны в блоке 53 памяти коэффициентов блока выбора коэффициентов 22. Блок 53 па мяти коэффициентов также состоит из четырех частей соответственно четырем функциям. Каждая из частей состоит из т-,+ m 0 + m строк. Каждая строка блока 53 содержит коэффициен ты Ь и k для всех участков соответствующей зоны в порядке возрастания их (участков) порядкового номера (фиг.5). Оба блока памяти могут быт выполнены на основе микросхем типа КД917А (диодные сборки). Каждое из чисел, записанных в блоке 19 памяти зон, представляет собой дойюлнительный код соответствующего значения аргумента, взятого со знаком минус.. Определение используемого участк аппроксимации осуществляется в матричных умножителях 13 - 15. Каждый из них содержит матрицу элементов И из которых 2пг элементов - трехвходовые, остальные - двухвходовые, а также матрицу сумматоров, имеющую древовидную структуру. На фиг.З при ведена структура такой матрицы сумматоров для m 8 (m - разрядность множителя). Кружками обозначены празрядные сумк1аторы (п - разрядност множимого, п т). Число г п-разрядных сумматоров в верхней строке дерева сумматоров, к торая обозначена на фиг.З пунктиром равно наибольшему четному ЧИСЛУ, меньшему или равному т. Каждый из гп-разрядных сумматоров верхней стр ки дерева сумматоров выполнен по сх ме сумматора с частично-групповым переносом (t ЮО - 150) не. Входы каждого из г -разрядных сумма торов верхней строки соединены с вы ходами 2п трехвходовых элементов И таким образом, что на выходах первой группы из п элементов И присутствует одно слагаемое для данного сумматора, на выходах второй группы из п элементов И - другое слагаемое. На первые два вхдда каждого из трехвходовых элементов И поступают соответствующие разряды множимого и множителя. Для осуществления операции сравнения на данном п-разрядном сумматоре на третий вход каждого из п элементов первой группы трехвходовых элементов И поступает соответствующий разряд данного значения аргумента, а на третий вход каждого из п элементов второй группы - соответствующий разряд значения аргумента в граничном узле (отрицательное число в дополнительном . коде). При наличии единиц на первом k втором входах -каждого из 2 п трехвходовых элементов И, на выходах первой и второй групл этих элементов присутствуют соответственно данное значение аргумента и значение аргумента в каком-либо граничном узле, т.е. в данном сумматоре выполняется операция сравнения. В умножителях 13 - 15 имеется cj, 3,.-разрядных сумматоров, в которых выполняется сравнение, Тс,е. в предлагаемом устройстве возможно одновременное выполнение сравнения данного значения аргумента со значениями аргумента в q, Зр граничных узлах. При наличии единицы на третьем входе каждого из 2 трехвходовых элементов И, S умножителях 13 - 15 осуществляется умножение. Рассмо1 РИМ процесс вычисления в предлагаемом устройстве функции cos-jf. Значение (в относительных единицах) записано в регистрах, например, 27, 36 и 5 соответственно блоков 1 - 3. По сигналам из блока 23 управления на выходах мультиплексоров 33, , 51 и групп элементов И-НЕ 10 - 12 устанавливаются двоичные числа из г единиц. Тем самым на первых двух входах каждого из трехвходовкх элементов И умножи1 елей 13 - 15 устанавливаются единицы. Из блока 23 управления на адресные входы дешифратора 20 и дешифратора 52 блока 53 поступает адрес тех из частей блока 19 памяти зон и блока 53, в которых хранятся соответственно значения аргумента и коэффициентов Ь, k для функции cos у (пусть это будет первая часть). Одновременно на выходах мультиплексоров 32, k и 50 присутствует данное значение аргумента f , Из блока 23 управления на второй вход дешифратора 20 поступает двоичное (т + 0-разрядное число вида 1000..,.0. С выхода дешифратора оно поступает на адресный вход части блока 19 памяти зон, на выходе которой появляется содержание первой строки этой части gnразрядных чисел, каждое из которых представляет собой значение аргумен та в соответствующем граничном (для зон) узле аппроксимации Каждое из дп-разрядных двоичных чисел (со знаком минус в дополнительном коде поступает на вход соответствую щего п-разрядного сумматора верхней строки умножителей 13 - 15 на другой вход которого поступает данное значение аргумента - . В каждом из этих сумматоров происходит сравнение вышеупомянутых значений аргумента. Если данное значение аргумента Y больше значения аргумента в данном граничном узле, то на выходе сравне ния сумматора присутствует О, если меньше или равно -1. Выход сравнения каждого из g сумматоров верхней строки соединен с соответствующим входом блока ИСКЛЮЧАЮЩЕЕ ИЛИ 18, ко торый содержит (g - 1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.Способ соединения выходов сравнения сумматоров со входами блока ИСКЛЮЧАЮЩЕЕ ИЛИ 8 показан на фиг,. Пусть На вход блока ИСКЛЮЧАЮЩЕЕ ИЛИ 18 поступает С|,-разрядное число вида 0000111..11. На выходе этого блока формируется (g разрядное число G П00100...00. Позиция единицы в последнем числе ука зывает на зону, содержащую данное значение -у. В блоке 23 управления записаны но мера полных и неполных зон. С выхода блока ИСКЛЮЧАЮЩЕЕ ИЛИ число G поступает на вход блока 23 управления, который анализирует число G. Если число G указывает на полную или неполную зону, то оно записывается в регистр 21, с выхода которого поступает на вход дешифратора 28. При это на адресных входах первой части блока 19 присутствует адрес анализируемой зоны„ На выходе блока 19 появляется содержимое соответствукицвй его строки, котсЧ)ое представляет собой значения аргумента в узлах аппроксимации, входящих в анализируемую зону. Далее, аналогично вышеописанному, происходит процесс сравнения, в результате чего на выходе блока ИСКЛЮЧАЮЩЕЕ ИЛИ 18 появляется -разрядный адрес искомого участка аппроксимации. Адрес участка аппроксимации поступает на управляющий вход 59 мультиплексора З. На вход 58 дешифратора 52 поступает адрес зоны, содержащей искомый j4acTOK аппроксимации С выхода дешифратора 52 этот адрес поступает на адресные входы первой части блока памяти коэффициентов 53. При этом на выходе блока 53 появляется содержимое строки, которая соответствует-анализируемой зоне. Содержание этой строки представляет собой коэффициент К. и Ь всех участков аппроксимации, входящих в данную зону. На выходе б1 мультиплексора 5 появляются коэффициенты К. и В искомого участка аппроксимации. Если- анализ числа G в блоке 23 управления показывает, что анализируемая зона единичная, то число G записывается в регистр 21, на управляющий вход 60f2 мультиплексора 5 одновременно поступает код 0...0, а на выходе этого мультиплексора появляются коэффициенты К и Ь искомого участка аппроксимации. Вычисление функции О, УЗ . Q arctg у, и Q S{ п у выполняется полностью аналогичным образом, Рассмотрим работу предлагаемого устройства при осуществлении следующих трех координатных преобразованийПреобразование из одной трехмерной прямоугольной сист емы координат в другую. В регистры 26 - 30 блока 1 записываются соответственно, X , ДЛ , А, D, R в регистры 35 - 39 блока 2 записываются соответственно , j , В, М, S, а а регистры k - блока 3 - соответственно Z, AZ , С, N, Р. Процесс преобразования разбит на шесть циклов. Первый цикл. На выходах мультип-. лексоров 32, 33, И,42, 50 и 51 присутствуют соответственно X, 4Х , а, ,г-,лг. В сумматорах - 6 1Э проводится суммирование соответстX ; ( венно X + frX 14-Д1 Z. Результаты суммирования х , « , z; записываются в ре- гистры соответственно 31, О и kS. Второй цикл. На выходах мультиплексоров 32, 1, 50 и на выходе бло ка 19 памяти зон присутствуют числа из N единиц. Мультиплексоры 33, и 51 пропускают на выход соответственно х, i и i , которые записываются в регистры соответственно . Далее на выходы мультиплексороб .33, и 51 поступают числа соответственно D, В и Р, а на выходах групп элементов И-НЕ 10 - 12 присутствуют числа соответственно к , j и г . В умножителях 13 - 15 осуществля ется умножение соответственно ) , B-il, Р-2. , результаты которого, пройдя через мультиплексоры соответ ственно 25, З и 3, записываются в регистры соответственно 36, 27 и Третий цикл. Аналогичным образом R-X , , ..I .. -.1 производится умножение С-г , результаты которого записываются в регистры соответственно 8, 37 и 29. Четвертый цикл. Производится умножение А-ч , S-a , N-z. , ре;%ультаты которого записываются в регистры соответственно 30, 38 и . Пятый цикл. Аналогично 1 такту, в сумматорах - 6 осуществляется суммирование соответственно B-v 4+Сг ,1)Х +Ма , PZ: +RX результаты которого записываются в регист ры соответственно 2б, 35 и Л. Шестой цикл, В сумматорах - 6 осуществляется суммирование соответ ственно ( + Ст.,) + АХ Xi , (ох + ) + N Z У, {Р2. + RX ) + S I. результаты которого записываются в регистры соответственно 7, 36 и 5. Преобразование из трехмерной пря моугольной системы координат в сферическую. В регистры 28 и 37 заносится координата , а в регистры 37 и соответственно тих. Координаты , Z и X поступают по,входам соответственно 55 - 57. Для предотвращения переполнения разрядной сетки при .вы числении Yxl-H + 1 и координаты ,X , 1 умножаем на масш табный коэффициент 2, для чего в регистрах соответственно 28 и , l 37, б осуществляется сдвиг влево на один разряд. Преобразование состоит из пяти циклово Первый цикл. На выходах мультиплексора 51 присутствует х, который записывают в регистр 9. Далее на выходе этого же мультиплексора появляется V , после чего обе координаты X и записываются в сдвигатель 16. После этого в устройстве осуществляется параллельно два процесса. В сдвигателе 16, выполненном на основе сдвиговых регистров, проводится взаимная нормализация координат X и а , которая заключается в одновременном сдвиге координат х и : влево до появления единицы в старшем разряде координаты X. После окончания взаимной нормализации осуществляется сдвиг V на 8 разрядов вправо, что соответствует умножению на масштабный коэффициент , которое проводится для предотвращения переполнения разрядной сетки при вычислении функции Ч arctg --. . Таким образом, диапазон аргумента функции Q arctg f представляется как О f 1. В умножителях 13 - 15 осуществляется вышеописанным образом умножение соответственно i V. V - . Z-, X- X ; X результаты которого записываются соответственно в регистры 27, 36, 45) 31, to, 49 и 26, 35, 44. Далее в сумматорах 4 - 6 вышеописанным способом проводится суммирование i, в результат которого записывают . в регистры 29, 38 и 47. После этого в сумматорах 4-6 проводится суммирование (х + S) + z-, результат которого записывают в регистры 26 и 35. Нормализованную вышеописанным способом координату записывают в регистр 48, а нормализованный х поступает в блок 17 обратной величины, который реализован на матрице сумматоров. С выхода блока 17 обратнойвеличины величина --- записывается в регистр 49. Очередность записи результатов умножения, суммирования и т«д. в регистры буферных блоков 1 - 3 устанавливается блоком 23 управления.

21 Второй цикл. Вычисляем 1 Полученные описанным ранее способом коэффициенты К и 6 записываются в регистры 30 и 31. Далее в умножителях 13 - 15 осуществляется умно- s

жение соответственно k-() ,г-1,

результаты которого записываются в регистры соответственно 29, +9, 27, 36 и 5 1очередность записи результатов умножения следующая г , ii Х ) После этого в сумматоре k проводится суммирование k(A+il ) 4- Ь, результат которого (Yx +:j ) заносится в регистр 30.

Третий цикл. В умножителе 13 проводится умножение , результат которого, записывается в регистр 8. Далее в сдвигатель 1б записывают вышеописанным образом Т и tx2-+ У . После этого в преобразователе параллельно происходит два процесса. Аналогично первому циклу, в сдвигателе 1б проводится взаимная нормализация I. и , нормализованное число УЛ- записывают в /

регистр 8, А величину - - в регистр 9. Затем вычисляют известным :j

способом arctg

Для этого поJтyчeнныe вышеописанным образом коэффициенты К и В записываются в регистры 28 и 29.

В умножителе 13 осуществляется

1

умножение К.

, результат которого записывается в регистр 28. Далее в сумматоре проводится сложение

+ Ь, результат которого

(arctg -J-) заносится в регистр 31.

Л

Четвертый цикл. ВычисляютУх .

. Коэффициенты К и Ъ записываются в регистры 37 и 38. В умножителях 1 и 15 проводится умножение соответственно k-( +1)-и

, результаты которого зав регистры соответствен ..ч 1«-«.™-.---36 и . В сумматоре 5 сложение k(x + b.

V

результат которого - х заносят в регистр 35.

Пятый цикл. Вычисляют arctg

Коэффициенты К и Ь заносятся в ре Гистры 28 и 29 . В умножителе 13 осу , . ществляется умножение k ч ) ,

результат которого записывают , в регистр 26 о Далее в сумматоре

) + Ь,

проводится сложение k.-(

результат которого arctg

заносится в регистр 30.

Окончательные значения углов у и в определяются в блоке 2Ц анализа знака. На его входы по информационным входам 55 - 57 поступают знаки координат X , 3 , Z (siqf пх, sig пх, sign-г), а с выхода мультиплексо fAisl

pa 33 - значения arctg --, arctg.

При описываемом преобразовании блок 2 анализа знака выполняет следующие операции:

- 0; у arctg -

XX

8; X 0; у 0; у arctg

XX

- 0; у arctg -

XX

-Д- 0; X 0; у 0; у arctg - +1 XтГТГлГX

Z 0; Q arctg

, Л

Z 0; Q -arctg

Z2

Преобразование из сферической

5 системы координат в трехмерную прямоугольную осуществляется следующим образом.

Ч записывается в регистры 26,

0 35 и Q - в регистры 27, Зб и +5; г - в регистры 31, «О и . Кратко изложим последовательность операций при данном координатном преобразовании.

5

Первый цикл. Вычисляем cos Ч

Второй цикл. Вычисляем cos (Я .

Третий цикл. Вычисляем sin Ч .

Четвертый цикл. Вычисляем sin а.

Одновременно умножаем cos 4CosCl ; sin Ч- cosa.

Пятый цикл. Одновременно yMHomsf ем г «(cos -cosQ); г (sm4-cosQ);, г sInQ.

Блок анализа выполняет следующие операции:

signx sign (cos)xsign (cpsQ) sign У sign(siiti) sign(cosQ) sign Z sign(sinQ).

Остальные координатные преобразования 2, 5 и 6 являются частными случаями координатных преобразований соответственно 1, 3 и k,

Эффективность изобретения заключается в расширении функциональных возможностей. Так, если в устройстве-прототипе реализован один вид координатных преобразований (поворот вектора на плоскости), то предлагаемое устройство реализует шесть видов координатных преобразований. Кроме того,повышается быстродействие устройства. Сравним длительность выполнения операции поворота вектора на плоскости на угол Q в описанном устройстве (Тп) и в устройстве-прототипе (TVI):

п о5Р+7-1.р,-г-4Цд„+31,,д,

Тп n(tcvi,e+t5. Wb

где - время записи в регистр; tggp - время обращения к блоку

памяти;

t - время выполнения суммирования;ми время выполнения умножения;

СА6 период импульсов генератора импульсов сдвига; t - время задержки сигнала в

логических элементах. При изменении разрядности ( операндов в диапазоне от шести до двадцати и при использовании в устройстве-прототипе параллельного сдвигателя выигрыш по быстродействию от применения предлагаемого устройства изменяется в диапазоне соответственно от к 1,3 до t 1,9.

Предлагаемое устройство характеризуется оо сравнению с прототипом существенно меньшей скоростью роста времени работы от разрядности операндов.

Формула изобретения

Универсальный цифровой преобразователь координат, содержащий дешифратор, два регистра, три суммато ра, три умножителя, блок управления и сдвигатель, отличающийс я тем, что, с целью повышения быстродействия, в него.введены два регистра, три группу элементов И-НЕ, блок вычисления обратной величины, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок памяти зон, блок выбора коэффициентов блок анализа знака и три буферных блока, причем первые выходы буферных блоков соединены с информационными входами соответственно первого, второго и регистров и с первыми входами соответственно первого, второго и третьего сумматоров, вторые входы которых соединены с вторыми выходами соответствующих буферных блоков, выходы сумматоров соединены с первыми входами соответствующих буферных блоков, выходы первого, второго и третьего регистров соединены с информационными входами элементов И-НЕ соответствующих групп, выходы элементов И-Н которых соединены с первыми входами соответствующих умножителей, вторые входы которых соединены с вторыми выходами соответствующих буферных блоков, третьи входы умножителей соединены с первыми выходами соответствующих буферных блоков, первые выходы умножителей соединены с соответствующими входами блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые выходы умножителей соединены с вторыми, третьими и четвертыми входами каждого буферного блока, выход блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом блока управления первым управляющим входом блока выбора коэффициентов и с информационным входом четвертого регистра, выход которого соединен с первым информационным входом дешифратора и с информационным входом блока выбора коэффициентов, второй управляющий вход которого соединен с первым выходом блока управления и адресным входом дешифратора, второй информационный вход которого соединен с вторым выходом блока управления, выход дешифратора подключен к входу блока памяти зон, выход которого соединен с четвертыми входами умножителей, выход блока выбора коэффициентов подключен к пятым входам буферных блоков, первый выход третьего буферного блока и выходы третьей группы 25 ;Элементов И-НЕ соединены с входами сдвигателя, выход которого соединен с шестым входом третьего буферного блока, седьмой вход которого через блок вычисления обратной величины соединен с выходом сдвигателя, первый вход блока анализа знака соединен с первым входом первого буфер JHoro блока, информационные входы бу ферных блоков и входы с второго по четвертый блока анализа знака являются информационными входами преобразователя, управляющие входы буфер ных блоков, регистров, групп элемен тов И, умножителей, сдвигателя и блока выбора коэффициентов соединены соответственно с выходами первой второй, третьей, четвертой,пятой и шестой групп блока управления, управляющие входы блока вычисления об ратной величины и блока анализа зна ка соединены с третьим и четвертым выходами блока управления соответственно. 2. Преобразователь по п. 1, о т личающийся тем, что каждый буферный блок содержит три муль типлексора и шесть регистров, инфор мационные входы первого мультиплексора являются входами буферного бло ка, выход первого мультиплексора соединен с информационными входами регистров, выхода регистров с первого по четвертый соединены с информационными входами второго мультиплексора, выходы всех регистров соединены с соответствующими информационными входами третьего мультип лексора, выходы второго и .го мультиплексоров являются соответственно вторым и первым выходами бу ферного блока, управляющие входы мультиплексоров и регистров являются управляющими входами буферного блока 3 Преобразователь по п. 1, о т личающийся тем, что блок выбора коэффициентов содержит дешифратор, мультиплексор и блок памяти коэффициентов, вход которого соединен с выходом дешифратора, вход которого является информационным входом блока выбора коэффициентов, выход блока памяти коэффициентов соединен с информационным входом мультиплексора, первый управляю щий вход которого является первым управляющим входом блока выбора коэффициентов, второй управляющий 26 . 1 вход которого соединен с вторым управляющим входом мультиплексора и адресным входом дешифратора. t. Преобразователь по п. 1, о т личающийся тем, что блок управления содержит блоки памяти программы вычислениявида преобразования и характеристик зон, счетчик, регистр, схему сравнения, коммутатор, генератор импульсов, мультиплексоры, блоки задания режима, пять элементов И и элемент И-НЕ, причем выходы с первого по восемнадцатый и с девятнадцатого по тридцать шестой блока памяти программы вычисления соединены с первыми и вторыми управляющими входами соответственно с первого по восемнадцатый мультиплексоров, первые и вторые информационные входы которых соединены соответс1венно с выходом первого блока задания режима .и выходом девятнадца- того мультиплексора, выходы мультиплексоров с первого по восемнадцатый являются выходами первой группы блока управления, выходы с тридцать седьмого по сороковой блока памяти программы вычисления соединены с управляющими входами соответственно с первого по четвертый элементов И, информационные входы с первого по третий элементов И соединены с выходом первого блока задания режима, вход Которого соединен с выходом генератора импульсов и информационным входом пятого элемента И, выход которого соединен с входами с второго по восьмой блоков задания режима, выход второго блока задания режима соединен с информационным входом четвертого элемента И, выход которого соединен через элемент И-НЕ .с вторым выходом блока управления, выход четвертого элемента И является выходом второй гоуппы блока управленияj вы-ходы с сорок первого по шестьдесят седьмой блока памяти программы вычисления являются выходами первой группы блока управления, выходы шестьдесят восьмой и шестьдесят девятый блока памяти программы вычисления являются выходами пятой группы блока управления, выходы с семидесятого по семьдесят второй блока памяти программы вычисления являются выходами третьей группы блока управления, вь1ходы с cfeмьдecят третьего по семьдесят пятый блока памяти программы вычисления соединены с

управляющими входами девятнадцатого мультиплексора и блока памяти харак тёристик зон и является первым выходом блока управления, семьдесят шестой выход блока памяти программы вычисления является третьим выходом блока управления, семьдесят .седьмой выход блока памяти программы вычисления соединен с вторым выходом блока, управления, семьдесят восьмой ,выход блока памяти программы вычисления является выходом первой группы блока управления, семьдесят девятый выход блока памяти программы вычисления соединен с управляющим входом пятого элемента И, восьмидесятый выход блока памяти программы вычисления является четвертым выходом блока управления, выходы блоков задания рекима с третьего по шестой подключены к информационным входам с первого по четвертый девятнадцатого мультиплексора, пятый вход которого соединен с выходом двадцатого мультиплексора, управляю1цие входы которого соединены с выходами блока памяти характеристик зон и являются выходами шестой группы блока управления, вход блока управления соединен с информационным входом блока пдмяти характеристик зон, первый и второй информационные

входы двадцатого мультиплексора соединены соответственно с выходами седьмого и восьмого блоков задания режима, выход девятнадцатого мультиплексора соединен с управлякмцим входом коммутатора, „информационный вход которого соединен с выходом генератора импульсов, выход коммутатора соединен с тактовым входом

счетчика, установочные входы которого соединены с первыми выходами блока памяти вида преобразования,, вторые выходы которых соединены с установочными входами регистра,

вход блока памяти вида преобразов ания является входом задания режима блока управления, выход счетчика соединен с входом блока памяти программы вычисления и первым

ВХОДОМ схемы сравнения, выход которой подключен к управляющему входу генератора импульсов, второй вход схемы сравнения соединен с выходом регистра.

Источники информации,

принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 6Uit39, кл. Q06T 15/3, 1978. 2, Авторское свидетельство СССР № 6 12712, кл. Gi06F 15/20,1979 (прототип).

55

LJ fJLJ

о

w

f

/J М

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1103225A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для решения уравнений математической физики | 1986 |

|

SU1363260A1 |

| Устройство для вычисления функций в модулярной системе счисления | 1985 |

|

SU1322268A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления элементарных функций | 1985 |

|

SU1298764A1 |

H;

/

tt

J LJ S LJ

/3

I

г/

Я7

55 S6S

4l W W r

f i (

t w 1

z

/f

//

17

/5

T

Л7

i

«-1

tf/

25 (ЭМ)

I

г 11

I

ш,

т.

liw LJ С.

ИЙ

Г

«Sl/jf

31 и

1 f t (J г

w (J J,

wf-f,);

ej

/ г j

litj;j:j :,:j:j

i I

f2 J gr

9-3 ft t-f

-H ft

t4

,:.

&

Ж

53

Авторы

Даты

1982-04-30—Публикация

1980-04-28—Подача