/let

СЛ

00

о о

1 1465809

Изобретение относится к измерительной технике с применением цифровой фильтрации и может быть использовано в автоматизированнь 1х систе- мах испытаний электрических машин переменнод о тока и в других областях техники, где требуется ин.формация об амплитудах и фазовых сдвигах сигналов,to

Цель изобретения - повышение быстродействия.

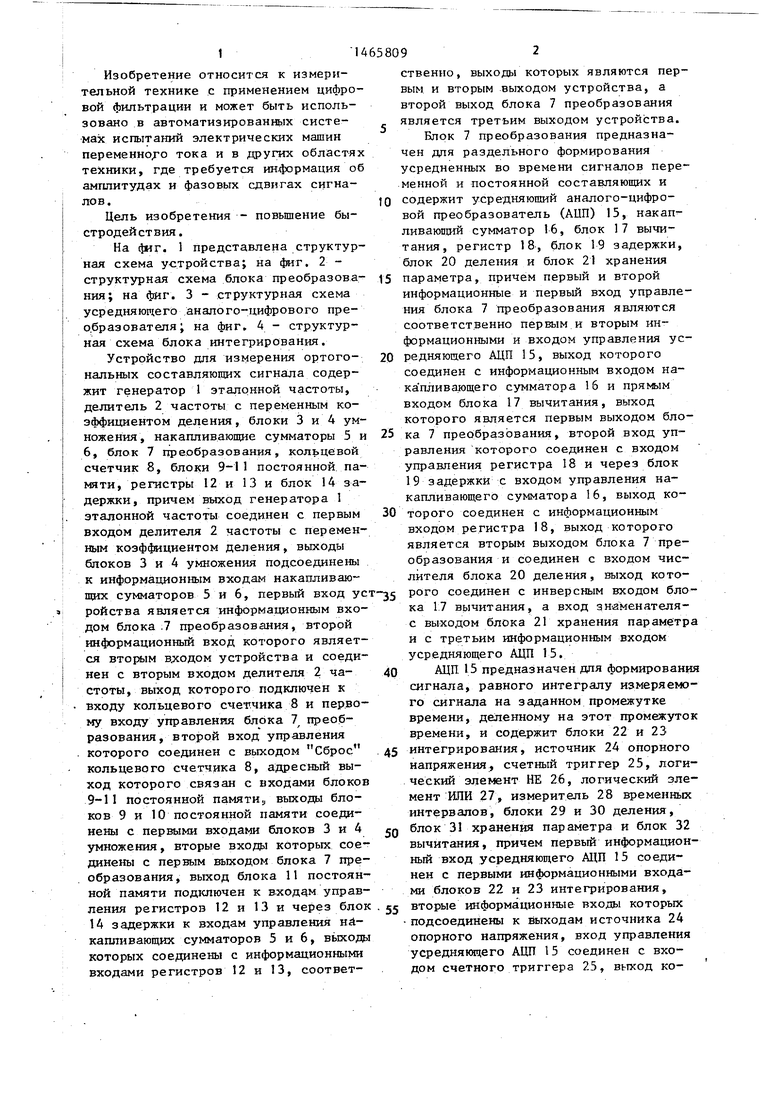

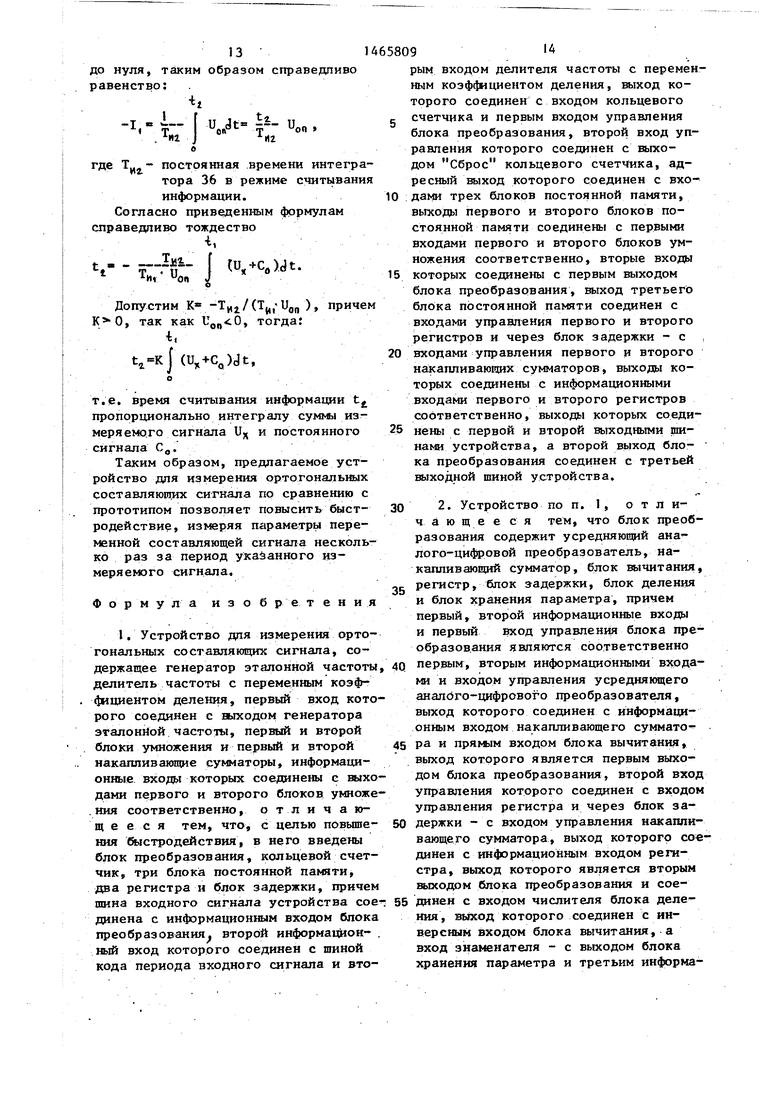

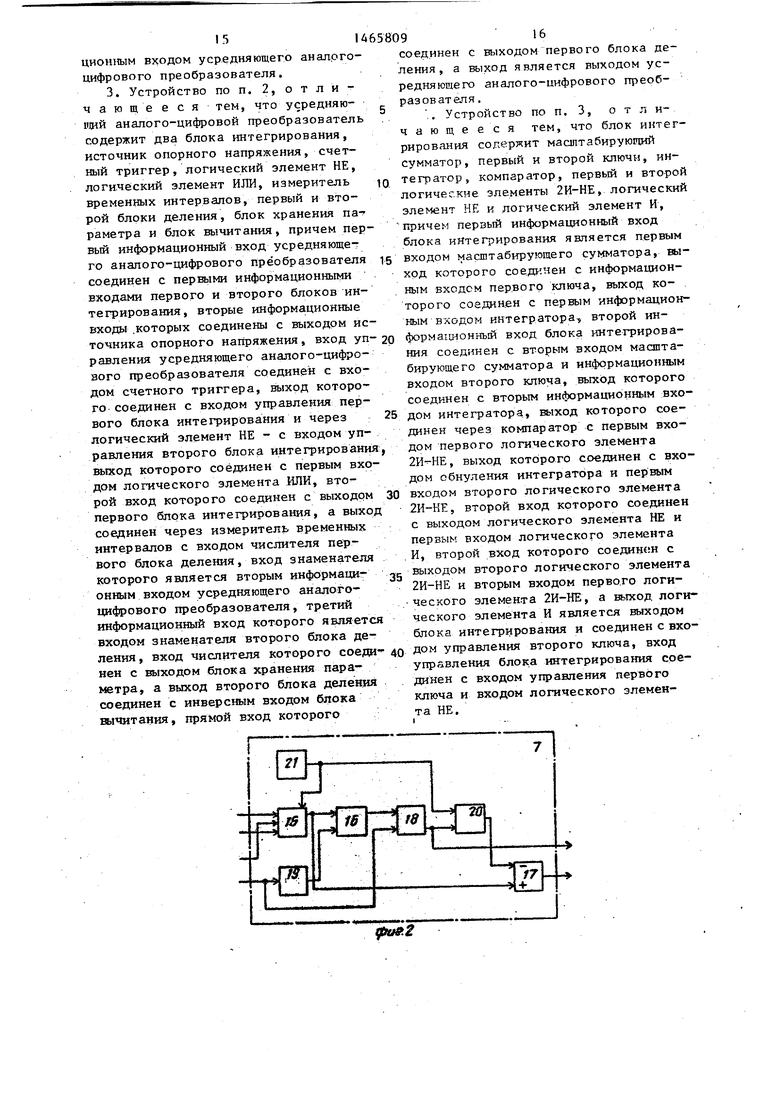

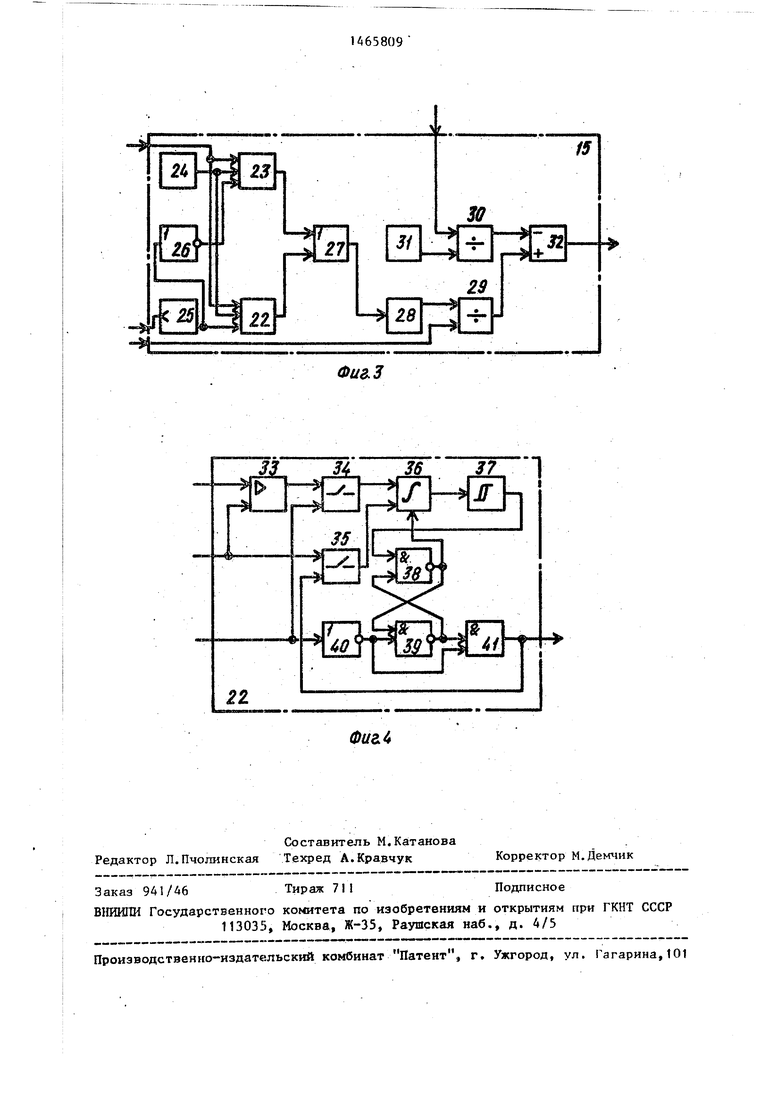

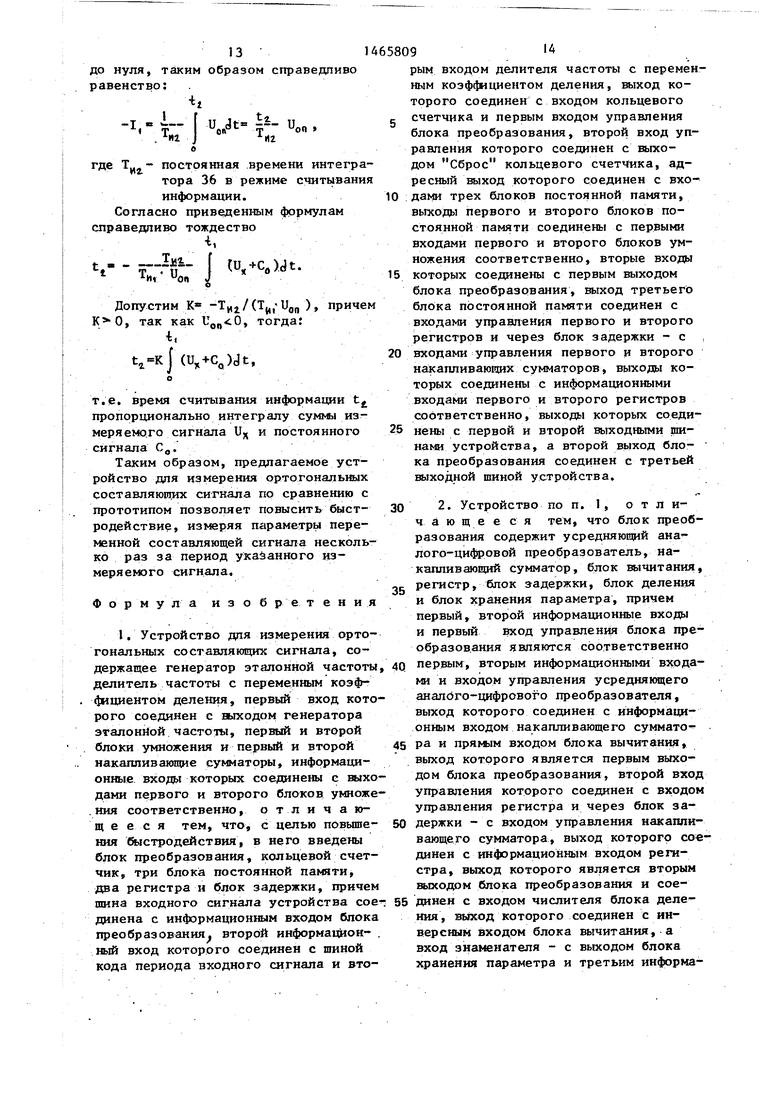

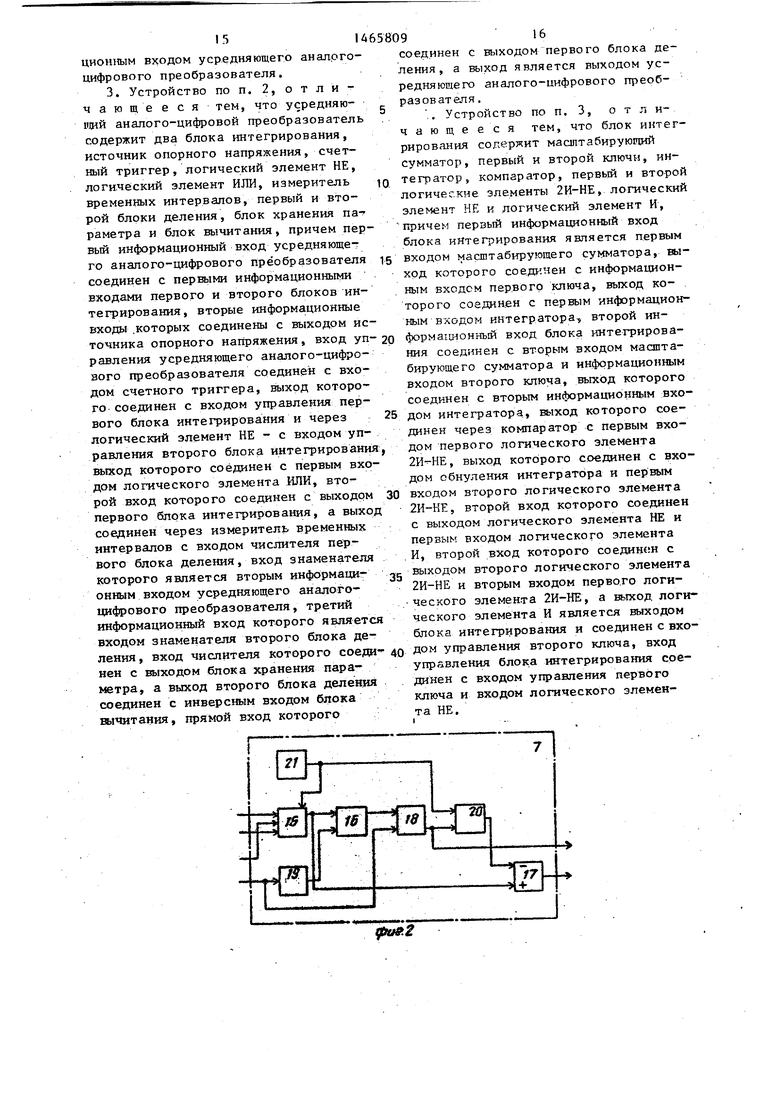

На ({иг. 1 представлена структурная схема устройства; на фиг, 2 - структурная схема блока преобразова- V5 ния; на фиг. 3 - структурная схема усредняющего аналого-цифрового преобразователя ; на фиг. 4 - структурная схема блока интегрирования.

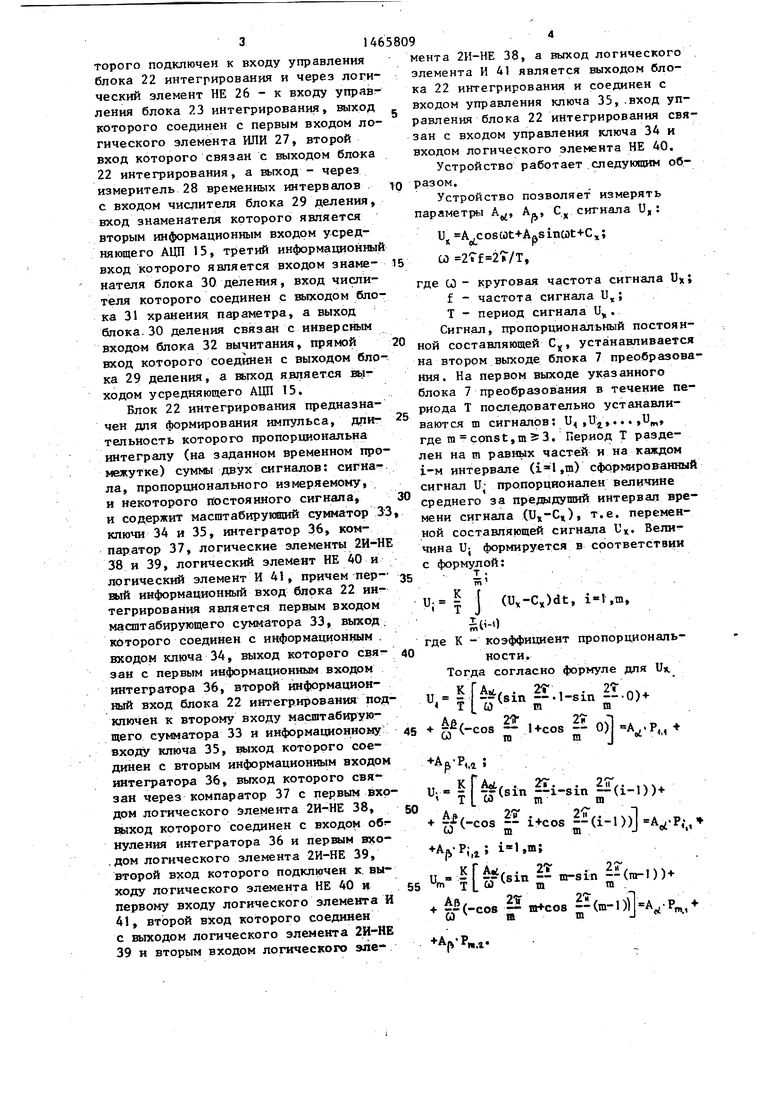

Устройство для измерения ортого- 2D нальных составляющих сигнала содержит генератор 1 эталонной частоты, делитель 2 частоты с переменным коэффициентом деления, блоки 3 и 4 умножения, накапливающие сумматоры 5 и 25 6, блок 7 преобразования, кольцевой счетчик 8, блоки 9-П постоянной памяти, регистры 12 и 13 и блок 14 задержки, причем выход генератора 1 эталонной частоты соединен с первым 30 входом делителя 2 частоты с переменным коэффициентом деления, выходы блоков 3 и 4 умножения подсоединены к информационным входам накапливаюственно, выходы которых являются первым и вторым выходом устройства, а второй выход блока 7 преобразования является третьим выходом устройства. Блок 7 преобразования предназначен для раздельного формирования усредненных во времени сигналов переменной и постоянной составляющих и содержит усредняющий аналого-цифровой преобразователь (АЦП) 15, накап ливаюпщй сумматор 16, блок 17 вычитания, регистр 18, блок 19 задержки, блок 20 деления и блок 21 хранения параметра, причем первый и второй информационные и первый вход управления блока 7 преобразования являются соответственно первым и вторым информационными и входом управления усредняющего АЦП 15, выход которого соединен с информационным входом на- ка пливающего сумматора 16 и прямым входом блока 17 вычитания, выход которого является первым выходом блока 7 преобразования, второй вход управления которого соединен с входом управления регистра 18 и через блок 19 задержки с входом управления накапливающего сумматора 16, выход которого соединен с информациоиным входом регистра 18, выход которого является вторым выходом блока 7 преобразования и соединен с входом числителя блока 20 деления, выход котощих сумматоров 5 и 6, первый вход уст-з5 соединен с инверсным входом блоройства является информационным входом блока .7 преобразования, второй информационный вход которого является вторым вдодом устройства и соединен с вторым входом делителя 2 частоты, выход которого подключен к входу кольцевого счеттчика 8 и первому входу управления блока 7 преобразования, второй вход управления которого соединен с выходом Сброс кольцевого счетчика В, адресный выход которого связан с входами блоков 9-1 I постоянной памяти,, выходы блоков 9 и 10 постоянной памяти соединены с первыми входами блоков 3 и 4 умножения, вторые входы которых сое- дине1И)1 с первым выходом блока 7 преобразования, выход блока 11 постоянной памяти подключен к входам управ40

45

50

ка 17 вычитания, а вход знйменатепя- с выходом блока 21 хранения параметра и с третьим информационным входом усредняющего АЦП 15.

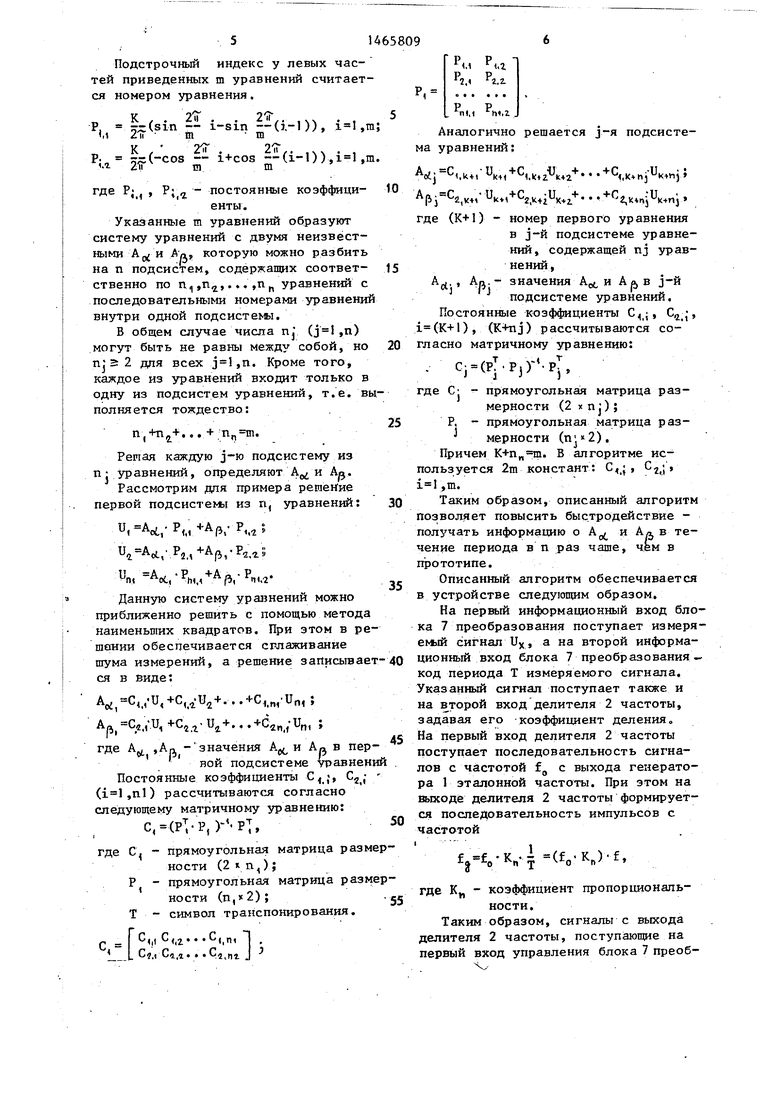

АЦП 15 предназначен дпя формирования сигнала, равного интегралу измеряемого сигнала на заданном промежутке времени, деленному на этот промежуток времени, и содержит блоки 22 и 23 интегрирования, источник 24 опорного напряжения, счетный триггер 25, логический элемент НЕ 26, логический элемент ИЛИ 27, измеритель 28 временных интервалов, блоки 29 и 30 деления, блок 31 хранения параметра и блок 32 вычитания, причем первый информационный вход усредняющего АЦП 15 соединен с первыми информационными входами блоков 22 и 23 интегрирования.

ления регистров 12 и 13 и через блок . 55 вторые информационные входы которых 14 задержки к входам управления нЛ- -подсоединены к йыходам источника 24 капливающих сумматоров 5 и 6, вькоды опорного напряжения, вход управления которых соединены с информационными усреднянщего АЦП 15 соединен с вхо- входами регистров 12 и 13, соответ- дом счетного триггера 25, выход коственно, выходы которых являются первым и вторым выходом устройства, а второй выход блока 7 преобразования является третьим выходом устройства. Блок 7 преобразования предназначен для раздельного формирования усредненных во времени сигналов переменной и постоянной составляющих и содержит усредняющий аналого-цифровой преобразователь (АЦП) 15, накап ливаюпщй сумматор 16, блок 17 вычитания, регистр 18, блок 19 задержки, блок 20 деления и блок 21 хранения параметра, причем первый и второй информационные и первый вход управления блока 7 преобразования являются соответственно первым и вторым информационными и входом управления усредняющего АЦП 15, выход которого соединен с информационным входом на- ка пливающего сумматора 16 и прямым входом блока 17 вычитания, выход которого является первым выходом блока 7 преобразования, второй вход управления которого соединен с входом управления регистра 18 и через блок 19 задержки с входом управления накапливающего сумматора 16, выход которого соединен с информациоиным входом регистра 18, выход которого является вторым выходом блока 7 преобразования и соединен с входом числителя блока 20 деления, выход котоР о соединен с инверсным входом бло

ка 17 вычитания, а вход знйменатепя- с выходом блока 21 хранения параметра и с третьим информационным входом усредняющего АЦП 15.

АЦП 15 предназначен дпя формирования сигнала, равного интегралу измеряемого сигнала на заданном промежутке времени, деленному на этот промежуток времени, и содержит блоки 22 и 23 интегрирования, источник 24 опорного напряжения, счетный триггер 25, логический элемент НЕ 26, логический элемент ИЛИ 27, измеритель 28 временных интервалов, блоки 29 и 30 деления, блок 31 хранения параметра и блок 32 вычитания, причем первый информационный вход усредняющего АЦП 15 соединен с первыми информационными входами блоков 22 и 23 интегрирования.

314658094

зг.ггг дггл-™-

ScK LLeHT НЕ 26 - к входу упр.- ка 22 ™- ™„:;/° ™:„%„-- : ::;.- гirS™r -к-Е.™-™;.

измеритель 28 ° с;ройство позволяет измерят, с входом числителя блока /У деления,fА г Г1ггняпд U

вход знаменателя которого являетсяпараметрь, А, А. С, сигнала U, .

вторым информационным входом усред-u A coscot+Apsina)t+C,;

няющего АЦП 15, третий информационный.л

вход которого является входом зяаме- 15w -.: i - / ,

нагеля блока 30 деления, вход числи- де (j круговая частота сигнала Ux

теля которого соединен с выходом бло-f - частота сигнала U,;

ка 31 хранения параметра, а выходх - период сигнала U .

блока.30 деления связан с инверснымСигнал, пропорциональный постоянвходом блока 32 вычитания, прямой 20„ой составляющей С, устанавливается

вход которого соединен с выходом втором выходе блока 7 преобразовака 29 деления, а вьпсод является вь1-„j. на первом выходе указанного

ходом усредняющего АЦП 15.блока 7 преобразования в течение пеБлок 22 интегрирования предназна-риода Т последовательно устанавличен для формирования импульса, дли- ваются ш сигналов: U, ,13,... ,и„,

тельность которого пропорциональнагде m const,. Период Т раздеинтегралу (на заданном временном про- ен на m равных частей и на каждом

межутке) суммы двух сигналов: сигна i-м интервале (,т) сформированный

ла, пропорционального измеряемому,сигнал U- пропорционален величине

и некоторого постоянного сигнала, 30среднего за предыдущий интервал вреи содержит масштабирукяций сумматор 53, сигнала (U,-Cx), т.е. переменключи ЗА и 35, интегратор 36, ком-„д составляющей сигнала L. Велипаратор 37, логические элементы 2И-НЕчина Uj формируется в соответствии

38 и 39, логический злемент НЕ 40 и формулой:

логический элемент И 41, причем пер- 35I;

вый информационный вход блока 22 ИИ- f пг-г t i-lm.

тегрирования является первым входомU; - f J

масштабирующего сумматора 33, выход;х.,)

которого соединен с информационным,д j коэффициент пропорциональвходом ключа 34, выход которого свяг- 40ности.

зав с первым информационным входомТогда согласно формуле для U)t интегратора 36, второй информацион-К ГЛы,, . 2Г. . 2Г . . ный вход блока 22 интегрирования под-U, т I U Г ы ключей к второму входу масштабирую-д 21 , 27 . Л . щего сумматора 33 и информационному 45 + -(-cos -- 0)1 A.I входу ключа 35, выход которого соединен с вторым информационным входом A P,,i ;

интегратора 36, выход которого свя-кГАы., . 27. . 2,. ,,,

зан через компаратор 37 с первым вхо-Ц- -и

дом логического элемента 2И-НЕ 38, 50 д2V. 21Г,. .,Л . „ .

выход которого соединен с входом ( -- i+cos --(i-l ))J ,-„

нуления интегратора 36 и .-Р; , ; i«l.«;

дом логического элемента 2И-НЕ jy,р чг

второй вход которого подключен к. вы- KI 6jf(sin -- m-sin --(га-1)) +

ходу логического элемеита НЕ 40 и55 Т L

первому входу логического элемента И Ав, 2 .. ,д.р

41, второй вход которого соединенQmmJ

с выходом логического элемента 2И-НЕ +А -Р .

39 и вторым входом логического эле-( +

U)t . . I

РМ +

Подстрочный индекс у левых частей приведенных m уравнений считается номером уравнения,

К , . 27 . . 2 аР, :r-(sin - i-sin -(з,-1)), ,m; 111 /II m m

К 2 .Z-ir .vv . ,

Р;.г и --(i-l)),.m.

где Pj , Р;л - постоянные коэффициенты.

Указанные m уравнений образуют систему уравнений с двумя неизвестными А( и An, которую можно разбить на п подсистем, содержащих соответственно по п .п,... ,11 уравнений с последовательными номерами уравнений внутри одной подсистемы,

В общем случае числа nj (j l ,п) могут быть не равны между собой, но nj2 2 для всех ,n. Кроме того, каждое из уравнений входит только в одну из подсистем уравнений, т.е. выполняется тождество:

п,,,

+ .

Реиая каждую j-ю подсистему из п- уравнений, определяют А и А.

Рассмотрим для примера регаеНие первой подсистег из п, уравнений

U,Aci,-P,.,,.P,. , Р2,ЛАэ,.г

П| ,

РИ,,,-Р.,.Г

Описанный алгоритм обеспечивается в устройстве следующим образом.

На первый информационный вход блока 7 преобразования поступает измеряемый сигнал Ujt, а на второй информа7

Данную систему уравнений можно приближенно решить с помощью метода наименьших квадратов. При этом в решении обеспечивается сглаживание

шума измерений, а решение записьгаает-40 ционный вход блока 7 преобразования- код периода Т измеряемого сигнала, Указанный сигнал поступает также и на второй вход делителя 2 Частоты, задавая его коэффициент деления, 45 На первый вход делителя 2 частоты поступает последовательность сигналов с частотой fg с выхода генератора 1 эталонной частоты. При этом на выходе делителя 2 частоты формируется последовательность импульсов с частотой

ся в виде: Aoi,C4, U,+C,,, U2+. . ,+C.„,Un, ;

А|5,с,.,-.и, -с,,г- Ui+.. .., Un, ;

где А ,Аа - значения А и А в пер вой подсистеме уравнений Постоянные коэффициенты С j, / (,п1) рассчитываются согласно следующему матричному уравнению:

c,(PVP, )

,.

рТ

«

50

.

Р7.

.г Рг,г

. п1,1 -им .

Аналогично решается j-я подсистема уравнений;

Aolj nk+i ,K+hj к -l) (ij.,vtr ktl 2, ,K nj K+nj

где (К+1) - номер первого уравнения в j-й подсистеме уравнений, содержащей nj уравнений, ct « р- значения К и А л в j-й

подсистеме уравнений. Постоянные коэффициенты , С,,, i(K+l), (K+nj) рассчитываются согласно матричному уравнению:

Cj(p;

РЗ)

,-t

И

где

S 5

0

5

прямоугольная матрица раз- мерности (2 X п:); Р. - прямоугольная матрица раз- мерности (). Причем , В алгоритме используется 2т констант: C,j , г, ,m.

Таким образом, описанный алгоритм позволяет повысить быстродействие - получать информацию о А и А чение периода в п раз чаше, ч прототипе.

Описанный алгоритм обеспечивается в устройстве следующим образом.

На первый информационный вход блока 7 преобразования поступает измеряемый сигнал Ujt, а на второй информа7

;ем

в тев

0 ционный вход блока 7 преобразования- код периода Т измеряемого сигнала, Указанный сигнал поступает также и на второй вход делителя 2 Частоты, задавая его коэффициент деления, 5 На первый вход делителя 2 частоты поступает последовательность сигна

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННОЕ УСТРОЙСТВО | 2002 |

|

RU2229156C2 |

| ВЫЧИСЛИТЕЛЬ ОЦЕНКИ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ | 2002 |

|

RU2229158C1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| Устройство регулирования компенсатора реактивной мощности | 1990 |

|

SU1830524A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| Цифровое устройство для измерения порядка интерференции | 1987 |

|

SU1420364A1 |

| Цифровой измеритель | 1988 |

|

SU1626170A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

Изобретение может быть использа вано в измерительной технике с применением цифровой фильтрации, в системах испытания электрических машин. Цель изобретения - повышение быстродействия. Цель достигается введением в устройство блока 7 преобразования, выполняющего раздельное формирование переменной и постоянной составляющих входного сигнала, блоков 9, Ю, П постоянной памяти. Последние управляются адресами с кольцевого счетчика 8, в которых хранятся и считываются соответственно адресам коэффициенты дискретных значений ортогональных составляющих. Блок 14 задержки обеспечивает необходимую последовательность работы регистров 12 и 13 и сумматоров 5 и 6, в которые выводится ргн- формация об ортогональных составляющих сигнала. Устройство содержит также генератор 1 эталонной частоты, де- ..литель 2 частоты с переменным коэффи- - циентом деления и блоки 3 и 4 уменьшения. 3 з.п. ф-лы, 4 ил. i

С, - прямоугольная матрица размерности (2 к п,);

Р - прямоугольная матрица размерности (п, 2);-55 Т - символ транспонирования.

С .i , 1 . 5L .li J

f h

Vf fo

KJ-f.

где К„ - коэффициент пропорциональности.

Таким образом, сигналы с выхода делителя 2 частоты, поступающие на первый вход управления блока 7 преоб- я,.

разования, имеют частоту, пропорциональную частоте измеряемого сигнала. Параметры f, и К подбирают так, чтобы , т.е. чтобы ..

Кольцевой счетчик 8 выполнен как

счетчик с модулем т. После каждой группы сигналов из m импульсов, т.е. в конце периода измеряемого сигнала, на выходе Сброс кольцевого счетчика 8 вырабатывается импульс, который подается на второй вход управления блока 7 преобразования.

Каждый из блоков 10 и П постоянной памяти и счетчик 8 имеет по m входных адресов и по m соответствующих ячеек памяти. В течение периода Т измеряемого сигнала Hia адресном ВЫКОД8 кольцевого счетчика 8 поеледаваемой блоком 14, накапливающие сумматоры 5 и 6 обнуляют свое содержание, после чего они начинают новое накопление информации.

Блок 7 преобразования работает сле дующим обр аз ом J

На первый информационный вход усредняющего А1Ш 15 поступает измеря- сигнал U, на второй информацион ный вход - сигнал периода Т измеряемого сигнала, а на третий информационный ВХОД - сигнал пропорциональный параметру т, с выхода блока 21 хранения параметра. На вход управления

10

15

усредняющего АЦП 15 поступают импульс ные сигналы с частотой . При

этом на выходе усредняющего АЦП I5 последовательно устанавливаются за

,И tVfcJJl J-Jti,ti - -.- -

довательно устанавливаются все m ад- 20 период Т измеряемо го сигнала U сиг- ресов„ На выходах блоков 9-11 уста-налы j, .Цу, - jyj. Ч,5;т причем

навливаются при этом сигналы, записанные в соответствующие ячейки памяти.

В блоке 9 постоянной памяти запи- /э саны в порядке следования адресов следующие сигналы: С,, , С,д ,... ,С,,„. В блоке 10 постоянной памяти записаныj i

в порядке следования адресов сигналыобразуя сигнал и, j L ,Jt, который

Ci., Р блоке 11 постоян- 30 ной памяти записаны сигналы, управ- .ляющие работой выходных регистров 12 и 13 и накапливаюпдах сумматоров 5 и 6, таким образом, что на первом

(Ч

. V, l j

Сигналы U,s.; (i l ,ш) накапливаются в течение периода Т в сумматоре 16,

переписывается в конце периода Т в регистр 18 по сигналу, поступающему на второй вход управления блока 7 преобразования. Далее с выдержкой

временном интервале в каждой из ука- 35 создаваемой блоком 19, со .;. .- гчк -ъгчtTQn-arTJ V«rtO Л ТГХЛКОТАГ Я 1 П nfiHVTTCT РТ и

держимое сумматора 16 обнуляется и начинается новый цикл накопления информации, дпящийся в течение периода Т. Согласно формуле для измеряемого сигнала U сигнал U,g-K Cx. Данный сигнал и, пропорциональный постоянной составляющей измеряемого сигнала и, устанавливается на втором выходе блока 7 преобразования, т.е. на трезанных п групп временных интервалов на выходе блока П устанавливается сигнал 1. В остальных случаях на выходе блока П постоянной памяти - сигнал О.40

В течение периода Т на первом выходе блока 7 преобразования последовательно устанавливаются сигналы и.,и4,..,и„, каждмй из которых в блоках 3 и 4 умножается на сигналы , 45 тьем выходе устройства. С (1 1,го), т.е. последовательно фор-Указанные выще сигнапы U,- (i-l,m)

мируются произведения () и

(11,- Сг,); (и 2-С,л) и ( ).. () и (и„-С,.). Эти произведения накапливаются в сумматорах 5 и о JQ в соответствии с приведенными формулами дпя Apt и , и сигналы Aet и АлП раз в течение периода Т переписываются в регистры 12 и 13 т.е. на первый и второй выходы устройства. jj Причем переписывание информации про-, исходит при появлении сигнала 1 на выходе блока 11 постоянной памяти. Далее с задержкой времени, соэформируются в соответствии с формулой :

1 u.s.

с помощью блока 20 деления и блока 17 вычитания. Приведенная формула для U; (,т) верна, так как

,..; I j (u,-c,)dt+ I j c,dt

{ -0 ii-O

-U;+ - -U;+U g/m.

658098

даваемой блоком 14, накапливающие сумматоры 5 и 6 обнуляют свое содержание, после чего они начинают новое накопление информации.

Блок 7 преобразования работает следующим обр аз ом J

На первый информационный вход усредняющего А1Ш 15 поступает измеря- сигнал U, на второй информационный вход - сигнал периода Т измеряемого сигнала, а на третий информационный ВХОД - сигнал пропорциональный параметру т, с выхода блока 21 хранения параметра. На вход управления

10

15

усредняющего АЦП 15 поступают импульсные сигналы с частотой . При

этом на выходе усредняющего АЦП I5 последовательно устанавливаются за

j i

(Ч

V, l j

Сигналы U,s.; (i l ,ш) накапливаются течение периода Т в сумматоре 16,

переписывается в конце периода Т в регистр 18 по сигналу, поступающему на второй вход управления блока 7 преобразования. Далее с выдержкой

создаваемой блоком 19, соtTQn-arTJ V«rtO Л ТГХЛКОТАГ Я 1 П nfiHVTTCT РТ и

держимое сумматора 16 обнуляется и начинается новый цикл накопления информации, дпящийся в течение периода Т. Согласно формуле для измеряемого сигнала U сигнал U,g-K Cx. Данный сигнал и, пропорциональный постоянной составляющей измеряемого сигнала и, устанавливается на втором выходе блока 7 преобразования, т.е. на третьем выходе устройства. Указанные выще сигнапы U,- (i-l,m)

тьем выходе устройства. Указанные выще сигнапы U,- (i-l,m

формируются в соответствии с формулой :

1 u.s.

с помощью блока 20 деления и блока 17 вычитания. Приведенная формула для U; (,т) верна, так как

,..; I j (u,-c,)dt+ I j c,dt

{ -0 ii-O

-U;+ - -U;+U g/m.

Сигналы U; (,m) переменной составляющей измеряемого сигнала U, устанавливаются на первом выходе блока 7 преобразования,5

УсредЯяюинй АЦП 15 работает следукяцим образом.

Измеряемый сигнал U, подается на первые информационные входы блоков Q 22 и 23 интегрирования. На вторые информационные входы указанньтх блоков 22 и 23 подается сигнал U, опорного напряжения с выхода блока 24. Указанные блоки 22 и 23 формируют импульсы, продалжит€1пьность которых пропорциональна интегралу суммы двух сигналов: измеряемого и опорного, на заданном временном интервале. Причем опорное напряжение выбрано так, что- 20 бы указанная сумма была одного знака при всех возможных изменениях измеряемого сигнала. Время интегрирования задается сигналами, поступающими на вход управления усредняющего АЦП 15, 25 и равно периоду частоты указанных сигналов управления. Блоки 22 и 23 осуществляют интегрирование (накопление информации) в то время, когда на их входах управления установлен сиг- jg нал 1. В противном случае блоки 22 и 23 переходят в режим считывания информации (режим формирования выходного сигнала) и затем а режим ожидания нового периода накопления инфоррежнме накопления информации. Выходные сигналы блоков 22 и 23 интегрирования через логический элемент ШТИ 27 подаются на вход измерителя 28 временшях интервалов и преобразуются им в цифровой крд. Причем так как блоки 22 и 23 поочередно находятся в режиме накопления и выдачи информации, то и сигнал выходе измерителя 28 временных интервалов всегда соответствует формуле:

и

28

к j (u,-«-c)dt.

(-

где i изменяется в течение периода

Т от до т;

С - постоянный сигнал, пропорциональный опорному напряжению и

Ч

Блок 29 осуществляет деление указанно гр сигнала на сигнал периода Т. На выходе блока 29 устанавливаетсигнап т.

ся

24 28 - т т.«

(U.-bC«)dt

К

(i-)

I I U, Со, ,т.

i-)

В блоке 3 хранится сигнал (КС), который поступает на вход числителя блока 30 деления, на вход знаменатеНИЯ HOBUi о иериидл п г1л1ды слг1л .

мащга.. Счетный триггер 25 обеспечива- ля которого поступает сигнал, пропорет деление частоты сигналов управления пополам. При этом применение логического элемента НЕ 26 на входе управления одного из блоков интегрирования позволяет использовать дпя измерения ортогонапьнь:х составляющих сигнала всю информацию об измеряемом сигнале без пропусков, В то время, когда на входе управления блока 22 интегрирования установлен сигнал 1 и блок 22 находится в режиме накопления информации, на входе управления блока 23 интегрирования установлен сигнал О и блок 23 находится в ре жиме считывания информации (формирование выходного сигнала) или в режиме ожидания. В то время, когда на входе управления блока 22 интегрирования установлен сигнал О, блок 22 находится в режиме считывания информации или в режиме ожидания. При этом на входе управления блока 23 установлен сигнал 1 и блок 23 находится в

40

циональный т. Таким образом, блок 30 деления формирует на своем выходе сигнал 11,0 КСо /т, который поступает на инверсный вход блока 32 вычита-г ния. Блок 32 вычитания формирует на своем выходе согласно приведенным формулам сигнал

45

и

.i

и„-и,о I

I , ,m.

Ci-)

50

55

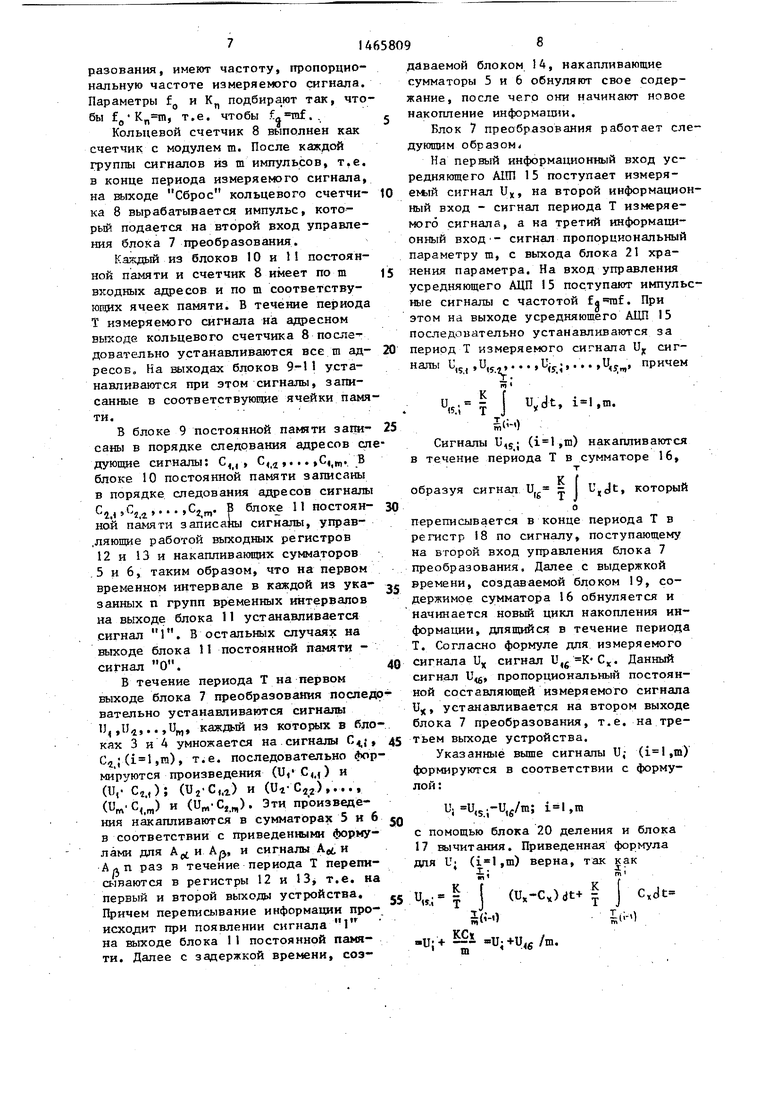

Блок 22 интегрирования работает по принципу двухтактного интегрирования следующим образом.

На первый информационный вход блока 22 интегрирования поступает измеряемый сигнал U, а на второй информационшлй вход указанного блока 22 поступает сигнал опорного напряжения ). Указанные сигналы масштабируются и суммируются масштабирующим сумматором 33, и сигнал на его выходе

режнме накопления информации. Выходные сигналы блоков 22 и 23 интегрирования через логический элемент ШТИ 27 подаются на вход измерителя 28 временшях интервалов и преобразуются им в цифровой крд. Причем так как блоки 22 и 23 поочередно находятся в режиме накопления и выдачи информации, то и сигнал выходе измерителя 28 временных интервалов всегда соответствует формуле:

и

28

к j (u,-«-c)dt.

(-

где i изменяется в течение периода

Т от до т;

С - постоянный сигнал, пропорциональный опорному напряжению и

Ч

Блок 29 осуществляет деление указанно гр сигнала на сигнал периода Т. На выходе блока 29 устанавливаетсигнап т.

ся

24 28 - т т.«

(U.-bC«)dt

К

(i-)

I I U, Со, ,т.

i-)

В блоке 3 хранится сигнал (КС), который поступает на вход числителя блока 30 деления, на вход знаменате

ля которого поступает сигнал, пропорля которого поступает сигнал, пропор

циональный т. Таким образом, блок 30 деления формирует на своем выходе сигнал 11,0 КСо /т, который поступает на инверсный вход блока 32 вычита-г ния. Блок 32 вычитания формирует на своем выходе согласно приведенным формулам сигнал

и

.i

и„-и,о I

I , ,m.

Ci-)

Блок 22 интегрирования работает по принципу двухтактного интегрирования следующим образом.

На первый информационный вход блока 22 интегрирования поступает измеряемый сигнал U, а на второй информационшлй вход указанного блока 22 поступает сигнал опорного напряжения ). Указанные сигналы масштабируются и суммируются масштабирующим сумматором 33, и сигнал на его выходе

11

,(, и„„)к,(и,-нс„);

UOH

где К,jK - коэффициенты пропорииональности, К,0, . Причем параметры Kj, и выбйр.ают- ся так, чтобы при любых изменениях и сигнал U,j6bm больше нуля.

менятся, так как RS-триггер переход в режим хранения информации. На ных де логического элемента И А1 устана ливается сигнал 1, так как тепер на обоих его входах присутствуют с налы 1. При этом кпюч 35. размыка ся и на второй информационный вход интегратора 36 поступает отрицател

сигнал и„был больше нуля.„ сигнал U опорного напряжения,

В режиме накопления информации или 10 - - ньшение по абсолютно

во время первого такта интегрирования на входе управления указанного - блока 22 установлен сигнал 1, ключ

20

30

35

или IXd J - tj-iiv i-frf - --

34 открыт, положительный сигнал U, поступает на первый информационный вход интегратора 36. При этом происходит интегрирование с нулевыми начальными усповиями в течение всего вре-. мени нахождения на входе управления сигнала 1. В этом режиме сигнал и,бНа выходе интегратора 36 растет по абсолютной величине, но всегда меньше нулр. Компаратор 37 сравнивает сигнал Ujec нулевым. При этом, когда на входе компаратора 37 имеется отрицательный сигнал, на выходе присутствует сигнал 1, которьй в режиме накоппения информации поступает на первый вход логического элемента 2И-НЕ 38. В то же на второй, вход логического элемента 2И-НЕ 39 поступает сигнал О с выхода логического элемента НЕ 40. Блоки 38 И 2И-НЕ 39 образуют RS-триггер,а в указанном режиме блока 22 интегрирования на выходе логического элемен- . та 2И-НЕ 38 устанавливается сигнал О, который размыкает внутренний : ключ интегратора 36 и обеспечивает ре- жим интегрирования. На вьрсоде логического элемента 2И-НЕ 38 в указанном режиме устанавливается сигнал 1 который поступает на второй вход логического элемента И 41, «а первь1Й вход которого поступает сигнал О с выхода логического элемента НЕ.40, поэтому на выходе логического элемента И 41 устанавливается сигнал О , что обеспечивает разомкнутое состояние ключа 35.

Когда на входе управления блока 22 интегрирования устанаапивается сигнал О, начинается режим считывания информации, или второй такт ин- 55 тегрирования. При этом ключ 34 разкв.1-V кается. На выходе логического элемен-. та НЕ 40 устанавливается сигнал 1 выходные сигналы RS-триггера не изначинается уменьшение по абсолютно значению выходного- напряжения инте ратора и,б. В момент, когда сигнал и меняет знак, на выходе коьшарат 15 ра 37 устанавливается сигнал О.

При этом RS-триггер скачком изменя свое выходное состояние, т.е. на в де логического элемента 2И-НЕ 38

г ii tt

устанавливается

сигнал 1, а на в

ходе логического элемента 2И-НЕ 39 сигнал О. При этом на выходе лог ческого элемента И 41 также устана ливается сигнал О - режим считыв ния информации закончился. Кроме т 25 го, ключ 35 размыкается и по сигн логической единицы с выхода логич кого элемента 2И-НЕ 38 внутренний ключ интегратора 36 замыкается, н нается режим обнуления интегратор или режим ожидания нового интегри вания. При этом выходное состояни компаратора 37 не онределено, так как сигнал на его входе колеблет около нулевого уровня. Однако RS триггер независимо от уровня сигн на первом входе логического элеме 2И-НЕ 38 не изменяет своего выход

состояния до появления сигнала

на входе управления блока 22 инт рирования и начала режима накопле

информации.

использование принципа двухта ного интегрирования позволяет вы лить на выходе блока 22 интегрир 45 ния импульс, продолжительность к рого t пропорциональна интеграл заданном временном интервале t, мы измеряемого сигнала U, и пост ного сигнапа С„. В режиме накопл 50 информации формируется сигнал

L, i- m J

(U.+C.)cJt,

где Т - постоянная времени инте тора 36 в режиме накопл

информации.

В режиме считывания информац сформированный сигнал I, уменьш

т-

1465809

менятся, так как RS-триггер переходит в режим хранения информации. На ныхо- де логического элемента И А1 устанавливается сигнал 1, так как теперь на обоих его входах присутствуют сигналы 1. При этом кпюч 35. размыкается и на второй информационный вход интегратора 36 поступает отрицатель„ сигнал U опорного напряжения,

„ сигнал U опорного напряжения,

- - ньшение по абсолютно

0

30

35

- начинается уменьшение по абсолютному значению выходного- напряжения интегратора и,б. В момент, когда сигнал и меняет знак, на выходе коьшарато- 5 ра 37 устанавливается сигнал О.

При этом RS-триггер скачком изменяет свое выходное состояние, т.е. на выходе логического элемента 2И-НЕ 38

г ii tt

устанавливается

сигнал 1, а на выходе логического элемента 2И-НЕ 39 сигнал О. При этом на выходе логического элемента И 41 также устанавливается сигнал О - режим считывания информации закончился. Кроме то- 25 го, ключ 35 размыкается и по сигналу, логической единицы с выхода логического элемента 2И-НЕ 38 внутренний ключ интегратора 36 замыкается, начинается режим обнуления интегратора .36 или режим ожидания нового интегриро вания. При этом выходное состояние компаратора 37 не онределено, так как сигнал на его входе колеблется около нулевого уровня. Однако RS- триггер независимо от уровня сигнала на первом входе логического элемента 2И-НЕ 38 не изменяет своего выходного

состояния до появления сигнала

Г

на входе управления блока 22 интегрирования и начала режима накопления

информации.

использование принципа двухтактного интегрирования позволяет выделить на выходе блока 22 интегрирова- 45 ния импульс, продолжительность кото- рого t пропорциональна интегралу на заданном временном интервале t, суммы измеряемого сигнала U, и постоянного сигнапа С„. В режиме накопления 50 информации формируется сигнал

L, i- m J

(U.+C.)cJt,

где Т - постоянная времени интегра- тора 36 в режиме накопления

информации.

В режиме считывания информации сформированный сигнал I, уменьшается

13

до нуля, таким образом равенство:

fci

i- и

.«i J

Jt - « Т,,

и.

on

где

Т

постоянная времени интегратора 36 в режиме считывания информации.

Согласно приведенным формулам справедливо тождество

1

Ч--т-- - ( on J

Допустим К« / (Тц,- Uon ) , , так как , тогда:

,

к| (u,+c)dt,

т.е. время считывания информации t пропорционально интегралу суммы измеряемого сигнала и и постоянного сигнала С.

Таким образом, предлагаемое устройство для измерения ортогональных составляющих сигнала по сравнению с прототипом позволяет повысить быстродействие, измеряя параметры переменной составляющей сигнала несколько раз за период указанного измеряемого сигнала.

Формула и 3 о б ре т е н и я

20 входами управления первого и второго накапливающих сумматоров, выходы которых соединены с информационными входами первого и второго регистров соответственно, выходы которых соеди25 йены с первой и второй выходными пш- нами устройства, а второй выход бло- ка преобразования соединен с третьей выходной шиной устройства.

30 2. Устройство по п. 1, отличающееся тем, что блок преобразования содержит усредняющий ана лого-цифровой преобразователь, накапливающий сумматор, блок вычитания,

g регистр, блок задержки, блок деления и блок хранения параметра, причем первый, второй информационные входа и первый вход управления блока преобразования являются соответственно

4Q первым, вторым информационными входами и входом управления усредняющего аналбго-цнфрового преобразователя, выход которого соединен с информационным входом накапливающего суммато45 ра и прямым входом блока вычитания, выход которого является первым выходом блока преобразования, второй вход управления которого соединен с входом управления регистра и через блок за50 держки - с входом управления накапливающего сумматора, выход которого соединен с информационным входом регистра, вьпсод которого является вторым выходом блока преобразования и соешина входного сигнала устройства сое 55 динен с входом числителя блока деле- динена с информационным входом блокания, выход которого соединен с инпреобразования. второй информадаон- . версным входом блока вычитания, а ный вход которого соединен с шинойвход знаменателя - с выходом блока

кода периода входного сигнала и вто-хранения параметра и третьим информа14

рым входом делителя частоты с переменным коэффициентом деления, выход которого соединен с входом кольцевого

счетчика и первым входом управления блока преобразования, второй вход управления которого соединен с выходом Сброс кольцевого счетчика, адресный выход которого соединен с входани трех блоков постоянной памяти, выходы первого и второго блоков постоянной памяти соединены с первыми входами первого и второго блоков умножения соответственно, вторые входы

5 которых соединены с первым выходом блока преобразования, выход третьего блока постоянной памяти соединен с входами управления первого и второго регистров и через блок задержки - с

0 входами управления первого и второго накапливающих сумматоров, выходы которых соединены с информационными входами первого и второго регистров соответственно, выходы которых соеди5 йены с первой и второй выходными пш- нами устройства, а второй выход бло- ка преобразования соединен с третьей выходной шиной устройства.

0 2. Устройство по п. 1, отличающееся тем, что блок преобразования содержит усредняющий ана лого-цифровой преобразователь, накапливающий сумматор, блок вычитания,

g регистр, блок задержки, блок деления и блок хранения параметра, причем первый, второй информационные входа и первый вход управления блока преобразования являются соответственно

Q первым, вторым информационными входами и входом управления усредняющего аналбго-цнфрового преобразователя, выход которого соединен с информационным входом накапливающего суммато45 ра и прямым входом блока вычитания, выход которого является первым выходом блока преобразования, второй вход управления которого соединен с входом управления регистра и через блок за50 держки - с входом управления накапливающего сумматора, выход которого соединен с информационным входом регистра, вьпсод которого является вторым выходом блока преобразования и сое10

соединен с выходом первого блока деления, а выход является выходом усредняющего аналого-цифрового преобразователя.

. Устройство по п. 3, отличающееся тем, что блок интегрирования содержит масштабирующий сумматор, первый и второй ключи, ин- тегратор, компаратор, первьй и второй логические элементы 2И-НЕ, логический элемент НЕ и логический элемент И, причем первый информационный вход блока интегрирования является первым

ционным входом усредняющего аналого- цифрового преобразователя.

ления, вход числителя которого соеди--40 Дон Управления

нен с выходом блока хранения параметра, а выход второго блока деления соединен с инверсным входом блока вычитания, прямой вход которого

управления блока интегрирования соединен с входом управления первого ключа и входом логического элемента НЕ.

5809

16

10

соединен с выходом первого блока деления, а выход является выходом усредняющего аналого-цифрового преобразователя.

. Устройство по п. 3, отличающееся тем, что блок интегрирования содержит масштабирующий сумматор, первый и второй ключи, ин- тегратор, компаратор, первьй и второй логические элементы 2И-НЕ, логический элемент НЕ и логический элемент И, причем первый информационный вход блока интегрирования является первым

-- vпDaвлeния второго ключа, вход

Дон Управления

управления блока интегрирования соединен с входом управления первого ключа и входом логического элемента НЕ.

ycas/K2

Фиг.3

Л JL -$1

-н

-X-.

-фФиг. ft

36

37 1

f

н

| Способ определения параметров полупроводниковых элементов | 1984 |

|

SU1211668A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смаляков В.В | |||

| Цифровая измерительная аппаратура инфранизких частот | |||

| - М.: Энергия, 1975, с | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| П, | |||

Авторы

Даты

1989-03-15—Публикация

1987-03-25—Подача