1

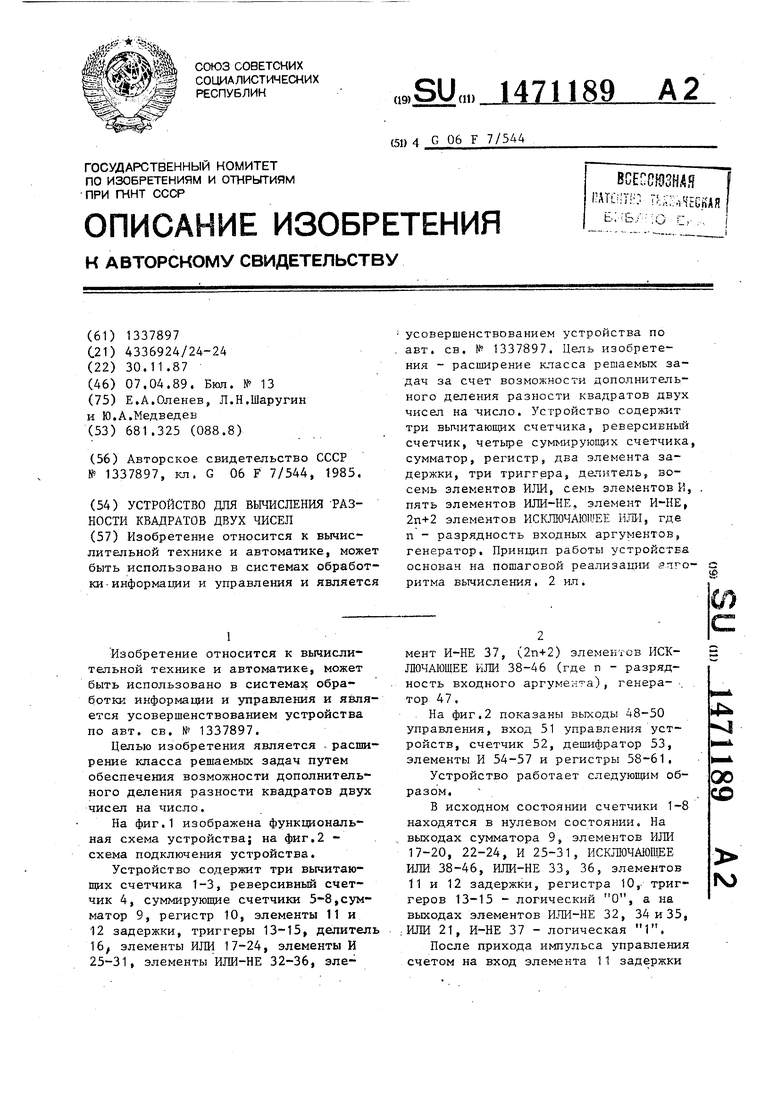

Изобретение относится к вычислительной технике и автоматике, может быть использовано в системах обработки информации и управления и является усовершенствованием устройства по авт. св. № 1337897.

Целью изобретения является . расширение класса решаемых задач путем обеспечения возможности дополнительного деления разности квадратов двух чисел на число.

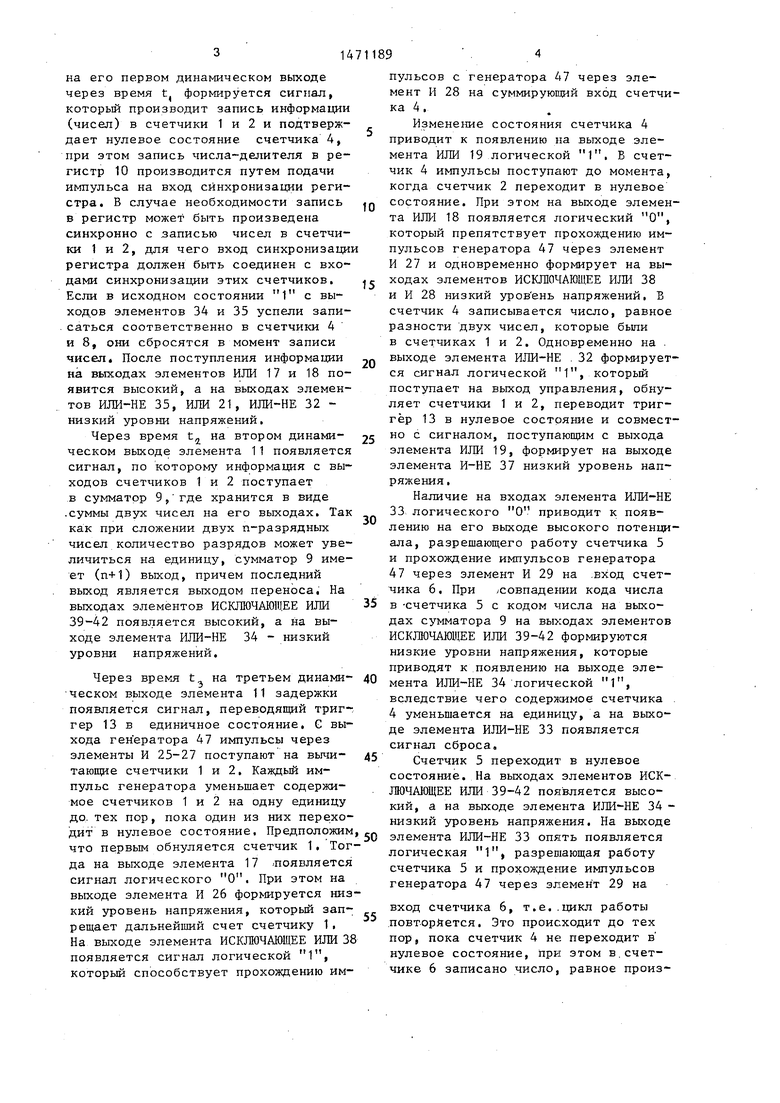

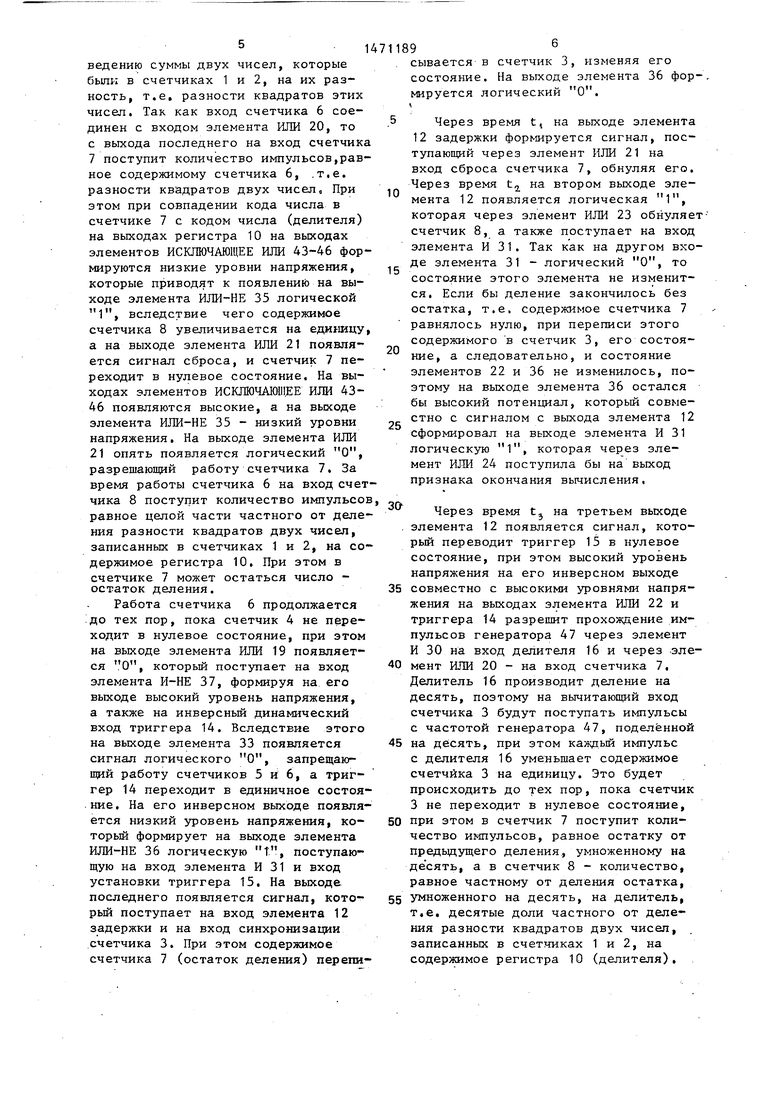

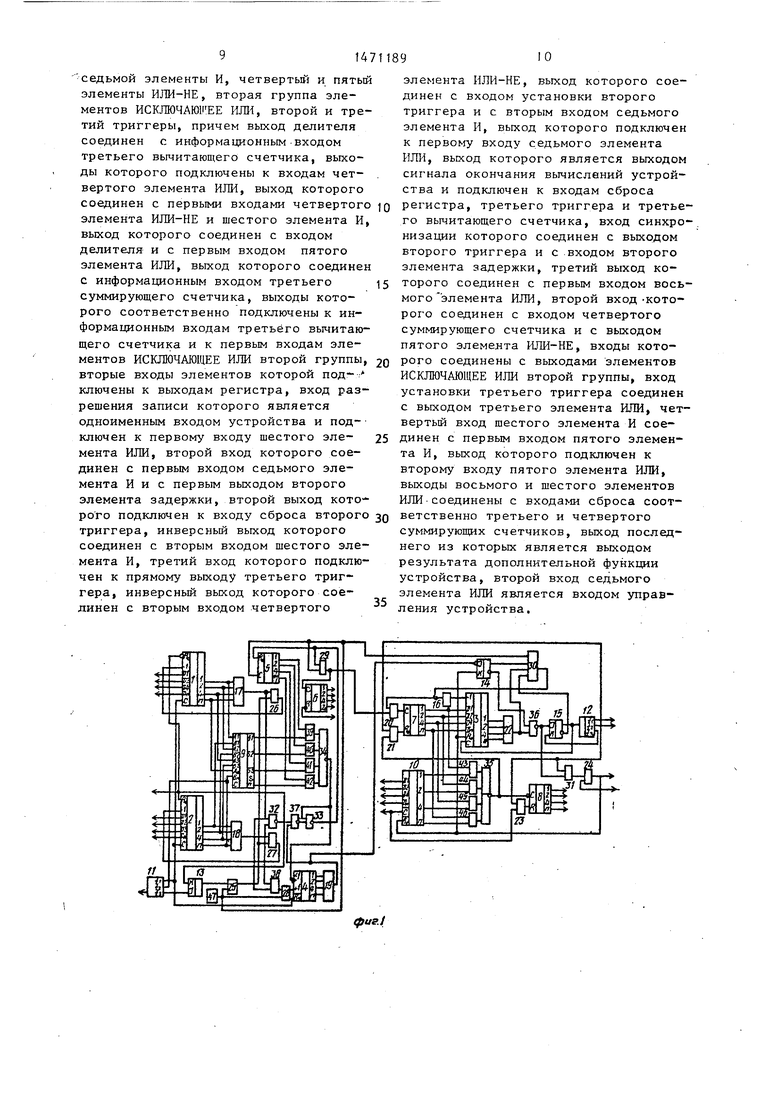

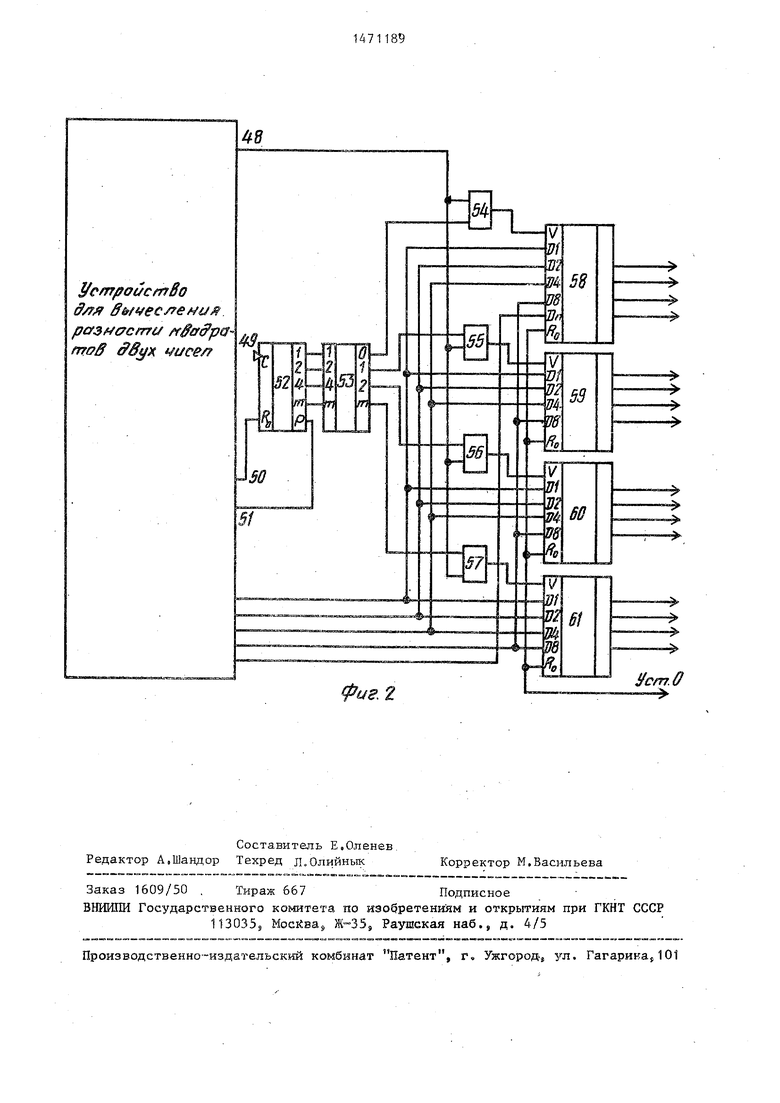

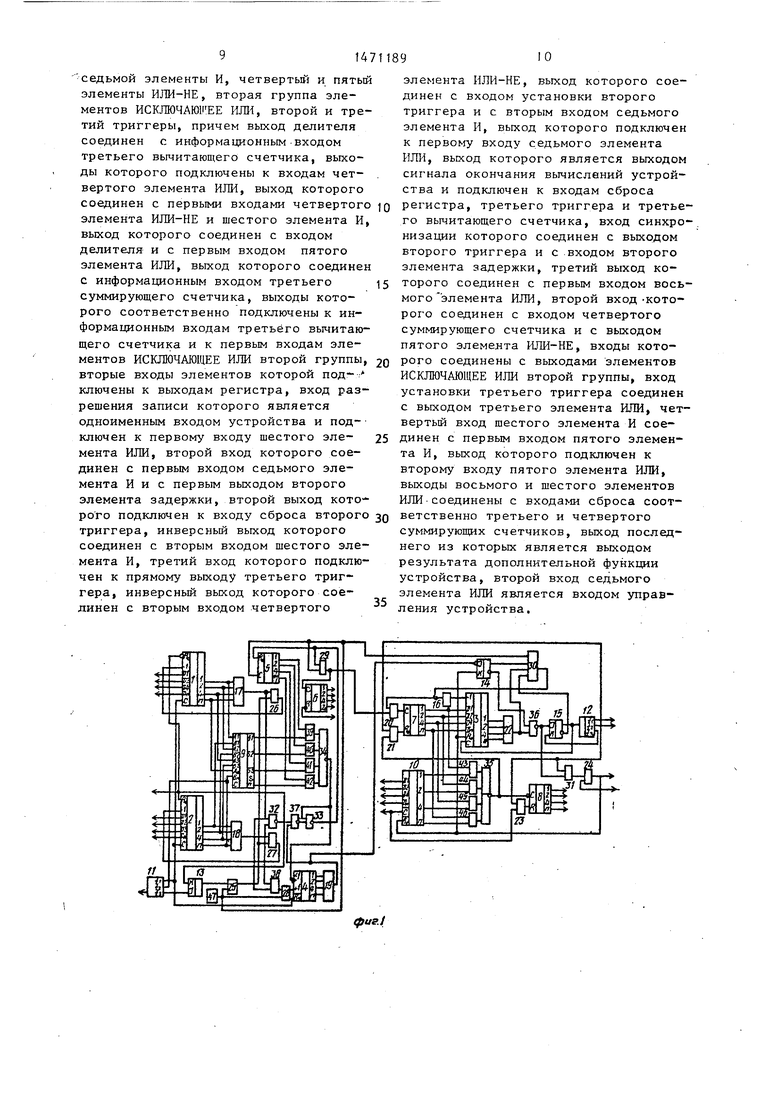

На фиг.1 изображена функциональная схема устройства; на фиг.2 - схема подключения устройства.

Устройство содержит три вычитающих счетчика 1-3, реверсивный счетчик 4, суммирующие счетчики 5-8,сумматор 9, регистр 10, элементы 11 и 12 задержки, триггеры 13-15 делитель 16, элементы ИЛИ 17-24, элементы И 25-31, элементы ИЛИ-НЕ 32-36, элемент И-НЕ 37, (2п+2) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 38-46 (где п - разрядность входного аргумента), генера- -. тор 47.

. На фиг.2 показаны выходы 48-50 управления, вход 51 управления устройств, счетчик 52, дешифратор 53, элементы И 54-57 и регистры 58-61.

Устройство работает следующим образом.

В исходном состоянии счетчики 1-8 находятся в нулевом состоянии. На выходах сумматора 9, элементов ИЛИ 17-20, 22-24, И 25-31, ИСКЛЮЧАЮЩЕЕ ИЛИ 38-46, ИЛИ-НЕ 33, 36, элементов 11 и 12 задержки, регистра 10, триггеров 13-15 - логический О, а на выходах элементов ИЛИ-НЕ 32, 34 и 35, :ШШ 21, И-НЕ 37 - логическая 1.

После прихода импульса управления счетом на вход элемента 11 задержки

СХ)

со

N

на его первом динамическом вьпсоде через время t формируется сигнал, которьй производит запись информации (чисел) в счетчики 1 и 2 и подтверждает нулевое состояние счетчика 4, при этом запись числа-делителя в регистр 10 производится путем подачи импульса на вход синхронизации регистра. В случае необходимости запись в регистр может быть произведена синхронно с записью чисел в счетчики 1 и 2, для чего вход синхронизации регистра должен быть соединен с входами синхронизации этих счетчиков. Если в исходном состоянии 1 с выходов элементов 34 и 35 успели запи- саться соответственно в счетчики 4 и 8, они сбросятся в момент записи чисел. После поступления информации на выходах элементов ИЛИ 17 и 18 появится высокий, а на выходах элементов ИЛИ-НЕ 35, ИЛИ 21, ИЛИ-НЕ 32 - низкий уровни напряжений. Через время t

10

- на втором динамическом выходе элемента 11 появляется сигнал, по которому информация с выходов счетчиков 1 и 2 поступает в сумматор 9, где хранится в виде .суммы двух чисел на его выходах. Так как при сложении двух п-разрядных чисел количество разрядов может увеличиться на единицу, сумматор 9 имеет (п+1) выход, причем последний выход является выходом переноса. На выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 39-42 появляется высокий, а на выходе элемента ИЛИ-НЕ 34 - низкий уровни напряжений.

Через время t на третьем динами- -ческом выходе элемента 11 задержки появляется сигнал, переводящий триггер 13 в единичное состояние. С выхода ген ератора 47 импульсы через элементы И 25-27 поступают на вычитающие счетчики 1 и 2. Каждый импульс генератора уменьшает содержимое счетчиков 1 и 2 на одну единицу ДО- тех пор, пока один из них перехо1471189 .4

пульсов с генератора 47 через элемент И 28 на суммируюпзий вход счетчика 4.

Изменение состояния счетчика 4 приводит к появлению на выходе элемента ИЛИ 19 логической 1, В счетчик 4 импульсы поступают до момента, когда счетчик 2 переходит в нулевое состояние. При этом на выходе элемента ИЛИ 18 появляется логический О, который препятствует прохождению импульсов генератора 47 через элемент И 27 и одновременно формирует на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 38 и И 28 низкий уров ень напряжений. В счетчик 4 записывается число, равное разности двух чисел, которые были в счетчиках 1 и 2. Одновременно на . выходе элемента ИЛИ-НЕ . 32 формируется сигнал логической 1, который поступает на выход управления, обнуляет счетчики 1 и 2, переводит триггер 13 в нулевое состояние и совместно с сигналом, поступающим с выхода элемента ИЛИ 19, формирует на выходе элемента И-НЕ 37 низкий уровень напряжения.

Наличие на входах элемента ИЛИ-НЕ 33 логического О приводит к появлению на его выходе высокого потенци15

20

25

30

35

40

45

ала, разрешающего работу счетчика 5 и прохождение импульсов генератора 47 через элемент И 29 на .вход счетчика 6. При совпадении кода числа в -счетчика 5 с кодом числа на выходах сумматора 9 на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 39-42 формируются низкие уровни напряжения, которые приводят к появлению на выходе элемента ИЛИ-НЕ 34 логической 1, вследствие чего содерясимое счетчика 4 уменьшается на единицу, а на выходе элемента ИЛИ-НЕ 33 появляется сигнал сброса.

Счетчик 5 переходит в нулевое состояние. На выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 39-42 появляется высокий, а на выходе элемешта ИЛИ-НЕ 34 - низкий уровень напряж€;ния. На выходе

дит в нулевое состояние. Предположим,р элемента ИЛИ-НЕ 33 опять появляется

что первым обнуляется счетчик 1. Тогда на выходе элемента 17 .появляется сигнал логического О. При этом на выходе элемента И 26 формируется низлогическая 1, разрешающая работу счетчика 5 и прохождение импульсов генератора 47 через элемен т 29 на

кий уровень напряжения, который зап-вход счетчика 6, т.е..цикл работы

рещает дальнейший счет счетчику 1.довторйется. Это происходит до тех

На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 38пор, пока счетчик 4 не переходит в

появляется сигнал логической 1,нулевое состояние. При этом в.счеткоторый способствует прохождению им-чике 6 записано число, равное произ

ала, разрешающего работу счетчика 5 и прохождение импульсов генератора 47 через элемент И 29 на .вход счетчика 6. При совпадении кода числа в -счетчика 5 с кодом числа на выходах сумматора 9 на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 39-42 формируются низкие уровни напряжения, которые приводят к появлению на выходе элемента ИЛИ-НЕ 34 логической 1, вследствие чего содерясимое счетчика 4 уменьшается на единицу, а на выходе элемента ИЛИ-НЕ 33 появляется сигнал сброса.

Счетчик 5 переходит в нулевое состояние. На выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 39-42 появляется высокий, а на выходе элемешта ИЛИ-НЕ 34 - низкий уровень напряж€;ния. На выходе

элемента ИЛИ-НЕ 33 опять появляется

логическая 1, разрешающая работу счетчика 5 и прохождение импульсов генератора 47 через элемен т 29 на

51

ведению суммы двух чисел, которые бьшк в счетчиках 1 и 2, на их разность, т.е. разности квадратов этих чисел. Так как вход счетчика 6 соединен с входом элемента ИЛИ 20, то с выхода последнего на вход счетчика 7 поступит количество импульсов,равное содержимому счетчика 6, .т.е. разности квадратов двух чисел. При этом при совпадении кода числа в счетчике 7 с кодом числа (делителя) на выходах регистра 10 на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 43-46 формируются низкие уровни напряжения, которые приводят к появлений) на выходе элемента ИЛИ-НЕ 35 логической 1, вследствие чего содержимое счетчика 8 увеличивается на единицу, а на выходе элемента ИЛИ 21 появляется сигнал сброса, и счетчик 7 переходит в нулевое состояние. На выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 43- 46 появляются высокие, а на выходе элемента ИЛИ-НЕ 35 - низкий уровни напряжения. На выходе элемента ИЛИ 21 опять появляется логический О, разрешающий работу счетчика 7. За время работы счетчика 6 на вход счетчика 8 поступит количество импульсов равное целой части частного от деления разности квадратов двух чисел, записанных в счетчиках 1 и 2, на содержимое регистра 10. При этом в

счетчике 7 может остаться число - остаток деления.

Работа счетчика 6 продолжается до тех пор, пока счетчик 4 не переходит в нулевое состояние, при этом на выходе элемента ИЛИ 19 появляется О, который поступает на вход элемента И-НЕ 37, формируя на его выходе высокий уровень напряжения, а также на инверсный динамический вход триггера 14. Вследствие этого на выходе элемента 33 появляется сигнал логического О, запрещающий работу счетчиков 5 и 6, а триггер 14 переходит в единичное состояние. На его инверсном выходе появляется низкий уровень напряжения, который формирует на выходе элемента ИЛИ-НЕ 36 логическую Т., поступающую на вход элемента И 31 и вход установки триггера 15. На выходе последнего появляется сигнал, который поступает на вход элемента 12 задержки и на вход синхронизации счетчика 3. При этом содержимое счетчика 7 (остаток деления) перепи5

0

5

189

сывается в счетчик 3, изменяя его состояние. На выходе элемента 36 фор-.

мируется логический О.

Через время t, на выходе элемента 12 задержки формируется сигнал, поступающий через элемент ИЛИ 21 на вход сброса счетчика 7, обнуляя его. Через время t на втором выходе элемента 12 появляется логическая 1, которая через элемент ИЛИ 23 обнуляет- счетчик 8, а также поступает на вход элемента И 31. Так как на другом входе элемента 31 - логический О, то состо.яние этого элемента не изменится. Если бы деление закончилось без остатка, т.е. содержимое счетчика 7 равнялось нулю, при переписи этого содержимого в счетчик 3, его состояние, а следовательно, и состояние элементов 22 и 36 не изменилось, поэтому на выходе элемента 36 остался бы высокий потенциал, который совместно с сигналом с выхода элемента 12 сформировал на выходе элемента И 31 логическую 1, которая через элемент ИЛИ 24 поступила бы на выход признака окончания вычисления.

/у

Через время t на третьем выходе . элемента 12 появляется сигнал, который переводит триггер 15 в нулевое состояние, при этом высокий уровень напряжения на его инверсном выходе

5 совместно с высокими уровнями напряжения на выходах элемента ИЛИ 22 и триггера 14 разрешит прохождение импульсов генератора 47 через элемент И 30 на вход делителя 16 и через -эле0 мент ИЛИ 20 - на вход счетчика 7. Делитель 16 производит деление на десять, поэтому на вычитающий вход счетчика 3 будут поступать импульсы с частотой генератора 47, поделённой

5 на десять, при этом казкдьй импульс с делителя 16 уменьшает содержимое счетчика 3 на единицу. Это будет происходить до тех пор, пока счетчик 3 не переходит в нулевое состояние,

0 при этом в счетчик 7 поступит количество импульсов, равное остатку от предьщущего деления, умноженному на де сять, а в счетчик 8 - количество, равное частному от деления остатка,

5 умноженного на десять, на делитель, т.е. десятые доли частного от деления разности квадратов двух чисел, записанных в счетчиках 1 и 2, на содержимое регистра 10 (делителя).

.714

После того, как счетчик 3 переходит в нулевое состояние, на выходе элемента ИЛИ 22 появляется О, который запрещает прохождение импульсов с генератора 47 через элемент 30 и формирует на выходе элемента ИЛИ- НЕ 36 логическую 1, которая переводит триггер 15 в- единичное состояние. Нулевой уровень напряжения на инверсном выходе триггера 15 подтверждает запрет на прохождение им- пульсовд генератора 47 через элемент И 30, а высокий уровень напряжения на прямом выходе триггера 15 обеспечивает перезапись остатка деления из счетчика , 7 в счетчик 3, На выходе элемента ИЛИ 22 появляется логическая 1, а на выходе элемента ИЛИ- НЕ 36 - логический О, Далее, сигнал с первого выхода элемента 12 задержки обнулит через элемент ИЛИ 20 счетчик 7, сигнал с второго выхода элемента 12 обнулит счетчик 8, а сигнал с третьего выхода элемента 12 переведет триггер 15 в нулевое состояние. При этом высокие уровни напряжений соответственно с прямого и инверсного выходов триггеров 14 и 15 и выхода элемента ИЛИ 22 обеспечат прохождение импульсов генератора 47 через элемент И 30, цикл счета повторяется, В случае, когда остаток очередного цикла становится равным нулю, сигнал с выхода триггера 15 переписывает нулевую информаци в счетчик 3, подтверждая его состояние, при этом на выходе элемента ИЛИ 22 остается низкий, а на выходе элемента ИЛИ-НЕ 36 - высокий уровни напряжения. По сигналу с второго выхода элемента 12 на выходе элемента И 31 формируется логическая 1, которая поступает через элемент ИЛИ 24 на выход признака окончания вычисления и на входы сброса регистра 10, счетчика 3 и триггера 14, Устройство возвращается в исходное состояние,

Процесс деления в устройстве можно остановить на любом цикле с по- мотцью внешнего сигнала, поступающего на управляющей вход элемента ИЛИ 24, на выходе которого формируется сигнал признака окончания вычисления.

Таким образом, устройство обеспечивает вычисление разности квадратов двух чисел, записанных в счетчиках 1 и 2, а также осуществляет деление этой разности на число, записанное

1858

в регистре 10, с любой степенью точности, причем результат вычисления разности квадратов двух чисел записы- вается в счетчике 6, а результат деления этой разности - на . делитель, т.е, частное выдается в последовательном коде с выходов счетчика 8, Если необходимо получить частное в

0 параллельном коде, ил:и хранить его, устройство можно подключить к памяти (фиг,2),

Б 9ТОМ случае при появлении сигнала на первом выходе 48 элемента 12

5 обеспечивается запись информации через элементы И 54-57 в тот из регистров 58-61, на входе разрешения записи которого будет логическая 1, т,е, на каком выходе дешифратора 53 будет

0 высокий уровень напряжения. После получения целой части частного (так как счетчик 52 и дешифратор 53 находятся в нулевом состоянии) запись по сигналу с выхода 48 произойдет

5 в, регистр 58, Сигнал с второго выхода 49 элемента 12 изменит состояние счетчика 52 на единицу, следовательно, на первом выходе дешифратора 53 будет высокий уровень.напряжения,

0 который после следующего цикла счета обеспечит запись десятьк долей частного в регистр 59. После записи состояние счетчика 52 увеличится еще на единицу, и запись сотых долей частного произойдет в регистр 60 и . Число возможных состояний счетчика . должно быть равно числу регистров памяти. Если деление происходит все время с остатком, при переполнении

д счетчика 52 на его выходе формируется сигнал, которьш поступает на вход 51 управления элемента ИЛИ 24, формируя на его выходе 50 сигнал окончания вычислений, который сбрасывает счет чик 52, 5

Формула изобретения

Устройство для вычисления разности квадратов двух чисел по авт, св.

0 № 1337897, отличающееся тем, что, с целью расширения класса решаемых задач путем обеспечения возможности дополнительного деления разности квадратов двух чисел на чис5 ло, в него введены третий и четвертый суммирующие счетчики, третий вычи- . тающий счетчик, регистр, делитель, второй элемент задерж:ки, с четвертого по восьмой элементы ИЛИ, шестой и

5

седьмой элементы И, четвертый и пятый элементы ИЛИ-НЕ, вторая группа элементов ИСКЛЮЧАЮН ЕЕ ИЛИ, второй и третий триггеры, причем выход делителя соединен с информационным входом третьего вычитающего счетчика, выходы которого подключены к входам четвертого элемента ИЛИ, выход которого соединен с первыми входами четвертого элемента ИЛИ-НЕ и шестого элемента И, выход которого соединен с входом делителя и с первым входом пятого элемента ИЛИ, выход которого соединен с информационным входом третьего суммирующего счетчика, выходы которого соответственно подключены к информационным входам третьего вычитающего счетчика и к первым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы элементов которой под ключены к выходам регистра, вход разрешения записи которого является одноименным входом устройства и под- ключей к первому входу шестого эле- мента ИЛИ, второй вход которого соединен с первым входом седьмого элемента И и с первым выходом второго элемента задержки, второй выход кото- ро го подключен к входу сброса второго триггера, инверсный выход которого соединен с вторым входом шестого элемента И, третий вход которого подключен к прямому выходу третьего триггера, инверсный выход которого соединен с вторым входом четвертого

JQ 15 20 25 зо

5

элемента ИЛИ-НЕ, выход которого соединен с входом установки второго триггера и с вторым входом седьмого элемента И, выход которого подключен к первоьгу входу седьмого элемента ИЛИ, выход которого является выходом сигнала окончания вычислений устройства и подключен к входам сброса регистра, третьего триггера и третьего вычитающего счетчика, вход синхронизации которого соединен с выходом второго триггера и с входом второго элемента задержки, третий выход которого соединен с первьм входом восьмого элемента ИЛИ, второй вход-которого соединен с входом четвертого суммирующего счетчика и с выходом пятого элемента ИЛИ-НЕ, входы которого соединены с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вход установки третьего триггера соединен с выходом третьего элемента ИЛИ, четвертый вход шестого элемента И соединен с первым входом пятого элемента И, выход которого подключен к второму входу пятого элемента ИЛИ, выходы восьмого и шестого элементов ИЛИсоединены с входами сброса соответственно третьего и четвертого суммирующих счетчиков, выход последнего из которых является выходом результата дополнительной функции устройства, второй вход седьмого элемента ИЛИ является входом управления устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления разности квадратов двух чисел | 1985 |

|

SU1337897A1 |

| Цифровая система для программного управления двигателем | 1986 |

|

SU1320793A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для вычисления разности квадратов двух чисел | 1990 |

|

SU1727121A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство измерения напряжения химического источника тока | 1983 |

|

SU1096719A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Автоматический следящий делитель периодов импульсных сигналов | 1984 |

|

SU1234963A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

Изобретение относится к вычислительной технике и автоматике, может быть использовано в системах обработки информации и управления и является усовершенствованием устройства по авт.свид. N 1337897. Цель изобретения - расширение класса решаемых задач за счет возможности дополнительного деления разности квадратов двух чисел на число. Устройство содержит три вычитающих счетчика, реверсивный счетчик, четыре суммирующих счетчика, сумматор, регистр, элементы задержки, три триггера, делитель, восемь элементов ИЛИ, семь элементов И, пять элементов ИЛИ-НЕ, элемент И-НЕ, 2N+2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, где N-разрядность входных аргументов, генератор. Принцип работы устройства основан на пошаговой реализации алгоритма вычисления. 2 ил.

| Устройство для вычисления разности квадратов двух чисел | 1985 |

|

SU1337897A1 |

Авторы

Даты

1989-04-07—Публикация

1987-11-30—Подача