Изобретение относится к вычислительной технике и автоматике и может быть использовано в системах обработки информации и управления.

Известно устройство для вычисления разности квадратов двух чисел, которое содержит генератор импульсов, триггер, реверсивный счетчик, суммирующий счетчик, элементы И, блок синхронизации и сумматор.

Недостатками этого устройства являют- ся ограниченная функциональная возможность и сложность конструкции.

Наиболее близким к предлагаемому является устройство для вычисления разности квадратов двух чисел, содержащее пять счетчиков, триггер, генератор, элемент задержки, сумматор, элементы ИЛИ, элементы И и элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

Недостатком такого устройства является сложность конструкции; кроме того, быстродействие устройства падает с

увеличением разности чисел, над которыми производят операцию вычисления.

Целью изобретения является повышение быстродействия и упрощен неустройства.

Цель достигается тем, что в устройстве для вычисления разности квадратов двух чисел, содержащем генератор тактовых импульсов, триггер, четыре элемента И, два счетчика, блок синхронизации сумматор, три элемента ИЛИ, два элемента ИЛИ-НЕ, группу элементов ИСКЛ ЮЧАЮЩЕ Е ИЛ И, элемент И СКЛ КАЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом первого элемента И.второй вход которого соединен с выходом генератора тактовых импульсов и с первым входом второго элемента И, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходам соответственно первого и второго элементов ИЛИ, к первым входам третьего и четвертого элементов И, вторые входы которых объединены, и к входам первого элемента ИЛИ-НЕ, выход которого соединен с

ю

4 ЬО

входом установки нуля триггера, выходы сумматора соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторые входы которых подключены к выходам первого счетчика, а выходы к входам второго элемента ИЛ И-НЕ, выходы третьего и четвертого элементов И соединены с входами вычитания соответственно первого и второго вычитающих счетчиков, выходы которых соединены с входами соответственно первого и второго слагаемых сумматора и с входами первого и второго элементов ИЛИ, входы синхронизации первого и второго вычитающих счетчиков подключены к первому выходу блока синхронизации, вход запуска которого является одноименным входом устройства, а второй и третий выходы подключены соответственно к входу синхронизации сумматора и входу установки единицы триггера, информационные входы первого и второго вычитающих счетчиков являются соответственно первым и вторым информационными входами устройства, входы сброса первого и второго вычитающих счетчиков объединены и являются входом сброса устройства, выход второго элемента ИЛ И-НЕ соединен с первым входом третьего элемента ИЛИ и входом установки нуля первого счетчика, счетный вход которого объединен со счетным входом второго счетчика и подключен к выходу первого элемента И, третий вход которого объединен с одноименными входами третьего и четвертого элементов И и подключен к выходу триггера, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с инверсным входом второго элемента И, выход которого соединен со вторым входом третьего элемента ИЛИ, выход которого подключен ко второму входу четвертого элемента И..

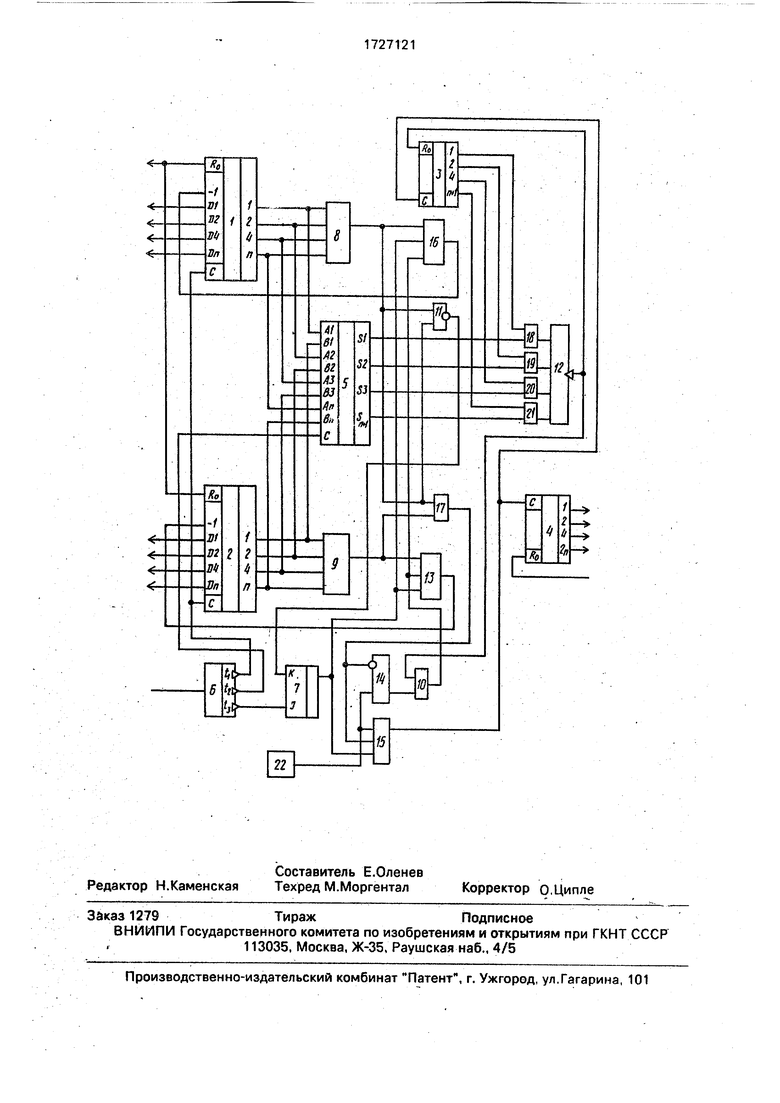

На чертеже представлена функциональная схема устройства для вычисления разности квадратов двух чисел,.где показаны вычитающие счетчики 1 и 2, счетчики 3 и 4, сумматор 5, блок синхронизации 6, триггер 7, элементы ИЛИ8-10, элементы ИЛИ-НЕ 11 и 12, элементы И 13-16, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 17-21 и генератор тактовых импульсов 22..

Устройство работает следующим образом.

В исходном состоянии счетчики 1-4 и триггер 7 находятся в нулевом состоянии. На выходах сумматора 5, элементов ИЛИ 8, 9, ИЛИ-НЕ 12 , И 13, 15, 16, ИСКЛЮЧАЮЩЕЕ ИЛИ 17-21, блока, синхронизации 6 - логический 0, а на выходе элемента ИЛИ-НЕ 11- логическая 1. Импульсы с выхода генератора 22 через элементы И 14 и ИЛИ 10 поступают на входы элементов И 13,16.

После прихода импульса управления на вход элемента 6, на его первом динамическом выходе через время ti формируется сигнал, который производит запись информации (чисел) в счетчики 1 и 2. При этом на выходах элементов ИЛИ 8,9 появляется высокий, а на выходе элемента ИЛИ-НЕ 11 - низкий уровни напряжения. Через время t2 на втором динамическом выходе элемента 6

0 появляется сигнал, по которому информация с выходов счетчиков 1 и 2 поступает в. сумматор 5, где хранится в виде суммы двух чисел на его выходах. Так как при сложении двух n-разрядных чисел количество разря5 дов может увеличиться на единицу, то сумматор 5 имеет п+1 выход, причем последний выход является выходом переноса. На выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 18-21 появляется высокий уровень напряжения, а

0 на выходе элемента ИЛИ-НЕ 12 по прежнему остается логический 0.

Через время t3 на третьем динамическом выходе блока 6 появляется сигнал, пе- реводящий триггер 7 в единичное

5 состояние. Импульсы генератора 22, которые до этого момента поступали на входы элементов И 13, 16 с выхода элемента ИЛИ 10, начинают прохрдить через элементы И 13, 16 на вычитающие входы счетчиков 1 и

0 2. Каждый импульс генератора 22 уменьшает содержимое счетчиков 1 и 2 на одну единицу до тех пор, пока один из них переходит в нулевое состояние. Предположим, что первым обнуляется счетчик 1. Тогда на выходе

5 элемента ИЛИ 8 появляется сигнал логического нуля. При этом на выходе элемента И

16формируется низкий уровень напряжения, который запрещает дальнейший счет счетчику 1. К этому моменту в счетчике 2

0 будет число, равное разности двух чисел, которые были в счетчиках 1 и 2. Одновременно на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

17формируется сигнал логической 1, который через элемент И 14 запрещает, а через

5 элемент И 15 разрешает прохождение импульсов генератора 22.

Счетчики 3 и 4 начинают накапливать счетные импульсы. При совпадении кода числа в счетчике 3 с кодом числа на выходах

0 сумматора 5 на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 18-21 формируются низкие уровни напряжения, которые приводят к появлению на выходе элемента ИЛИ-НЕ 12 логической 1, поступающей на вход сброса

5 счетчика 3 и через элементы ИЛИ 10 и И 13 - на вычитающий вход счетчика 2. Вследствие этого содержимое счетчика 2 уменьшается на единицу, а счетчик 3 обнуляется. Счетчик 3 вновь начинает накапливать информацию, весь цикл работы повторяется.

Это будет продолжаться до тех пор, пока счетчик 2 не перейдет в нулевое состояние. При этом в счетчике 4 будет записано число, равное произведению суммы двух чисел, которые были в счетчиках 1 и 2, на их разность, т.е. разность квадратов этих чисел.

После того как счетчик 2 перейдет в нулевое состояние, на выходе элемента ИЛИ- НЕ 11 формируется сигнал логической 1, который переведет триггер 7 в нулевое состояние. Наличие низкого потенциала на выходах элементов И 13, 15, 16 запрещает работу счетчиков 1-4.

Сигналы с выхода триггера 7 можно также использовать в качестве признака окончания работы устройства.

Формула изобретения Устройство для вычисления разности квадратов двух чисел, содержащее генератор тактовых импульсов, два счетчика, триггер, первый и второй вычитающие счетчики, сумматор, три элемента ИЛИ, блок синхронизации, четыре элемента И, первый и второй элементы ИЛИ-НЕ, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов и с первым входом второго элемента И, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к вы ходам соответствен но первого и второго элементов ИЛИ, к первым входам соответственно третьего и четвертого элементов И, вторые входы которых объединены, и к одноименным входам первого элемента ИЛИ-НЕ, выход которого соединено входом установки нуля триггера, выходы сумматора соединены с первыми

входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторые входы которых подключены к выходам первого счетчика, а выходы - к входам второго элемента ИЛИ-НЕ, выходы третьего и четвертого элементов И соединены с входами вычитания соответственно первого и второго вычитающих счетчиков, выходы которых соединены с входами соответственно первого и второго слагаемых

сумматора и с входами первого и второго элементов ИЛИ, входы синхронизации первого и второго вычитающих счетчиков под- ключены к первому выходу блока синхронизации, вход запуска которого является одноименным входом устройства, а второй и третий выходы подключены соответственно к входу синхронизации сумматора и входу установки единицы триггера, информационные входы первого и второго

вычитающих счетчиков являются соответственно первым и вторым информационными входами устройства, а их входы сброса объединены и являются входом сброса устройства, отличающееся тем, что, с целью

повышения быстродействия и упрощения устройства, выход второго элемента ИЛИ- Н Е соединен с первым входом третьего эле- мента ИЛИ и входом установки нуля первого счетчика, счетный вход которого

объединен со счетным входом второго счетчика и подключен к выходу первого элемента И, третий вход которого объединен с одноименными входами третьего и четвертого элементов И и подключен к выходу

триггера, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с инверсным входом второго элемента И, выход которого соединен со вторым входом третьего элемента ИЛИ, выход которого подключен ко второму входу

четвертого элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления разности квадратов двух чисел | 1985 |

|

SU1337897A1 |

| Устройство для вычисления разности квадратов двух чисел | 1987 |

|

SU1471189A2 |

| Преобразователь частоты в код | 1988 |

|

SU1797159A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД | 1989 |

|

RU2075829C1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Преобразователь амплитуда-код нестационарных механических колебаний | 1987 |

|

SU1481888A1 |

| Устройство для определения дисперсии | 1982 |

|

SU1092522A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство для вычисления логарифма | 1984 |

|

SU1179328A1 |

| Устройство для определения средне-КВАдРАТичНОгО зНАчЕНия | 1979 |

|

SU842834A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в системах обработки информации и управления. Цель изобретения - повышение быстродействия и упрощение устройства. Устройство содержит четыре счетчика, три элемента ИЛИ, п+2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, где п разрядность входного аргумента, четыре элемента И, два элемента ИЛИ-НЕ, триггер, генератор, элемент задержки, сумматор с соответствующими связями. Принцип работы устройства основан на пошаговой реализации алгоритма вычисления под управлением блока син- хронизации с тремя динамическими выходами. 1 ил.

| Цифровое вычислительное устройство | 1977 |

|

SU739529A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления разности квадратов двух чисел | 1985 |

|

SU1337897A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-15—Публикация

1990-07-17—Подача