в в, 1, 6г 1Ј

ПП П

етЪ .

11

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий между ЭВМ | 1989 |

|

SU1695300A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Многоканальное устройство диспетчеризации | 1989 |

|

SU1689950A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1539779A1 |

| Многоканальное устройство для управления обслуживанием запросов | 1988 |

|

SU1552183A1 |

| Устройство переменного приоритета | 1988 |

|

SU1640689A1 |

| Многоканальное приоритетное устройство | 1984 |

|

SU1239716A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для приоритетного управления | 1982 |

|

SU1070552A1 |

| Многоканальное устройство приоритета | 1989 |

|

SU1686444A1 |

Изобретение относится к вычислительной технике и может найти применение при построении вычислительных комплексов. Цель изобретения - сокращение объема оборудования. Устройство содержит блок 2 выделения запросов и группу блоков элементов И 3. Очередной поступающий на вход устройства запрос направляется на ту ЭВМ, число решаемых задач в которой минимально, а при равенстве решаемых задач - на ЭВМ с минимальным номером, что обеспечивает равномерную загрузку всех ЭВМ. 2 ил.

о о

о о

Фиг.1

т

Изобретение относится к вычислительной технике и может найти применение при построении вычислительных комплексов.

Цель изобретения - сокращение объема оборудования.

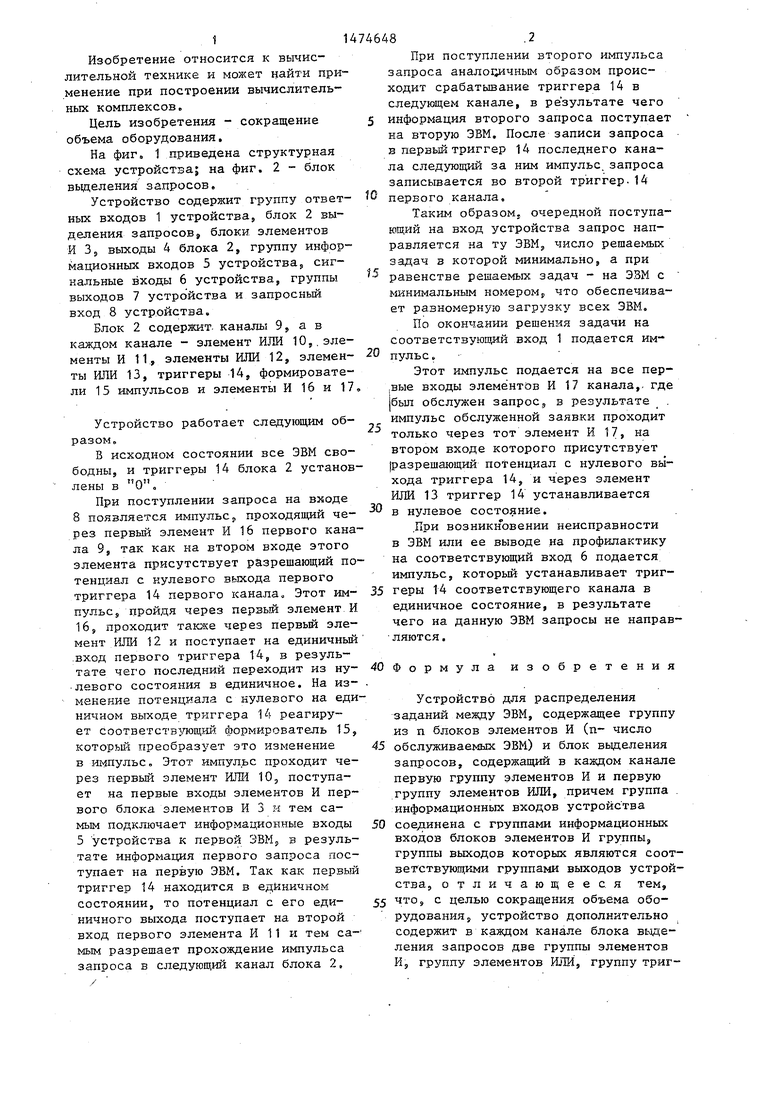

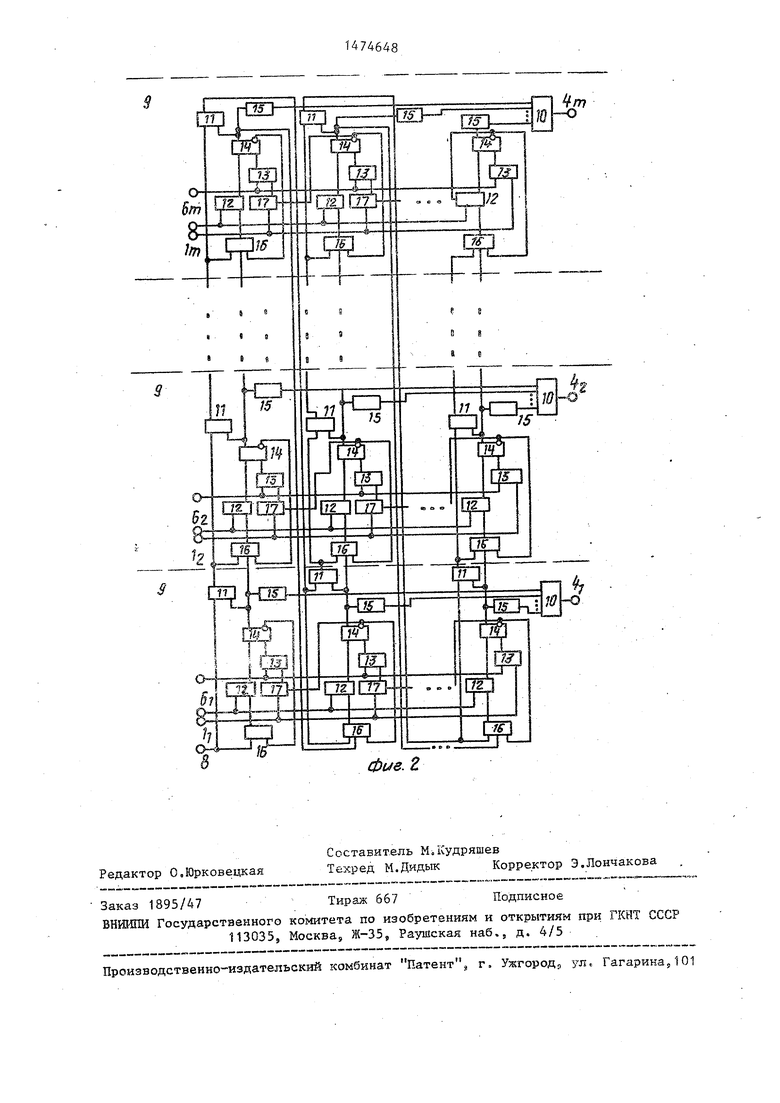

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - блок выделения запросов.

Устройство содержит группу ответ- ных входов 1 устройстваs блок 2 выделения запросов, блоки элементов И 3„ выходы 4 блока 2, группу информационных входов 5 устройства,, сигнальные входы 6 устройства, группы выходов 7 устройства и запросный вход 8 устройства.

Блок 2 содержит каналы 9, а в каждом канале - элемент ИЛИ 10, элементы И 11, элементы ИЛИ 12, элемен- ты ИЛИ 13, триггеры 14, формирователи 15 импульсов и элементы И 16 и 17

Устройство работает следующим об- разом.

В исходном состоянии все ЭВМ свободны, и триггеры 14 блока 2 установлены в О,

При поступлении запроса на входе 8 появляется импульс, проходящий через первьй элемент И 16 первого канала 9, так как на втором входе этого элемента присутствует разрешающий потенциал с кулевого выхода первого триггера 14 первого канала. Этот им- пульс9 пройдя через первый элемент И 16, проходит также через первьй элемент ИЛИ 12 и поступает на единичный вход первого триггера 14, в результате чего последний переходит из ну- левого состояния в единичное. На изменение потенциала с кулевого на единичном выходе триггера Ь реагирует соответствующий Формирователь 15, который преобразует это изменение в импульс. Этот импульс проходит через первый элемент ИЛИ 10, поступает на первые входы элементов И первого блока элементов И 3 и тем самым подключает информационные входы 5 устройства к первой ЭВМ, в результате информация первого запроса поступает на первую ЭВМ. Так как первый триггер 14 находится в единичном состоянии, то потенциал с его еди- ничного выхода поступает на второй вход первого элемента И 11 и тем самым разрешает прохождение импульса запроса в следующий канал блока 2,

5 0 5 0 5

При поступлении второго импульса запроса аналогичным образом происходит срабатывание триггера 14 в следующем канале, в результате чего информация второго запроса поступает на вторую ЭВМ. После записи запроса в первый триггер 14 последнего канала следующий за ним импульс запроса записывается во второй триггер.14 первого канала.

Таким образом, очередной поступающий на вход устройства запрос направляется на ту ЭВМ, число решаемых задач в которой минимально, а при равенстве решаемых задач - на ЭВМ с минимальным номером, что обеспечивает равномерную загрузку всех ЭВМ,

По окончании решения задачи на соответствующий вход 1 подается импульс.

Этот импульс подается на все первые входы элементов И 17 канала, где был обслужен запрос, в результате импульс обслуженной заявки проходит только через тот элемент И 17, на втором входе которого присутствует (разрешающий потенциал с нулевого выхода триггера 14, и через элемент ИЛИ 13 триггер 14 устанавливается в нулевое состояние.

При возникновении неисправности в ЭВМ или ее выводе на профилактику на соответствующий вход 6 подается импульс, который устанавливает триггеры 14 соответствующего канала в единичное состояние, в результате чего на данную ЭВМ запросы не направляются .

Формула изобретения

Устройство для распределения заданий между ЭВМ, содержащее группу из п блоков элементов И (п- число обслуживаемых ЭВМ) и блок выделения запросов, содержащий в каждом канале первую группу элементов И и первую группу элементов ИЛИ, причем группа информационных входов устройства соединена с группами информационных входов блоков элементов И группы, группы выходов которых являются соответствующими группами выходов устройства, отличающееся тем, что9 с целью сокращения объема оборудования s устройство дополнительно содержит в каждом канале блока выделения запросов две группы элементов И, группу элементов ИЛИ, группу триггеров, группу формирователей импульсов и элемент ИЛИ, причем вход запроса устройства соединен в блоке выделения запросов с первыми входами первых элементов И первой и второй групп, выход первого элемента И второй группы каждого канала, кроме выхода первого элемента И второй группы последнего канала, соединен с пер вым входом первого элемента И первой группы и с первым входом первого элемента И второй группы следующего канала, выход каждого элемента И первой группы в каждом канале сое- динен с первым входом одноименного элемента ИЛИ первой группы своего канала, первые входы элементов И третьей группы каждого канала соединены содноименным ответным входом устройства, второй вход каждого элемента И третьей группы в каждом канале соединен с инверсным выходом следующего по номеру триггера группы данного канала, первые входы элементов ИЛИ второй группы каждого канала, кроме последних элементов, соединены с выходами одноименных элементов И третьей группы данного канала, первый вход последнего эле- мента ИЛИ второй группы каждого канала соединен с одноименным ответным входом устройства, вторые вяоды элементов ИЛИ первой и второй групп в каждом канале соединены соответственно с одноименным сигнальным и с одноименным входом сброса устройства второй вход первого элемента И первой группы в каждом канале соединен с инверсным выходом-первого триггера группы своего канала, первый вход каждого элемента И первой группы, начиная с второго, в каждом канале соединен с инверсным выходом одноименного триггера группы своего кана

Q 0 5 п

0

ла, второй вход каждого элемента И, начиная с второго, первой группы в каждом канале, начиная с второго, соединен с прямым выходом одноименного триггера группы предыдущего канала, третий вход первого элемента И первой группы в каждом канале, начиная с второго, соединен с прямым выходом первого триггера группы предыдущего канала, третий вход каждого элемента И первой группы, начиная с .второго, каждого канала,, начиная с ВТОРОГО, соединен с выходом одноименного элемента И второй группы предыдущего канала, второй вход первого элемента И второй группы каждого канала соединен с прямым выходом первого триггера группы своего канала, первый вход каждого элемента И, начиная с второго, второй группы каждого канала, начиная с второго, соединен с выходом одноименного элемента И второй группы предыдущего канала, второй вход каждого элемента И второй группы каждого канала, начиная с второго, кроме последнего, соединен с прямым выходом одноименного триггера своего канала, прямой выход триггера каждого канала соединен с входом одноименного формирователя импульсов группы своего канала, выходы формирователей импульсов группы каждого канала соединены с входами элемента ИЛИ своего канала, первые входы элементов И первой и второй групп первого канала, начиная с второго элемента И, соединены с выходом предыдущего по номеру элемента И второй группы последнего канала, третий вход каждого элемента И, начиная с второго, первой группы первого канала соединен с прямым выходом предыдущего по номеру триггера группы последнего канала.

| Устройство для распределения заданий процессорам | 1983 |

|

SU1111165A1 |

| Устройство для распределения заданий между ЭВМ | 1983 |

|

SU1111163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-27—Подача