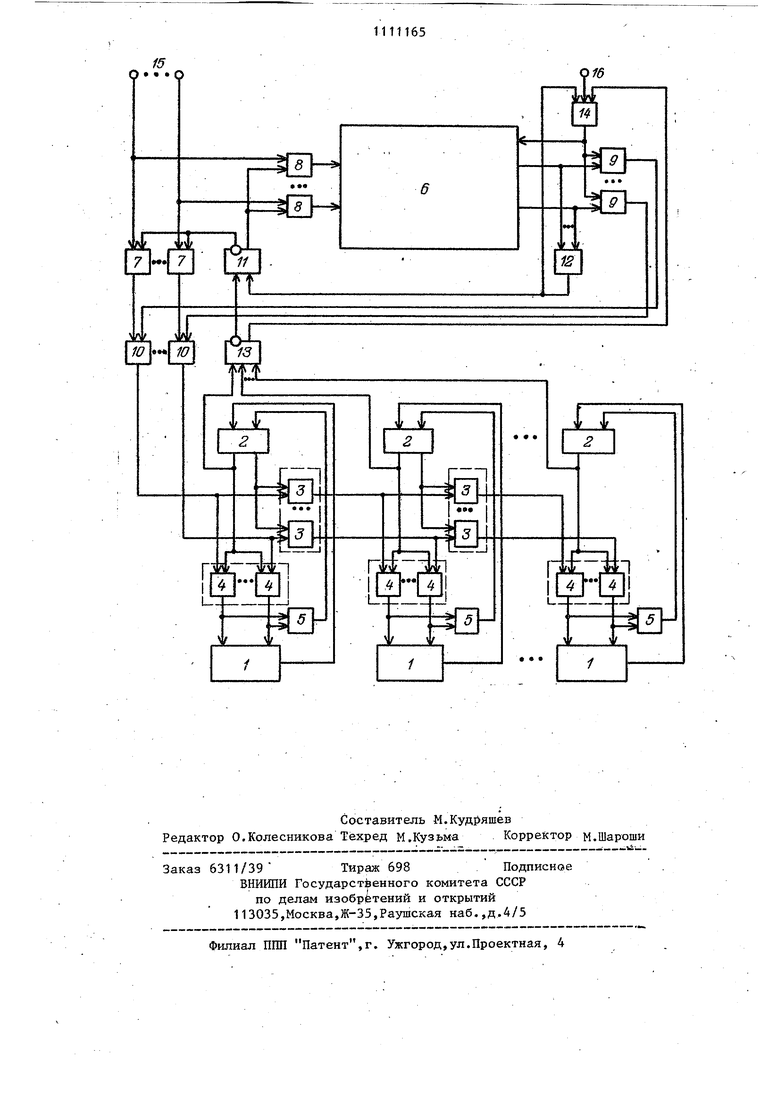

Изобретение относится к вьиислительной технике и может быть использ вано в многопроцессорныхсистемах дл распределения нагрузки между процессорами. Известно устройство для распределения заданий процессорам, содержащее процессоры, группы элементов И; элементы ИЖ регистр готовности процессоров, регистр сдвига, узел управления til. Недостатком этого устройства является низкое быстродействие, обусловленное использованием последовательно работающего сдвига, а также возможность отказа в выполнении задания в случае, если число свободных процессоров меньше их потребного количества. . Наиболее близким по технической сущности к изобретению является устройство для распределения заданий процессорам, содержащее блок управления, йервую и вторую группы,элемен тов И, регистр сдвига, элемент ИЛИ, блок элементов ИЛИ, группу регистров хранения, элемент И, регистр готовности процессоров, группа выходов ко торого соединена с группой информаци онных входов блока управления и с первыми входами элементов И первой группы, вторые входы которьк соедине ны с группой выходов регистра сдвига и с группой входов элемента ИЛИ, выход которого соединен с управляющим входом блока управления, первый выхо которого соединен с управляющим входом регистра сдвига, вход сброса которого соединен с выходом блока элементов ИЛИ и с входом сброса регистра готовности процессоров, группа информационных входов которого соеди нена с выходами процессоров группы, входы которых соединены с выходами элементов И первой группы и с входам блока элементов. ИЛИ, rpyiina информационных входов первого регистра хранения группы является группой входов заданий устройства, управляющий вход каждого регистра хранения группы сое динен с выходом соотв.етствующего элемента И второй группы, группа информационных выходов каждого регистра хранения группы,кроме последнего,соединена с группой информационных входов последующего регистра хранения группы, первая и вторая группв разрядньпс выходов последнего регистра хранения группы соединена соответственно с третьими входами элементов И первой групгаг и с группой информацирнньк входов регистра сдвига, вход сдвига которого соединен с выходом элемента И, первый вход которого соединен с выходом старшего разряда группы выходов регистра сдвига, второй вход элемента И соединен с выходом элемента ИЖ и с первыми входами элементов И второй группы, второй вход каждого элемента И второй группы, кроме последнего, соединен с выходом последующего элемента И этой группы, второй вход последнего элемента И второй группы соединен с вторым выходом блока управления 121. Цель изобретения - повьшение быстродействия устройства. Поставленная цель достигается тем, что в устройство для распределения заданий процессорам, содержащее регистр готовности процессоров, блок регистров, первую и вторую группы элементов И, первую группу элементов ИЛИ, элемент И, первый элемент ИЛИ, причем выходы процессоров соединены с единичными входами регистра готовности процессоров, выходы элементов И первой группы соединены с группой входов блока регистров, введены третья группа элементов И, вторая группа элементов ИЛИ, второй и третий элементы ИЛИ. и две группы блоков элементов И, причем информационные входы устройства соединены с первыми входами элементов И первой и второй групп, к вторым входам элементов И второй группы подключен инверсный вькод первого элемента ИЛИ, прямой вькод которого соединен с вторыми входами элементов И первой группы, выходы блока регистров соединены с первыми входами элементов И третьей группы и с входами второго элемента ИЛИ, выход которого соединен с первыми входами элемента И, выходы элементов И второй группы соединены с дервыми входами одноименных элементов ИЛИ первой группы, вторые входы которых соединены с выходами одноименных элементов И третьей группы, группа выходов элементов ИЛИ первой группы соединена с группами входов первьк блоков элементов И первой и второй группы, управляющие входы блоков элементов И первой и второй групп соединены соответственно с прямым и инверсным выходами одноименных разрядов регистра готовности процессоров, группа выходов к-аждого блока элементов И первой группы соединена с группой входов следующего блока элементов И первой и второй групп, группы выходов блоков элементов И второй группы соединены с группами входов одноименных процессоров и с группами входов одноименных элементов ИЛИ второй группы, выход каждого элемента ИЛИ второй группы соединен с нулевым входом одноименного разряд регистра готовности процессоров, вьг ход второго элемента ИЛИ соединен с первьм входом первого элемента ИЛИ, второй вход которого соединен с инве сньм выходом третьего элемента ИЛИ, прямой выход и входы которого соединены соответственно с вторым входом элемента И и прямыми выходами ре гистра готовности процессоров, третий вход элемента И соединен с тактовьм входом устройства, выход элемента И соединен с тактовым входом блока регистров и вторыми входами элементов И третьей группы. На чертеже представлена структурная схема устройства. Устройство содержит процессоры 1, регистр готовности процессоров 2, блоки элементов И 3,4, группу элемен тов ИЛИ 5, блок регистров 6, группы элементов И 7-9, группу элементов ИЛ 10,элементы ИЛИ 11-13, элемент И 14 информационные входы 15, тактовый вход 14. Устройство работает следующим образом. В исходном состояниипроцессоры 1 свободны, триггеры регистра готовности процессоров 2 находятся в единичном состоянии. Единичные сигналы поступают на входы элемента ИЛИ-13 и с его инверсного выхода нулевой сигнал поступает на вход элемента ИЛИ 11,на второй вход которого также поступает нулевой сигнал с выхода элемента ИЛИ 12. Элементы И 7 открыт а элементы И 8 закрыты. Так как триг геры находятся в единичном состоянии то элементы И 4 открыты, а элементы И 3 закрыты. Поступающее на входы 15 устройств задание, пройдя И 7, ИЛИ 10 И 8, поступает на первый процессор, одновременно через элемент ИЛИ 5, первый триггер устанавливается в нул вое состояние, открываются элементы И 3, подготавливая таким образом поступление очередного задания во второй процессор. Второе задание, поступающее на входы устройства 15, . пройдя элементы И 7, ИЛИ 10, И 3, И 4, поступает во второй процессор и устанавливает через второй элемент ИЛИ 5 соответствующий триггер в нулевое состояние, разрешая тем самым поступление очередного задания в следующий процессор. После выполнения задания процессор устанавливает соответствующий триггер в единичное состояние. Очередное задание поступает в один из свободных процессоров начиная с первого. Если все процессоры заняты, что соответствует нулевым сигналам на . входах элемента ИЛИ-13, то на вход элемента ИЛИ 11 с инверсного выхода элемента ИЛИ 13 поступает единичный сигнал и элементы И 7 закрьшаются, а элементы И 8 открываются. Поступающее очередное задание через элементы И 8 поступает в блок запоминающих регистров 6. Так как на выходах блока запоминающих регистров не нулевой сигнал то на выходе элемента ИЛИ 12 единичный сигнал, которьпЧ поступает на вход элемента ИЛИ 11. С прямого выхода элемента ИЛИ 11 единичный сигнал поступает на вход элементов И 8, а нулевой сигнал на вход элементов И 7. Как только освободится один из процессоров, что соответствует наличию единичного сигнала на входе элемента ИЛИ 13, открывается элемент И 14, так как с выходов элементов ИЛИ 12, 13 на вход элемента И 14 поступают единичные сигналы. Поступающий тактовый импульс разрешает считывание первого задания из блока запоминающих регистров через элементы И 9, которое поступает через элементы ИЛИ 10, И 3,4 в свободный процессор. Элементы И 14, И 8 закрываются, а элементы И 7 открываются, и поступающее задание на входы устройства 15 поступит, минуя блок 6, в один из свободных процессоров 1. Таким образом, при наличии свободных процессоров 1 задания поступают на обработку, минуя блок 6, если процессоры заняты, то задание поступит в блок 6. Применение изобретения позволяет повысить быстродействие устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1983 |

|

SU1151966A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| Устройство для распределения задач между процессорами | 1988 |

|

SU1532929A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1269136A1 |

| Устройство для распределения групповых заявок по процессорам | 1985 |

|

SU1254485A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1246096A1 |

| Устройство для диспетчеризации заявок | 1985 |

|

SU1247873A1 |

| Устройство для распределения заданий процессорам | 1986 |

|

SU1410029A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1413630A1 |

) УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙПРОЦЕССОРАМ, содержащее регистр готовности процессоров, блок регистров, первую и вторую группы элементов И, первую группу элементов ИЛИ, элемент И, первый элемент ИЛИ, причем выходы процессоров соединены с единичными входами регистра готовности процессоров, выходы элементов И первой группы соединены с группой входов блока регистров, о т л и ч аю щ е е с я тем, что, с целью повышения быстродействия, в устройство введены третья группа элементов И, вторая группа элементов ИЛИ, второй и третий элементы ИЛИ и две группы блоков элементов И, причем информационные входы устройства соединены с первьши входами элементов И первой и второй групп,к вторым входам элементов И второй группы подключен ин, версный выход первого элемента ИЛИ, прямой выход которого соединен с вторыми входами элементов И первой группы, выходы блока регистров соединены с П1ервыми входами элементов И третьей группы и с входами второго элемента ИЛИ, выход которого соединен с первыми входами элемента И, выходы элементов И второй группы соединены с первыми входами одноименных элементов ИЛИ первой группы, вторые входы koTopbK соединены с выходами одноименных элементов И третьей группы, группа выходов элементов ИЛИ первой группы соединена с группами входов первых блоков элементов И первой и второй групп, управлякицие входы блоков элементов И первой и второй групп соединены соответственно с прямым и инверсным выходами одноименных разрядов регистра готовности процессоров, группа выходов каждого блока элементов И первой группы соединена с группой входов следуюО) щего .блока элементов И первой и второй групп, группы выходов блоков элементов И второй группы соединены с группами входов одноименньсх процесв соров и группами входов одноименных элементов ШШ второй группы, выход каждого элемента ИЛИ второй группы соединен с нулевым входом одноименного разряда регистра готовности процессоров, выход второго элемента ИЛИ соединен с первым входом первого элеО5 мента ИЛИ, второй вход которого сое-, ел динен с инверсным выходом третьего элемента ИЛИ, прямой выход и входы которого соединены соответственно с вторым входом элемента И и прямыми выходами регистра готовности процессоров, третий вход элемента И соединен с тактовым входом устройства, выход элемента И соединен с тактовым входом блока регистров и вторыми входами элементов И третьей группы.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для распределения заданий процессорам | 1977 |

|

SU629538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для распределения заявок по процессорам | 1979 |

|

SU866560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-30—Публикация

1983-04-08—Подача