Изобретение относится к вычислительной технике и может быть применено при построении вычислительных комплексов.

Цель изобретения - расширение области применения устройства за счет учета приоритета заданий при их распределении.

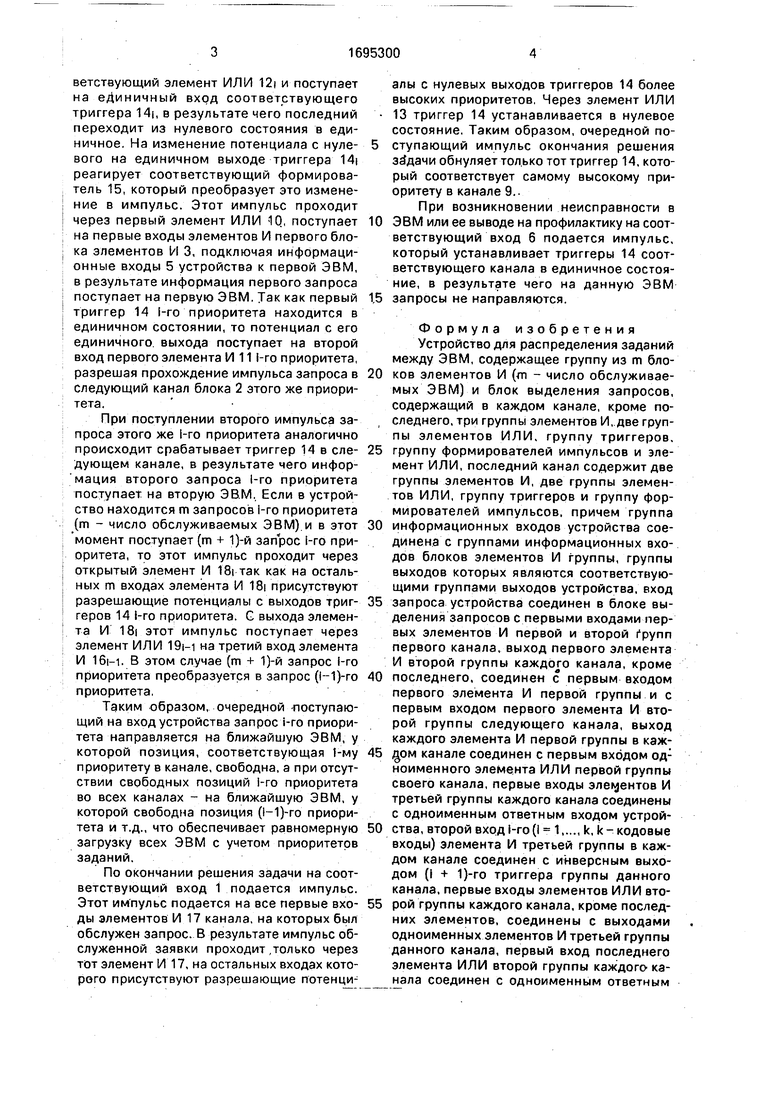

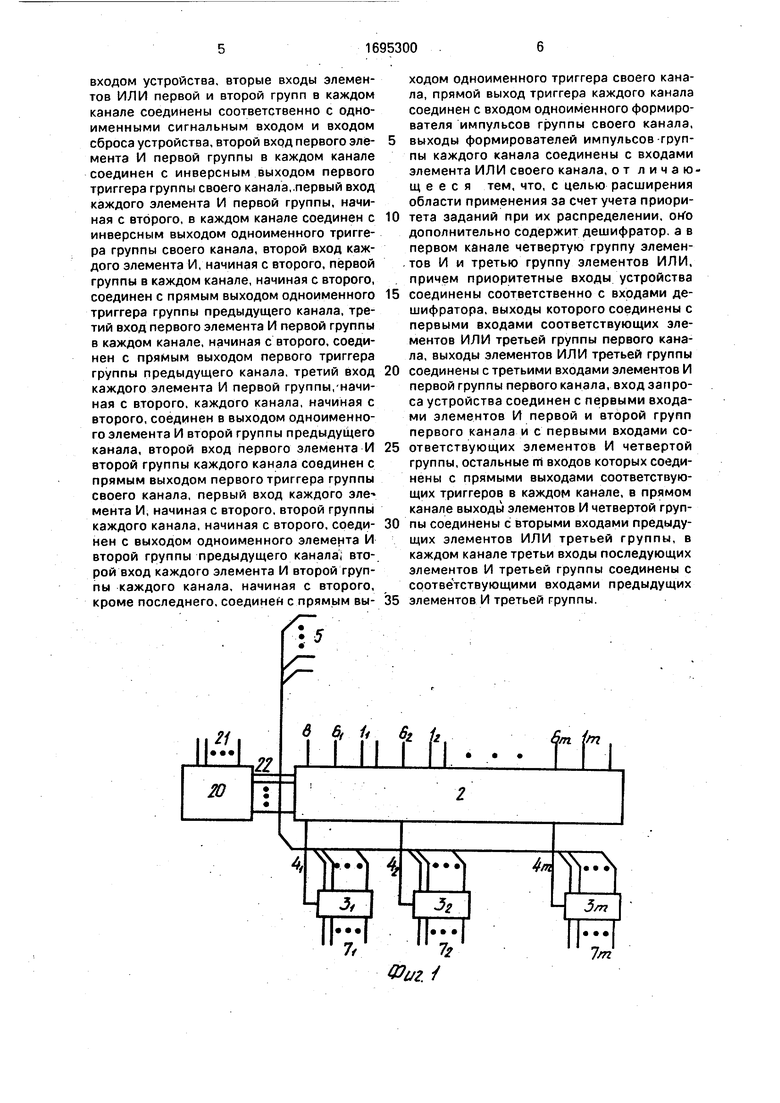

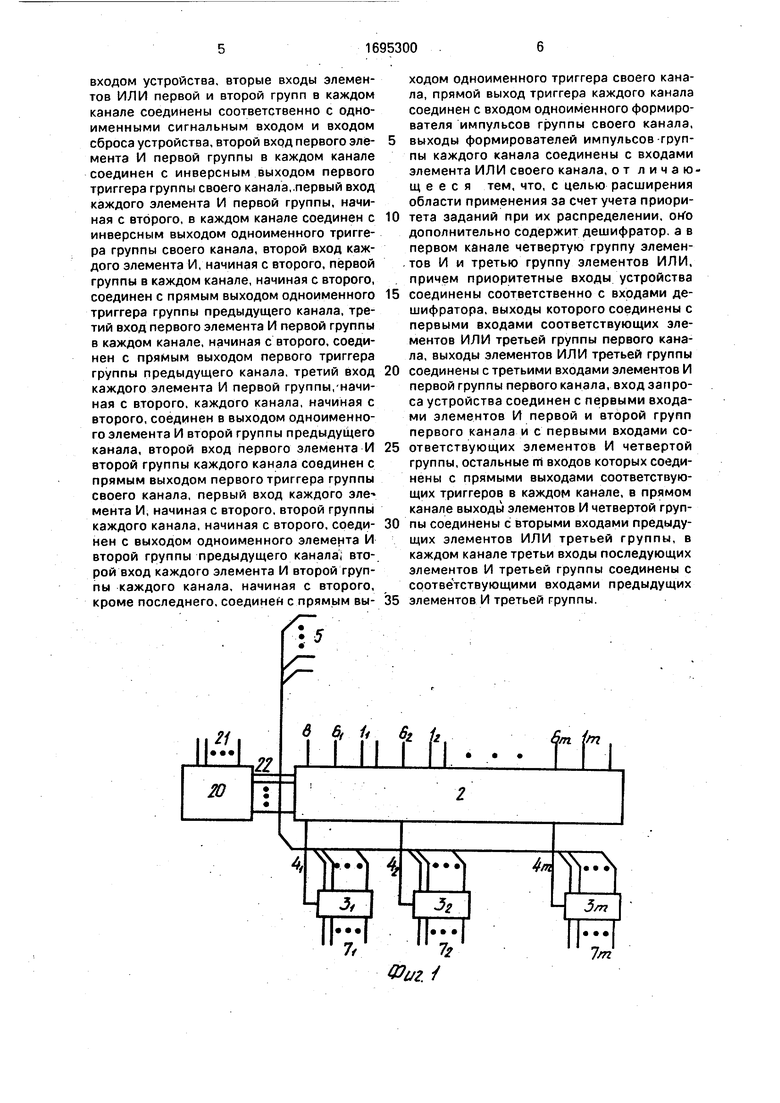

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - блок выделения запросов.

Устройство имеет группу ответных входов 1 устройства, блок 2 выделения запро- , сов, блоки элементов И 3, выходы 4 блока 2, группу информационных входов 5 устройства, сигнальные входы 6 устройства, группы выходов 7 устройства и вход 8 запроса устройства.

Блок 2 выделения запросов содержит каналы 9, каждый из которых состоит из элемента ИЛИ 10, элемента И 11, элемента ИЛИ 12, элемента ИЛИ 13, триггера 14, формирователя 15 импульсов и элементов И 16 и 17, а также элементы И 18 и элементы ИЛИ 19.

В устройство также входят дешифратор 20, приоритетные входы 21 и кодовые входы 22.

Устройство работает следующим образом.

В исходном состоянии все ЭВМ свободны, триггеры 14 блока 2 установлены в О.,

При поступлении запроса одновременно появляются импульс на входе 8 и код, соответствующий приоритету запроса (задания), на входах 21 дешифратора 20. Код приоритета запроса дешифрируется в дешифраторе 20 в результате чего на одном из его выходов 22i появляется импульс, где i 1, R (k - число приоритетов). Этот им- пульс проходит через соответствующий элемент ИЛИ 19i и поступает на третий -вход элемента И 16i.-Импульс запроса поступает на первые входы элементов И 16 первого канала. Таким образом на выходе элемента И 16i появляется импульс, так как на втором входе этого элемента присутствует разрешающий потенциал с нуле- вого выхода соответствующего триггера 14i первого канала. Этот импульс, пройдя через элемент И 16i, проходит также через соот

Ј

О

о ел со

ветствующий элемент ИЛИ 12i и поступает на единичный вход соответствующего триггера 14|, в результате чего последний переходит из нулевого состояния в единичное. На изменение потенциала с нулевого на единичном выходе триггера 14| реагирует соответствующий формирователь 15, который преобразует это изменение в импульс. Этот импульс проходит через первый элемент ИЛИ 10, поступает на первые входы элементов И первого блока элементов И 3, подключая информационные входы 5 устройства к первой ЭВМ, в результате информация первого запроса поступает на первую ЭВМ. Так как первый триггер 14 1-го приоритета находится в единичном состоянии, то потенциал с его единичного выхода поступает на второй вход первого элемента И 11 i-ro приоритета, разрешая прохождение импульса запроса в следующий канал блока 2 этого же приоритета.

При поступлении второго импульса запроса этого же 1-го приоритета аналогично происходит срабатывает триггер 14 в следующем канале, в результате чего инфор- мация второго запроса 1-го приоритета поступает на вторую ЭВМ. Если в устройство находится m запросов 1-го приоритета (т - число обслуживаемых ЭВМ) и в этот момент поступает (т + 1)-й зап рос i-ro приоритета, то этот импульс проходит через открытый элемент И 18i так как на остальных m входах элемента И 18i присутствуют разрешающие потенциалы с выходов триггеров 14 1-го приоритета. С выхода элемента И 18| этот импульс поступает через элемент ИЛИ 19i-i на третий вход элемента И 16ы. В этом случае (т + 1)-й запрос 1-го приоритета преобразуется в запрос (1-1)-го приоритета,

Таким образом, очередной поступающий на вход устройства запрос i-ro приоритета направляется на ближайшую ЭВМ, у которой позиция, соответствующая t-му приоритету в канале, свободна, а при отсутствии свободных позиций 1-го приоритета во всех каналах - на ближайшую ЭВМ, у которой свободна позиция (1-1)-го приоритета и т.д., что обеспечивает равномерную загрузку всех ЭВМ с учетом приоритетов заданий.

По окончании решения задачи на соответствующий вход 1 подается импульс. Этот импульс подается на все первые входы элементов И 17 канала, на которых был обслужен запрос. В результате импульс обслуженной заявки проходит,только через тот элемент И 17, на остальных входах которого присутствуют разрешающие потенциалы с нулевых выходов триггеров 14 более

высоких приоритетов, Через элемент ИЛИ

13 триггер 14 устанавливается в нулевое

состояние. Таким образом, очередной поступающий импульс окончания решения обнуляет только тот триггер 14, который соответствует самому высокому приоритету в канале 9..

При возникновении неисправности в

ЭВМ или ее выводе на профилактику на соответствующий вход б подается импульс, который устанавливает триггеры 14 соответствующего канала в единичное состояние, в результате чего на данную ЭВМ

запросы не направляются.

Формула изобретения Устройство для распределения заданий между ЭВМ, содержащее группу из m блоков элементов И (т - число обслуживаемых ЭВМ) и блок выделения запросов, содержащий в каждом канале, кроме последнего, три группы элементов И, две группы элементов ИЛИ. группу триггеров,

группу формирователей импульсов и элемент ИЛИ, последний канал содержит две группы элементов И, две группы элементов ИЛИ, группу триггеров и группу формирователей импульсов, причем группа

информационных входов устройства соединена с группами информационных входов блоков элементов И группы, группы выходов которых являются соответствующими группами выходов устройства, вход

запроса устройства соединен в блоке выделения запросов с первыми входами первых элементов И первой и второй г рупп первого канала, выход первого элемента И второй группы каждого канала, кроме

последнего, соединен с первым входом первого элемента И первой группы и с первым входом первого элемента И второй группы следующего канала, выход каждого элемента И первой группы в канале соединен с первым входом од: ноименного элемента ИЛИ первой группы своего канала, первые входы элементов И третьей группы каждого канала соединены с одноименным ответным входом устрой0 ства, второй вход i-ro (1 1k, k - кодовые

входы) элемента И третьей группы в каждом канале соединен с инверсным выходом (I + 1)-го триггера группы данного канала, первые входы элементов ИЛИ вто5 рой группы каждого канала, кроме последних элементов, соединены с выходами одноименных элементов И третьей группы данного канала, первый вход последнего элемента ИЛИ второй группы каждого канала соединен с одноименным ответным

входом устройства, вторые входы элементов ИЛИ первой и второй групп в каждом канале соединены соответственно с одноименными сигнальным входом и входом сброса устройства, второй вход первого элемента И первой группы в каждом канале соединен с инверсным выходом первого триггера группы своего канала,.первый вход каждого элемента И первой группы, начиная с второго, в каждом канале соединен с инверсным выходом одноименного триггера группы своего канала, второй вход каждого элемента И, начиная с второго, первой группы в каждом канале, начиная с второго, соединен с прямым выходом одноименного триггера группы предыдущего канала, третий вход первого элемента И первой группы в каждом канале, начиная с второго, соединен с прямым выходом первого триггера группы предыдущего канала, третий вход каждого элемента И первой группы,-начиная с второго, каждого канала, начиная с второго, соединен в выходом одноименного элемента И второй группы предыдущего канала, второй вход первого элемента И второй группы каждого канала соединен с прямым выходом первого триггера группы своего канала, первый вход каждого элемента И, начиная с второго, второй группы каждого канала, начиная с второго, соединен с выходом одноименного элемента И второй группы предыдущего канала, второй вход каждого элемента И второй группы каждого канала, начиная с второго, кроме последнего, соединен с прямым выходом одноименного триггера своего канала, прямой выход триггера каждого канала соединен с входом одноименного формирователя импульсов группы своего канала,

выходы формирователей импульсов группы каждого канала соединены с входами элемента ИЛИ своего канала, от личаю- щ е е с я тем, что, с целью расширения области применения за счет учета приоритета заданий при их распределении, orfo дополнительно содержит дешифратор, а в первом канале четвертую группу элементов И и третью группу элементов ИЛИ, причем приоритетные входы устройства

соединены соответственно с входами дешифратора, выходы которого соединены с первыми входами соответствующих элементов ИЛИ третьей группы первого канала, выходы элементов ИЛИ третьей группы

соединены с третьими входами элементов И первой группы первого канала, вход запроса устройства соединен с первыми входами элементов И первой и второй групп первого канала и с первыми входами соответствующих элементов И четвертой группы, остальные m входов которых соединены с прямыми выходами соответствующих триггеров в каждом канале, в прямом канале выходы элементов И четвертой груп0 пы соединены с вторыми входами предыдущих элементов ИЛИ третьей группы, в каждом канале третьи входы последующих элементов И третьей группы соединены с соответствующими входами предыдущих

5 элементов И третьей группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания резервированной вычислительной системы | 1991 |

|

SU1824636A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Многоканальное устройство динамического приоритета | 1990 |

|

SU1762306A1 |

| Устройство для обслуживания запросов | 1989 |

|

SU1741132A1 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| МНОГОВЫХОДНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2613536C1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Устройство для распределения заданий между ЭВМ | 1987 |

|

SU1474648A1 |

| Многоканальное устройство приоритета | 1990 |

|

SU1809441A1 |

| Многоканальное устройство приоритета | 1989 |

|

SU1686444A1 |

Изобретение относится к вычислительной технике и может быть применено при построении вычислительных комплексов. Цель изобретения - расширение области применения устройства за счет учета приоритета заданий при их распределении. Устройство содержит блок выделения запросов, блоки элементов И, дешифратор. Блок выделения запросов дополнительно содержит в первом канале четвертую группу элементов И i третью группу элементов ИЛИ. 2 ил.

«foz/

в М

Фиг.2

Составитель Г. Пономарева редактор Л. Пчолинская Техред М.МоргенталКорректор Т. Палий

33KR3 «мпм Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

4т

22к

| Устройство для распределения заданий между ЭВМ | 1983 |

|

SU1111163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий между ЭВМ | 1987 |

|

SU1474648A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-11-09—Подача