J

|

о

Јь

О

сд

Изобретение относится к электроизмерительной технике и может быть использовано при построении анализат торов импульсных сигналов.

Цель изобретения - повышение точности измерения длительности при измерении длительности симметричного импульсного сигнала.

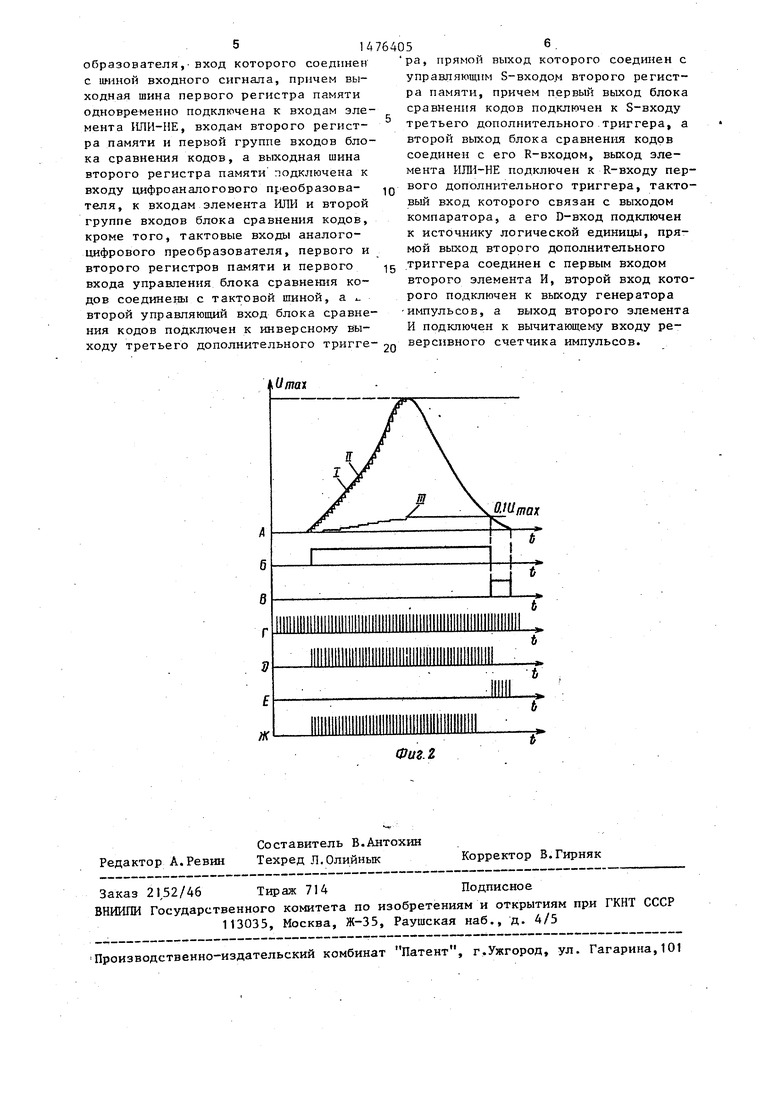

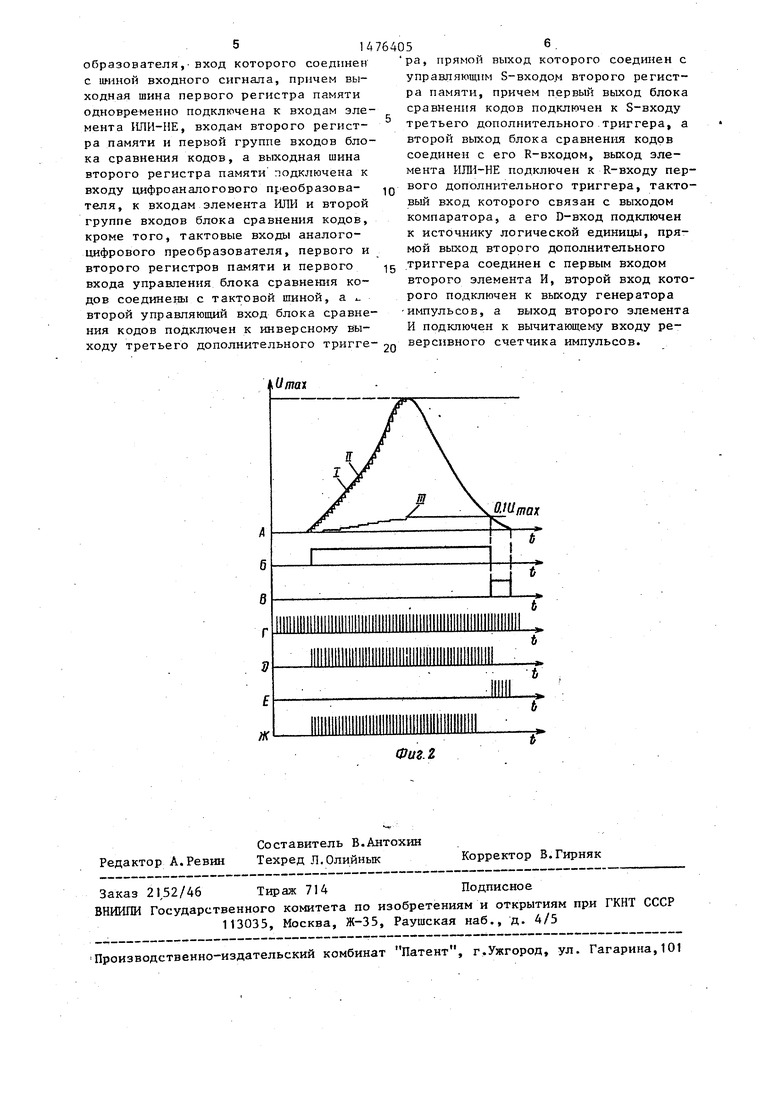

На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - диаграммы, поясняющие его работу.

Устройство содержит тактовую шину (ТИ) 1, входную шину (U6x) 2, аналого-цифровой преобразователь (АЦП) 3, первый регистр 4 памяти (РП1), элемент ИЛИ-НЕ 5, шину 6 логической единицы, первый дополнительный триггер

10

15

второго дополнительного триггера (ТЗ) 18, а второй выход блока 17 сравнения кодов соединен с его R-входом, кроме того, выход цифреаналогевого преобразователя (ЦАП) 9 подключен к входу усилителя (У) 10, выход которого соединен с первым входом компаратора (К) 11, а второй вход компаратора (К) 1I подключен к входной шине 2, выход компаратора (К) 11 соединен с тактовым входом первого дополнительного триггера (Т1) 7 и R- входом триггера (Т2) 13, D-входы которых подключены к источнику логической единицы, причем прямой выход первого дополнительного триггера (TI) 7 подключен к второму входу второго элемента И 15, выход которого соединен с вычитающим

(Т1) 7, второй регистр 8 памяти (РП2) ,20 входом реверсивного счетчика (PC) 16,

а прямой выход триггера (Т2) 13 подключен к второму входу первого элемента И 14, выход которого подключен к суммирующему входу реверсивного

цифрозналоговый преобразователь (ЦАП) 9, усилитель (У) 10, компаратор (К) 11, элемент ИЛИ 12, триггер (Т2) 13, первый элемент И 14, второй элемент И 15, реверсивный счетчик (РГ) 25 счетчика 16, выход элемента ИЛИ-НЕ 5 16 импульсов, блок 17 сравнения ко- ; соединен с R-входом первого дополнительного триггера 7, а выход элемента ИЛИ 12 подключен к тактовому входу триггера 13, выход реверсивного 30

35

40

дов, второй дополнительный триггер (ТЗ) 18, генератор 19 импульсов, выход которого подключен к объединенным между собой первыми входами элементов И 14 и И 15-, входная шина первого регистра 4 памяти (РП1) подключена к выходным шинам аналого-цифрового преобразователя (АЦП) 3, вход которогр соединен с шиной 2 входного сигнала, причем выходная шина первого регистра 4 памяти (РП1) одновременно подключена к входам элемента ИЛК-НЕ 5, информационным входам второго регистра 8 памяти (РП2) и первой группе входов блока 17 сравнения кодов, а выходная шина второго регистра 8 памяти подключена к входу цифроаналогового преобразователя

(ЦАП) 9, к входам элемента ИЛИ 12 и .

45

к второй группе входов блока 17 сравнения кодов, причем тактовые входы аналого-цифрового преобразователя (АЦП) 3, первого 4 и второго 8 регистров памяти и входа управления блока 17 сравнения кодов соединены с тактовой шиной 1, а управляющий вход блока 17 сравнения кодов подключен к инверсному выходу второго дополнительного триггера (ТЗ) 18, прямой выход которого соединен с уп равняющим S-входом второго регистра 8 памяти, первый выход блока 17 сравнения кодов подключен к S-входу

50

I 55

счетчика 16 является выходом устройства.

Устройство работает следующим образом.

В исходном состоянии триггеры 7 и 13, регистры 4 и 8 памяти и реверсивный счетчик 16 находятся в нулевом состоянии (установка в исходное состояние перечисленных элементов устройства в схеме не показана).

Импульсное воздействие, подлежащее измерению (линия I на фиг.2), по ступает на входную шину 2 устройства В аналого-цифровом преобразователе 3 происходит преобразование входного напряжения в код, в результате чего по переднему фронту тактового импуль са код записывается в первый регистр 4 памяти, который находится в режиме непрерывной записи. Записанная кодовая комбинация поступает на блок 17 сравнения кодов, где за время тактового импульса, поступающего на управ ляющий вход блока 17 сравнения кодов, происходит сравнение кодов, записанных в первом 4 и втором 8 регистрах памяти. Запись кода в регистр 8 памяти возможна только по заднему фронту тактового импульса и при наличии уровня логического ну

5

второго дополнительного триггера (ТЗ) 18, а второй выход блока 17 сравнения кодов соединен с его R-входом, кроме того, выход цифреаналогевого преобразователя (ЦАП) 9 подключен к входу усилителя (У) 10, выход которого соединен с первым входом компаратора (К) 11, а второй вход компаратора (К) 1I подключен к входной шине 2, выход компаратора (К) 11 соединен с тактовым входом первого дополнительного триггера (Т1) 7 и R- входом триггера (Т2) 13, D-входы которых подключены к источнику логической единицы, причем прямой выход первого дополнительного триггера (TI) 7 подключен к второму входу второго элемента И 15, выход которого соединен с вычитающим

а прямой выход триггера (Т2) 13 подключен к второму входу первого элемента И 14, выход которого подключен к суммирующему входу реверсивного

счетчика 16, выход элемента ИЛИ-НЕ 5 соединен с R-входом первого дополнительного триггера 7, а выход элемента ИЛИ 12 подключен к тактовому входу триггера 13, выход реверсивного

25 счетчика 16, выход элемента ИЛИ-НЕ 5 соединен с R-входом первого дополнительного триггера 7, а выход элемента ИЛИ 12 подключен к тактовому входу триггера 13, выход реверсивного 30

35

40

.

45

50

55

счетчика 16 является выходом устройства.

Устройство работает следующим образом.

В исходном состоянии триггеры 7 и 13, регистры 4 и 8 памяти и реверсивный счетчик 16 находятся в нулевом состоянии (установка в исходное состояние перечисленных элементов устройства в схеме не показана).

Импульсное воздействие, подлежащее измерению (линия I на фиг.2), поступает на входную шину 2 устройства. В аналого-цифровом преобразователе 3 происходит преобразование входного напряжения в код, в результате чего по переднему фронту тактового импульса код записывается в первый регистр 4 памяти, который находится в режиме непрерывной записи. Записанная кодовая комбинация поступает на блок 17 сравнения кодов, где за время тактового импульса, поступающего на управляющий вход блока 17 сравнения кодов, происходит сравнение кодов, записанных в первом 4 и втором 8 регистрах памяти. Запись кода в регистр 8 памяти возможна только по заднему фронту тактового импульса и при наличии уровня логического нуля на его управляющем S-входе. На втором выходе блока 17 сравнения кодов в течение длительности тактового импульса появляется уровень логической 1, в результате чего триггер 18 устанавливается в нулевое состояние. По заднему фронту тактового импульса код, записанный в регистре

(фнг.2в), разрешая прохождение тактовых импульсов от генератора 19 через элемент И I5 на вычитающий вход реверсивного счетчика 16 импульсов (фиг.2б). Вычитание импульсов в реверсивном счетчике 16 импульсов будет происходить до тех пор, пока UB, (t) не станет меньше минимального

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель пикового значения импульсных воздействий | 1984 |

|

SU1167734A1 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ МАКСИМАЛЬНОГО ЗНАЧЕНИЯ ИМПУЛЬСНОГО АНАЛОГОВОГО СИГНАЛА | 1993 |

|

RU2063048C1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2024194C1 |

| Устройство для измерения длительности импульсных сигналов | 1985 |

|

SU1272257A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2028730C1 |

Изобретение относится к электроизмерительной технике и может быть использовано в анализаторах импульсных сигналов при измерении длительности импульсных сигналов симметричной формы. Целью изобретения является повышение точности измерения длительности импульсного сигнала симметричной формы. Цель изобретения достигается за счет введения поправки в конечный результат измерения, учитывающей уровень 0,1 Uмакс по переднему фронту импульсного сигнала. Для реализации указанной функции в него введены аналого-цифровой преобразователь 3, блок 17 сравнения кодов, второй и третий дополнительные триггеры 7,18, два регистра 4,8 памяти, элемент ИЛИ 12, элемент И 15. Кроме того, устройство также содержит тактовую шину 1, входную шину 2, элемент ИЛИ-НЕ 5, шину 6 логической единицы, цифроаналоговый преобразователь 9, усилитель 10, компаратор 11, триггер 13, элемент И 14, реверсивный счетчик 16 импульсов, генератор 19 импульсов. 2 ил.

памяти переписывается в регистр 8 па-JQ шага дискретизации по уровню аналогомяти.

На выходе элемента ИЛИ 12появляется уровень логической 1,который устанавливает триггер 13 вединнчное состояние (фиг.26), разрешая про- вает триггер 7 в нулевое состояние

(фиг.2в), запрещая прохождение такт вых импульсов от генератора 19 импульсов на вычитающий вход реверсив ного счетчика 16 импульсов (фиг.2ж) в , результате чего на выходе реве сивного счетчика 16 импульсов форми руется двоичный код, эквивалентный длительности измеряемого симметричн го импульсного воздействия на уров- не 0,1имо«.

хождение тактовых импульсов через элемент И 1 ч от генератора 19 импульсов (фиг.2г) на суммирующий вход реверсивного счетчика 16 (фиг.2д). Уровень логической единицы на инверсном выходе триггера 18 поступает на первый управляющий вход блока 17 сравнения кодов и непрерывно производит сравнение двух кодов на выполнение условия, когда значение кода в регистре 4 памяти станет меньше, чем в регистре 8 памяти. Данное условие вы

полняется в том случае, станет меньше

если UBҐ(t)

UMnl//.(t). Как только

мокс

UBx(t) станет меньше U c(t), значемако

памяти станет 8 памяти, в

.ние кода в регистре 4 меньше, чем в регистре результате чего триггер 18 установится в единичное состояние, запрещая перезапись кода из регистра 4 памяти в регистр 8 памяти и на выходе регистра 8 памяти установится код

соответствующий значению U

мам

Сигнал, соответствующий , с выхода цифроаналогового преобразователя 9 (линия II на фиг.2) поступает на вход усилителя 10, коэффициент усиления которого равен 0,1. На выходе усилителя 10 формируется сигнал уровня,

40

Устройство измерения длительности импульсных сигналов, содержащее последовательно соединенные цифроана- логовый преобразователь, усилитель, компаратор, триггер, первый элемент И, реверсивный счетчик импульсов, а также второй элемент И, элемент ИЛИ- НЕ и генератор импульсов, выход которого подключен к первому входу первого элемента И, а второй вход компаравный 0,1 U М01КС (линия III на фиг.2), . ратора соединен с шиной входного сигкоторый поступает на первый вход компаратора 11, на второй вход которого поступает входной сигнал Uei((t). Если Ugx(t) -У 0.1U вых ЦД|1 , то компаратор 11 не изменяет своего состояния. Как только U8l((t) станет меньше О., компаратор 11 срабатывает, устанавливая триггер 13 в нулевое состояние (фиг.26) и запрещая прохождение тактовых импульсов от генератора 19 через элемент И 14 на суммирующий вход реверсивного счетчика 16 импульсов, в результате чего триггер 7 устанавливается в единичное состояние

50

55

нала, отличающееся тем, что, с целью повышения точности измерения длительности при измерении длительности симметричного импульсного сигнала, в него введены аналого-цифровой преобразователь, блок сравнения кодов,второй и третий дополнительные триггеры, два регистра памяти, .элемент ИЛИ, выход которого соединен с тактовым входом второго триггера, а D-вход этого триггера - с источни- , ком логической единицы, входная шина первого регистра памяти подключена к выходным шинам аналого-цифрового пре

цифрового преобразователя 3. При выполнении этого условия на выходе элемента ИЛИ-НЕ 5 появляется уровень логической единицы, который устанавливает триггер 7 в нулевое состояние

(фиг.2в), запрещая прохождение тактовых импульсов от генератора 19 импульсов на вычитающий вход реверсивного счетчика 16 импульсов (фиг.2ж), в , результате чего на выходе реверсивного счетчика 16 импульсов формируется двоичный код, эквивалентный длительности измеряемого симметричного импульсного воздействия на уров- не 0,1имо«.

Таким образом, измерение длительности симметричного импульсного воздействия происходит на уровне 0,lUMaW, что позволяет повысить точность измерения длительности импульс- ноко воздействия.

Формула изобретения

Устройство измерения длительности импульсных сигналов, содержащее последовательно соединенные цифроана- логовый преобразователь, усилитель, компаратор, триггер, первый элемент И, реверсивный счетчик импульсов, а также второй элемент И, элемент ИЛИ- НЕ и генератор импульсов, выход которого подключен к первому входу первого элемента И, а второй вход компа0

5

нала, отличающееся тем, что, с целью повышения точности измерения длительности при измерении длительности симметричного импульсного сигнала, в него введены аналого-цифровой преобразователь, блок сравнения кодов,второй и третий дополнительные триггеры, два регистра памяти, .элемент ИЛИ, выход которого соединен с тактовым входом второго триггера, а D-вход этого триггера - с источни- , ком логической единицы, входная шина первого регистра памяти подключена к выходным шинам аналого-цифрового пре

514

образователя, вход которого соединен с ш-иной входного сигнала, причем выходная шина первого регистра памяти одновременно подключена к входам элемента ИЛИ-НЕ, входам второго регистра памяти и первой группе входов блока сравнения кодов, а выходная шина второго регистра памяти подключена к входу цифроаналогового преобразователя, к входам элемента ИЛИ и второй группе входов блока сравнения кодов, кроме того, тактовые входы аналого- цифрового преобразователя, первого и второго регистров памяти и первого входа управления блока сравнения кодов соединены с тактовой шиной, а . второй управляющий вход блока сравнения кодов подключен к инверсному выходу третьего дополнительного тригге64056

ра, прямой выход которого соединен с

управляющим S-входом второго регистра памяти, причем первый выход блока сравнения кодов подключен к S-входу

5 третьего дополнительного триггера, а второй выход блока сравнения кодов соединен с его R-входом, выход элемента ИЛИ-НЕ подключен к R-входу пер вого дополнительного триггера, тактовый вход которого связан с выходом компаратора, а его D-вход подключен к источнику логической единицы, прямой выход второго дополнительного

15 триггера соединен с первым входом второго элемента И, второй вход которого подключен к выходу генератора импульсов, а выход второго элемента И подключен к вычитающему входу ре версивного счетчика импульсов.

| Устройство для регистрации и определения параметров импульсных сигналов | 1983 |

|

SU1092415A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения длительности импульсных сигналов | 1985 |

|

SU1272257A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-04-30—Публикация

1986-04-16—Подача