1

Изобретение относится к вычислительной технике, в частности к устройствам цифровой фильтрациио

Цель изобретения - сокращение аппаратных затрат за счет одноканальной схейы обработки входного сигнала.

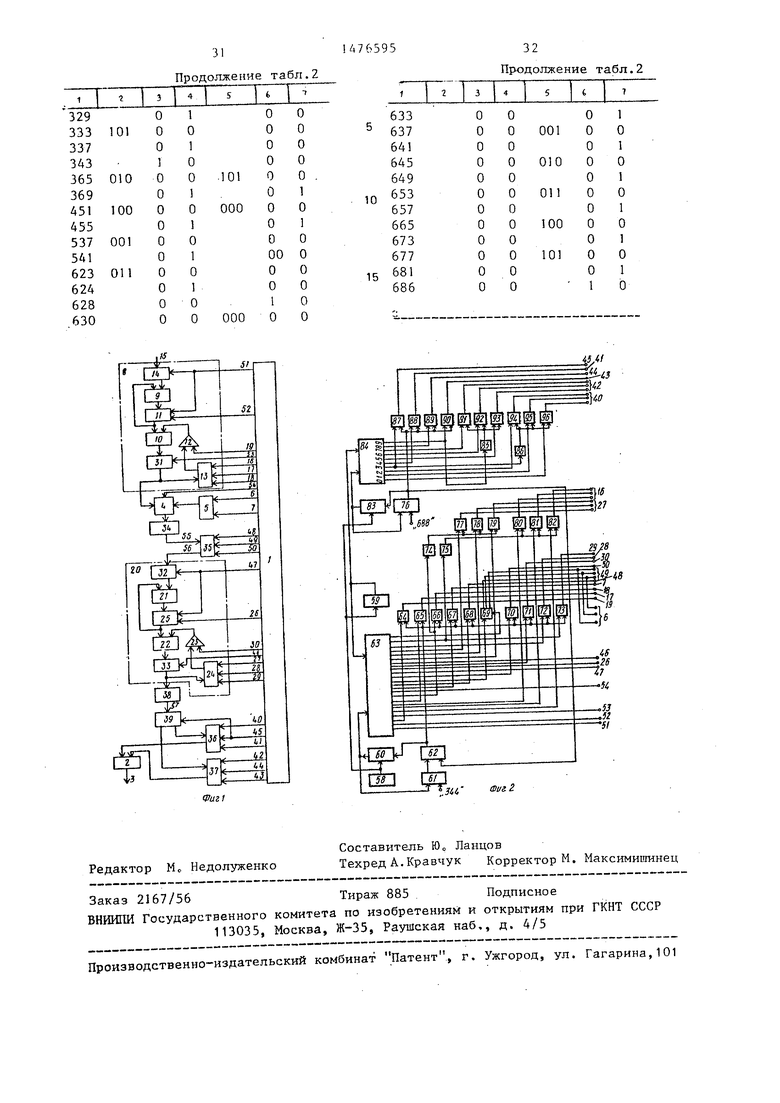

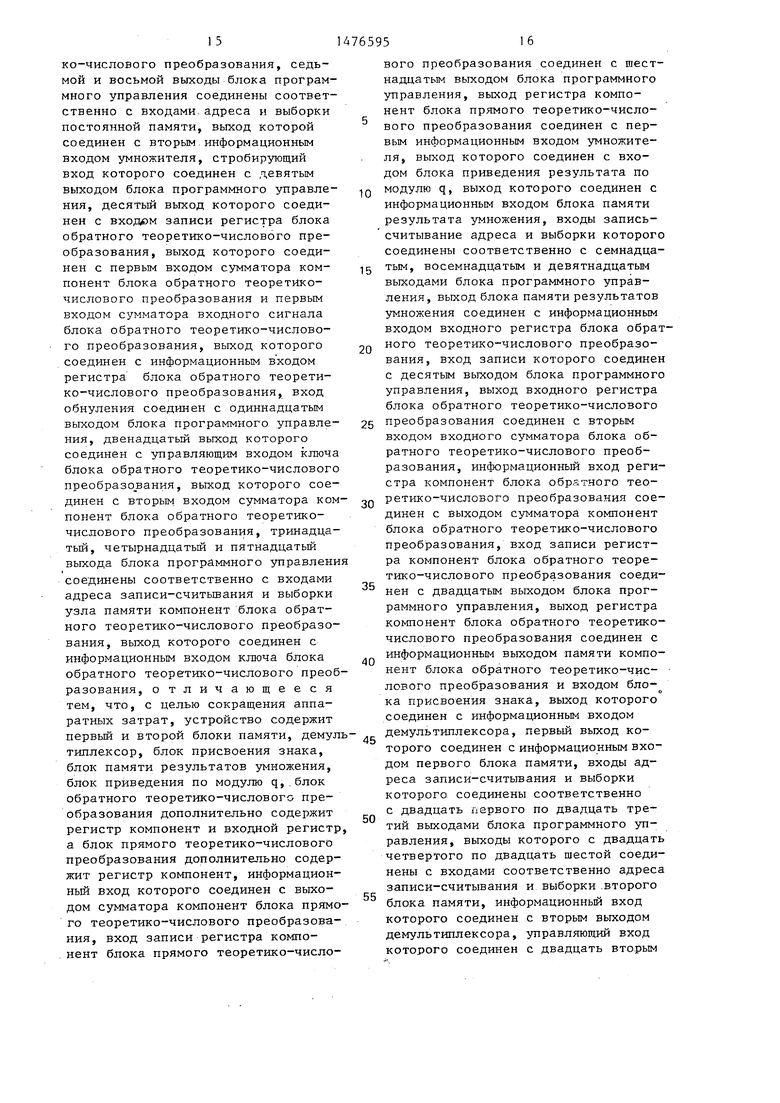

На фиг. 1 представлена схема устройства; на фиг. 2 - схема блока управления.

Устройство содержит блок 1 программного управления, выходной сумматор 2, информационный выход 3, умножитель 4, блок 5 постоянной памяти, седьмой и восьмой выходы 6 и 7 блока программного управления, блок 8

прямого теоретико-числового преобра-1 зования (ТЧП), выходной сумматор 9 блока 8, сумматор 10 компонент блока 8, регистр 13 блока 8, ключ 12 блока 8, узел 13 памяти блока 8, выходной регистр 14 блока 8, информационный вход 15, четвертый, пятый и шестой выходы 16-18 блока программного управления, третий выход 19 блока программного управления, блок 20 обратного ТЧП Фурье, содержащий входной.сумматор 21, регистр компонент 22, ключ 23, узел 24 памяти, регистр 25, одиннадцатый выход 26 блока программного управления, тринадцатый, четырнадцатый и пятнадца sj

о ел со ел

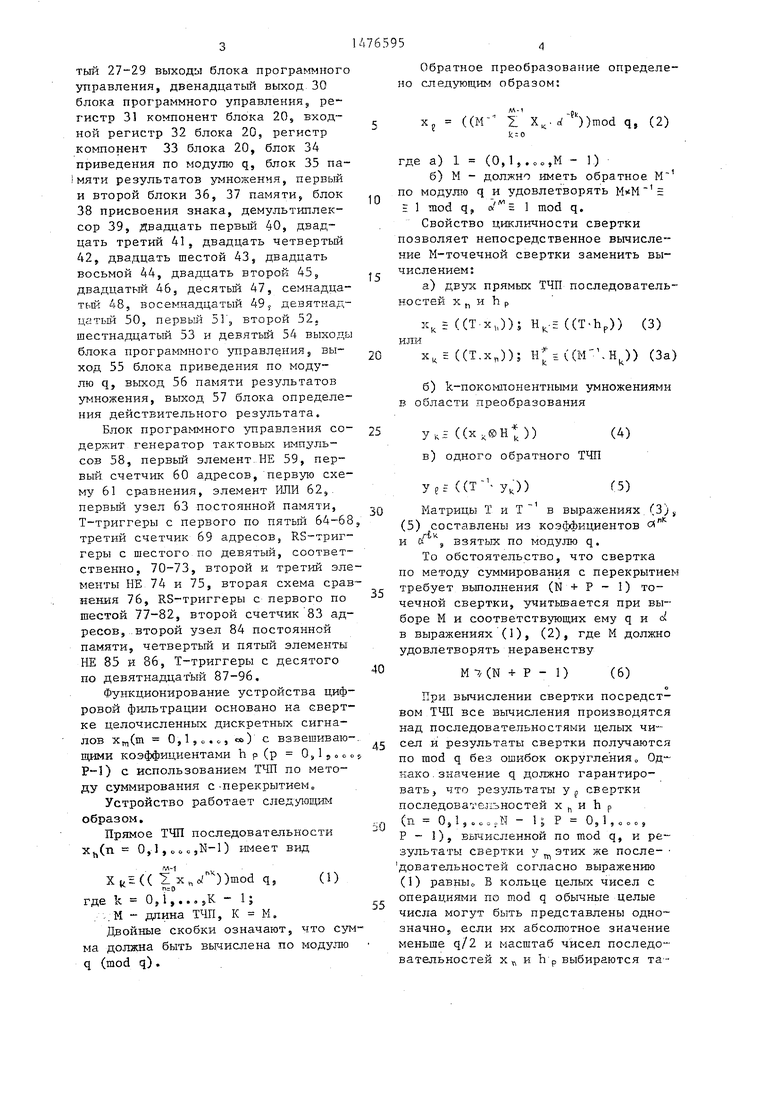

тый 27-29 выходы блока программного управления, двенадцатый выход 30 блока программного управления, ре- гистр 31 компонент блока 20, входной регистр 32 блока 20, регистр компонент 33 блока 20, блок 34 приведения по модулю q, блок 35 па- мяти результатов умножения, первый и второй блоки 36, 37 памяти, блок 38 присвоения знака, демультиплек- сор 39, двадцать первый 40, двадцать третий 41, двадцать четвертый 42, двадцать шестой 43, двадцать восьмой 44, двадцать второй 45, двадцатый 46, десятый 47, семнадцатый 48, восемнадцатый 49t девятнадцатый 50, первый 53 э второй 52. шестнадцатый 53 и девятый 54 выходи блока программного управления, выход 55 блока приведения по модулю q, выход 56 памяти результатов умножения, выход 57 блока определения действительного результата.

Блок программного управления содержит генератор тактовых импульсов 58, первый элемент НЕ 59, первый счетчик 60 адресов, первую схему 61 сравнения, элемент ИЛИ 62, первый узел 63 постоянной памяти, Т-триггеры с первого по пятый 64-68 третий счетчик 69 адресов, RS-триг- геры с шестого по девятый, соответственно, 70-73, второй и третий элементы НЕ 74 и 75, вторая схема сравнения 76, RS-триггеры с первого по шестой 77-82, второй счетчик 83 адресов, второй узел 84 постоянной памяти, четвертый и пятый элементы Ж 85 и 86, Т-триггеры с десятого по девятнадцатый 87-96.

Функционирование устройства цифровой фильтрации основано на свертке целочисленных дискретных сигналов xm(m 0,1,о.с, «,) с взвешивающими коэффициентами hp(p 0,1,.о о Р-1) с использованием ТЧП по методу суммирования с перекрытием.

Устройство работает следующим образом.

Прямое ТЧП последовательности xh(n 0,l,oo«,N-l) имеет вид

ЛЛ-1

XkH(( xhcT4))mod q, (1)

п-Q

где k О,1,...,К - 1;

М - длина ТЧП, К М. Двойные скобки означают, что сумма должна быть вычислена по модулю q (mod q).

Обратное преобразование определено следующим образом:

х ((М- Z XK d )-)mod q, (2)

с о

где а) 1 (0,1,.оо,М - 1)

б) М - должно иметь обратное по модулю q и удовлетворять

/VI 11

1 mod q, at 1 mod q.

Свойство цикличности свертки позволяет непосредственное вычисление М-точечной свертки заменить вычислением:

а)двух прямых ТЧП последовательностей х п и h p

хк ((Т x,,))j HKE ((T-hp)) (3)

илт х, (CT.xJ); H(()) (За)

б)k-покомпонентными умножениями в области преобразования

YwH (())(4)

в)одного обратного ТЧП

У е-- ((Т 1- у,)) Г5)

Матрицы Т и Т 1 в выражениях (3; (5) составлены из коэффициентов и ff Ks взятых по модулю q.

То обстоятельство, что свертка по методу суммирования с перекрытием

требует выполнения (N + Р - 1) точечной свертки, учитывается при выборе М и соответствующих ему q и d в выражениях (1), (2), где М должно удовлетворять неравенству

М (N + Р - 1)

(6)

При вычислении свертки посредством ТЧП все вычисления производятся над последовательностями целых чи5 сел и результаты свертки получаются по mod q без ошибок округления Однако значение q должно гарантировать, что результаты yf свертки последовательностей х h и h P

0 (п 0,1,..-. - 1, Р 0,1,000

Р - 1), вычисленной по mod q, и результаты свертки у этих же после- довательностей согласно выражению (1) равньи В кольце целых чисел с операциями по mod q обычные целые числа могут быть представлены однозначно, если их абсолютное значение меньше q/2 и масштаб чисел последовательностей хft и h pвыбираются таким образом, чтобы /У,,,/ никогда н превышало q/2.

Работа блоков устройства цифровой фильтрации по реализации функции свертки осуществляется следующим образом.

Входные отсчеты х m(m 0,,„,„, со ), условно разделенные на секции xn,i по отсчетов, последовательно поступают в блок 8 прямого ТЧП, где из каждой секции входных отсчетов х „ (n 0,1,.0.,N - 1) по мере их поступления формируется вектор х к согласно выражению (1). С поступле- нием каждого нового отсчета входной последовательности xh в блоке 8 прямого ТЧП каждый раз проводится вычисление всех слагаемых (( xn))mod q соответствующих данному отсчету из выражения (3), и прибавление этих слагаемых к вычисленным ранее промежуточным значениям компонентов вектора хк. Вычисление слагаемых (())mod q от отсчета х„, фикси- руемого во входном регистре 14, производится циклическим суммированием значения х п и результата регистра 11 на сумматоре входного сигнала 9. Прибавление слагаемых ((/ xt))mod q к вычисленным ранее промежуточным значениям компонентов вектора хк и записанных в блок 13 памяти промежуточных значений осуществляется на сумматоре компонентов 10 с последую- щей записью сначала в регистр 31 компонентов, а затем в блок 13 памяти промежуточных значений. После получения n N-ro отсчета i-й секции xh каждый окончательно вычис- ленный компонент вектора х К|1 с соответствующим ему компонентом вектора Н (За), считываемым из постоянной памяти коэффициентов фильтра 5, где хранятся результаты прямого преобразования последовательностей взвешивающих коэффициентов hp, умножаются на умножителе 4 согласно выражению (4) и результат умножения у k ; , приведенный по модулю q в бло- ке 34 приведения числа по модулю q 34 записывается в блок 35 памяти результатов умножения.

Когда блок прямого преобразования 8 начинает обработку (i + 1)-й секции входных отсчетов х ft (,t1) , из результатов умножения у к , , покомпонентно считываемых из блока 35 памяти результатов умножения в блоке 20 обратного ТЧП, начинается формирование вектора обратного преобразования у р ; согласно уравнению (2)0 С поступлением каждого нового компонента вектора yk в блоке 20 обратного ТЧП каждый раз производится вычисление всех слагаемых ((d (K. YR) )mod q, соответствующих данному компоненту у k из выражения (5), и прибавление этих слагаемых к вычисленным ранее промежуточным значениям компонентов вектора yf . Вычисление слагаемых ((k.YK))mod q от компонента yk, фиксируемого во входном регистре 32, производится циклическим суммированием значения ук и результата регистра 25 на сумматоре 21. Прибавление слагаемых ((с/ YK))mod q к вычисленным ранее промежуточным значениям компонентов вектора yf, записанных в узле 24 памяти промежуточных значений осуществляется на сумматоре компо-1 нентов 22 с последующей записью сначала в регистр 33 компонентов, а затем в узел 24 памяти промежуточных значений. После получения

компонента вектора у

и его обработки в блоке обратного ТЧП 20 каждый окончательно вычисленный компонент вектора у f|t с выхода регистра компонентов 33 через блок присвоения знака свертки 38, приводящий результаты свертки по mod q последовательностей х „ . и h p к результатам обычной свертки и коммутатор 39, записывается в первый блок 36 памяти После записи в блок 36 памяти последнего компонента вектора у g , являющегося результатом свертки последовательностей х П| и h р, в блоке 20 обратного ТЧП начинается формирование вектора у р (.tf} из компонентов вектора у k , ..

Результаты уг м обратного преобразования вектора у k , через блок 36 присвоения знака свертки и коммутатор 39 записываются во второй блок 37 памяти

Выходной сумматор 2 предназначен для суммирования перекрывающихся компонентов векторов у c ; и у р (f+1j , считываемых из блоков 36 и 37 памя- тж.

Управление работой всех блоков устройства цифровой фильтрации осуществляет блок 1 управления о

7

Более детально работа устройства цифровой фильтрации рассматривается на конкретном примере выполнения свертки последовательностей х (т 0,1,00,) и h р (,1 .. . , Р-1) с использованием ТЧП по mod 7 с о( - 3, М 6. Длина свертки (N + Р - 1) выбирается ррвной длине ТЧП при N 4 и Р 30

Далее примем, что (k 1,2,..., К; п 1/2,3,4; 1 ,2,..0.,м).

Тогда выражение (1) принимает следующий вид:

х (( Z x, rK))mod 7 (7)

h: i

и определяется по следующим уравнениям

x;((3x,4.32x 33x3+31x4))mod 7; X2 ((3 xl+34x1+3ex3+38x4))mod 7; X3 ((33x1+36x +39x3+3 lx4))mod 7; X4((34x1+38xl+3 x3+3ux4))mod 7;

,

Ш6595a

x5 ((3Jx1+3 °xt+3 x 32x))mod 7; x6((3 x,+3nxz+3 x3+3Mx4))mod 7.

(8)

Если коэффициенты при хп в системе уравнений (8) определить по mod 7, то выражение (1) можно записать в следующем виде

XT((Зх,+2xz+6x3+4x4))mod 7; x, ((2xt+4x7+x 3+2x4))mod 7; X3((6x,+x1+6x3+x4))mod 7; . . хф ((4х1+2х,г+хэ+4х4 ))mod 7; x5((5x,+4x +6x3+2x4))mod 7; х6((х,+х7+х3+x4))mod 7.

Для того, чтобы исключить опера- цию умножения на коэффициент в выражении (2) при обратном преобразовании, результаты прямого преобразования последовательности hp, которые необходимо записать в постоянную память коэффициентов фильтра 9, вычисляются по следующим уравнениям

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Устройство для вычисления свертки | 1985 |

|

SU1297073A1 |

| Устройство для спектрального анализа сигналов | 1987 |

|

SU1513474A1 |

| Устройство для вычисления цифровой свертки | 1986 |

|

SU1354205A2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ СЛОЖНЫХ СИГНАЛОВ | 1987 |

|

SU1840228A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| СПОСОБ ФОРМИРОВАНИЯ ТЕКУЩЕГО ЭНЕРГЕТИЧЕСКОГО СПЕКТРА ВЫХОДНОГО СИГНАЛА ПРИЕМНИКА, УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ И СПОСОБ ИЗМЕРЕНИЯ ДАЛЬНОСТИ | 2007 |

|

RU2371736C2 |

| Цифровой полосовой фильтр | 1976 |

|

SU813703A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

Изобретение относится к вычислительной технике ,в частности к устройствам цифровой фильтрации, основанным на методах свертки. Целью заявляемого технического решения является сокращение аппаратных затрат за счет одноканальной схемы обработки. Устройство содержит блок программного управления, выходной сумматор, первый и второй блоки памяти результатов преобразования, блок присвоения знака, блок памяти результатов умножения, блок приведения по модулю, умножитель, блок постоянной памяти, блоки прямого и обратного теоретико-числового преобразования, каждый из которых содержит входной регистр, входной сумматор, регистр, сумматор компонент, ключ, узел памяти, регистр компонент. Функционирование устройства основано на теоретико-числовом преобразовании фрагментов входной последовательности, последующей свертке преобразованного фрагмента со взвешивающими коэффициентами и, после обратного преобразования, суммировании перекрывающихся элементов. 2 ил.

H1))7 ((6(3h,+ 2Ъг+ 6h3)))mod 7;

(( Ht)) ((6(2h,+ 4h,+ Ьэ)));

((И 1 Н3)) C(6(6h,+ h7+ 6h3)));

((М-1 НО) ((6(4h,+ 2Ъг+ h3)));

((М-1. НО) ((6(511,+ 4Ьг+ 6h,)));

((М-А- Ht)) ((6(hn+ ha+ h3)));

где ((M ))mod 7 6.

Обратное преобразование вектора Y.. ,,, соответствующее пря/ -t мому преобразованию (7) с учетом

уравнений (10), имеет вид

((4Y, + 2V2 + 3 + 4Ч« + 2VS + t ))mod 7;

((64, + Y4+ 6Ч5 +Yt ));

((2, + 4v7 + 244+ 4V5 + vt));

((34, + 2V + 6Vj + 4V, + +Vt ));

- (( V,+47 + Y3+ 44+V5+Vt));

((5 V, + 4Va+ 643+ 3V 5 + Vt)) .

Формирование вектора прямого преобразования х к из последовательности х„ выполняется в блоке 8 прямого ТЧП согласно уравнениям (9).

(10)

У, «

м

N

/( + 1|k))mod 7 (П)

и описывается по следующим уравнениям:

I

(12)

Формирование вектора обратного преобразования у из компонентов вектора у ус выполняется в блоке 20 обратного ТЧП согласно уравнениям (13).

Отсчеты xh и hf перед выполнены-- ем прямого преобразования представляются в обратных кодах. В дальнейшем при выполнении прямого и обратного преобразования, умножения все операции над числами выполняются без учета знака разряда, вследствие чего результаты свертки посредством ТЧП по mod 7 всегда положительные.

В общем случае блок 38 присвоения знака результата свертки из результатов свертки, вычисленных посредством ТЧП по mod 7, где q 2 -1 , целое положительное число может быть построено на сумматоре с использованием схем анализа величины результатов свертки„

Входной отсчет х, секции хh ; стробирующим импульсом с первого выхода 51 блока 1, одновременно обнуляющим регистр 11, записывается в регистр 14, суммируется на сумматоре 9 с нулем, стробирующим импульсом с второго выхода 52 блока 1 записывается в регистр 11, суммируется на сумматоре 10 с нулем, так как ключ 12 до поступления второго отсчета последовательности хh на вход блока 8 закрыт сигналом с третьего выхода 19, блока 1 затем стробом с шестнадцатого выхода 53 блока 1 записывается в регистр 31„ Число, зафиксированное в регистре 31, представляющее промежуточное значение по mod 7 компонента xt вектора прямого преобразования х k от отсчета XT (9) записывается в блок 13 памяти компонент подачей адреса с четвертого выхода 16, команды Запись с пятого выхода 17, строба Выборка с шестого выхода 18 блока 1 „ i

В результате суммирования значений на выходе регистра 14 и регистра 11 на выходе сумматора 9 стоит число 2х по mod 7. Подачей стро- бирующего импульса с второго выхода 52 блока 1 число С(2х ,))mod 7 записывается в регистр 11, суммируется на сумматоре 10 с нулем, фиксируется в регистре 31, и как промежуточное значение компонента ((Х)) вектора прямого преобразования х kот отсчета х , записывается в блок 13 памяти компонент„

Подачей следующего стробирующего импульса с второго выхода 52 бло

476595 0

ка 1 в регистр 11 записывается число ((3x,))mod 7, которое суммируется на сумматоре 10 с нулем, фиксируется в регистре 31, и как промежу5 точное значение компонента ((х,)) (9) вектора прямого преобразования хе записывается в блок 13 памяти компонент, i

10 Вычисляемые таким образом промежуточные значения компонентов ((х«)), ((Ху)), ((х)) вектора прямого преобразования х от отсчета х , также записываются в блок 13 памяти ком15 поненто

Входной отсчет х стробирующим импульсом с первого выхода 51 блока 1, одновременно обнуляющим регистр 11, записывается в регистр 14,

20 суммируется на сумматоре 9 с нулем с выхода регистра 11, стробирующим импульсом с двадцать четвертого выхода 52 блока 1 записывается в регистр 11. Согласно уравнениям (9)

25 число х необходимо просуммировать с промежуточными значениями компонентов х t и х , вектора прямого пре- образованиЯо Для этого, сигналом с третьего выхода 19 блока 1 открыва30 ется ключ 12, подачей адреса с четвертого выхода 16, команды Считывание с пятого выхода 17, строба выборки с шестого выхода 18 блока 1 на блок 13 памяти компонент, с него

2g считывается промежуточное значение компонента ((xt)) на второй вход сумматора 100 Результат суммирования ((х 7+ х.,)) записывается в регистр 31 стробом с шестнадцатого вы40 хода 53 блока 1, а затем по тому же адресу, изменив команду Считывание на Запись на пятом выходе 17 блока 1, стробом выборки с шестого выхода 18 блока 1 промежуточный компо45 нент ((х)) от отсчетов х , и х- записывается в блок памяти компонентов вектора 7 0

Для того чтобы число х , сложить с промежуточным значением компоненCQ та х3, из блока 13 памяти компонент считывается число ((х)) на второй вход сумматора 31, а результат суммирования как промежуточное значение компонента ((х3)) ((6х ,+х))

55

записывается по тому же адресу об- ратро в блок 13 памяти компонент

Дальнейшая последовательность функционирования блока 8 по формированию вектора прямого преобразования xk согласно уравнениям (9) аналогична приведенному.

После поступления последнего отсчета х h последовательности в блок начинается вычисление окончательных результатов компонент вектора прямого преобразования х v, г выхода регистра 31 и соответствующий компоненту х,, компонент вектора Н, считанный из блока 5 постоянной памяти стробом выборки с восьмого выхода 7 и по адресу с седьмого выхода 6 блока 1 подаются на соответствующие входы умножителя 4 и, стробом с девятого выхода 54 блока 1, записывается в его входные регистры Результаты умножения, приведенные по модулю 7 (mod 7) в блоке приведения числа по mod 7 34 записываются в блок 35 памяти результатов умножения стробами выборки с восемнадцатого выхода 49 по адресу с девятнадцатого выхода 50 и команде Запись с семнадцатого выхода 48 блока 10

Когда в блоке прямого преобразования 8 начинается формирование следующего вектора х к lt, от следующей секции входных отсчетов х „ 1 + | , в блоке 20 начинается формирование вектора у r ( из компонентов вектора У k(, считываемых из блока 35 памят результатов умножения

Функциональные схемы блока 20 и блоков 8 идентичны,, Последовательность работы элементов блока 20 по формированию вектора обратного преобразования согласно уравнениям (12) такая же, как и в блоке 80 Запись в регистр 32 и обнуление регистра 25 осуществляется стробиру- кщим импульсом с десятого выхода 47 блока 1, запись в регистр 25 осуществляется стробом с одиннадцатого выхода 26 блока 1, управление ключом 23 осуществляется с двенадцатого выхода 30 блока 1, запись в регистр 33 осуществляется стробом с двадцатого выхода 46 блока 1, запись в блок 24 памяти компонент и считывание из нее осуществляется стробами выборки с пятнадцатого выхода 29 по адресам с тринадцатого выхода 27 и командам Запись и Считывание с четырнадцатого выхода 28 блока 1„

После поступления последнего компонента вектора у к,; в регистр 3 в блоке 20 начинается вычисление

окончательных результатов компонентов вектора обратного преобразования У|,с Каждый окончательный вычисленный компонент вектора у е , с выхода регистра 33 проходит через блок присвоения знака результата 38 и де- мультиплексор 39 и записывается в первый блок 35 памяти стробами выборки с двадцать третьего выхода 41 по адресу с двадцать первого выхода 40 и команде Запись с двадцать второго выхода 45 блока 1 управления о

5 При наличии сигнала, соответствующего команде Запись или Считывание на двадцать втором выходе 45 блока 1, информация с входа демуль- типлексора 39 подключается к входQ ным шинам соответствующего блока 36 или 37 памятио

После записи последнего компонента вектора у j , с выхода регистра 33 блок 36 памяти результатов пре5 образования в блоке 20 начинается формирование следующего вектора У { 1+1 результирующие значения компонент которого должны быть записаны в блок 37 памяти стробами выборо ки с двадцать шестого выхода 43 по адресу двадцать четвертого выхода 42 и команда Запись с двадцать пятого выхода 44 блока 1„

В данном устройстве цифровой фильтрации для свертки последовательностей xm(m 0,1,ооо, со) и hp (p 0,1,ооо,Р - 1) применен метод суммирования с перекрытием, вследствие чего последовательность хт условно

„ разделяется на секции хп(п 0,1, ooo,N - 1), каждая секция сворачивается с последовательностью np, a перекрывающиеся отсчеты свертки у °(t с двумя соседними свертками У е , , ,. и у р ,+1 складываются

При N 4 и Р 3 перекрываются два парных и два последних компонента (отсчета) свертки у f|1 с двумя соседними свертками у ,., и

п У е, Перекрывающиеся отсчеты считываются на входы выходного сумматора 2 из блоков 36 и 37 одновременно о

Блок 1 управления для устройства цифровой фильтрации, основанной на свертке секций входной последовательности xh с коэффициентами фильтра hp с использованием ТЧП по mod 7, выполнен как программное устройство

5

5

13

и построен на постоянных запоминающих устройствах.

Генератор 58 вырабатывает тактовые импульсы Счетчики 60 и 83 адресов обеспечивают адресами постоянные запоминающие устройства 63 и 8А соответственно о К выходам счетчика адресов 69 подключены десятая, одиннадцатая выходные шины 92 и 94 блока управления Счетные Т-триггеры предназначены для формирования импульсов нужной длительности о RS-триггеры предназначены для запоминания адресов о Счетчик адресов 69 обнуляется сигналом с 23-го вывода ПЗУ 63„

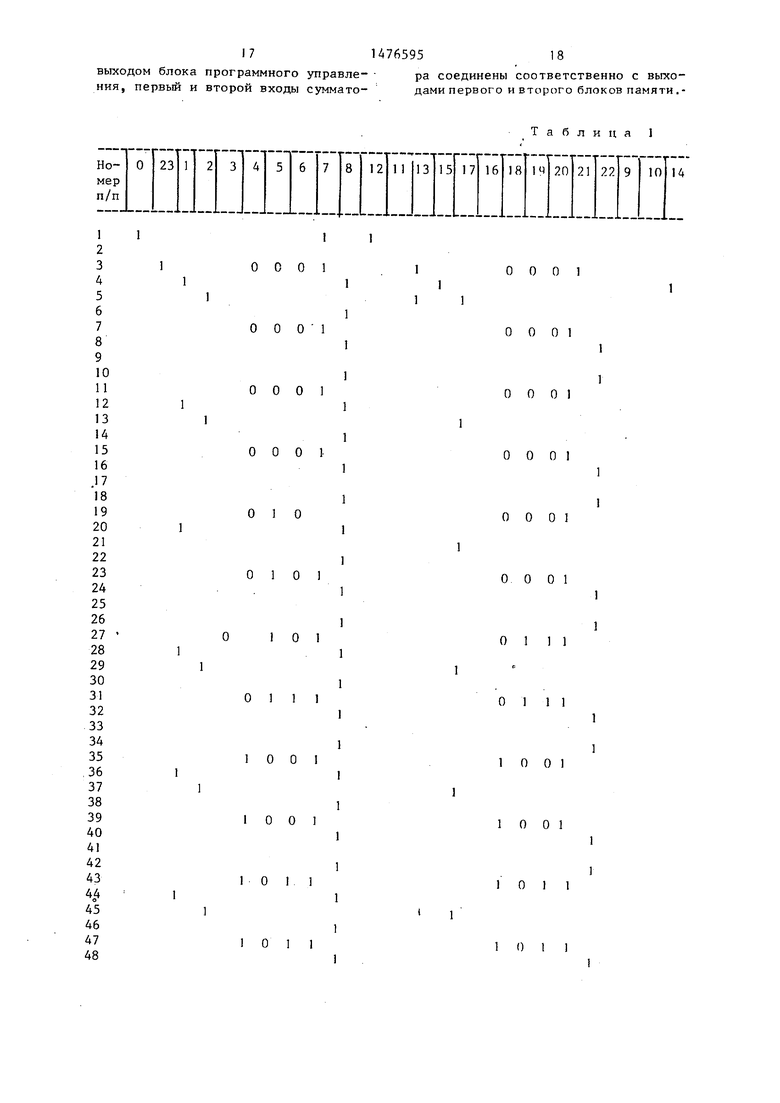

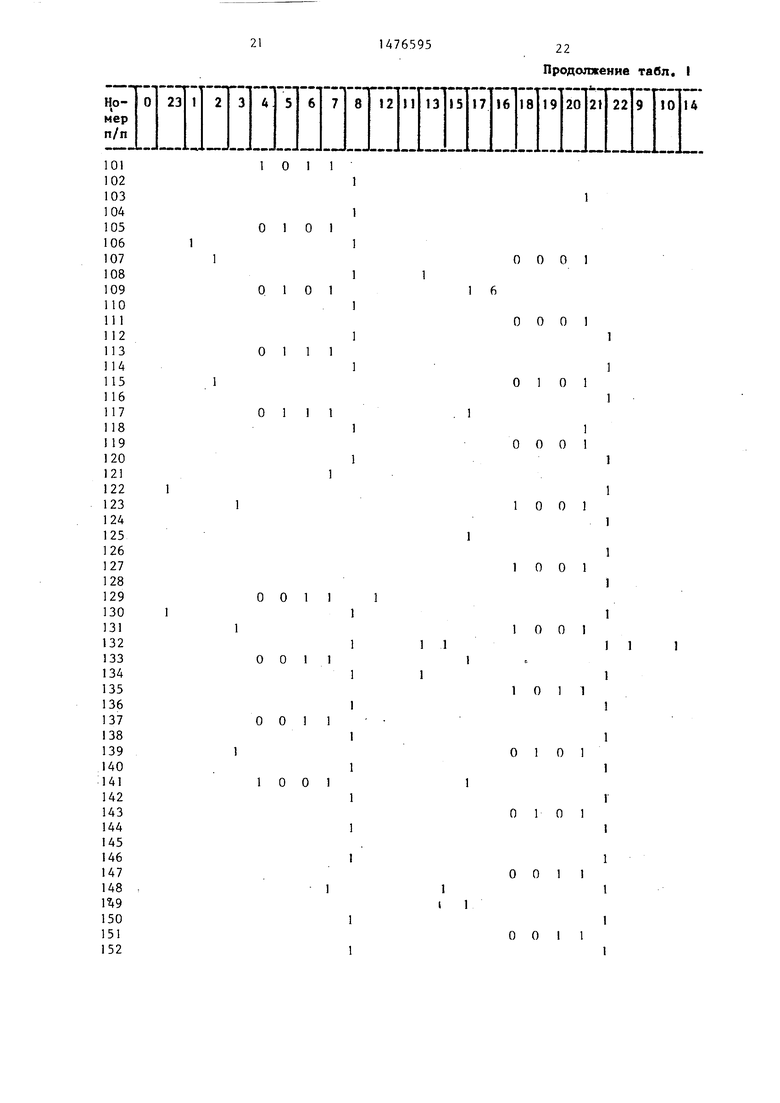

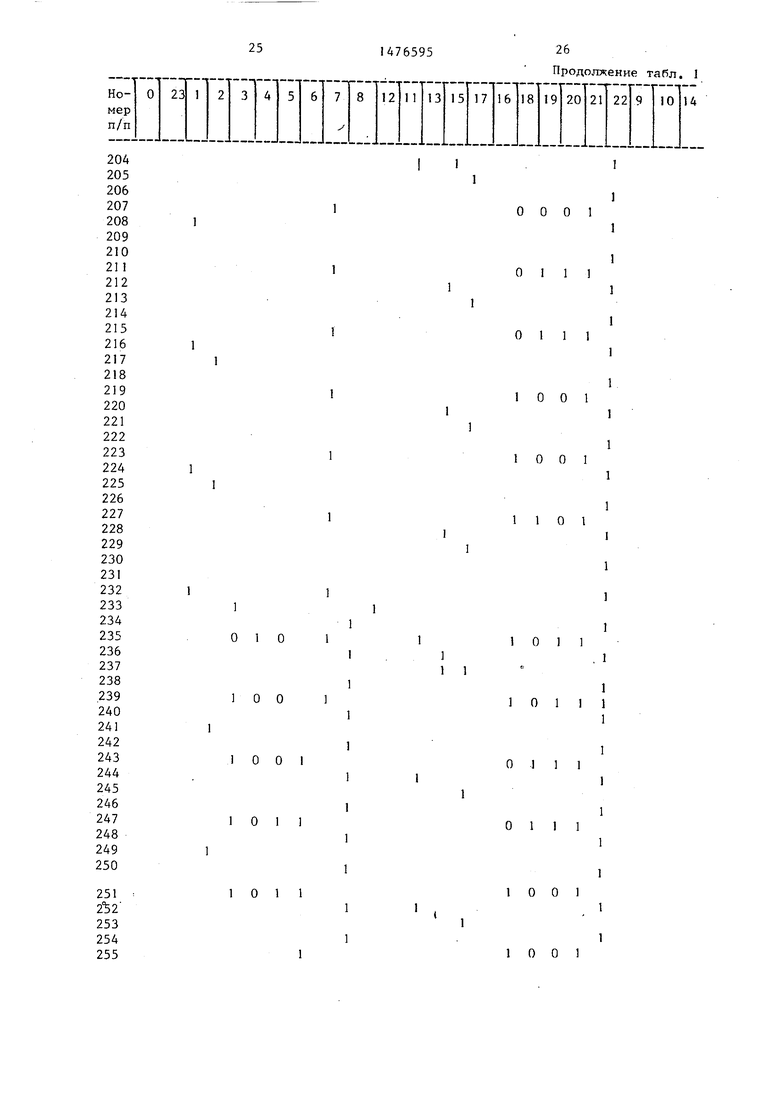

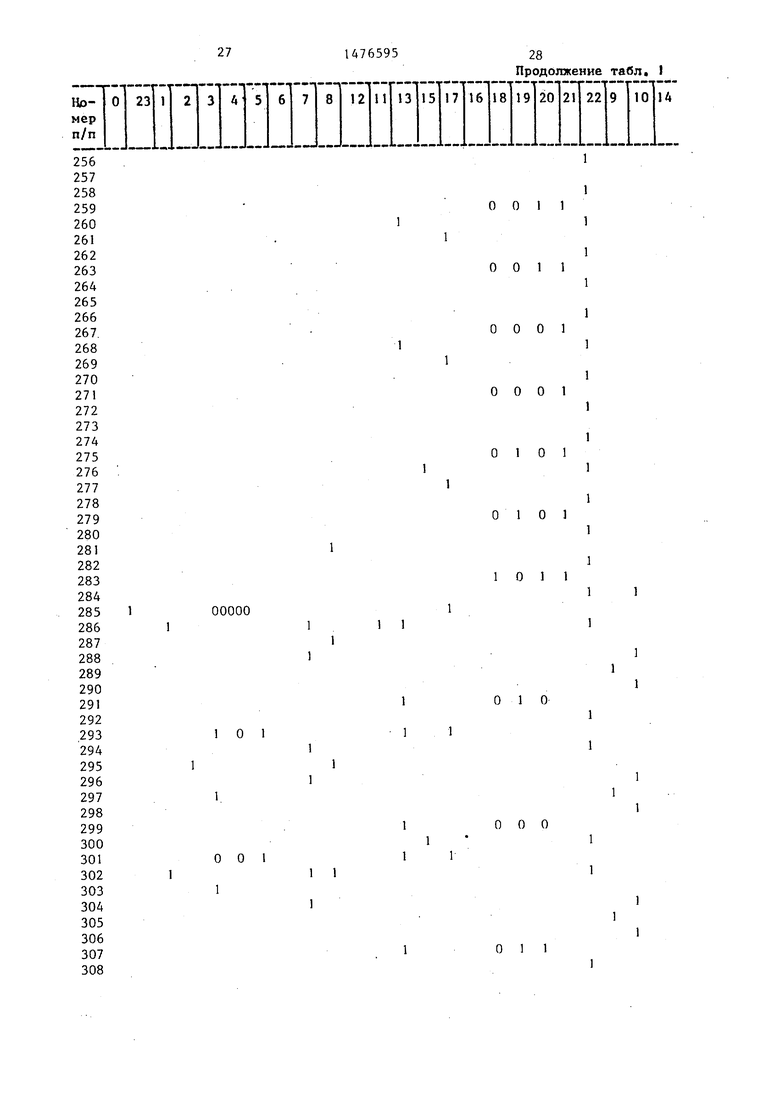

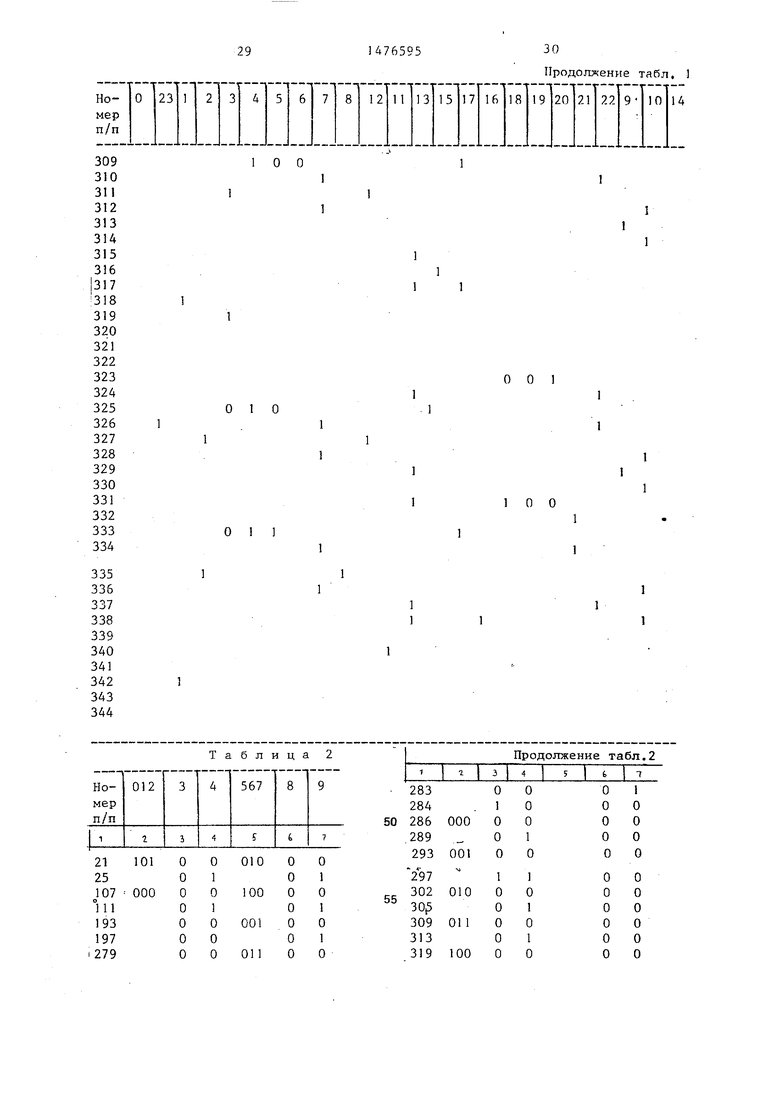

Последовательность микрокоманд, необходимых для управления устройством цифровой фильтрации, записана в ПЗУ 59,69 и приведена соответствен но в табло 1,2, в табло 1,2 отсутствие данных означает наличие логического О

В табл. манды по задействованным адресам

Число команд в ПЗУ 63 И 84 составляет соответственно 344 и 688о

Блок управления работает следующим образом.

Сигналом Пуск для блока управления, как и для всего устройства цифровой фильтрации, является подключение питания ко всем функциональным элементам. Генератор 58 начинает вырабатывать тактовые импульв ПЗУ 63,84. 1 и 2 приведены микроко

сы, поступающие на счетчики 60 и 83 адресов и через элемент НЕ 59 на входы выборки узлов 63 И 84. С выхода счетчика 60 и 83 адресов поступают адреса на адресные шины узлов 63 И 84, а сигналами с элемента НЕ 59 на входы выборки узлов 63 И 84 считыванием из них микрокомандыо

Как только на выходе счетчика ад- ресов 60 устанавливается значение числа, равное 344, схема 61 сравнения вырабатывает импульс, который через элемент ИЛИ 62 поступает на вход Усто 0 счетчика адреса 60 и сбрасывает его в ноль. Если на выходах счетчика адресов 83 устанавливается число 688, срабатывают обе схемы сравнения 61 и 76, сигналы которых обнуляют оба счетчика адресов 60 и 83„

Элемент ИЛИ 62 предназначен для упорядочения выдачи микрокоманд иЗ постоянных запоминающих устройств 63 И 84, так как после подключения

6595U

к устройству цифровой фильтрации счетчики адресов 60 и 83 могут устанавливаться в любое состояние о Сигнал схемы сравнения 76 обнуляет оба счетчика адресов 60 и 83,

0

5

Q

5

0

5

0

5

0

5

Формула изобретения

Устройство цифровой фильтрации, содержащее блок программного управления, выходной сумматор, блок прямого теоретико-числового преобразования, содержащий входной регистр, входной сумматор, регистр, сумматор компонент, ключ, узел памяти, блок умножителя, постоянную память, блок обратного теоретико-числового преобразования, содержащий входной сумматор, регистр, сумматор компонент, ключ, узел памяти, причем выход выходного сумматора соединен с выходом устройства, информационный вход входного регистра блока прямого теоретико-числового преобразования соединен с входом устройства, первый выход блока программного управления соединен с входами записи входного регистра и регистра блока прямого теоретико-числового преобразования, выход которого соединен с первым входом входного сумматора блока прямого теоретико-числового преобразования, выход которого соединен с информационным входом регистра блока прямого теоретико-числового преобразования, второй выход блока программного управления соединен с входом обнуления регистра блока прямого теоретико-числового преобразования, выход которого соединен с вторым входом входного сумматора блока прямого теоретико-числового преобразования и первым входом сумматора компонент блока прямого теоретико-числового преобразования, второй вход которого соединен с выходом ключа блока прямого теоретико-числового преобразования, управляющий вход которого соединен с третьим выходом блока программного управления, четвертый, пятый и шестой выходы которого соединены соответственно с входами адреса записи- считывания и выборки узла памяти компонент, блока прямого теоретико- числового преобразования, выход которого соединен с информационным входом ключа блока прямого теоретико-числового преобразования, седьмой и восьмой выходы блока программного управления соединены соответственно с входами адреса и выборки постоянной памяти, выход которой соединен с вторым информационным входом умножителя, стробирующий вход которого соединен с девятым выходом блока программного управления, десятый выход которого соединен с входом записи регистра блока обратного теоретико-числового преобразования, выход которого соединен с первым входом сумматора компонент блока обратного теоретико- числового преобразования и первым входом сумматора входного сигнала блока обратного теоретико-числового преобразования, выход которого соединен с информационным входом регистра блока обратного теоретико-числового преобразования, вход обнуления соединен с одиннадцатым выходом блока программного управления, двенадцатый выход которого соединен с управляющим входом ключа блока обратного теоретико-числового преобразования, выход которого соединен с вторым входом сумматора компонент блока обратного теоретико- числового преобразования, тринадцатый, четырнадцатый и пятнадцатый выхода блока программного управлени соединены соответственно с входами адреса записи-считывания и выборки узла памяти компонент блока обратного теоретико-числового преобразования, выход которого соединен с информационным входом ключа блока обратного теоретико-числового преобразования, отличающееся тем, что, с целью сокращения аппаратных затрат, устройство содержит первый и второй блоки памяти, демул типлексор, блок присвоения знака, блок памяти результатов умножения, блок приведения по модулю q, блок обратного теоретико-числового преобразования дополнительно содержит регистр компонент и входной регистр а блок прямого теоретико-числового преобразования дополнительно содержит регистр компонент, информационный вход которого соединен с выходом сумматора компонент блока прямого теоретико-числового преобразования, вход записи регистра компонент блока прямого теоретико-число0

5

0

5

0

5

0

5

0

5

вого преобразования соединен с шестнадцатым выходом блока программного управления, выход регистра компонент блока прямого теоретико-числового преобразования соединен с первым информационным входом умножителя, выход которого соединен с входом блока приведения результата по модулю q, выход которого соединен с информационным входом блока памяти результата умножения, входы запись- считывание адреса и выборки которого соединены соответственно с семнадцатым, восемнадцатым и девятнадцатым выходами блока программного управления, выход блока памяти результатов умножения соединен с информационным входом входного регистра блока обратного теоретико-числового преобразования, вход записи которого соединен с десятым выходом блока программного управления, выход входного регистра блока обратного теоретико-числового преобразования соединен с вторым входом входного сумматора блока обратного теоретико-числового преобразования, информационный вход регистра компонент блока обратного теоретико-числового преобразования соединен с выходом сумматора компонент блока обратного теоретико-числового преобразования, вход записи регистра компонент блока обратного теоретико-числового преобразования соединен с двадцатым выходом блока программного управления, выход регистра компонент блока обратного теоретико- числового преобразования соединен с информационным выходом памяти компонент блока обратного теоретике-числового преобразования и входом блока присвоения знака, выход которого соединен с информационным входом демультиплексора, первый выход которого соединен с информационным входом первого блока памяти, входы адреса записи-считывания и выборки которого соединены соответственно с двадцать первого по двадцать третий выходами блока программного управления, выходы которого с двадцать четвертого по двадцать шестой соединены с входами соответственно адреса записи-считывания и выборки второго блока памяти, информационный вход которого соединен с вторым выходом демультиплексора, управляющий вход которого соединен с двадцать вторым

171476595

программного управле- второй входы сумматорада

11

0001

о о о 1

0001

11

1

1

00011

О 1 О

11

1

0101

О101

0111

1

1001

I1

1

1

1001

1

1

1011

11

1

1

1011

ра соединены соответственно с выходами первого и второго блоков памяти .Таблица 1

0001

1 1

0001

0001

0001

0001

0001

0111

0111

1001

1001

1011

« 1

101)

19

1476595

9 0 1 52 53 54

&

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 .100

1 1

0001

0001

1011

20 Продолжение табл. 1

1

110011

11

1 1

1

0011,

0011

0111

1011

1011

21

0101

11

1

1 0101

0111

0111

00111

1

0011

0011

1001

1

1476595

22 Продолжение табл. I

14

0001

0001

0101

0001

1001

1001

1001

1

1 1

1

1011

0101

0101

0011

1 I 1

0011

0001

0001

0011

0011

0111

0111

Продолжение табл. 1

1001

1001

0001

1 1

0001

0111

0111

1011

1 1

11

1011

0011

0011

О 0 0 1

1 11

1 0101

1

1 1001

1 1

1001

1

1

1011

1011

1

0001

1 1

0111

1 1

0111

1

1

1001

1

1 1 1 I 1 1 1 1

10111

1

1001

1101

1011

1

0111

0111

1001

1001

1 00000 1

1 0 1

О 0 1

1 1

0011

0011

0001

0001

0101

0101

1011

1

1

1 1

О 1 О

000

1 1

О 1 1

29

1 О О

О 1 О

О 1 1

Таблица 2

21 25

107

111

193

197

79

101

000

О О

О

о о о о

о

1

о

о о о

010 100 001 011

о о о о о о о

о 1

о

1

о 1 о

1476595

30

Продолжение табл. 1

О 0 1

1 О О

Продолжение табл.2

31 Продолжение табл.2

Фаг

1476595

32 Продолжение табл.2

4f.4f

13U

Авторы

Даты

1989-04-30—Публикация

1987-04-06—Подача