Јь

ОО

00

со

ОО

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1683172A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1990 |

|

SU1730723A2 |

| Цифровой фильтр с дельта-модуляцией | 1987 |

|

SU1418908A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в устройствах цифровой обработки сигналов позволяет повысить быстродействие фильтра. Цифровой фильтр содержит генератор 1 импульсов, формирователи 2, 3 адресов, формирователь 4 импульсов, блок 5 постоянной памяти, блок 6 оперативной памяти, блок 8 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ , блок 9 мультиплексирования, двоичный сумматор 10, накапливающий сумматор 11 и буферные регистры 12, 13. Благодаря введению блока 7 оперативной памяти вычисление цифровой свертки обеспечивается более быстро. 1 з.п.ф-лы, 3 ил.

фиг. 1

I. 21

t.o

(hi

s-;

M-1

, , (2)

гле V Т v Рш где п, 2 х s-, i

(Ы

S i

S-i

(3) Рассмотрение сЬормулы (2) показывательных значений fyh Каждое из этих значений вычисляется только при помощи операций суммиИзобретение относится к вычислительной технике и технике связи и может быть использовано в устройствах цифровой обработки сигналов.

Цель изобретения - повышение быстродействия фильтра.

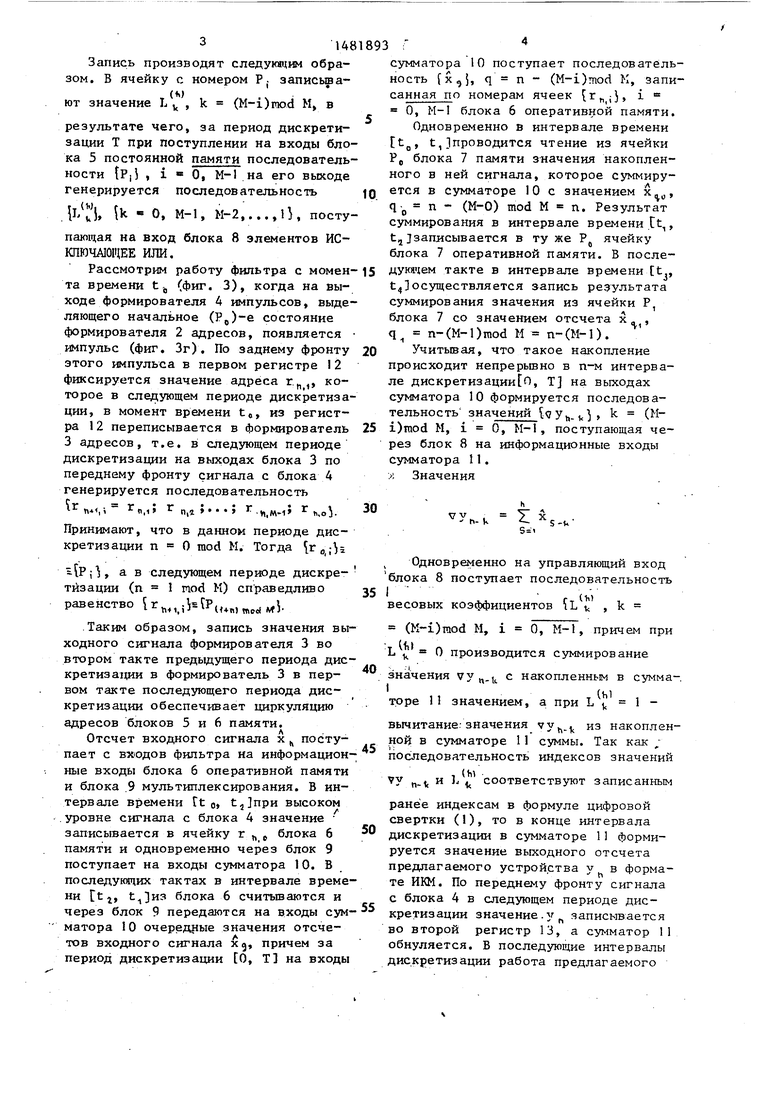

На фиг. 1 представлена функциональ ная схема фильтра; на фиг. 2 - формирователь адресов; на фиг. 3 -времен- JQ ет, что выходной сигнал Лильтра мож- ные диаграммы работы фильтра.но получить, суммируя М последоваЦифровой фильтр с линейной дельта- модуляцией содержит генератор 1 импульсов, первый 2 и второй 3 формирователи адресов, формирователь 4 им- $ рования, без выполнения операции пульсов, блок 5 постоянной памяти,многоразрядного умножения, что позпервьй 6 и второй 7 блоки оператив-воляет сократить затраты времени на

ной памяти, блок 8 элементов ИСКПЮЧА- вычисление последовательности у„}, ЮЩЕЕ ИЛИ, блок 9 мультиплексирования,- а в результате увеличить быстродей- двоичный сумматор 10, накапливающий 20 ствие цифрового фильтра, сумматор 11, первый 12 и второй 13 J регистры сдвига.

Формирователи 2 и 3 адресов содержат (фиг. 2) выделитель 14 положительного перепада, регистр 15 сдвига 25 рователях 2 и 3 адресов (цепи сброса и сумматор lb по модулю два.не показаны). На выходах фильтра при

Цифровой фильтр с линейной дельта- этом устанавливается нулевое значе- модуляцией работает по следующему ая- ние выходного сигнала. Одновременно горитму.в блоки 6 и 7 оперативной памяти неИзвестно, что выходной сигнал циф- 30 обходимо занести нулевые последова- рового фильтра, в котором весовые ко- тельности. эффициенты представлены в формате ли нейной дельта-модуляции (ЛДМ), а входной сигнал - в формате импульсноПеред началом фильтрации необходимо провести обнуление накапливающего сумматора 11, регистра 13 и установить начальные значения в формиГенератор 1 импульсов генерирует непрерывную последовательность импульсов (Лиг. За) частотой К/Т, где

кодовЪй модуляции (ИКМ), вычисляется 35 Т - период дискретизации. По передпо Лормуле цифровой свертки

нему фронту (положительному перепаду) этих импульсов, поступающих на тактовые входы Формирователей 2 и 3 адресов, на выходах последних формиру- 4д ются соответственно последовательности адресов блока 5 постоянной памяти (весовых коэффициентов) I,-},

1 -L

}гО

(М

(О

где |xj, k О - входная ИКМ-последо тельность;

Јe(m J, , К-1 -весовая последованему фронту (положительному перепаду) этих импульсов, поступающих на тактовые входы Формирователей 2 и 3 адресов, на выходах последних формиру- 4д ются соответственно последовательности адресов блока 5 постоянной памяти (весовых коэффициентов) I,-},

i - О, М-1 (фиг. 36), совпадающих с i последовательностью адресов второго

тельность, д блока 7 оперативной памяти, и после- ленная в формате

довательность адресов блока 6 опера- тивной памяти Гц,, i О, М-1.

ЛДМ: е(Г е Н; ППрямое вычисление последовательности отсчетов 1у„} по (1) требует ведения в каждом периоде дискретизации большого числа ар метических . операций (п М), что препятствует получению высокого быстродействия цифрового фильтра,55

довательность адресов блока 6 опера- тивной памяти Гц,, i О, М-1.

Формирователи 2 и 3 адресов выпол нены одинаковыми, т.е. при rtod I где п - номер отсчета входного сигна ла, {rh|;) По каждому из адресов Р, в блоке 5 постоянной памяти записанное значение соответствующего коэффициента весовой последовательно

сти цифрового фильтра в формате ли- Для получения алгоритма функциони- нейной дельта.модуляции L (wfc (1

рования предлагаемого устройства изменяют порядок суммирования в O)s

V,

)/2, LliMof 11

I. 21

t.o

(hi

s-;

M-1

, , (2)

гле V Т v Рш где п, 2 х s-, i

(Ы

Рассмотрение сЬормулы ет, что выходной сигнал но получить, суммируя М тельных значений fyh Каждое из этих значений вычисляется только при помощи операций суммиет, что выходной сигнал Лильтра мож- но получить, суммируя М последоварования, без выполнения операции многоразрядного умножения, что поз вычисление последовательности у„}, а в результате увеличить быстродей- ствие цифрового фильтра,

рователях 2 и 3 адресов (цепи сброса не показаны). На выходах фильтра при

Перед началом фильтрации необходимо провести обнуление накапливающего сумматора 11, регистра 13 и установить начальные значения в форми обходимо занести нулевые последова- тельности.

Генератор 1 импульсов генерирует непрерывную последовательность импульсов (Лиг. За) частотой К/Т, где

Т - период дискретизации. По переднему фронту (положительному перепаду) этих импульсов, поступающих на тактовые входы Формирователей 2 и 3 адресов, на выходах последних формиру- ются соответственно последовательности адресов блока 5 постоянной памяти (весовых коэффициентов) I,-},

i - О, М-1 (фиг. 36), совпадающих с последовательностью адресов второго

блока 7 оперативной памяти, и после-

блока 7 оперативной памяти, и после-

довательность адресов блока 6 опера- тивной памяти Гц,, i О, М-1.

Формирователи 2 и 3 адресов выполнены одинаковыми, т.е. при rtod II, где п - номер отсчета входного сигнала, {rh|;) По каждому из адресов Р, в блоке 5 постоянной памяти записанное значение соответствующего коэффициента весовой последовательно V,

)/2, LliMof 11

31481893

Запись производят следующим образом. В ячейку с номером Р( записывают значение L v , k (M-i)mod М, в

5

результате чего, за период дискретизации Т при поступлении на входы блока 5 постоянной памяти последовательности {Р,5 , i « О, М-1 на его выходе генерируется последовательность 10 ,(w

сумматора 10 поступает последователь ность x,j, q n - (M-i)Tnod К, запи санная по номерам ячеек г,,} i и О, М-1 блока 6 оперативной памяти. Одновременно в интервале времени t0, t,проводится чтение из ячейки Рс блока 7 памяти значения накопленного в ней сигнала, которое суммируется в сумматоре 10 с значением х

n - (М-0) mod M

цо

п. Результат

гт IWi tiл w i w о V W шии n - и. гезулътйч L J, k - 0, M-l, M-2,...,l), посту- суммирования в интервале времени tt,,

пающая на вход блока 8 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Рассмотрим работу фильтра с момента времени t ъ (фиг. 3), когда на выходе формирователя 4 импульсов, выделяющего начальное (Р0)-е состояние формирователя 2 адресов, появляется импульс (фиг. Зг). По заднему фронту этого импульса в первом регистре 12 фиксируется значение адреса г п ,, которое в следующем периоде дискретизации, в момент времени te, из регистра 12 переписывается в йюрмирователь 3 адресов, т.е. в следующем периоде дискретизации на выходах блока 3 по переднему фронту сигнала с блока 4 генерируется последовательность

1Г «, , Гп,1 г , г у,,м-1 Г h,ol

Принимают, что в данном периоде дискретизации n 0 mod M. Тогда frd;}j

,, а в следующем периоде дискре- тизации (n I nod M) справедливо

равенство fr „+1 i№lUn, Wcc( M.

Таким образом, запись значения выходного сигнала формирователя 3 во втором такте предыдущего периода дискретизации в формирователь 3 в первом такте последующего периода дискретизации обеспечивает циркуляцию адресов блоков 5 и 6 памяти.

Отсчет входного сигнала х h поступает с входов фильтра на информацией ные входы блока 6 оперативной памяти и блока 9 мультиплексирования. В интервале времени ft 0 высоком уровне сигнала с блока 4 значение записывается в ячейку г „ с блока 6 памяти и одновременно через блок 9 поступает на входы сумматора 10. В последующих тактах в интервале времени , Ц}из блока 6 считываются и через блок Ч передаются на входы сум- матора 10 очередные значения отсчетов входного сигнала хд, причем за период дискретизации О, Т на входы

,

сумматора 10 поступает последовательность x,j, q n - (M-i)Tnod К, запи- санная по номерам ячеек г,,} i и О, М-1 блока 6 оперативной памяти. Одновременно в интервале времени t0, t,проводится чтение из ячейки Рс блока 7 памяти значения накопленного в ней сигнала, которое суммируется в сумматоре 10 с значением х

n - (М-0) mod M

цо

п. Результат

Ч о V W шии n - и. гезулътйч суммирования в интервале времени tt,,

Vi:

tajзаписывается в ту же Р0 ячейку блока 7 оперативной памяти. В последующем такте в интервале времени t., t4 осуществляется запись результата суммирования значения из ячейки Р блока 7 со значением отсчета х qi n-(M-l)mod M n-(M-l).

Учитывая, что такое накопление происходит непрерывно в n-м интервале дискретизации Г, Т на выходах сумматора Ю формируется последовательность значений Уь-П (М i)tnod M, 1 0, М-1, поступающая через блок 8 на информационные входы сумматора I1. Значения

:VK

Ј,s

S-U

Одновременно на управляющий вход блока 8 поступает последовательность

(ю весовых коэффициентов iL , k

®

45

40

(K-i)raod M, i О, М-1, причем при L 0 производится суммирование

значения vy n.k с накопленным в сумма1 , ,т (Ы ,

торе 1I значением, а при L t 1 вычитание значения vyh.v из накопленной в сумматоре 11 суммы. Так как последовательность индексов значений

У и L соответствуют записанным

ранее индексам в формуле цифровой свертки (1), то в конце интервала дискретизации в сумматоре 11 Формируется значение выходного отсчета предлагаемого устройства у в формате ИКМ. По переднему фронту сигнала с блока 4 в следующем периоде дискретизации значение уп записывается во второй регистр 13, а сумматор 11 обнуляется. В последующие интервалы дискретизации работа предлагаемого

514

цифрового фильтра происходит аналогично.

Формирователь 3 (2) адреса представляет собой генератор М-последова тельности. Для генерации последовательности адресов fP, } используется следующее свойство П-последователь- ности: ее можно получить на основе регистра сдвига с соответствующими обратными связями, причем задержка формирования очередной кодовой комбинации на выходе регистра сдвига не превышает времени задержки в одном триггере, в то время как, например, в счетчиках эта задержка значительно больше. Другим используемым свойством указанной последовательности является то, что на протяжении М тактов, М 2h - 1, п - разрядност регистра сдвига, выходные кодовые комбинации не повторяются. Начальная кодовая комбинация может быть произвольной, отличной от нулевой, причем все кодовые комбинации повторяются в выходной последовательности с соответствующим временным сдвигом.

Следовательно, псевдослучайная последовательность Р,-}, i 0, M-1, Р- О, М 2 - 1, генерируемая на выходах формирователя 3 (2) адреса, позволяет адресовать соответствующее число ячеек в блоках 5-7 памяти, а использование для ее формирования регистра 15 сдвига с соответствующими связями позволяет сократить непроизводительные потери времени на формирование каждого адреса.

Таким образом, затраты времени на вычисление отсчета выходного сигнала по сравнению с известным фильтром уменьшаются.

Формула изобретения

)о Цифровой фильтр с линейной дельта-модуляцией, содержащий генератор импульсов, выход которого подключен к входу первого формирователя адресов, выходы которого соединены с входами блока постоянной памяти и формирователя импульсов, выход которого подключен к тактовым входам первого и второго буферных регистров и управляющим входам первого блока оперативной памяти и блока мультиплексирования, второй формирователь .адресов, двоичный сумматор, накапливающий сумматор, выход блока постоянной памяти подключен к первому входу

936

блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы первого блока оперативной памяти соединены с первыми информационными входами блока мультиплексирования, вторые информационные входы которого объединены с информационными входами первого блока оперативной памяти и являются входами фильтра, о т л и чающийся тем, что, с целью повышения быстродействия фильтра, в него введен второй блок оперативной памяти, адресные входы которого подключены к выходам первого формирователя адресов, управляющий вход второго блока оперативной памяти объединен с тактовыми входами накапливающего сумматора и второго формирователя адресов и подключен к выходу генератора импульсов, выходы второго формирователя адресов соединены с адресными входами первого блока оперативной памяти и информационными входами первого буферного регистра, выходы

5 которого соединены с информационными входами второго формирователя адресов, управляющий вход которого объ- единен с входом обнуления накапливающего сумматора и подключен к выходу

формирователя импульсов, выходы блока мультиплексирования и второго блока оперативной памяти соединены соответственно с первыми и вторыми входами двоичного сумматора, выходы которого

5 подключены к информационным входам второго блока оперативной памяти и вторым входам блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которого соединены с информационными входами накапливающего сумматора, выходы которого соединены с информационными входами второго буферного регистра, выходы которого являются выходами фильтра. 2. Фильтр по п. 1, о т л и ч а ю Ч и и с я тем, что формирователь адресов содержит регистр сдвига, сумматор по модулю два и формирователь переднего фронта импульса, выход которого соединен с управляющим входом

регистра сдвига, установочные и тактовый входы которого и вход формиро- вателя переднего фронта импульса являются соответственно информационными тактовым и управляющим входами формирователя, выход сумматора по модулю два соединен с информационным входом регистра сдвига, выходы которого подключены к входам сумматора по модулю два и являются выходами формирователя.

а б

S

Фиг. I

Фг/sJ

| Погрибной В | |||

| А | |||

| Бортовые системы обработки сигналов | |||

| - Киев: Hay- кова думка, 1984, с; 84 | |||

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-23—Публикация

1987-07-13—Подача