(21)4273510/24-24

(22)06.04,87

(46) 30.04.89. Бкш. № 16

(71)Азербайджанский институт нефти и химии им, М.Азиэбекова

(72)Т.М,Алиев, Д.И.Дамиров, А.А.Тер-Хачатуров и А.З, Федорцов

(53)681.325(088.8)

(56)Авторское свидетельство СССР № 488147, кл. G 01 R 13/02, 1974.

Авторское свидетельство СССР № 1129528, кл. G 01 R 13/02, 1983.

(54)АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

(57)Изобретение относится к информационно-измерительной технике и может быть использовано как для измерения постоянных электрических сигналов, следующих на фоне аддитивных случайных помех, так и для определения параметров (математического ожидания) случайных процессов. Цель изобретения - повышение быстродействия - достигается тем, что в устройство, содержащее генератор 1 импульсов, генератор 4 шума, компараторы 5, 7, постоянное запоминающее устройство 9, цифроанапоговый преобразователь 13, сумматор 14, регистр 15, дешифратор 16, введены мультиплексоры 3, 10, блок 11 сравнения кодов, элемент 2 задержки,RS- триггер 8 и блок 12 задания кода. 1 з,п, ф-лы, 3 ил,

Sfi

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Цифровой генератор гармонических сигналов | 1984 |

|

SU1211846A1 |

| Формирователь импульсов тока | 1985 |

|

SU1287263A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Устройство для измерения аналоговых величин с автоматическим масштабированием | 1986 |

|

SU1406792A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ СЛУЧАЙНОЙ ПОГРЕШНОСТИ | 1991 |

|

RU2024193C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2012036C1 |

Изобретение относится к информационно-измерительной технике и может быть использовано как для измерения постоянных электрических сигналов, следующих на фоне аддитивных случайных помех, так и для определения параметров (математического ожидания) случайных процессов. Цель изобретения - повышение быстродействия - достигается тем, что в устройство, содержащее генератор 1 импульсов, генератор 4 шума, компараторы 5, 7, постоянное запоминающее устройство 9, цифроаналоговый преобразователь 13, сумматор 14, регистр 15, дешифратор 16, введены мультиплексоры 3, 10, блок 11 сравнения кодов, элемент 2 задержки, RS-триггер 8 и блок 12 задания кода. 1 з.п. ф-лы, 3 ил.

Ь

О

оэ о со

(риг./

11476609

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано как для измерения постоянных электрических сигналов р в том числе действующих на фоне аддитивных случайных помехt так и для определения параметров (математического ожидания) случайных процессов,

Целью изобретения является повышение быстродействия.

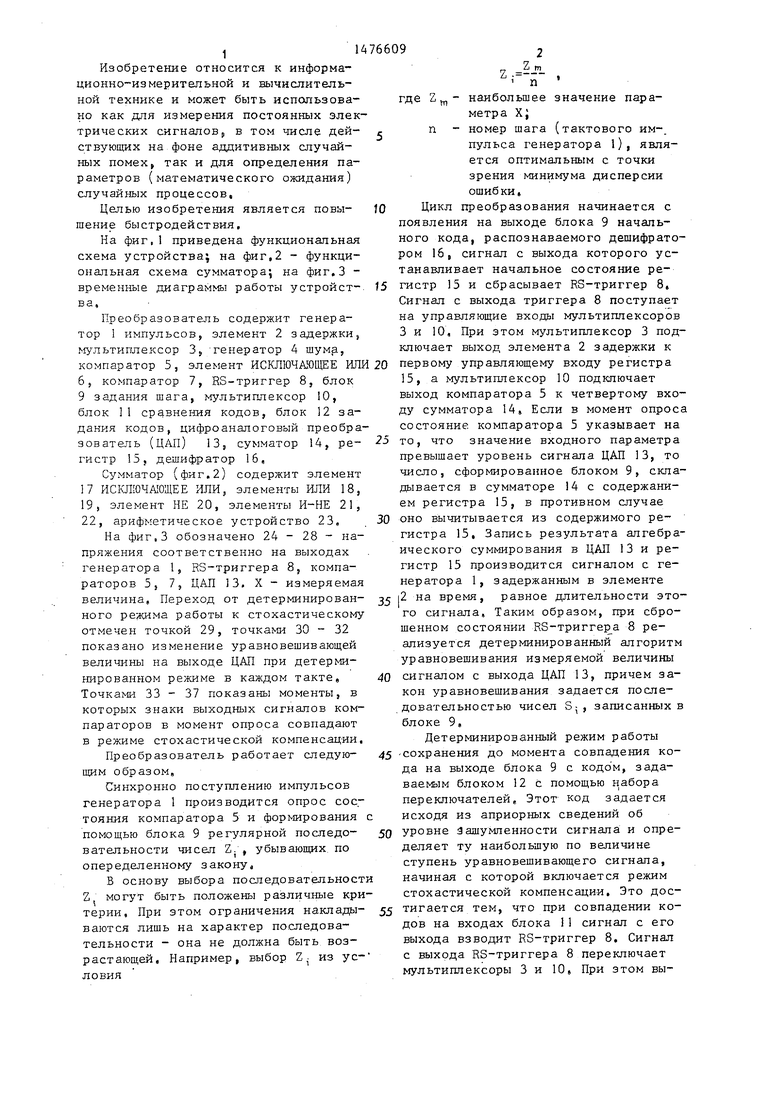

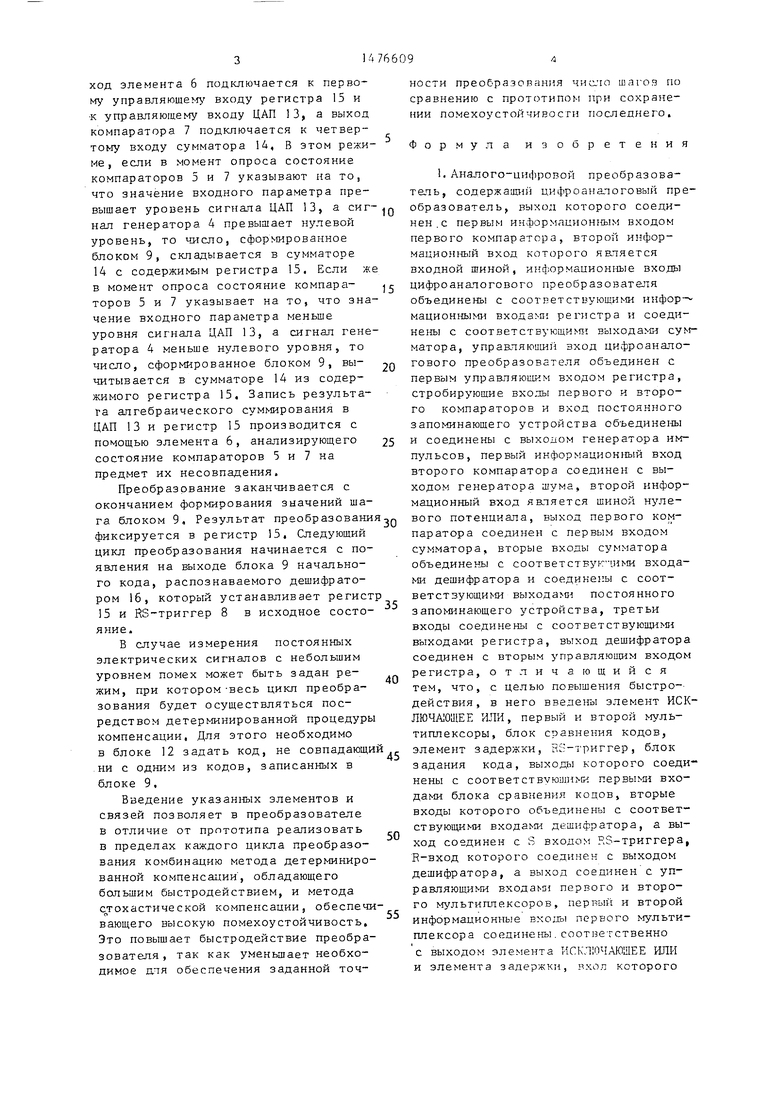

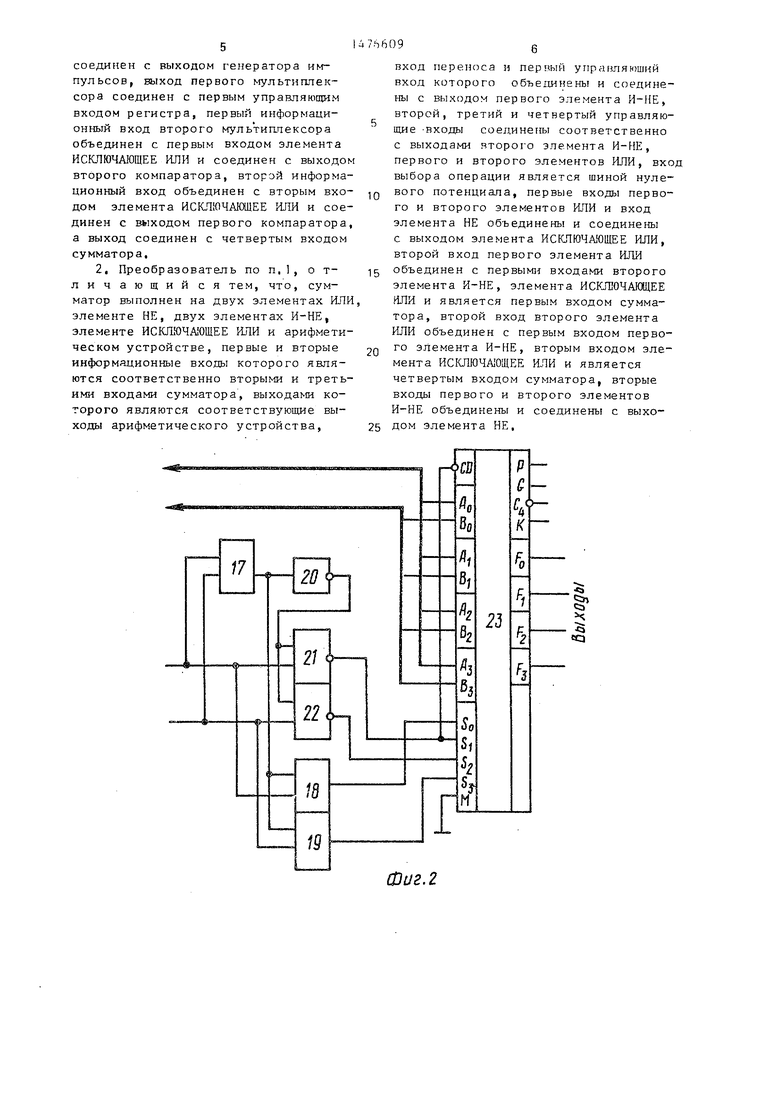

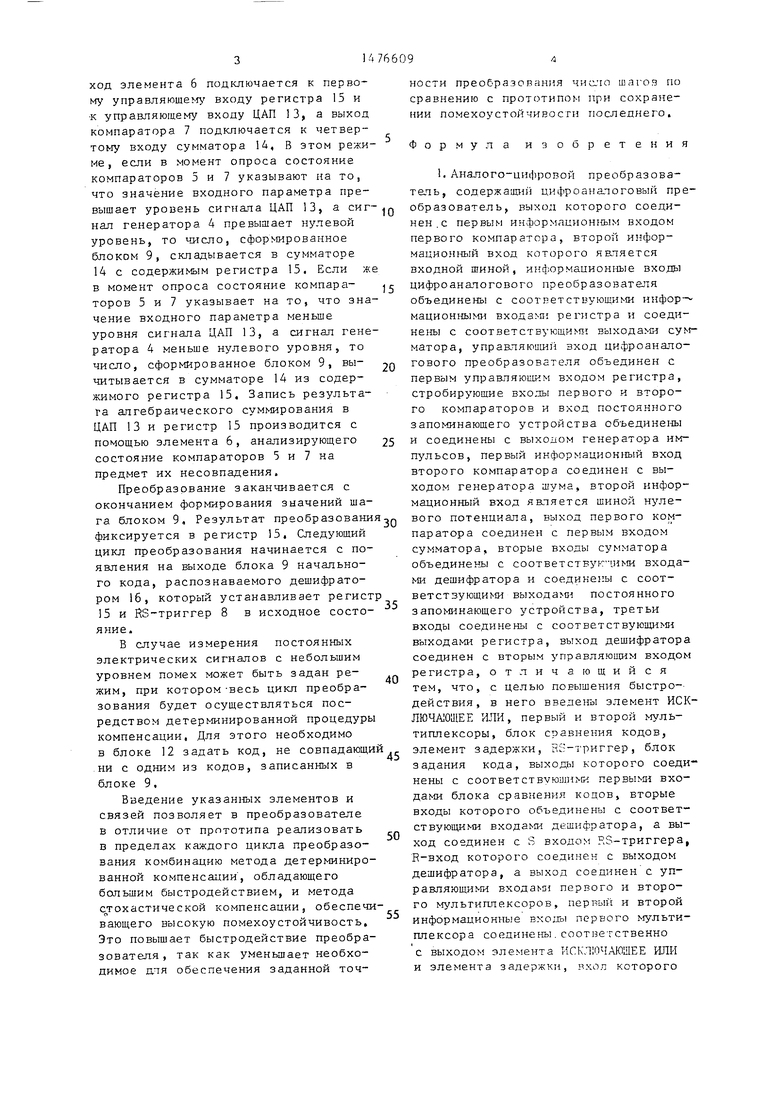

На фиг,1 приведена функциональная схема устройства; на фиг,2 - функциональная схема сумматора; на фиг,3 - временные диаграммы работы устройства,

Преобразователь содержит генератор 1 импульсов, элемент 2 задержки, мультиплексор 3S генератор 4 шума,

2

Z .-- 1 п

10

где Zm- наибольшее значение параметра XJ

п - номер шага (тактового им-, пульса генератора 1), является оптимальным с точки зрения минимума дисперсии ошиб ки,

Цикл преобразования начинается с появления на выходе блока 9 начального кода, распознаваемого дешифратором 16, сигнал с выхода которого устанавливает начальное состояние регистр 15 и сбрасывает RS-триггер 8, Сигнал с выхода триггера 8 поступает на управляющие входы мультиплексоров 3 и 10, При этом мультиплексор 3 подключает выход элемента 2 задержки к компаратор 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20 первому управляющему входу регистра 6, компаратор 7, RS-триггер 8, блок15, а мультиплексор 10 подключает

15

9 задания шага, мультиплексор 10, блок II сравнения кодов, блок 12 задания кодов, цифроаналоговый преобразователь (ЦАП) 13, сумматор 14, ре- гистр 15, дешифратор 16,

Сумматор (фиг.2) содержит элемент 17 ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы ИЛИ 18, 19, элемент НЕ 20, элементы И-НЕ 21, 22, арифметическое устройство 23,

На фиг.З обозначено 24 - 28 - напряжения соответственно на выходах генератора 1, RS-триггера 8, компараторов 5, 7, ЦАП 13, X - измеряемая величина, Переход от детерминирован- ного режима работы к стохастическому отмечен точкой 29, точками 30 - 32 показано изменение уравновешивающей величины на выходе ЦАП при детерминированном режиме в каждом такте, Точками 33 - 37 показаны моменты, в которых знаки выходных сигналов компараторов в момент опроса совпадают в режиме стохастической компенсации.

Преобразователь работает следую- щим образом.

Синхронно поступлению импульсов генератора 1 производится опрос состояния компаратора 5 и формирования с помощью блока 9 регулярной последе- вательности чисел Zt , убывающих по опеределенному закону

В основу выбора последовательности Z. могут быть положены различные критерии, При этом ограничения наклады- ваются лишь на характер последовательности - она не должна быть возрастающей. Например, выбор Z1 из ус-1 ловил

2

Z .-- 1 п

выход компаратора 5 к четвертому входу сумматора 14, Если в момент опрос состояние компаратора 5 указывает на то, что значение входного параметра превышает уровень сигнала ЦАП 13, то число, сформированное блоком 9, складывается в сумматоре 14 с содержанием регистра 15, в противном случае оно вычитывается из содержимого регистра 15, Запись результата алгебраического суммирования в ЦАП 13 и регистр 15 производится сигналом с генератора 1, задержанным в элементе |2 на время, равное длительности этого сигнала. Таким образом, при сброшенном состоянии RS-триггера 8 реализуется детерминированный алгоритм уравновешивания измеряемой величины сигналом с выхода ЦАП 13, причем закон уравновешивания задается последовательностью чисел S;, записанных в блоке 9,

Детерминированный режим работы сохранения до момента совпадения кода на выходе блока 9 с кодом, задаваемым блоком 12 с помощью набора переключателей. Этот код задается исходя из априорных сведений об уровне Зашумленности сигнала и определяет ту наибольшую по величине ступень уравновешивающего сигнала, начиная с которой включается режим стохастической компенсации. Это достигается тем, что при совпадении кодов на входах блока 11 сигнал с его выхода взводит RS-триггер 8, Сигнал с выхода RS-триггера 8 переключает мультиплексоры 3 и 10, При этом выход элемента 6 подключается к первому управляющему входу регистра 15 и к управляющему входу ЦАП 13, а выход компаратора 7 подключается к четвертому входу сумматора 14, В этом режиме, если в момент опроса состояние компараторов 5 и 7 указывают на то, что значение входного параметра превышает уровень сигнала ЦАП 13, а сигнал генератора 4 превышает нулевой уровень, то число, сформированное блоком 9, складывается в сумматоре

14с содержимым регистра 15. Если ж в момент опроса состояние компараторов 5 и 7 указывает на то, что значение входного параметра меньше уровня сигнала ЦАП 13, а сигнал генератора 4 меньше нулевого уровня, то число, сформированное блоком 9, вычитывается в сумматоре 14 из содержимого регистра 15. Запись результата алгебраического суммирования в ЦАП 13 и регистр 15 производится с помощью элемента 6, анализирующего состояние компараторов 5 и 7 на предмет их несовпадения.

Преобразование заканчивается с окончанием формирования значений шага блоком 9, Результат преобразовани фиксируется в регистр 15. Следующий цикл преобразования начинается с появления на выходе блока 9 начального кода, распознаваемого дешифратором 16, который устанавливает регист

15и RS-триггер 8 в исходное состояние.

В случае измерения постоянных электрических сигналов с небольшим уровнем помех может быть задан режим, при котором-весь цикл преобразования будет осуществляться посредством детерминированной процедуры компенсации, Для этого необходимо в блоке 12 задать код, не совпадающи ни с одним из кодов, записанных в блоке 9,

Введение указанных элементов и связей позволяет в преобразователе в отличие от прототипа реализовать в пределах каждого цикла преобразования комбинацию метода детерминированной компенсации, обладающего большим быстродействием, и метода стохастической компенсации, обеспечивающего высокую помехоустойчивость. Это повышает быстродействие преобразователя, так как уменьшает необходимое для обеспечения заданной точ0

5

0

5

0

5

0

5

0

5

ности преобразования число шагоч по сравнению с прототипом при сохранении помехоустойчивости последнего.

Формула изобретения

соединен с выходом генератора импульсов, выход первого мультиплексора соединен с первым управляющим входом регистра, первый информационный вход второго мультиплексора объединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и соединен с выходом второго компаратора, второй информационный вход объединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и соединен с выходом первого компаратора, а выход соединен с четвертым входом сумматора,

2, Преобразователь по п.1, отличающий ся тем, что, сумматор выполнен на двух элементах ИЛИ элементе НЕ, двух элементах И-НЕ, элементе ИСКЛЮЧАЮЩЕЕ ИЛИ и арифметическом устройстве, первые и вторые информационные входы которого являются соответственно вторыми и третьими входами сумматора, выходами которого являются соответствующие выходы арифметического устройства,

0

вход переноса и первый управляющий вход которого объединены и соединены с выходом первого элемента И-НЕ, второй, третий и четвертый управляющие -входы соединены соответственно с выходами второго элемента И-НЕ, первого и второго элементов ИЛИ, вход выбора операции является шиной нулевого потенциала, первые входы первого и второго элементов ИЛИ и вход элемента НЕ объединены и соединены с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход первого элемента ИЛИ объединен с первыми входами второго элемента И-НЕ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является первым входом сумматора, второй вход второго элемента ИЛИ объединен с первым входом первого элемента И-НЕ, вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является четвертым входом сумматора, вторые входы первого и второго элементов И-НЕ объединены и соединены с выхо- 5 дом элемента НЕ,

5

I

Ч

«а

Фиг.2

О

ФигЗ

Авторы

Даты

1989-04-30—Публикация

1987-04-06—Подача