Изобретение относится к измерительной технике и может быть использовано в системах телемеханики и автоматического управления для опре- деления разности двух независимых колебаний.

Цель изобретения - повышение быстродействия путем сокращения времени обработки сигналов.

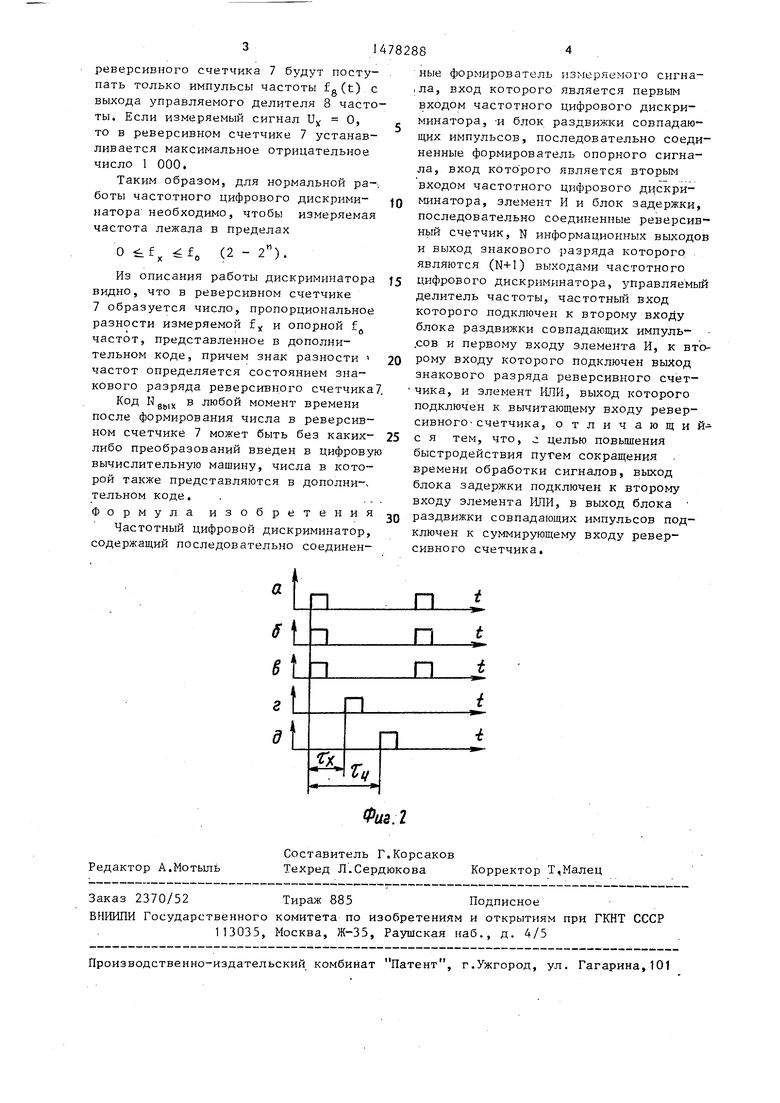

На фиг.1 показана структурная электрическая схема частотного цифрового дискриминатора; на фиг.2 - временные диаграммы его работы.

Частотный цифровой дискриминатор содержит формирователь 1 измеряемого сигнала, формирователь 2 опорного сигнала, блок 3 раздвижки совпадающих импульсов, блок 4 задержки, элемент ИЛИ 5, элемент И б, реверсивный счет- чик 7 и управляемый делитель 8 частоты.

Дискриминатор работает следующим образом.

Блок 4 и блок 3 обеспечивают раз- движку совпадающих во времени импульсов частоты f с выхода формирователя 1 (фиг.2а) и импульсов частоты f с выхода формирователя 2 (фиг.26). На фиг.2в показаны импульсы частоты

снимается логическая единица и элемент 6 открыт.-На вычитающий вход реверсивного счетчика 7 поступают сдвинутые, импульсы опорного сигнала f0 и импульсы с частотой fg с выхода управляемого делителя 8, а на суммирующий вход - сдвинутые импульсы измеряемого сигнала.

Работа дискриминатора в этом случае

описывается системой уравнении

N

вых

(t) (Ј,(«) - f,(7) - Ј,(Ј)) dt; МО „ N.hl, t)

&Ь|Х

реверсивного

где п - число разрядов

счетчика 7; Newx(t) - значение кода на выходах

дискриминатора.

Систему t 1) можно записать в операторной форме

5(fx(P) - fg(P)

- f0);

(2)

f0W fo Решая систему

,«.

(2), находим

L-:IPL.

i

-L

+

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| Цифровой дискриминатор | 1983 |

|

SU1184070A1 |

| Сглаживающий преобразователь знакопеременных частотно-импульсных сигналов в код | 1980 |

|

SU869027A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СКОРОСТИ ИЗМЕНЕНИЯ ТЕМПЕРАТУРЫ | 2012 |

|

RU2506548C1 |

| Цифровой следящий частотомер | 1980 |

|

SU892335A1 |

| Система регулирования скорости | 1984 |

|

SU1229727A1 |

| Цифровая динамическая следящая система | 1980 |

|

SU924667A2 |

| УМНОЖИТЕЛЬ ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU355624A1 |

| Аналого-цифровой преобразователь сдвига фаз | 1981 |

|

SU955519A2 |

Изобретение относится к измерительной технике и может быть использовано в системах телемеханики и автоматического управления. Цель изобретения - повышение быстродействия путем сокращения времени обработки сигналов. Дискриминатор содержит формирователь 1 измеряемого сигнала, формирователь 2 опорного сигнала, блок 3 раздвижки совпадающих импульсов, блок 4 задержки, элемент ИЛИ 5, элемент И 6, реверсивный счетчик 7, управляемый делитель 8 частоты. С целью повышения быстродействия выход блока 4 подключен ко второму входу элемента ИЛИ, выход блока 3 подключен к суммирующему входу счетчика 7. Для нормальной работы дискриминатора необходимо, чтобы измеряемая частота лежала в пределах O≤FX≤FO(2 - 2-N), где FX - измеряемая частота

FO -опорная частота. 2 ил.

fs на выходе управляемого делителя 8. Интервал Ј

о- - сдвиг импульсов частоты fjfj 1Ы выходе блока 3 (фиг.2г) относительно импульсов час-- тоты f0 опорного сигнала. Интервал 2 - сдвиг импульсов частоты Ј04 на выходе блока 4 (фиг.2д) отного сигнала. ь0 - минимальный интервал между импульсами, обусловленный быстродействием логических элементов и реверсивного счетчика 7. Максимальные значения частот измеряемого

fp и опорного

величиной f

сигналов 1

макс

Сравниваемые гармонические сигналы Ux и U0 поступают на формирователи 1 и 2, на выходах которых формируются частотно-импульсные сигналы

к и foПусть частота измеряемого сигнала

будет больше частоты опорного сигнала

fv Ј„

х - о )

тогда в реверсивном счетчике 7 устанавливается положительный код. При этом с его выхода знакового разряда

где Т 2n/f0 - постоянная времени частотного цифрового дискриминатора.

При СО , Т « 1, где СО л - максимальная частота в спектре огибающей частотно-модулированного сигнала f x, инерционностью дискриминатора можно пренебречь и значение кода на выходе определяется выражением

N

вых

0. р,

In

где uf(t) Јх(-) о причем величина fx(t) ограничена неравенством

45

f,(t)

f

0(2 - 2).

Q

5

Если частота измеряемого сигнала меньше частоты опорного сигнала, т.е.

.

то на вычитающий вход реверсивного счетчика 7 поступает больше импульсов,, чем на его суммирующий вход, и значение числа в реверсивном счетчике 7 начинает уменьшаться.

После образования в счетчике отт рицательного числа 1111 (соответствует 1 001 в прямом коде) закрывается элемент И 6, на вычитающий вход

реверсивного счетчика 7 будут поступать только импульсы частоты fg(t) с выхода управляемого делителя 8 частоты. Если измеряемый сигнал Ux О, то в реверсивном счетчике 7 устанавливается максимальное отрицательное число 1 000.

Таким образом, для нормальной работы частотного цифрового дискриминатора необходимо, чтобы измеряемая частота лежала в пределах

О ±fx f0 (2 - 2).

Из описания работы дискриминатора видно, что в реверсивном счетчике 7 образуется число, пропорциональное разности измеряемой fx и опорной Ј0 частот, представленное в дополнительном коде, причем знак разности частот определяется состоянием знакового разряда реверсивного счетчика

Код ЫВЬ1Х в любой момент времени после формирования числа в реверсивном счетчике 7 может быть без каких- либо преобразований введен в цифрову вычислительную машину, числа в которой также представляются в дополни- тельном коде. Формула изобретения

Частотный цифровой дискриминатор, содержащий последовательно соединенные формирователь измеряемого сигна- ,ла, вход которого является первым входом частотного цифрового дискриминатора, и блок раздвижки совпадающих импульсов, последовательно соединенные формирователь опорного сигнала, вход которого является вторым входом частотного цифрового дискриQ мина-гора, элемент И и блок задержки, последовательно соединенные реверсивный счетчик, N информационных выходов и выход знакового разряда которого являются (N+1) выходами частотного

5 цифрового дискриминатора, управляемый делитель частоты, частотный вход которого подключен к второму входу блока раздвижки совпадающих импуль- .сов и первому входу элемента И, к вто0 Р°му входу которого подключен выход

знакового разряда реверсивного счет- чика, и элемент ИЛИ, выход которого подключен к вычитающему входу реверсивного- счетчика, отличающий5 с я тем, что, с целью повышения быстродействия путем сокращения времени обработки сигналов, выход блока задержки подключен к второму входу элемента ИЛИ, в выход блока

0 раздвижки совпадающих импульсов подключен к суммирующему входу реверсивного счетчика.

| Цифровой дискриминатор | 1983 |

|

SU1184070A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-07—Публикация

1986-09-08—Подача