(Б ) ЦИФРОВАЯ ДИНАМИЧЕСКАЯ СЛЕДЯЩАЯ СИСТЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ФАЗОВЫЙ ДИСКРИМИНАТОР | 1972 |

|

SU349007A1 |

| Цифровой фазовый дискриминатор | 1980 |

|

SU924737A2 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368856A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368857A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

| Цифровая система регулирования частоты вращения двигателя постоянного тока | 1986 |

|

SU1386959A1 |

| Цифровой частотомер | 1980 |

|

SU918873A1 |

| Дискретный электропривод | 1978 |

|

SU911456A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В ЦИФРОВОЙ КОД | 1969 |

|

SU240345A1 |

| ЦИФРОВОЙ РЕГИСТРИРУЮЩИЙ ДЕВИОМЕТР | 1973 |

|

SU374548A1 |

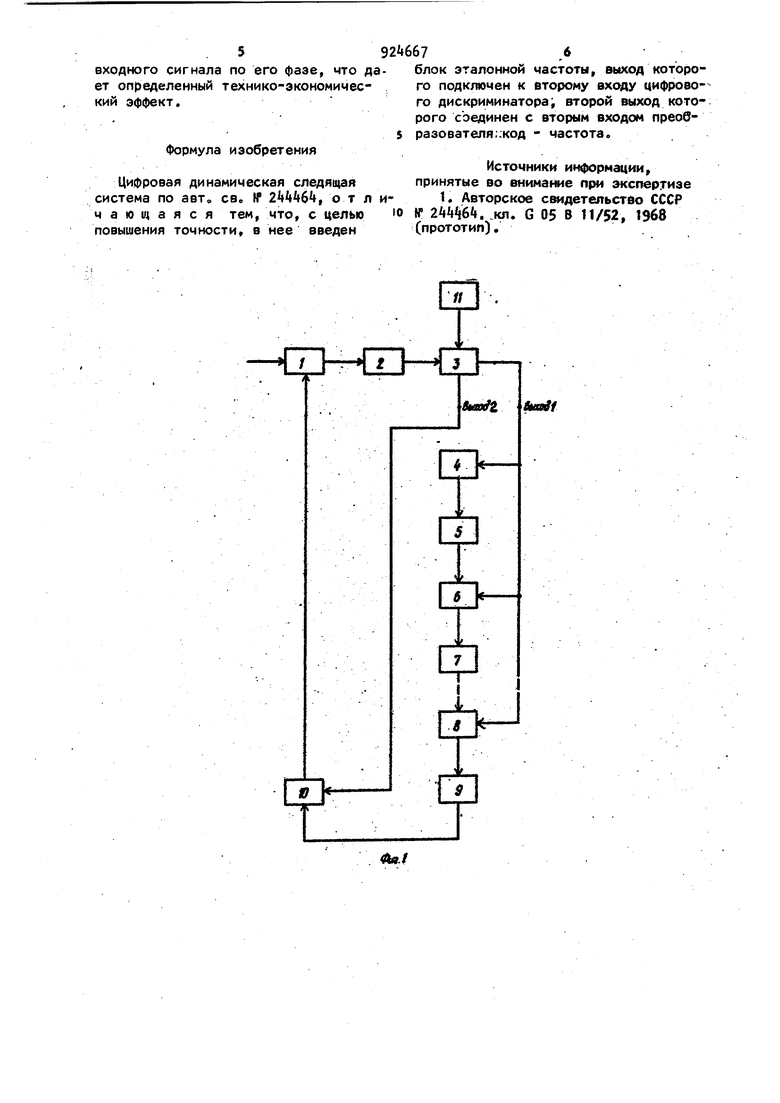

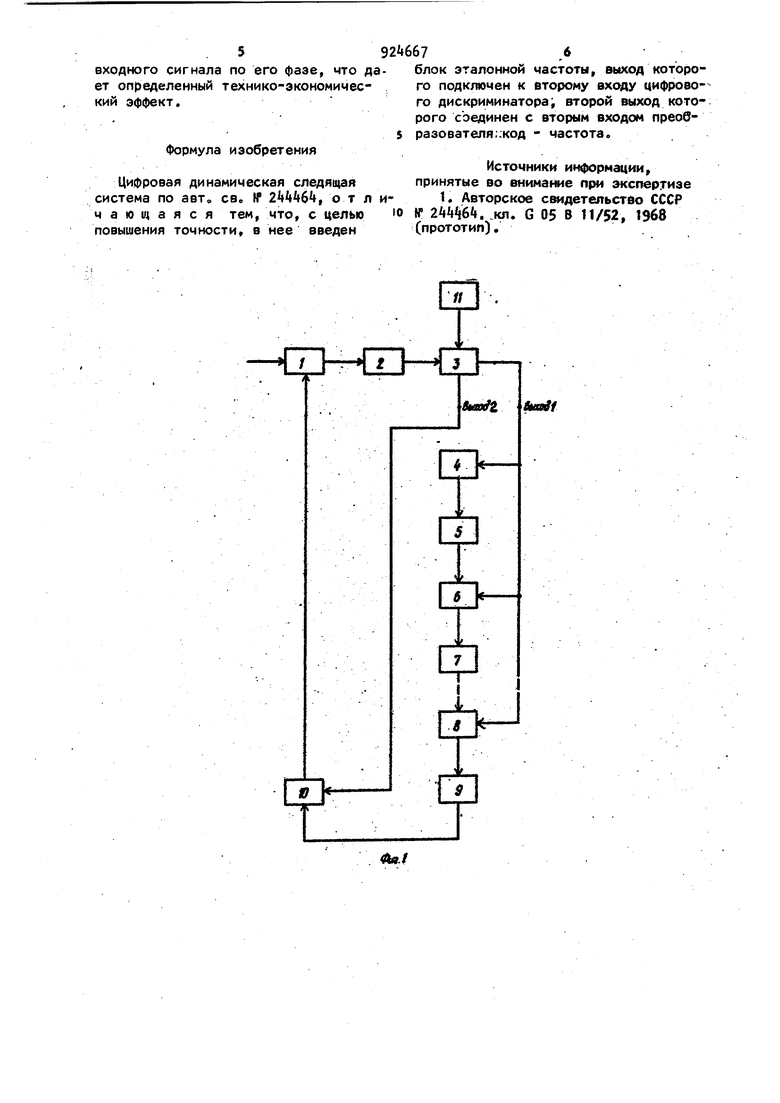

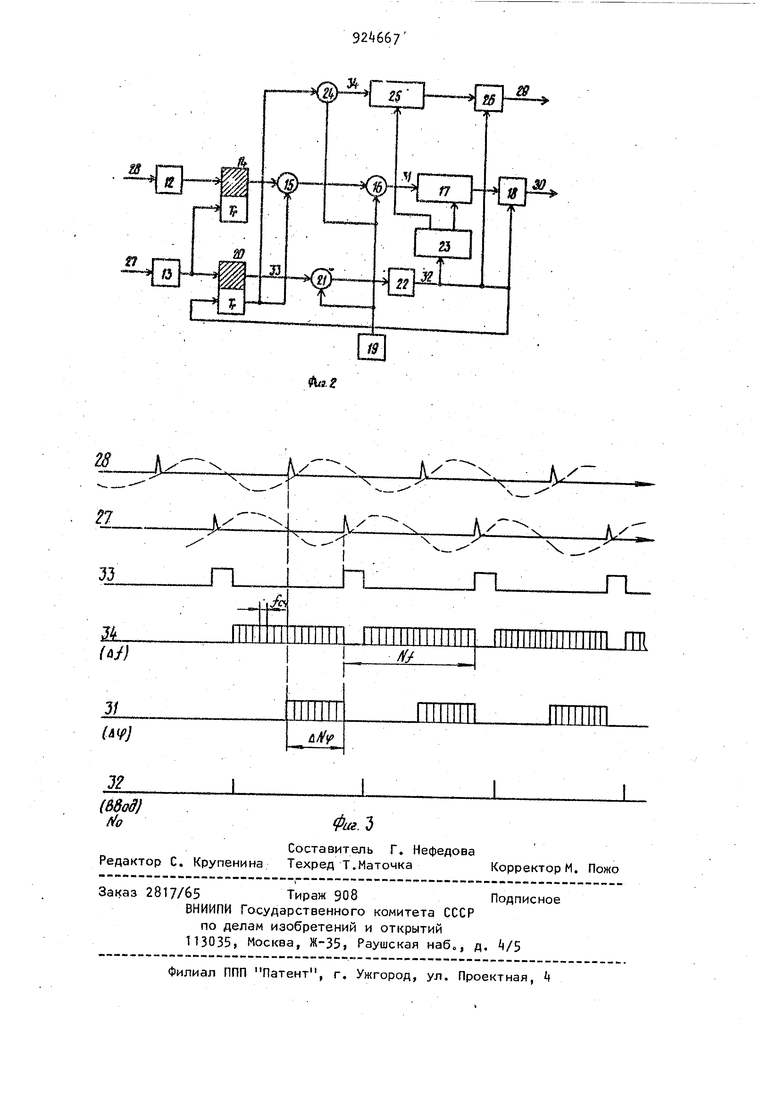

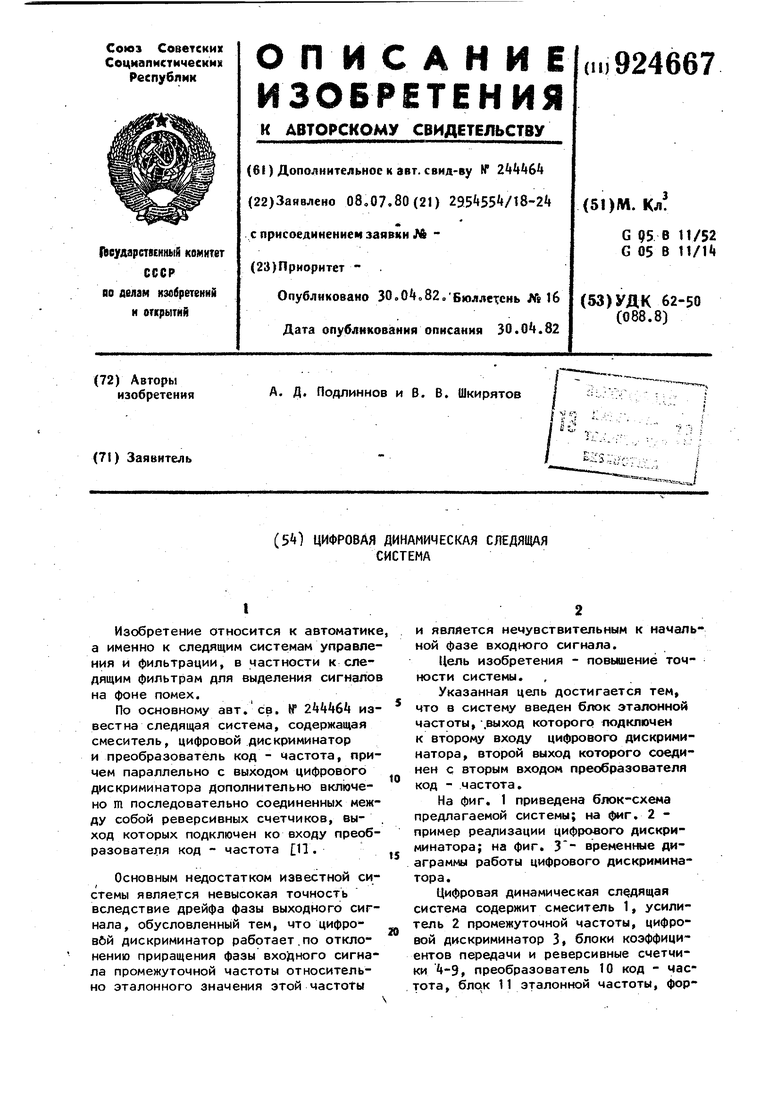

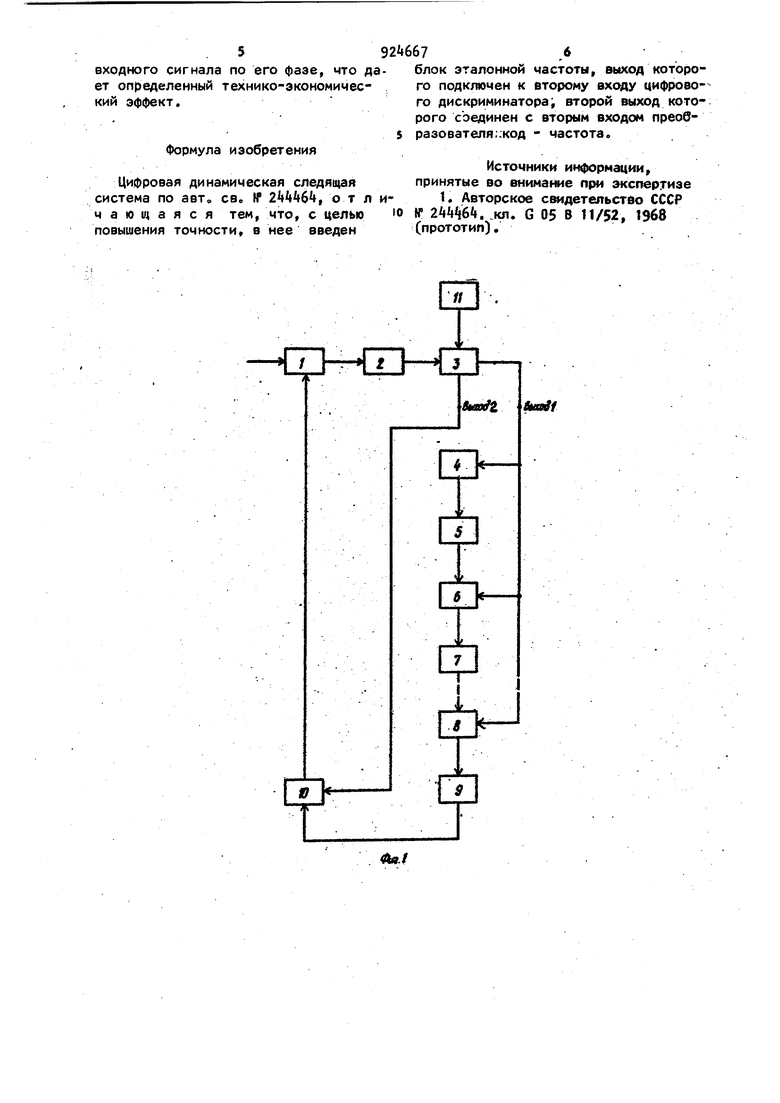

Изобретение относится к автоматике а именно к следящим системам управления и фильтрации, в частности к следящим фильтрам для выделения сигналов на фоне помех. По основному авт.св. № 2kkk6 t известна следящая система, содержащая смеситель, цифровой дискриминатор и преобразователь код - Частота, причем параллельно с выходом цифрового дискриминатора дополнительно включено m последовательно соединенных между собой реверсивных счетчиков, выход которых подключен ко входу преобразователя код - частота П. Основным недостатком известной системы является невысокая точность вследствие дрейфа фазы выходного сигнала, обусловленный тем, что цифровбй дискриминатор работает.по отклонению приращения фазы входного сигнала промежуточной частоты относительно эталонного значения этой частоты И является нечувствительным к начальной фазе входного сигнала. Цель изобретения - повьииениё точности системы. Указанная цель достигается тем, что в систему введен блок эталонной частоты, -.выход которого подключен к второму входу цифрювого дискриминатора, второй выход которого соединен с вторым входом преобразователя код - частота. На фиг. 1 приведена блок-схема предлагаемой системы; на фиг. 2 пример реализации цифрового дискриминатора; на фиг. 3- временные диаграммы работы цифрового дискриминатора. Цифровая динамическая следящая система содержит смеситель 1, усилитель 2 промежуточной частоты, цифровой дискриминатор 3, блоки коэффициентов передачи и реверсивные счетчики -Э, преобразователь 10 код - частота, блс1К 11 эталонной частоты, форнирователь 12 опорного сигнала, формирователь 13 измеряемого сигнала, первый триггер Н, первый и второй вентили 15 и 16, первый счетчик 17 первый регистр 18, генератор 19 эталонных импульсов, второй триггер 20, третий вентиль 21, делитель 22 частоты, регистр 23 опорных чисел, четвертый вентиль , второй счетчик 25, второй регистр 26, первый 27 и второй 28 входы цифрового дискриминатора, первый 29 и второй 30 выходы циф рооого дискриминатора, выход-31 вентиля 16, выход 22 частоты делителя 32 выход 35 триггера 20, выход З венти.ля 2k,. Система работает следующим :обра гй Напряжение промежуточной частоты с выхода усилителя 2 поступает на вход ЦИФРОВОГО дискриминатора 3, где на первом выходе выделяется величина рг ссогласования uNf в цифровой форме Все время обработки величины paccoi- ласования ANp занимает в системе астатизмом. тто порядка m временных циклов. - . Во время первого цикла величина NI записывается с соответстующими коэффициентами передачи в реверсивные счетчики, которые используются в качестве интеграторов. Во время второго цикла число из реверсивного счетчика 5 со своим знаком записывается в реверсивный счетчик 7, где суммируется с имеющимся там числом. Таким образом, после окончания т-го цикла в реверсивном счетчике 9 образуется результирующее число, пропорциональное сумме одинарного, двойного, тройного и т.д. вплоть до т-го интеграла от величины рассогласования. Пропорционально этому рассогласованию на выходе преобразователя 10 код - частота образуется частота, которая поступает на смеситель 1. Дискриминатор 3 работает следущим образом. Сигнал с выхода усилителя 2 промежуточной частоты поступает через первый вход 27 на формирователь 13 для формирования импульсов в момент перехода синусоидального сигнала через, нулевой уровень. При поступлении очередного импульса с выхода формирователя 13 триггер 20 устанавливает ся в единицу и открывает вентиль 21, в результате чего счетные импульсы проходят на делитель 22 частоты. остоящий в общем случае из п-разрядого счетчика-делителя„ Импульсы с выхода делителя 22 частоты поступают на опрос регистров 18 и 26, считывая цифровые значения частотного рассогласования ДЫ и фазового рассогласования uN( на выход дискриминатора и одновременно записывая в счетчики 17 и 25 через регистр 23 опорных чиел числа No; NO, и устанавливается триггер 20 в нулевое состояние для очередного измерения N и N. Причем Nf fuf -т. г. Nf N - N; ; N - 2 тогда окончательно имеем f сг f ег д Nf -J - V cr (Те. - TO) , Л.П-L Д где Тй и Тд, - периоды измеряемого и опорного сигналов соответственно. При поступлении на единичный вход триггера 20 очередного импульса fg, цикл работы повторяется. Согласно временной диаграмме (фиг. 3) на выходе триггера 20, вентилей 15 и 16 формируется мерный интервал, пропорциональный фазовому сдвигу между опорным импульсным сигналом 28 и измеряемым 27. В счетчике 17 с учетом предварительно записанного числа NU , пропорционального половине периода опорного сигнала f , образуется величина N - , которая через регистр 18 считывается на второй выход 30 дискриминатора. Преимущество предлагаемой динамической следящей системы состоит в том, что за любой интервал времени ее работы расхождение текущей фазы фходного сигнала код - частота относительно фазы входного сигнала не превышает половины периода частоты входного сигнала, поскольку предлагаемая следящая система, обладая всеми достоинствами частотной автоподстройки частоты в части вхождения в синхронизм, практически при любом частотном рассогласовании обеспечивает отслеживание входного сигнала с точностьк др его фазы. Таким образом, предлагаемая цифровая динамическая следящая система, обеспечивая высокие качества системы частотной автоподстройки, обладает и высокой точностью отслеживания входного сигнала по его фазе, что дает определенный технико-экономический эффект. Формула изобретения Цифровая динамическая еледя|цая система по авт, ев, № , о т л чающаяся тем, что, с целью повышения точности, в нее введен 5 ию67,6 блок эталонной частоты, выход которого подключен к второму входу цифрового дискриминатораi второй выход которого сэединен с вторым входом преобразователя;:код - частота. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № .,кл. G 05 В 11/52, 1968 (прототип).

W

.::

./

И

Авторы

Даты

1982-04-30—Публикация

1980-07-08—Подача