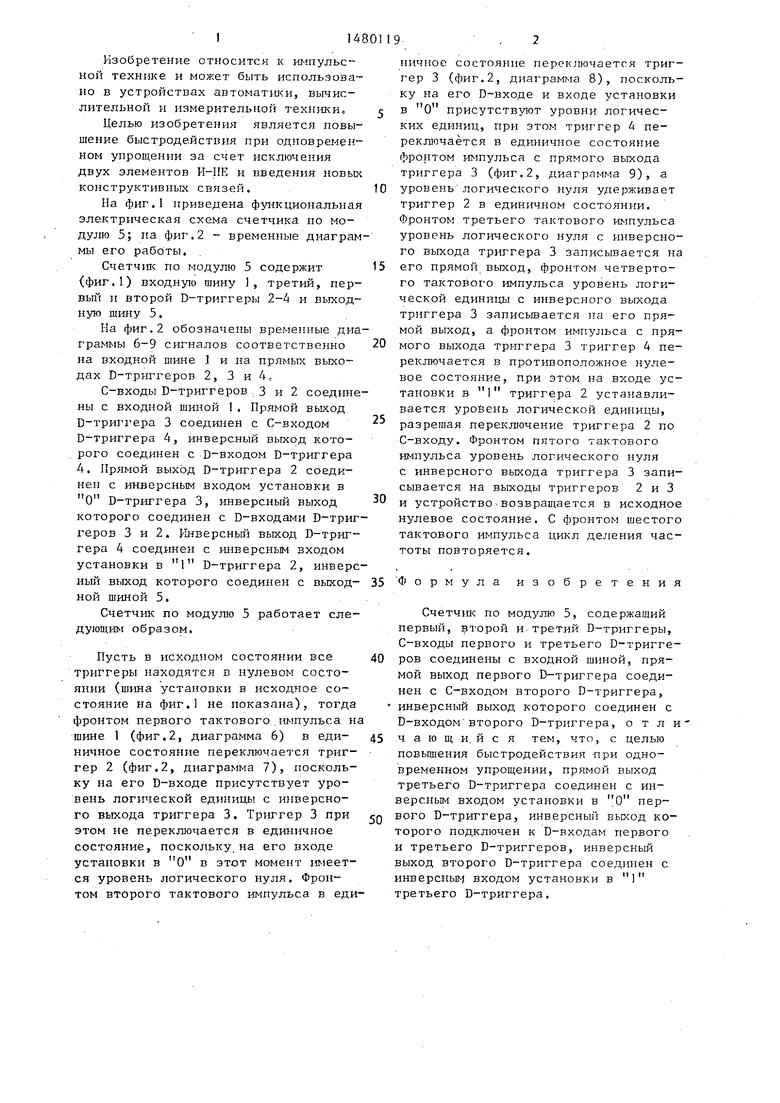

фиг.1

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, вычислительной и измерительной техники.

Целью изобретения является повышение быстродействия при одновременном упрощении за счет исключения двух элементов И-ПЕ и введения новых конструктивных связей.

На фиг.1 приведена функциональная электрическая схема счетчика по модулю 5; на фиг.2 - временные диаграммы его работы.

Счетчик по модулю 5 содержит (фиг.1) входную шину 1, третий, первый и второй D-триггеры 2-4 и выходную шину 5,

На фиг.2 обозначены временные диаграммы 6-9 сигналов соответственно на входной шине 3 и на прямых выходах D-триггеров 2, 3 и 4С

С-входы D-триггеров З и 2 соединены с входной шиной 1. Прямой выход В триггера 3 соединен с С-входом D-триггера 4, инверсный выход которого соединен с D-ВХОДОМ D-триггера 4. Прямой выход D-триггера 2 соединен с инверсным входом установки в О D-триггера З, инверсный выход которого соединен с D-входами D-триггеров 3 и 2. Инверсный выход D-триггера 4 соединен с инверсным входом установки в 1 D-триггера 2, инверсный выход которого соединен с выход- ной шиной 5.

Счетчик по модулю 5 работает следующим образом.

Пусть в исходном состоянии все триггеры находятся в нулевом состоянии (шина установки в исход юе состояние на фиг,1 не показана), тогда фронтом первого тактового импульса на шине 1 (фиг.2, диаграмма 6) в еди- ничное состояние переключается триггер 2 (фиг,2, диаграмма 7), поскольку на его D-входе присутствует уровень логической единицы с инверсного выхода триггера 3. Триггер 3 при этом не переключается в единичное состояние, поскольку на его входе установки в О в этот момент имеется уровень логического нуля. Фронтом второго тактового импульса в единичное состояние переключается триггер 3 (фиг.2, диаграмма 8), поскольку на его D-входе и входе установки в О присутствуют уровни логических единиц, при этом триггер 4 переключается в единичное состояние фронтом импульса с прямого выхода триггера 3 (фиг.2, диаграмма 9), а уровень логического нуля удерживает триггер 2 в единичном состоянии. Фронтом третьего тактового импульса уровень логического нуля с инверсного выхода триггера 3 записывается на его прямой выход, фронтом четвертого тактового импульса уровень логической единицы с инверсного выхода триггера 3 записывается на его прямой выход, а фронтом импульса с прямого выхода триггера 3 триггер 4 переключается в противоположное нулевое состояние, при этом на входе установки в 1 триггера 2 устанавливается уровень логической единицы, разрешая переключение триггера 2 по С-входу. Фронтом пятого тактового импульса уровень логического нуля с инверсного выхода триггера 3 записывается на выходы триггеров 2 и 3 и устройство возвращается в исходное нулевое состояние. С фронтом шестого тактового импульса цикл деления частоты повторяется.

Формула изобретения

Счетчик по модулю 5, содержащий первый, второй и третий D-триггеры, С-входы первого и третьего D-триггеров соединены с входной шиной, прямой выход первого D-триггера соединен с С-входом второго D-триггера, инверсный выход которого соединен с D-входом второго D-триггера, о т л и чающийся тем, что, с целью повышения быстродействия при одновременном упрощении, прямой выход третьего D-триггера соединен с инверсным входом установки в О первого D-триггера, инверсный выход которого подключен к D-входам первого и третьего D-триггеров, инверсный выход второго D-триггера соединен с инверсным входом установки в 1 третьего D-триггера,

Г

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь разностной частоты импульсных последовательностей | 1984 |

|

SU1265985A1 |

| Программируемый делитель частоты | 1985 |

|

SU1298899A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Устройство для устранения влияния дребезга сигнала | 1989 |

|

SU1725371A1 |

| Синхронный делитель частоты на двенадцать | 1985 |

|

SU1298902A1 |

| Синхронный делитель частоты по модулю 2 @ -1 | 1985 |

|

SU1298903A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Устройство для допускового контроля длительности последовательности временных интервалов | 1988 |

|

SU1647508A1 |

| Формирователь разностной частоты импульсных последовательностей | 1985 |

|

SU1307567A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, вычислительной и измерительной техники. Цель изобретения - повышение быстродействия при одновременном упрощении. Счетчик по модулю 5 содержит входную шину 1, Д-триггеры 2, 3, 4 и выходную шину 5. В счетчике по модулю 5 быстродействие повышено за счет исключения задержек распространения сигналов в межтриггерных связях. 2 ил.

Составитель К.Ранов Редактор А.Лежнина Техред М.Дидык Корректор М.Циткина

Заказ 2558/56

Тираж 885

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Синхронный делитель частоты следования импульсов на 5 | 1983 |

|

SU1145476A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Тарабрин Б.В | |||

| и др | |||

| Справочник по интегральным микросхемам | |||

| К.: Энер- гия, 1980, с | |||

| ПРИСПОСОБЛЕНИЕ ПРОТИВ УГОНА РЕЛЬСОВ | 1923 |

|

SU708A1 |

Авторы

Даты

1989-05-15—Публикация

1987-10-01—Подача