1

Изобретение относится к импульсной технике и может использоваться в

to

15

скоростных трактах деления частоты, например, синтезаторов частот.

Цель изобретения - повьшение симметричности выходного сигнала.

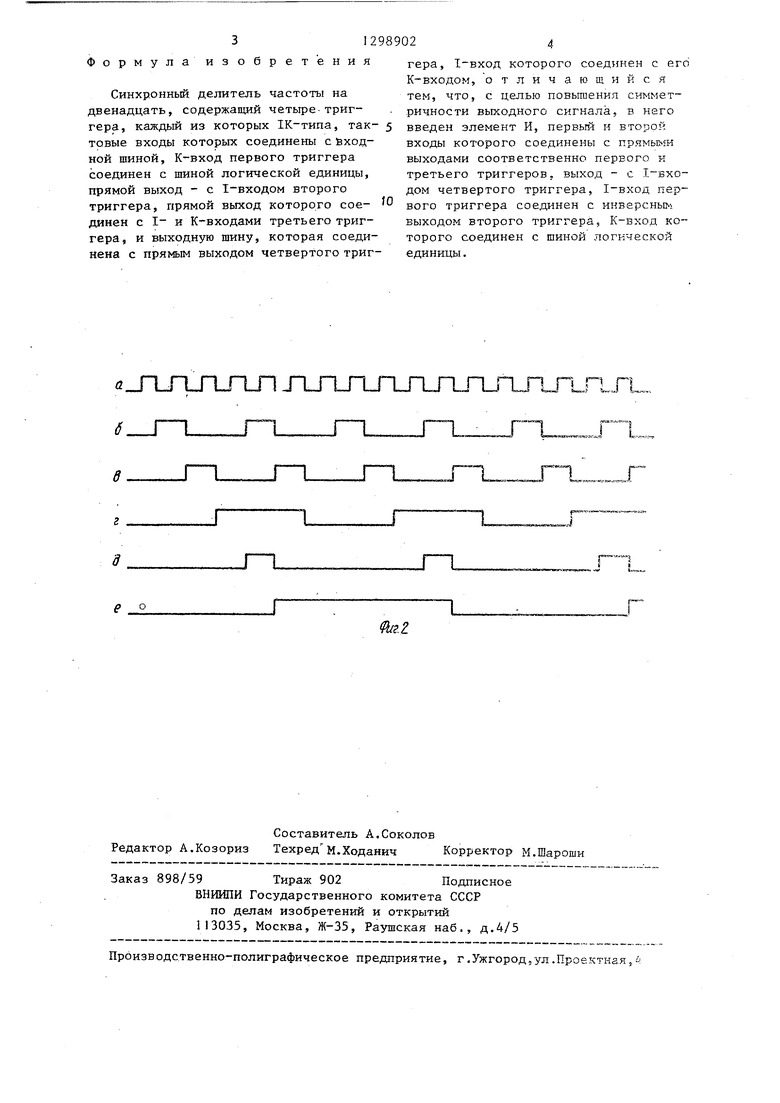

На фиг.1 показана электрическая функциональная схема синхронного делителя частоты на двенадцать; на фиг.2 - временные диаграммы, поясняющие его работу.

Синхронный делитель частоты на двенадцать содержит входную шину 1, соединенную с тактовыми входами первого 2, второго 3, третьего 4 и четвертого 5 триггеров, каждый из которых 1К-типа, К-вход первого триггера 2 соединен с шиной логической еди-. ницы, а прямой выход - с 1-входом второго триггера 3, К-вход которого соединен с шиной, логической единицы, а прямой выход подключен к 1-й К-вхо- дам третьего триггера 4, инверсный выход второго триггера 3 соединен с 1-входом первого триггера 2; 1-й К-входы четвертого триггера 5 соединены с выходом элемента И 6, первый и второй входы которого подключены к прямым выходам соответственно первого 2 и третье го 4 триггеров, выход четвертого триггера 5 соединен с выходной шиной 7.

Синхронный делитель частоты на двенадцать работает следующим образом. На шину 1 поступают входные импульсы (фиг.1а). Пусть в исходном состоянии все триггеры находятся в нулевом состоянии. Тогда спадом первого входного импульса триггер 2 переключается в единичное состояние (фиг.2б), а спадом второго входного импульса триггер 3 переключается в единичное состояние (фиг.2в), а триггер 2 - в нулевое, поскольку триггер 2 в этот момент находится в единичном состоянии и на его I- и К-входах присутствует уровень логической, единицы, д триггер 3 находится в нулевом состоянии и на его I- и К-входах также присутствует уровень логической единицы. Спадом третьего входного импульса на выход триггера 3 записывается уровень логического нуля с выхода триггера 2, при этом одновременно в единичное состояние переключается триггер 4 (фиг.2г).

Далее четвертым тактовым импульсом в единичное состояние переключа20

25

12989022

ется триггер 2 и одновременно на выходе элемента И 6 появляется уровень логической единицы (длительностью в один период входных импульсов). Спадом пятого входного импульса триггер 2 возвращается в исходное состояние и на выходе элемента И 6 появляется уровень логического нуля (фиг.2д). Одновременно (в момент спада пятого входного импульса) уровень логической единицы с выхода элемента 6 поступает на I- и К-входы триггера 5 и он переключается в единичное состояние (фиг.2е). В единичное состояние переключается и триггер 3 (фиг.2в). В момент спада шестого входного импульса в исходное (нулевое) состояние переключаются триггеры 3 и 4 (фиг.2в,г) при этОм состояние триггера 5 не изменяется, поскольку на его I- и К- входах действует уровень логического нуля. Спадом седьмого входного импульса в едиТничное состояние переключается триггер 2. Спадом восьмого входного импульса триггер 2 переключается в нулевое, а триггер 3 - в единичное состояние. Спадом девятого входного импульса триггер 3 переключается в нулевое состояние, а триггер 4 - в единичное. Спадом десятого входного импульса в единичное состояние переключается триггер 2 и на выходе элемента 6 появляется фронт его второго импульса (фиг.2д).Спадом одиннадцатого входного импульса триггер 2 переключается в нулевое состояние, триггер 4 сохраняет свое предыдущее единичное состояние, поскольку на его I- и К-входах в этот момент действуют уровни логического нуля; уровень логической единицы действует на I- и К-входы триггера 5, который переключается спадом одиннадцатого тактового импульса в нулевое состояние (фиг.2е). Спадом двенадцатого тактового импульса все триггеры устройства возвращаются в исходное (нулевое) состояние.

Таким образом, на выходах триггеров 4 и 5 имеются симметричные импульсы, при этом обеспечивается коэффициент деления на шесть и на двенадцать соответственно. На выходах триггеров 2 и 3 имеются импульсы, длительность которых равна длительности периода входной частоты, при этом обеспечивается коэффициент деления на три.

30

35

40

45

50

55

Формула изобретения

Синхронньй делитель частоты на двенадцать, содержащий четыре-триггера, каждый из которых 1К-типа, так- товые входы которых соединены с йход- ной шиной, К-вход первого триггера соединен с шиной логической единицы, прямой выход - с 1-входом второго триггера, прямой выход которого сое- динен с I- и К-входами третьего триггера, и выходнзпо шину, которая соединена с прямым выходом четвертого тригaJ-lTLTLrin J inJ-lJ lJ J lJ-lJ

J-L

в

гера, 1-вход которого соединен с его К-входом, отличающийся тем, что, с целью повышения симметричности выходного сигнала, в него введен элемент И, первый и второй входы которого соединены с прямы 5К выходами соответственно первого и третьего триггеров, выход - с дом четвертого триггера, 1-вход первого триггера соединен с инверсным выходом второго триггера, К-вход которого соединен с шиной логической единицы.

J™1

ГЛ.

..™.„..Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на десять | 1985 |

|

SU1298901A1 |

| Синхронный делитель частоты по модулю 2 @ -1 | 1985 |

|

SU1298903A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Программируемый делитель частоты | 1985 |

|

SU1298899A1 |

| Делитель частоты следования импульсов | 1985 |

|

SU1243128A1 |

| Счетчик по модулю 5 | 1987 |

|

SU1480119A1 |

| Синхронный делитель частоты | 1986 |

|

SU1322469A1 |

| Формирователь разностной частоты импульсных последовательностей | 1985 |

|

SU1307567A1 |

| Синхронный делитель частоты | 1988 |

|

SU1555854A2 |

| Кольцевой делитель частоты по модулю 2 @ -1 | 1982 |

|

SU1133665A1 |

Изобретение относится к импульсной технике и может быть использовано в скоростных трактах деления частоты, например синтезаторах частоты. Целью изобретения является повышение симметричности выходного сигнала. Устройство содержит входную шину 1,три1- геры 2 - 5 1К-типа. Для достижения поставленной цели в устройство введен элемент И 6. Устройством обеспечивается деление частоты с коэффициентами деления на три, шесть и двенадцать. Работа устройства поясняется временными диаграммами, приведен- , ными в описании изобретения. 2 ил. (Л iT i дыкод 7 я - rf

| Пересчетная декада | 1982 |

|

SU1022311A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Справочник по интегральным микросхемам | |||

| /Под ред | |||

| Б.В.Тарабрина | |||

| М.-: Энергия, 1980, с .7 11, рис.5-206 | |||

| ЛоН Ь / | |||

Авторы

Даты

1987-03-23—Публикация

1985-11-04—Подача