Изобретение относится к импульсной т ехнике и может быть использовано -в трактах деления частоты, например, в вычислитепьной технике, цифровых синтезаторах частот.

Цель изобретения - повьшение быстродействия при одновременном расширении функциональных возможностей за счет организации сигнала Перенос.

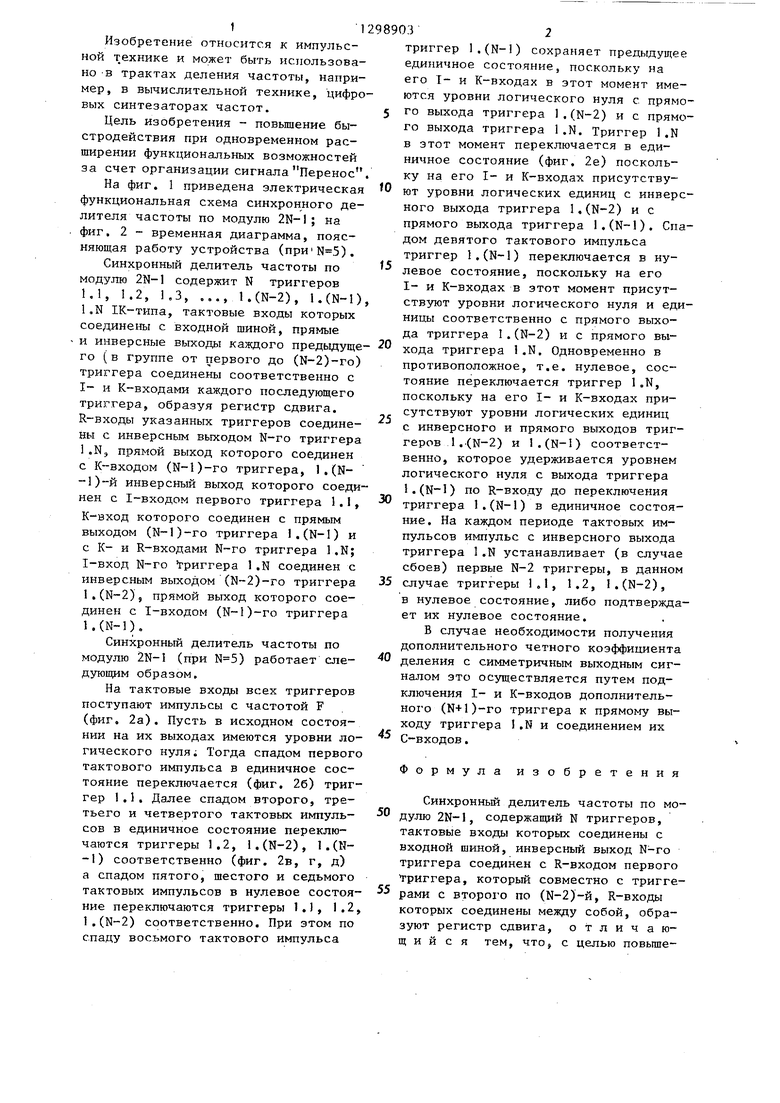

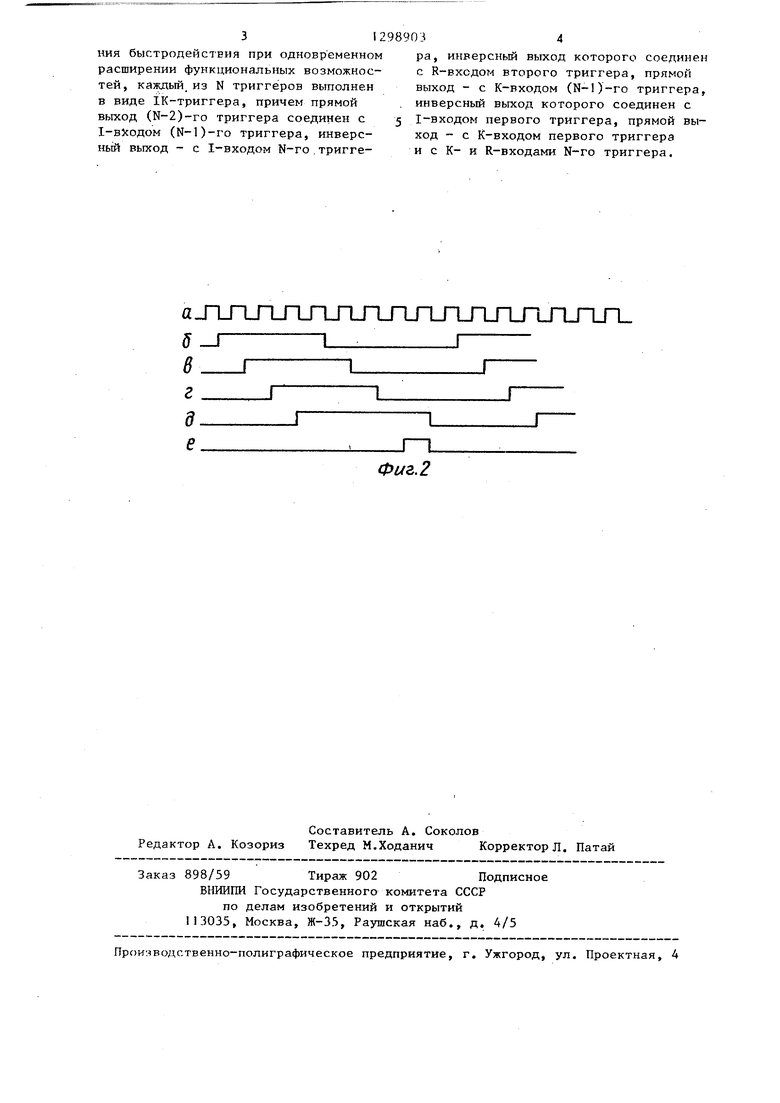

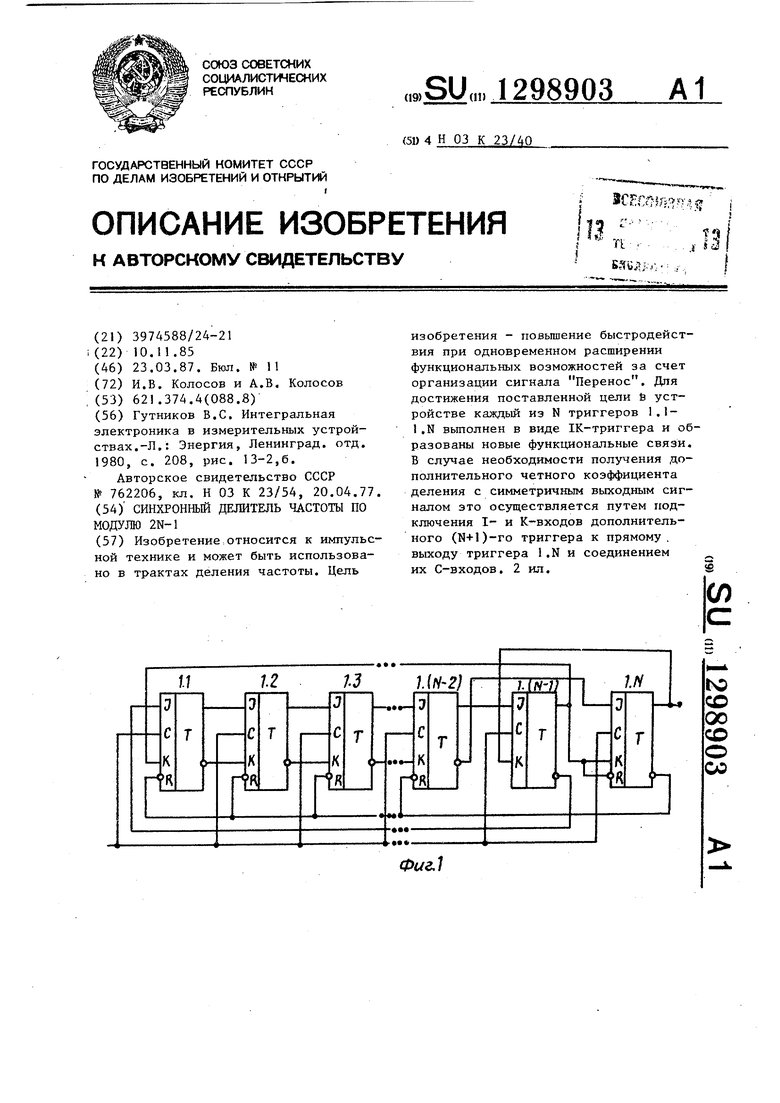

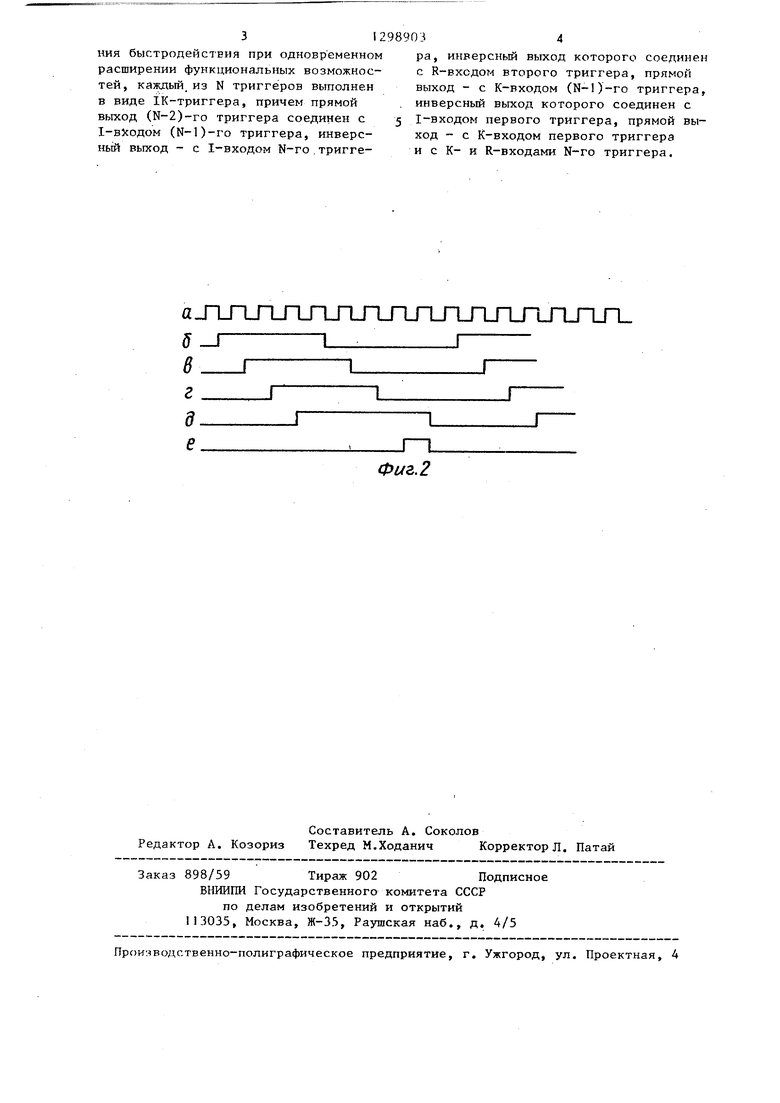

На фиг, 1 приведена электрическая функциональная схема синхронного делителя частоты по модулю 2N-1; на фиг. 2 - временная диаграмма, поясняющая работу устройства (при N 5).

Синхронный делитель частоты по моду.то 2N-1 содержит N триггеров 1,1, 1.2, 1.3, ,.., l.(N-2), l.(N-l), l.N IK-типа, тактовые входы которых соединены с входной шиной, прямые

fO

f5

триггер l.(N-l) сохраняет предыдущее единичное состояние, поскольку на его Т- и К-входах в этот момент имеются уровни логического нуля с прямого выхода триггера 1.(N-2) и с прямого выхода триггера 1.N. Триггер 1,N в этот момент переключается в единичное состояние (фиг. 2е) поскольку на его I- и К-входах присутствуют уровни логических единиц с инверсного выхода триггера l,(N-2) и с прямого выхода триггера 1,(N-), Спадом девятого тактового импульса триггер l.(N-l) переключается в нулевое состояние, поскольку на его I- и К-входах в этот момент присутствуют уровни логического нуля и единицы соответственно с прямого выхода триггера l.(N-2) и с прямого вы25

и инверсные выходы каждого предьщуще- 20 д триггера l.N. Одновременно в

го (в группе от первого до (N-2)-ro)

триггера соединены соответственно с

I- и К-входами каждого последующего

триггера, образуя регистр сдвига,

К входы указанных триггеров соединены с инверсным выходом N-ro триггера

1.N, прямой выход которого соединен

с К-входом (N-l)-ro триггера, 1,()й инверсный выход которого соединен с 1-входом первого триггера 1.1,

К-вход которого соединен с прямым

выходом (N-l)-ro триггера 1,(N-1) и с К- и R-входами N-ro триггера 1,N; 1-вход N-ro триггера 1 .N соединен с инверсным выходом (N-2)-ro триггера l.(N-2), прямой выход которого соединен с 1-входом (N-l)-ro триггера l.(N-l).

Синхронный делитель частоты по модулю 2N-I (при ) работает следующим образом.

На тактовые входы всех триггеров поступают импульсы с частотой F (фиг, 2а). Пусть в исходном состоянии на их выходах имеются уровни логического нуля; Тогда спадом первого тактового импульса в единичное состояние переключается (фиг, 2б) триггер 1,1, Далее спадом второго, третьего и четвертого тактовых импульсов в единичное состояние переключаются триггеры 1,2, 1,(N-2), 1,(N- -1) соответственно (фиг, 2в, г, д) а спадом пятого, шестого и седьмого

противоположное, т,е, нулевое, состояние переключается триггер 1,N, поскольку на его I- и К-входах присутствуют уровни логических единиц с инверсного и прямого выходов триггеров 1 ,.(N-2) и .(N-I) соответственно, которое удерживается уровнем логического нуля с выхода триггера 1,(N-1) по R-входу до переключения триггера ,(N-1) в единичное состояние. На каждом периоде тактовых импульсов импульс с инверсного выхода триггера I,N устанавливает (в случае сбоев) первые N-2 триггеры, в данном 35 случае триггеры 1,1, 1,2, l,(N-2), в нулевое состояние, либо подтверждает их нулевое состояние,

В случае необходимости получения дополнительного четного коэффициента деления с симметричным выходным сигналом это осуществляется путем подключения I- и К-входов дополнительного (К+1)-го триггера к прямому выходу триггера 1,N и соединением их

40

45

С-входов,

Формула изобретения

Синхронный делитель частоты по мо- 5 дулю 2N-1, содержащий N триггеров, тактовые входы которых соединены с входной шиной, инверсный выход N-ro триггера соединен с R-входом первого триггера, которьй совместно с триггетактовых импульсов в нулевое состоя- 5 рами с второго по (N-2)-й, К-входы ние переключаются триггеры 1,1, I«2, которых соединены между собой, обра- l,(N-2) соответственно. При этом по зуют регистр сдвига, отличаю- спаду восьмого тактового импульса щ и и с я тем, что, с целью повьше

триггер l.(N-l) сохраняет предыдущее единичное состояние, поскольку на его Т- и К-входах в этот момент имеются уровни логического нуля с прямого выхода триггера 1.(N-2) и с прямого выхода триггера 1.N. Триггер 1,N в этот момент переключается в единичное состояние (фиг. 2е) поскольку на его I- и К-входах присутствуют уровни логических единиц с инверсного выхода триггера l,(N-2) и с прямого выхода триггера 1,(N-), Спадом девятого тактового импульса триггер l.(N-l) переключается в нулевое состояние, поскольку на его I- и К-входах в этот момент присутствуют уровни логического нуля и единицы соответственно с прямого выхода триггера l.(N-2) и с прямого триггера l.N. Одновременно в

5

противоположное, т,е, нулевое, состояние переключается триггер 1,N, поскольку на его I- и К-входах присутствуют уровни логических единиц с инверсного и прямого выходов триггеров 1 ,.(N-2) и .(N-I) соответственно, которое удерживается уровнем логического нуля с выхода триггера 1,(N-1) по R-входу до переключения триггера ,(N-1) в единичное состояние. На каждом периоде тактовых импульсов импульс с инверсного выхода триггера I,N устанавливает (в случае сбоев) первые N-2 триггеры, в данном 5 случае триггеры 1,1, 1,2, l,(N-2), в нулевое состояние, либо подтверждает их нулевое состояние,

В случае необходимости получения дополнительного четного коэффициента деления с симметричным выходным сигналом это осуществляется путем подключения I- и К-входов дополнительного (К+1)-го триггера к прямому выходу триггера 1,N и соединением их

0

5

С-входов,

Формула изобретения

Синхронный делитель частоты по мо- дулю 2N-1, содержащий N триггеров, тактовые входы которых соединены с входной шиной, инверсный выход N-ro триггера соединен с R-входом первого триггера, которьй совместно с триггерами с второго по (N-2)-й, К-входы которых соединены между собой, обра- зуют регистр сдвига, отличаю- щ и и с я тем, что, с целью повьшения быстродействия при одновременном расширении функциональных возможностей, каждый, из N триггеров выполнен в виде 1К-тригге.ра, причем прямой выход (N-2)-ro триггера соединен с 1-вХодом (N-l)-ro триггера, инверсный выход - с 1-входом N-ro,триггеа JlJnJlJnjnJlJlJljaJlJl д -1I I

в -Jт.I

г1If

д11

е.

Редактор А. Козориз

Составитель А. Соколов

Техред М.Ходанич Корректор Л. Патай

Заказ 898/59 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Прс)и;1водственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

ра, инверсный выход которого соединен с R-вхсдом второго триггера, прямой выход - с К-входом (N-)-ro триггера, инверсный выход которого соединен с 1-входом первого триггера, прямой выход - с К-входом первого триггера и с К- и R-входами N-ro триггера.

.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на десять | 1985 |

|

SU1298901A1 |

| Синхронный делитель частоты на двенадцать | 1985 |

|

SU1298902A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Кольцевой делитель частоты по модулю 2 @ -1 | 1982 |

|

SU1133665A1 |

| Синхронный делитель частоты | 1988 |

|

SU1555854A2 |

| Формирователь разностной частоты импульсных последовательностей | 1985 |

|

SU1307567A1 |

| Программируемый делитель частоты | 1985 |

|

SU1298899A1 |

| Счетчик по модулю 5 | 1987 |

|

SU1480119A1 |

| Синхронный делитель частоты | 1986 |

|

SU1322469A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

Изобретение относится к импульсной технике и может быть использовано в трактах деления частоты. Цель изобретения - повьппение быстродействия при одновременном расширении функциональных возможностей за счет организации сигнала Перенос. Для достижения поставленной цели fe устройстве каждый из N триггеров 1.1- 1.N вьтолнен в виде 1К-триггера и образованы новые функциональные связи. В случае необходимости получения дополнительного четного коэффициента деления с симметричным выходным сигналом это осуществляется путем подключения I- и К-входов дополнительного (N+l)-ro триггера к прямому, выходу триггера 1.N и соединением их С-входов. 2 ил. (С (Л Фиг.1

| Гутников B.C | |||

| Интегральная электроника в измерительных устройствах | |||

| -Л.: Энергия, Ленинград, отд | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Гидравлическая или пневматическая передача | 0 |

|

SU208A1 |

| Насос | 1917 |

|

SU13A1 |

| Авторское свидетельство СССР № 762206, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1985-11-10—Подача