м н

(-3

Z-1

2-t

М..|о15)1

П-1

4

00

со со

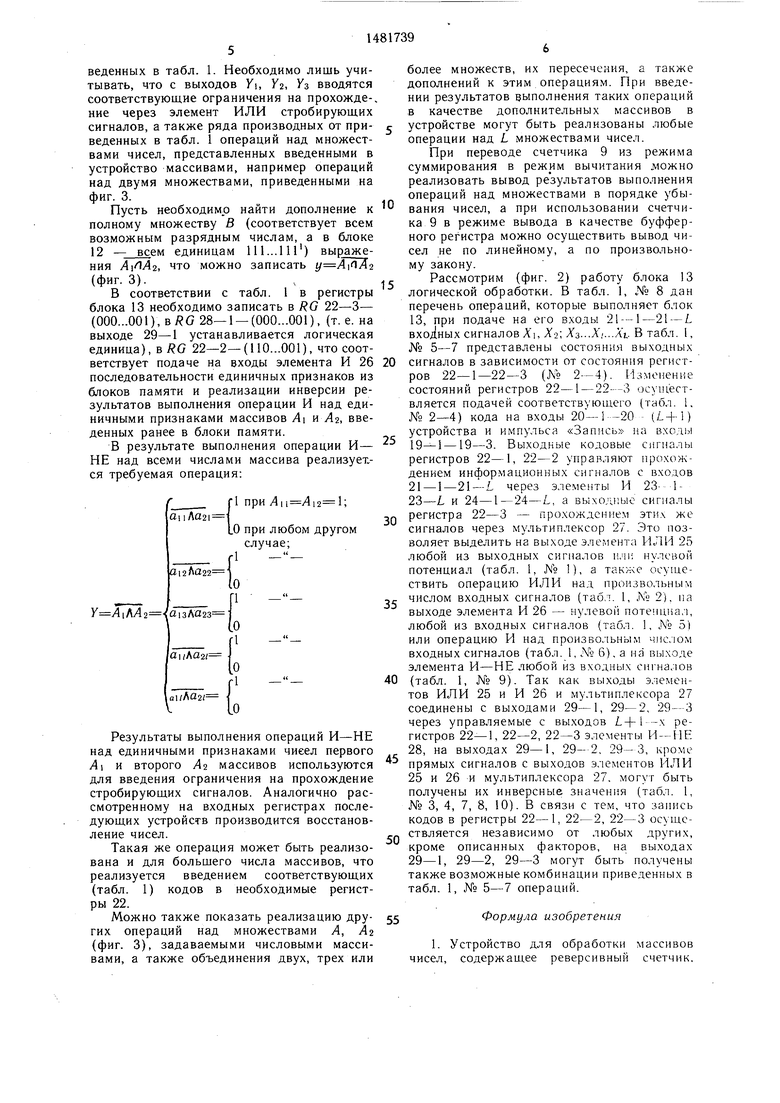

Изобретение относится к области вычислительной техники и может использоваться при построении систем сбора и обработки информации, представленной числовыми массивами, например, в цифровых устройствах обработки изображений.

Целью изобретения является расширение функциональных возможностей устройства за счет выполнения операций объединения, пересечения и дополнения над L-мно- жествами.

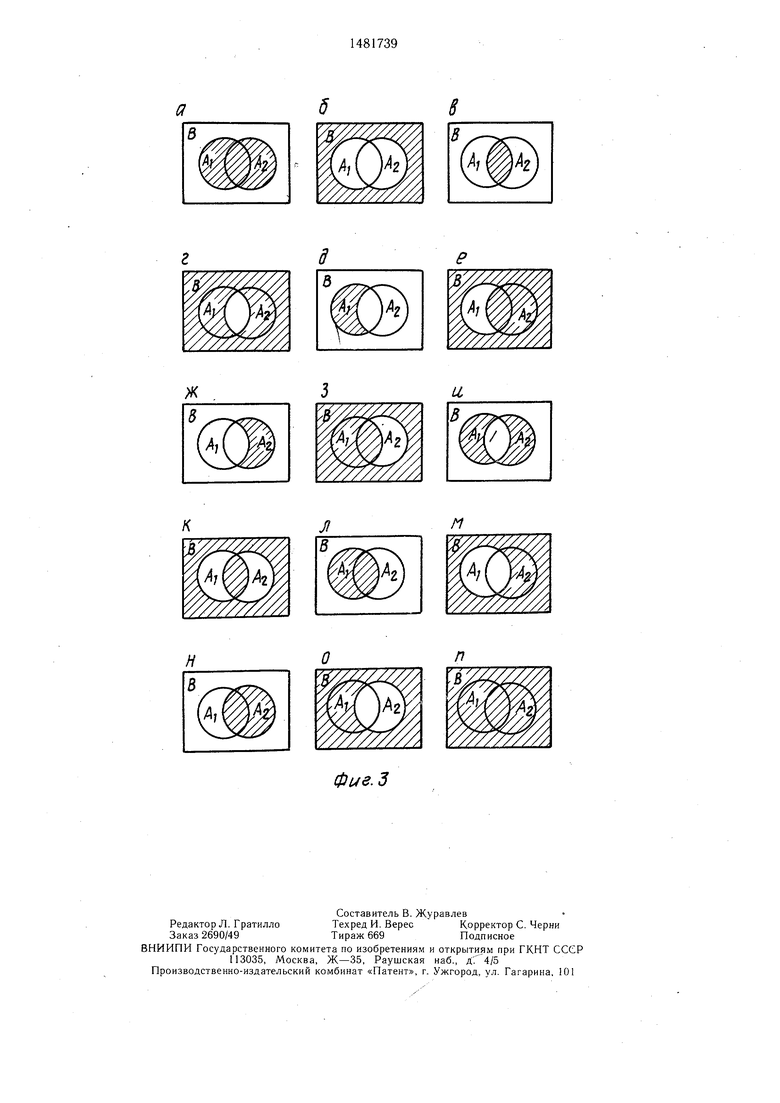

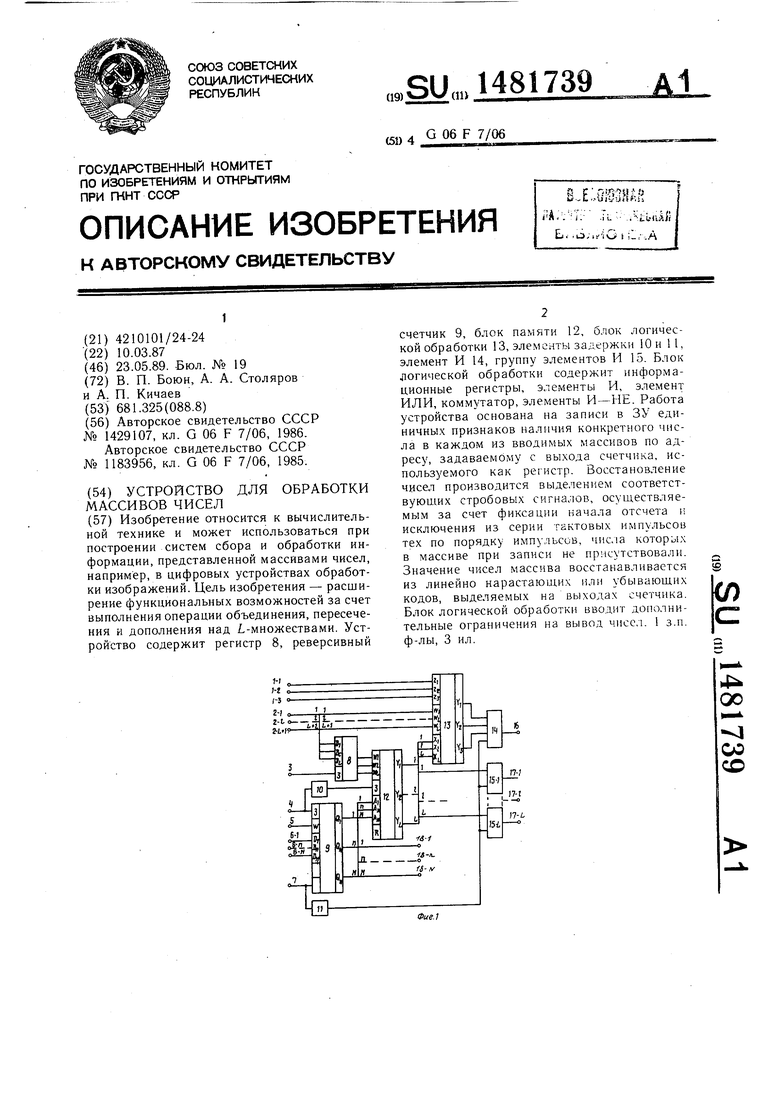

На фиг. 1 дана схема устройства для обработки массивов чисел; на фиг. 2 - схема блока логической обработки; на фиг. 3 - графическое изображение операции над двумя множествами.

Устройство для обработки массивов чисел (фиг. 1) содержит входы 1 - 1 -1-3 записи режимов устройства, входы 2-1-2 - (L + 1) задания режимов устройства, обеспечивающие возможность изменения функций, вход 3 записи режима работы блока памяти, позволяющий устанавливать его в режим записи любого из L массивов и его перевод в режим вывода информации, вход 4 записи чисел массива, вход 5 управления режимом вывода в порядке нарастания или

Элементы И 14 и 15-1 -15-L предназначены для получения стробирующих сигналов, с помощью которых осуществляется выборка результатов обработки из нарастающей или убывающей последовательности кодовых сигналов с выходов счетчика 9 в режиме вывода.

Пусть, например, требуется в одно внешнее устройство ввести в порядке возрастания /-и инверсный упорядоченный массив, а

10 в последующие L устройств в порядке возрастания - упорядоченные массивы, начиная с 1-го по L-ый.

В таком случае реверсивный счетчик 9 устанавливается единичным потенциалом в

с режим суммирования и нулевое начальное состояние (по цепи сброс) и в соответствии с табл. 1 обеспечивается следующий вариант установки кодов регистров: 22-1 - 000...0...001, 22-2-000...0...001, 22-3- 000...1...001.

20 С подачей тактовых импульсов на вход 7 реверсивный счетчик 9 обеспечивает линейное считывание записанных в блок 12 единичных признаков наличия чисел в ранее вводимых массивах. В том случае, если при записи массива число присутствовало на выубывания чисел, информационные входы 2 ходе блока 12, устанавливается логическая 6-1-6-N, тактовый вход 7, регистр 8,единица, если же нет - логический нуль,

реверсивный счетчик 9, элементы 10 и 11 за-Таким образом, на выходах 18-1 -18-N

держки, блок 12 памяти, блок 13 логичес-устройства выделяется линейно нарастаюкой обработки, элемент И 14, группу из Lщая последовательность возможных варианэлементов И 15-1 -15-L, стробирующий JQ тов N разрядных кодов, а на выходах (L + 1)-и выход 16, стробирующие выходы 17,блока 12 выделяется информация о присутс первого по L-й информационные выходы 18-1 - 18-/V

Блок 13 логической обработки содержит входы «Запись регистров 19-1 - 19-3,

ствии каждого числа в ранее вводимом массиве, что позволяет получить из последовательности тактовых импульсов на входе 7 соответствующий стробирующий сигнал на

входы 20-1-20-(L+1) задания режимов 35 выходах элементов И 15-1 -15-L, с по- блока, входы 21 - 1-21-L, информационные регистры 22-1-22-3 элементы И 23- 1-23-L и 24-1-24-L, элемент ИЛИ 25, элемент И 26, коммутатор 27, элементы И- НЕ 28-1, 28-2, 28-3, выходы 29- 1, 29-2,

мощью которого можно осуществить восстановление из кодов на выходе счетчика 9 каждого из чисел. Это реализуется на входных регистрах внешних для процессора устройств, в которые в соответствии со стро29-3 соответственно реализации функций 40 бирующими сигналами записываются выход- ИЛИ либо ИЛИ-НЕ, И либо И-НЕ и вы-ные коды счетчика 9.

деления одного из записанных в блоке 12 массивов.

Устройство для обработки массивов чисел работает следующим образом.

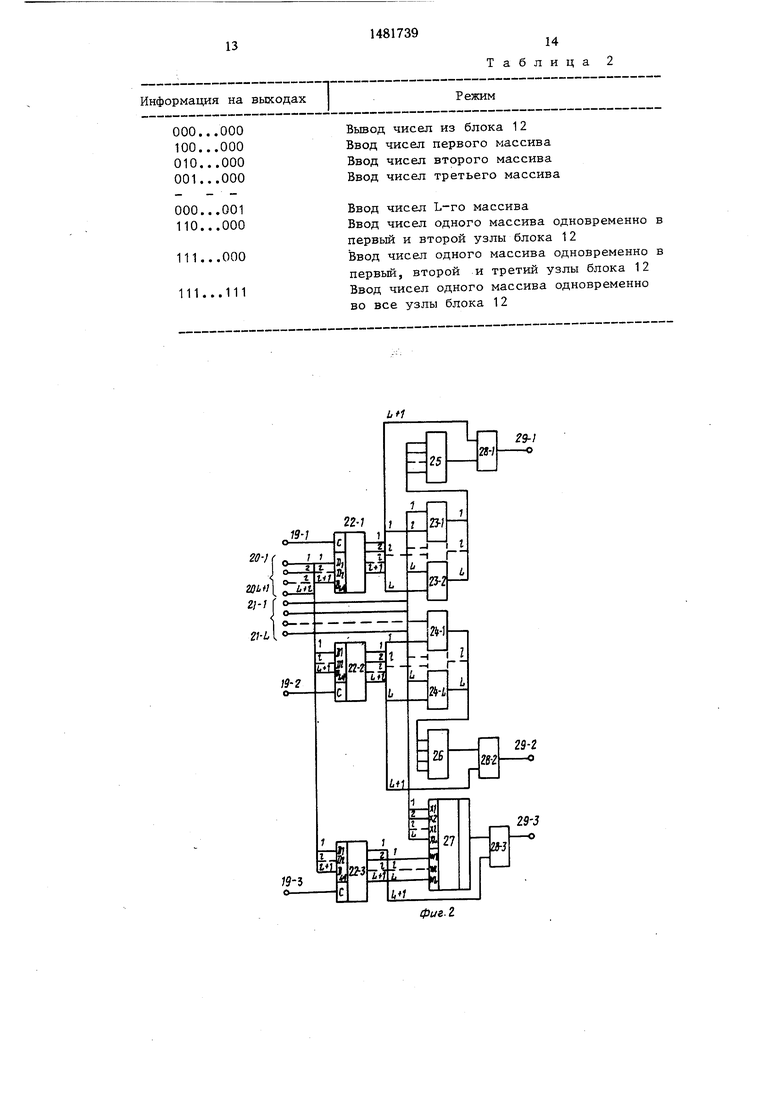

Регистр 8 служит для задания режима работы блока 12 памяти в соответствии с табл. 2.

Изменение режимов работы процессора производится записью требуемого кода в регистр 8.50 сигнала на вход «Запись, например, вход- Реверсивный счетчик 9 используется вного регистра внешнего устройства на Dтриггерах, информационные входы которого подключены к информационным выходам 18-1 -18-Л устройства так же, как и в предыдущем случае, происходит восстанов- 55 ление чисел массива по стробирующим сигналам.

Аналогично можно рассмотреть работу устройства при реализации функций, приТак как на выходах блока 13 в соответствии с табл. 1 выделяются следующие значения: 29-1-«1 ; 29-2-«1 ; 45 29-3-X/, то на выходе 16 стробирующие сигналы появятся в соответствии с изменением инверсного значения единичных признаков последовательности, записанной ранее в блок памяти.

При подаче выходного 16 стробирующего

качестве буфферного регистра при вводе массивов в процессор и в качестве развертывающего и восстанавливающего числа массивов устройства при выводе информации.

Элементы 10 и 11 задержки предназначены для согласования во времени внутренних сигналов устройства.

Элементы И 14 и 15-1 -15-L предназначены для получения стробирующих сигналов, с помощью которых осуществляется выборка результатов обработки из нарастающей или убывающей последовательности кодовых сигналов с выходов счетчика 9 в режиме вывода.

Пусть, например, требуется в одно внешнее устройство ввести в порядке возрастания /-и инверсный упорядоченный массив, а

0 в последующие L устройств в порядке возрастания - упорядоченные массивы, начиная с 1-го по L-ый.

В таком случае реверсивный счетчик 9 устанавливается единичным потенциалом в

с режим суммирования и нулевое начальное состояние (по цепи сброс) и в соответствии с табл. 1 обеспечивается следующий вариант установки кодов регистров: 22-1 - 000...0...001, 22-2-000...0...001, 22-3- 000...1...001.

0 С подачей тактовых импульсов на вход 7 реверсивный счетчик 9 обеспечивает линейное считывание записанных в блок 12 единичных признаков наличия чисел в ранее вводимых массивах. В том случае, если при записи массива число присутствовало на вы ходе блока 12, устанавливается логическая единица, если же нет - логический нуль,

ствии каждого числа в ранее вводимом массиве, что позволяет получить из последовательности тактовых импульсов на входе 7 соответствующий стробирующий сигнал на

выходах элементов И 15-1 -15-L, с по-

сигнала на вход «Запись, например, вход- ного регистра внешнего устройства на DТак как на выходах блока 13 в соответствии с табл. 1 выделяются следующие значения: 29-1-«1 ; 29-2-«1 ; 29-3-X/, то на выходе 16 стробирующие сигналы появятся в соответствии с изменением инверсного значения единичных признаков последовательности, записанной ранее в блок памяти.

При подаче выходного 16 стробирующего

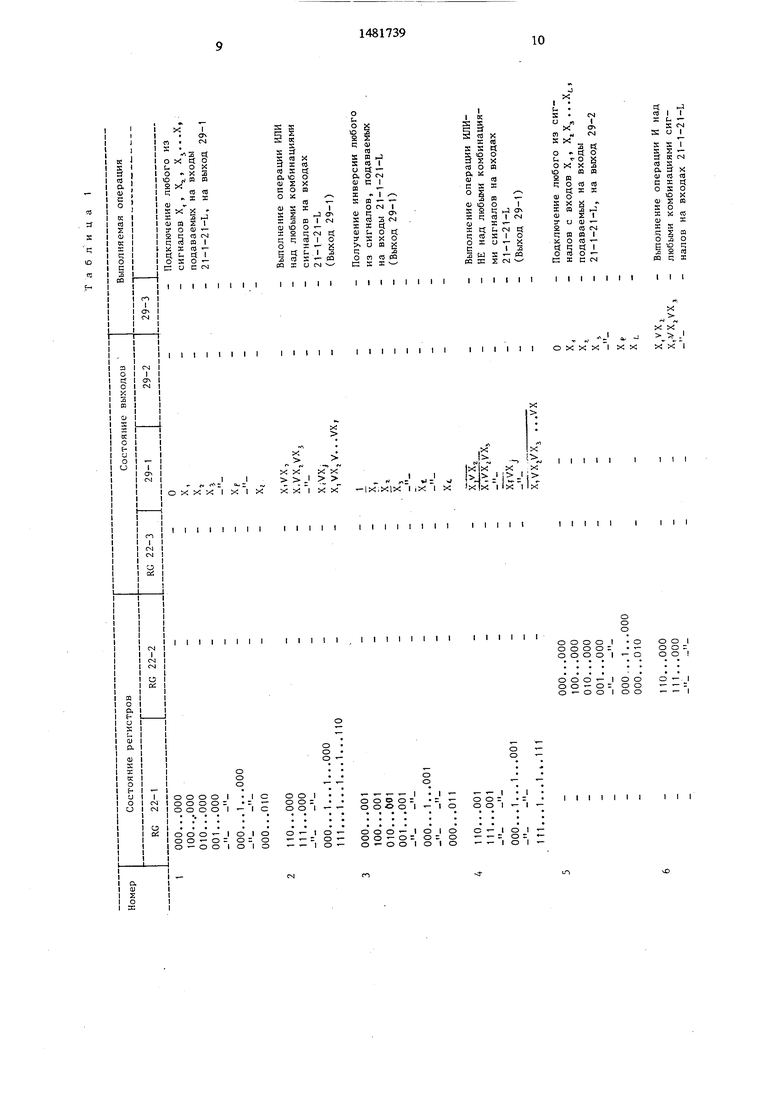

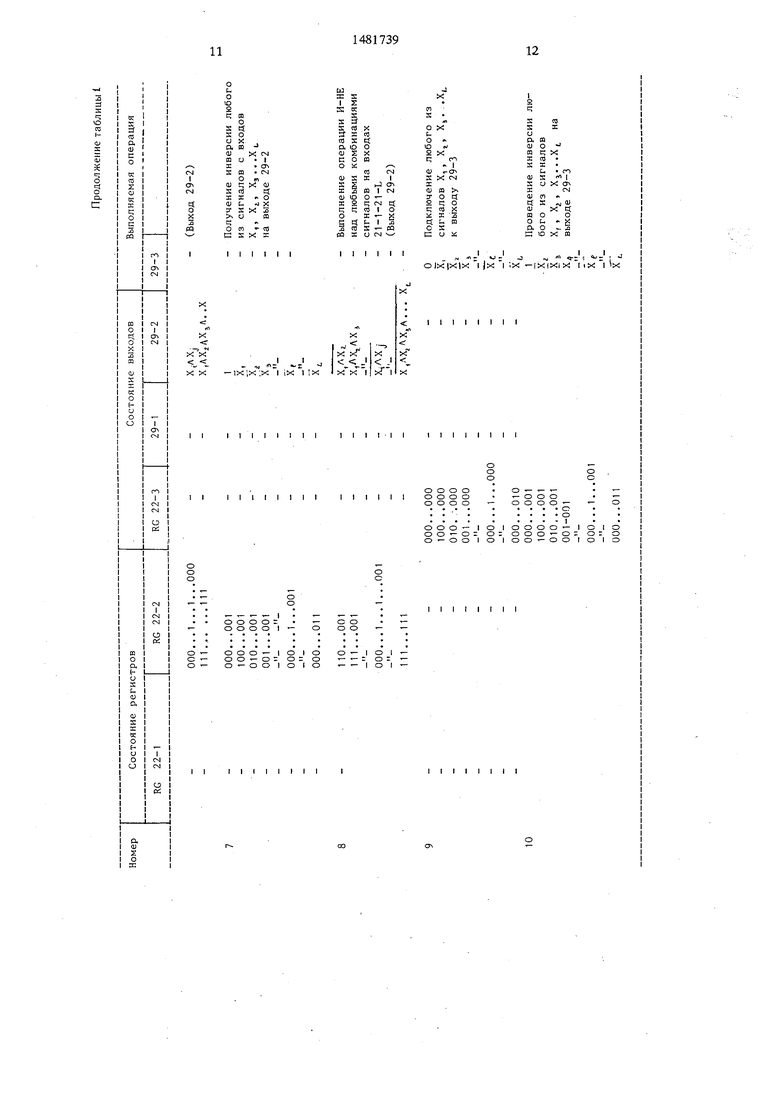

веденных в табл. 1. Необходимо лишь учитывать, что с выходов УЬ У2, Уз вводятся соответствующие ограничения на прохождение через элемент ИЛИ стробирующих сигналов, а также ряда производных от приведенных в табл. 1 операций над множествами чисел, представленных введенными в устройство массивами, например операций над двумя множествами, приведенными на фиг. 3.

более множеств, их пересечения, а также дополнений к этим операциям. При введении результатов выполнения таких операций в качестве дополнительных массивов в устройстве могут быть реализованы любые операции над L множествами чисел.

При переводе счетчика 9 из режима суммирования в режим вычитания .можно реализовать вывод результатов выполнения операций над множествами в порядке убыПусть необходимо найти дополнение к вания чисел, а при использовании счетчи15

полному множеству В (соответствует всем возможным разрядным числам, а в блоке 12 - всем единицам 111...1111) выраже- ния , что можно записать г/ Л|1Д2 (фиг. 3).

В соответствии с табл. 1 в регистры блока 13 необходимо записать в RG 22-3- (000...001), BRG 28-1 -(000...001), (т.е. на выходе 29-1 устанавливается логическая единица), в RG 22-2-(110...001), что соответствует подаче на входы элемента И 26 20 сигналов в зависимости от состояния регис г- последовательности единичных признаков изров 22-1-22-3 (Л° 2--4). Изменение

блоков памяти и реализации инверсии ре-состояний регистров 22-1 - 22--3 ис щестзультатов выполнения операции И над еди-вляется подачей соответствующего (габл. 1,

№ 2-4) кода на входы 20-1 -20 (L41)

ка 9 в режиме вывода в качестве буффер- ного регистра можно осуществить вывод чисел не по линейному, а по произвольному закону.

Рассмотрим (фиг. 2) работу блока 13 логической обработки. В табл. 1, № 8 дан перечень операций, которые выполняет блок 13, при подаче на его входы 21---1-21 - L входных сигналов А ь Xi Хз..-Xt...Xi.. В табл. I, № 5-7 представлены состояния выходных

ничными признаками массивов А и Аг, введенных ранее в блоки памяти.

В результате выполнения операции И- НЕ над всеми числами массива реализуемся требуемая операция:

25

устройства и импульса «Запись на вхош 19-1 -19-3. Выходные кодовые сигналы регистров 22-1, 22-2 управляют прохождением информационных сигналов с входов 21 - 1-21-L через элементы И 23 1- 23-L и 24-1-24-L, а выходные сигналы регистра 22-3 - прохождением этих же сигналов через мультиплексор 27. Это позволяет выделить на выходе элемента ИЛИ 25 любой из выходных сигналов или нулевой потенциал (табл. 1. № I), а так.е осуществить операцию ИЛИ над произвольным числом входных сигналов (таб т 1, К° 2), па выходе элемента И 26 - нулевой потенциал, любой из входных сигналов (табл. 1, Л° 5| или операцию И над произвольным числом входных сигналов (табл. 1, ЛГ9 6), а на выходе элемента И-НЕ любой из входных cm налов (табл. 1, № 9). Так как выходы элементов ИЛИ 25 и И 26 и мультиплексора 27 соединены с выходами 29-1, 29-2, 29-3 через управляемые с выходов L+I -х регистров 22-1, 22-2, 22-3 элементы И- НЕ 28, на выходах 29-1, 29--2. 29-3, кроме

ai2Aa22 1

Л,ЛЛ2

ОцЛа21

-С

1 при

при любом другом случае;

ачЛи21

ai/Aa2;

rl - -

О

j «

.0

о

о

Результаты выполнения операций И-НЕ над единичными признаками чисел первого

устройства и импульса «Запись на вхош 19-1 -19-3. Выходные кодовые сигналы регистров 22-1, 22-2 управляют прохождением информационных сигналов с входов 21 - 1-21-L через элементы И 23 1- 23-L и 24-1-24-L, а выходные сигналы регистра 22-3 - прохождением этих же сигналов через мультиплексор 27. Это позволяет выделить на выходе элемента ИЛИ 25 любой из выходных сигналов или нулевой потенциал (табл. 1. № I), а так.е осуществить операцию ИЛИ над произвольным числом входных сигналов (таб т 1, К° 2), па выходе элемента И 26 - нулевой потенциал, любой из входных сигналов (табл. 1, Л° 5| или операцию И над произвольным числом входных сигналов (табл. 1, ЛГ9 6), а на выходе элемента И-НЕ любой из входных cm налов (табл. 1, № 9). Так как выходы элементов ИЛИ 25 и И 26 и мультиплексора 27 соединены с выходами 29-1, 29-2, 29-3 через управляемые с выходов L+I -х регистров 22-1, 22-2, 22-3 элементы И- НЕ 28, на выходах 29-1, 29--2. 29-3, кроме

А и второго Аг массивов используются прямых сигналов с выходов элементов ИЛИ

25 и 26 и мультиплексора 27. могу г быть получены их инверсные значения (табл. 1, № 3, 4, 7, 8, 10). В связи с тем, что запись кодов в регистры 22-1, 22-2, 22-3 осуществляется независимо от любых других, кроме описанных факторов, на выходах 29-1, 29-2, 29-3 могут быть получены также возможные комбинации приведенных в табл. 1, № 5-7 операций.

для введения ограничения на прохождение стробирующих сигналов. Аналогично рассмотренному на входных регистрах последующих устройств производится восстановление чисел.

Такая же операция может быть реализована и для большего числа массивов, что реализуется введением соответствующих (табл. 1) кодов в необходимые регистры 22.

Можно также показать реализацию других операций над множествами А, Аг (фиг. 3), задаваемыми числовыми массивами, а также объединения двух, трех или

более множеств, их пересечения, а также дополнений к этим операциям. При введении результатов выполнения таких операций в качестве дополнительных массивов в устройстве могут быть реализованы любые операции над L множествами чисел.

При переводе счетчика 9 из режима суммирования в режим вычитания .можно реализовать вывод результатов выполнения операций над множествами в порядке убывания чисел, а при использовании счетчивания чисел, а при использовании счетчи

сигналов в зависимости от состояния регис г- ров 22-1-22-3 (Л° 2--4). Изменение

ка 9 в режиме вывода в качестве буффер- ного регистра можно осуществить вывод чисел не по линейному, а по произвольному закону.

Рассмотрим (фиг. 2) работу блока 13 логической обработки. В табл. 1, № 8 дан перечень операций, которые выполняет блок 13, при подаче на его входы 21---1-21 - L входных сигналов А ь Xi Хз..-Xt...Xi.. В табл. I, № 5-7 представлены состояния выходных

устройства и импульса «Запись на вхош 19-1 -19-3. Выходные кодовые сигналы регистров 22-1, 22-2 управляют прохождением информационных сигналов с входов 21 - 1-21-L через элементы И 23 1- 23-L и 24-1-24-L, а выходные сигналы регистра 22-3 - прохождением этих же сигналов через мультиплексор 27. Это позволяет выделить на выходе элемента ИЛИ 25 любой из выходных сигналов или нулевой потенциал (табл. 1. № I), а так.е осуществить операцию ИЛИ над произвольным числом входных сигналов (таб т 1, К° 2), па выходе элемента И 26 - нулевой потенциал, любой из входных сигналов (табл. 1, Л° 5| или операцию И над произвольным числом входных сигналов (табл. 1, ЛГ9 6), а на выходе элемента И-НЕ любой из входных cm налов (табл. 1, № 9). Так как выходы элементов ИЛИ 25 и И 26 и мультиплексора 27 соединены с выходами 29-1, 29-2, 29-3 через управляемые с выходов L+I -х регистров 22-1, 22-2, 22-3 элементы И- НЕ 28, на выходах 29-1, 29--2. 29-3, кроме

прямых сигналов с выходов элементов ИЛИ

прямых сигналов с выходов элементов ИЛИ

25 и 26 и мультиплексора 27. могу г быть получены их инверсные значения (табл. 1, № 3, 4, 7, 8, 10). В связи с тем, что запись кодов в регистры 22-1, 22-2, 22-3 осуществляется независимо от любых других, кроме описанных факторов, на выходах 29-1, 29-2, 29-3 могут быть получены также возможные комбинации приведенных в табл. 1, № 5-7 операций.

Формула изобретения

1. Устройство для обработки массивов чисел, содержащее реверсивный счетчик,

блок памяти, группу элементов И, причем информационные входы устройства соединены с информационным входом реверсивного счетчика, счетный вход которого соединен с тактовым входом устройства, вход «Запись устройства соединен с входом управления записью реверсивного счетчика, выходы разрядов которого соединены с адресными входами блока памяти, выходы которого соединены с первыми входами элементов И группы, вторые входы которых соединены между собой, выходы элементов И группы являются выходами устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операции объединения, пересечения и дополнения над L-множествами, в него введены регистр, блок логической обработки, два элемента задержки и элемент И, причем входы записи режимов устройства соединены с соответствующими входами записи режимов блока логической обработки, входы задания режимов которого соединены с входами задания режима устройства и с информационными входами регистра, выходы разрядов которого соединены с входами блока памяти, вход записи которого через первый элемент задержки соединен с входом «Запись устройства, выходы блока памяти подключены к информационным входам блока логической обработки, выходы которого соответственно соединены с первыми тремя входами элемента И, четвертый вход которого соединен с вторыми входами элементов И группы и через второй элемент задержки соединен с тактовым входом устройства, выходы элементов И группы яв0

5

ляются L-стробирующими выходами устройства, выход элемента И является (L + 1)-м стробирующим выходом устройства, выходы реверсивного счетчика являются информационными выходами устройства.

2. Устройство по п. 1, отличающееся тем, что блок логической обработки содержит три (L + 1)-разрядных регистра, первую и вторую группу элементов И по L элементов в каждой, L-входовые элементы И и ИЛИ, коммутатор и три элемента И-НЕ, причем входы записи режимов блока соединены соответственно с входами «Запись первого, второго и третьего регистров, информационные входы которых поразрядно подключены к соответствующим входам задания режимов блока, информационные входы блока соответственно подключены к первым входам элементов И первой и второй групп и к информационным входам коммутатора, первые L-выходов первого и второго регистров подключены к вторым входам элементов И первой и второй групп соответственно, выходы третьего регистра с первого по L-й соединены с соответствующими управляющими входами коммутатора, (L-H)-e выходы первого, второго и третьего регистров соединены соответственно с первыми входами первого, второго и третьего элементов И-НЕ, вторые входы которых соответственно подключены к выходам элемента ИЛИ, элемента И и коммутатора, выхо- п ды первой и второй групп элементов И соединены соответственно с входами элемента ИЛИ и элемента И, выходы первого, второго и третьего элементов И-НЕ являются выходами блока логической обработки.

0

5

000

1...000 1...1...110

1..

п

011

.001

Хр

м

х,

XtVX,

х,ухгух3

X.VXj

x,vx,v...vx,

1 x,

X

x,

п

Xt п

Xt

x,vx,vx5

fl

xTvx,

х,

Выполнение операции ИЛИ над любыми комбинациями сигналов на входах 21-1-21-L (Выход 29-1)

Получение инверсии любого из сигналов, подаваемых на входы 21-1-21-L (Выход 29-1)

Выполнение операции ИЛИ- НЕ над любыми комбинациями сигналов на входах 21-1-21-L (Выход 29-1)

чэ

&

к

vj

ы

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки массива чисел | 1986 |

|

SU1429107A1 |

| Устройство для упорядочения массива чисел | 1986 |

|

SU1383336A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Устройство для выбора упорядоченной последовательности данных | 1984 |

|

SU1218381A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для сравнения чисел | 1986 |

|

SU1339547A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| Устройство для сортировки двоичных чисел | 1984 |

|

SU1182509A1 |

Изобретение относится к вычислительной технике и может использоваться при построении систем сбора и обработки информации, представленной массивами чисел, например, в цифровых устройствах обработки изображений. Цель изобретения - расширение функциональных возможностей за счет выполнения операции объединения, пересечения и дополнения над L - множествами. Устройство содержит регистр 8, реверсивный счетчик 9, блок памяти 12, блок логической обработки 13, элементы задержки 10 и 11, элемент И 14, группу элементов И 15. Блок логической обработки содержит информационные регистры, элементы И, элемент ИЛИ, коммутатор, элементы И-НЕ. Работа устройства основана на записи в ЗУ единичных признаков наличия конкретного числа в каждом из вводимых массивов по адресу, задаваемому с выхода счетчика, используемого как регистр. Восстановление чисел производится выделением соответствующих стробовых сигналов, осуществляемым за счет фиксации начала отсчета и исключения из серии тактовых импульсов тех по порядку импульсов, числа которых в массиве при записи не присутствовали. Значение чисел массива восстанавливается из линейно нарастающих или убывающих кодов, выделяемых на выходах счетчика. Блок логической обработки вводит дополнительные ограничения на вывод чисел. 1 з.п.ф-лы, 3 ил.

000...000 100...000 010...000 001...000

000 ,..1...000 000...010

0

x x,. x 4

1

Xf XL

x,vx,

X,VX}VX3

Подключение любого из сигналов с входов Х1, XtX3...XL) подаваемых на входы 21-1-21-L, на выход 29-2

Выполнение операции И над любыми комбинациями сигналов на входах 21-1-21-L

10

000. 111.

000. 100. 010. 001 .

.001 .001 .001 .001

,1...000 ,111

X(AXj X.AXjAXjA. .X

X, X,

- (Выход 29-2)

-Получение инверсии любого

-из сигналов с входов 1 i Х3 .. . X

на выходе 29-2

х,

- .

х,

000.

.001 .001

Л...001

Х/.Хг.

4

,

Выполнение операции И-НЕ над любыми комбинациями сигналов на входах 21-1-21-L (Выход 29-2)

&

ы чо

о

X,

Ь

Х5

Подключение любого из сигналов Х1, Хг, X,. ,XL к выходу 29-3

000...1...000

11

000...010 000...001 100...001 010,..001 001-001

Хс

н

X,

Проведение инверсии любого из сигналов л, у л. у А...А| на выходе 29-3

to

xf

м

13

Информация на выходах

000...000 100...000 010...000 001...000

000...001 110...000

1481739

14

Таблица 2

Режим

Вывод чисел из блока 12 Ввод чисел первого массива Ввод чисел второго массива Ввод чисел третьего массива

Ввод чисел L-ro массива

Ввод чисел одного массива одновременно

первый и второй узлы блока 12

Ввод чисел одного массива одновременно

первый, второй и третий узлы блока 12

Ввод чисел одного массива одновременно

во все узлы блока 12

ж

т

к

н

т

м

п

| Устройство для сортировки массива чисел | 1986 |

|

SU1429107A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сортировки информации | 1984 |

|

SU1183956A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-03-10—Подача