1

и в блоки 3 и 4 памяти, а счетчик 9 чтения - при воспроизведении из них. Блоки 3 и 4 памяти, счетчики 8 и 9 и логические элементы 5-7 образуют стек с дисциплиной выборки «первым нришел-пер- 5 вым ушел.

Блок 23 сравнения обеспечивает поразрядное сравнение информации, воспроизводимой из проверяемого блока 67 памяти, с эталонной информацией, поступающей из Q блока 4 памяти слов.

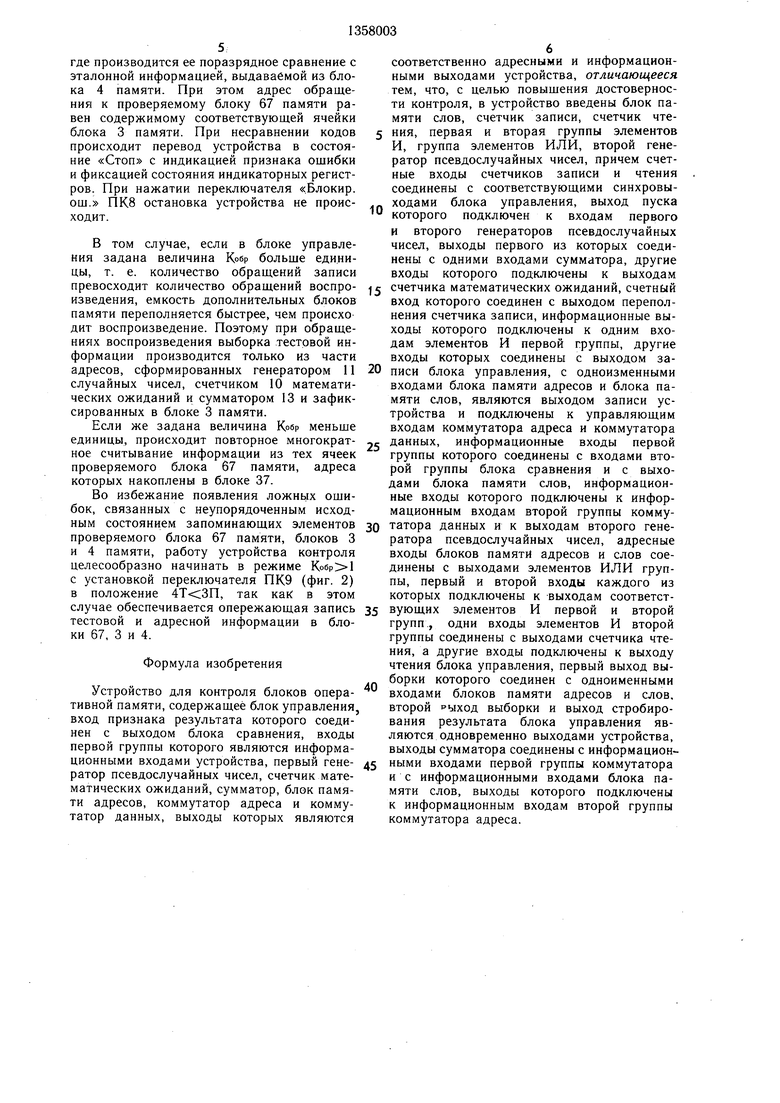

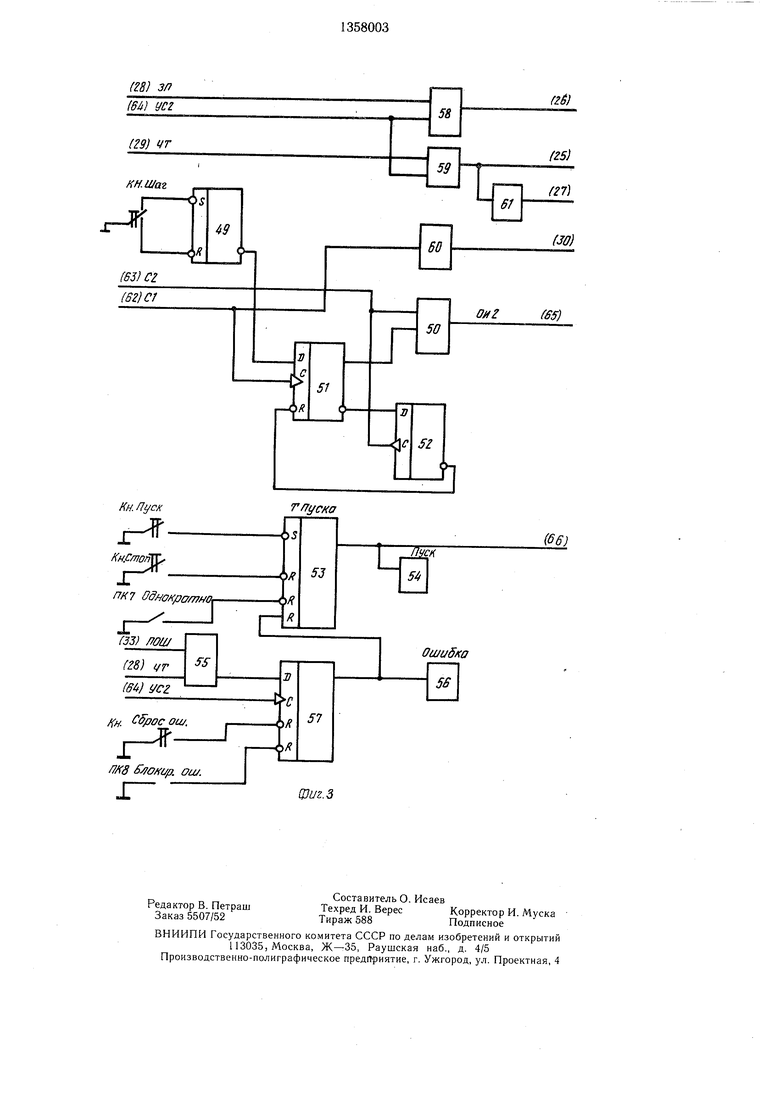

Блок 1 управления вырабатывает последовательность управляющих сигналов, синхронизирующих работу устройства. Схема блока управления обеспечивает выдачу чередующихся обращений записи и воспроиз9 чтения, счетчик 10 математических ожи- 5 ведения к проверяемому блоку 67 памяти. Дании, первый 11 и второй 12 генера-Кратность чередования обращений двух данных типов Кобр., равная отношению числа обращений записи Nsan. к числу обращений воспроизведения Neocn., задается схемой блока управления, состоящей из двоичного 6-разрядного счетчика 39, двух синхронизируемых формирователей, построенных на триггерах 41, 43, 44 и 46 с двумя логическими ко.ммутаторами 2И-ЗИ-ИЛИ 42 и 45, управляемых переключателем триггер 38, счетчик 39, мультиплексор 40, 25 . триггер 41, элемент И-ИЛИ 42, триггерыДанная схема обеспечивает при установ43 и 44, элемент И-ИЛИ 45, триггер 46,ке переключателя в положение стумультиплексор 47, тумблерный регистр 48,пенчатое изменение величины Кобр. в. диапатриггер 49, элемент И 50, триггеры 51-53, зоне от 1 до 1/127 и в положении элемент 54 индикации, элемент И 55,. - в диапазоне от 1 до 127. элемент 56 индикации, триггер 57, элемен- 30 При этом частота обращений F к прове- ты И-НЕ 58 и 59, элементы НЕ 60 и 61, ряемому блоку памяти может меняться в

диапазоне от F до F/128, где Е - частота следования синхроимпульсов (С1, С2), формируемых генератором 34. Период следования синхроимпульсов равен минимальноСмысл проверки блока памяти устройст му времени обращения, допустимому для вом контроля состоит в том, что в ячей- проверяемого блока памяти.

Изобретение относится к вычислительной технике и может быть использовано для контроля в динамическом режиме оперативных запоминающих устройств (ОЗУ) с произвольной выборкой.

Цель изобретения - повышение достоверности контроля.

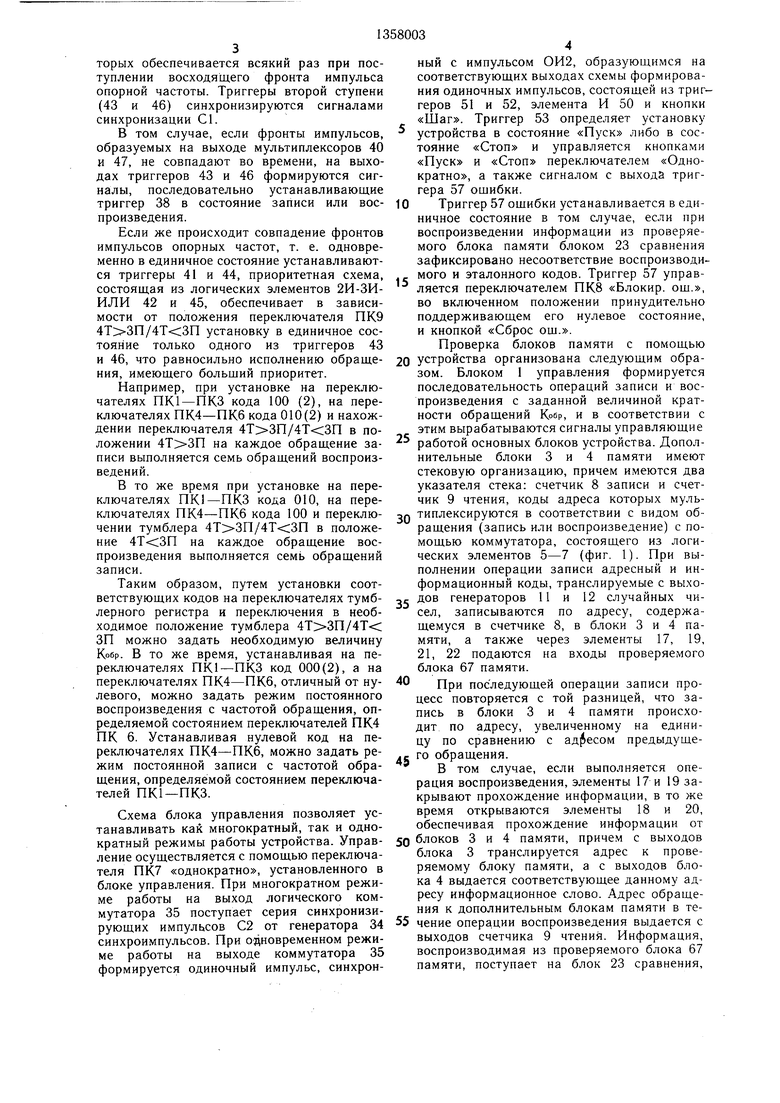

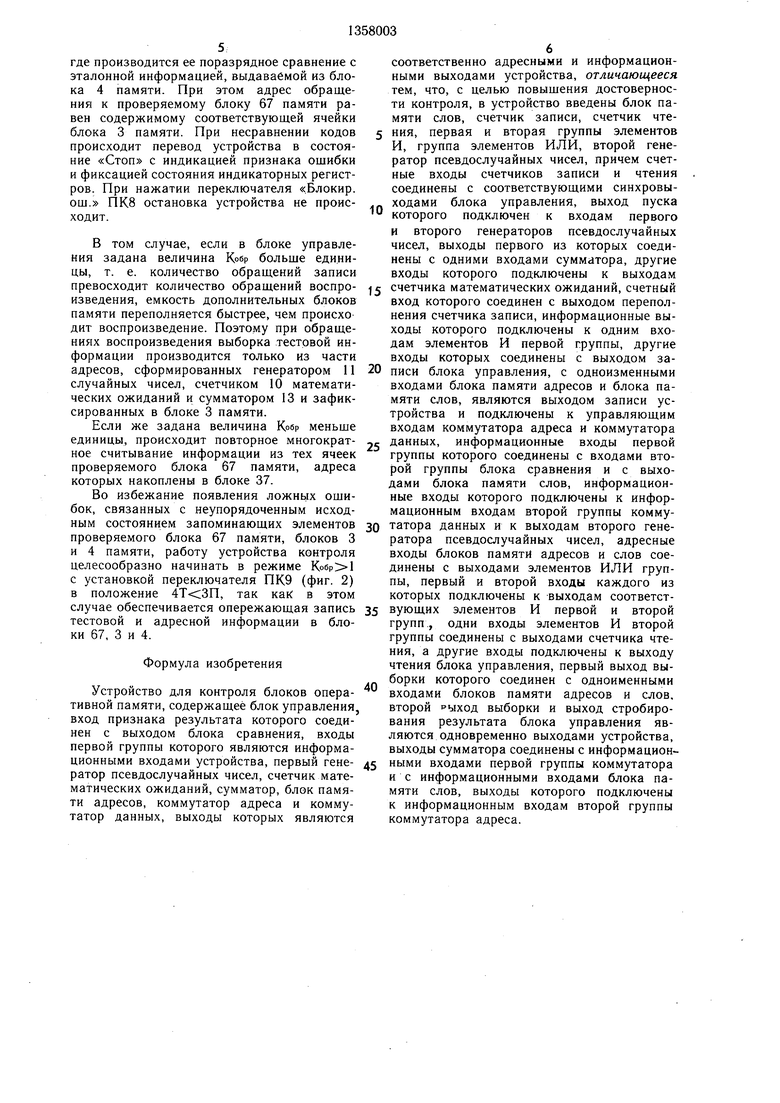

На фиг. 1 представлена схема устройства для контроля блоков оперативной памяти; на фиг. 2 и 3 - схема блока управления.

Устройство (фиг. 1) содержит блок 1 управления коммутатор 2 адреса, блок 3 памяти адресов, блок 4 памяти слов, первую 5 и вторую 6 группы элементов И, элемент ИЛИ 7, счетчик 8 записи, счетчик

торы случайных чисел, сумматор 13, коммутатор 14 данных, элементы НЕ 15 и 16, элементы И 17-20, элементы ИЛИ 21 и 22, блок 23 сравнения, блок 24 индикаторных регистров, выходы 25-32 и вход 33 блока 1 управления.

Блок управления (фиг. 2) содержит г енератор 34 синхроимпульсов, элемент И-ИЛИ 35, элемент JJE 36, элемент И 37,

20

связи 62-66.

Позицией 67 обозначен проверяемый блок оперативной памяти.

Устройство работает следующим образом.

ке с адресами, определяемыми нормальным законом распределения, записываются случайные числа, которые при последующем

На выходе счетчика 39 образуются щесть .опорных частот, которые подаются на входы

воспроизведении сравниваются с числом- 40 мультиплексоров 40 и 47. На эталоном. Формирование адресов, соответст- входы D1 подана серия синхросигналов УС2, вующих нормальному закону распределе- а на входы DO - логическая единица. В ния, осуществляется с помощью генератора зависимости от положения первой и второй 11 случайных чисел, счетчика 10 матема- групп переключателей ПК1-ПКЗ и ПК4- тических ожиданий и сумматора 13 адреса. ПК6 тумблерного регистра 48 выходы муль- Сохранение текущего массива случайных 45 типлексоров 40 и 47 коммутируются с их адресов осуществляется в блоке 3 памяти соответствующими входами, т. е. на выход

мультиплексора подается либо серия синхроимпульсов УС2, либо одна из щести опорных частот с выходов счетчика 39.

, ,..........J ...При нулевом положении переключателей

ных чисел. Сохранение текущего массива прохождение опорных частот через соот- эталонных информационных кодов организо-ветствуюил,ий мультиплексор перекрывается.

К выходам мультиплексоров 40 и 47 подключены входы синхронизируемых формирователей импульсов, служащих для получе- числения следующих адресов обращения в гг ния сигналов управления триггером 38 блоки 3 и 4 памяти возложены на счет- режима работы (триггером записи - вос- чики 8 и 9. При этом счетчик 8 за- произведения). Оба формирователя предс- писи формирует код адреса при записи тавляют собой синхронизированные одновиб- информации в проверяемый блок 67 памяти раторы на триггерах типа D, запуск коадресов. Тестовая информация, записываемая в проверяемый блок памяти, представляет собой последовательность случайных чисел, формируемых генератором 12 случайвано в блоке памяти слов. Функции сохранения текущих значений адресов для обращения к блокам 3 и 4 памяти и выторых обеспечивается всякий раз при поступлении восходящего фронта импульса опорной частоты. Триггеры второй ступени (43 и 46) синхронизируются сигналами синхронизации С1.

В том случае, если фронты импульсов, образуемых на выходе мультиплексоров 40 и 47, не совпадают во времени, на выходах триггеров 43 и 46 формируются сигналы, последовательно устанавливающие триггер 38 в состояние записи или воспроизведения.

Если же происходит совпадение фронтов импульсов опорных частот, т. е. одновременно в единичное состояние устанавливаются триггеры 41 и 44, приоритетная схема, состоящая из логических элементов 2И-ЗИ- ИЛИ 42 и 45, обеспечивает в зависимости от положения переключателя ПК9 4Т ЗП/4Т- ЗП установку в единичное состояние только одного из триггеров 43

10

15

ный с импульсом ОИ2, образующимся на соответствующих выходах схемы формирования одиночных импульсов, состоящей из триггеров 51 и 52, элемента И 50 и кнопки «Шаг. Триггер 53 определяет установку устройства в состояние «Пуск либо в состояние «Стоп и управляется кнопками «Пуск и «Стоп переключателем «Однократно, а также сигналом с выхода триггера 57 ощибки.

Триггер 57 ощибки устанавливается в единичное состояние в том случае, если при воспроизведении информации из проверяемого блока памяти блоком 23 сравнения зафиксировано несоответствие воспроизводимого и эталонного кодов. Триггер 57 управляется переключателем ПК8 «Блокир. ощ., во включенном положении принудительно поддерживающем его нулевое состояние, и кнопкой «Сброс ощ..

Проверка блоков памяти с помощью

и 46, что равносильно исполнению обраще- 20 устройства организована следующим обрания, имеющего больший приоритет.

Например, при установке на переключателях ПК1-ПКЗ кода 100 (2), на переключателях ПК4-ПК6 кода 010(2) и нахождении переключателя 4Т ЗП/4Т ЗП в позом. Блоком 1 управления формируется последовательность операций записи и воспроизведения с заданной величиной кратности обращений Кобр, и в соответствии с этим вырабатываются сигналы управляющие

ложении на каждое обращение за- работой основных блоков устройства. Допол- писи выполняется семь обращений воспроиз-нительные блоки 3 и 4 памяти имеют

ведений.стековую организацию, причем имеются два

В то же время при установке на пере- указателя стека: счетчик 8 записи и счет- ключателях кода 010, на пере-чик 9 чтения, коды адреса которых мульключателях ПК4-ПК6 кода 100 и переклю- n типлексируются в соответствии с видом об- чении тумблера 4Т ЗП/4Т :ЗП в положе-ращения (запись или воспроизведение) с поние на каждое обращение воспроизведения выполняется семь обращений записи.

Таким образом, путем установки соответствующих кодов на переключателях тумб- ,с дов генераторов 1

лерного регистра и переключения в необ--

ходимое положение тумблера 4Т ЗП/4Т ; ЗП можно задать необходимую величину Кобр. В то же время, устанавливая на переключателях ПК1-ПКЗ код 000(2), а на

мощью коммутатора, состоящего из логических элементов 5-7 (фиг. 1). При выполнении операции записи адресный и информационный коды, транслируемые с выхои 12 случайных чисел, записываются по адресу, содержащемуся в счетчике 8, в блоки 3 и 4 памяти, а также через элементы 17, 19, 21, 22 подаются на входы проверяемого блока 67 памяти.

переключателях ПК4-ПК6, отличный от ну- 40 При последующей операции записи процесс повторяется с той разницей, что запись в блоки 3 и 4 памяти происходит по адресу, увеличенному на единицу по сравнению с адресом предыдуще- можно задать ре- ро обращения, с частотой обра- 9 в том слу

левого, можно задать режим постоянного воспроизведения с частотой обращения, определяемой состоянием переключателей ПК4 ПК 6. Устанавливая нулевой код на переключателях ПК4-ПК6, можно задать режим постоянной записи

щения, определяемой состоянием переключателей ПК1--ПКЗ.

случае, если выполняется операция воспроизведения, элементы 17 и 19 закрывают прохождение информации, в то же

Схема блока управления позволяет ус-время открываются элементы 18 и 20,

танавливать как многократный, так и одно-обеспечивая прохождение информации от

кратный режимы работы устройства. Управ-50 блоков 3 и 4 памяти, причем с выходов

ление осуществляется с помощью переключа-блока 3 транслируется адрес к проветеля ПК7 «однократно, установленного вряемому блоку памяти, а с выходов блоблоке управления. При многократном режи-ка 4 выдается соответствующее данному адме работы на выход логического ком-ресу информационное слово. Адрес обращемутатора 35 поступает серия синхронизи-ния к дополнительным блокам памяти в терующих импульсов С2 от генератора 3455 чение операции воспроизведения выдается с

синхроимпульсов. При одновременном режи-выходов счетчика 9 чтения. Информация,

ме работы на выходе коммутатора 35воспроизводимая из проверяемого блока 67

формируется одиночный импульс, синхрон-памяти, поступает на блок 23 сравнения.

ный с импульсом ОИ2, образующимся на соответствующих выходах схемы формирования одиночных импульсов, состоящей из триггеров 51 и 52, элемента И 50 и кнопки «Шаг. Триггер 53 определяет установку устройства в состояние «Пуск либо в состояние «Стоп и управляется кнопками «Пуск и «Стоп переключателем «Однократно, а также сигналом с выхода триггера 57 ощибки.

Триггер 57 ощибки устанавливается в единичное состояние в том случае, если при воспроизведении информации из проверяемого блока памяти блоком 23 сравнения зафиксировано несоответствие воспроизводимого и эталонного кодов. Триггер 57 управляется переключателем ПК8 «Блокир. ощ., во включенном положении принудительно поддерживающем его нулевое состояние, и кнопкой «Сброс ощ..

Проверка блоков памяти с помощью

устройства организована следующим обрадов генераторов 1

-

мощью коммутатора, состоящего из логических элементов 5-7 (фиг. 1). При выполнении операции записи адресный и информационный коды, транслируемые с выхои 12 случайных чисел, записываются по адресу, содержащемуся в счетчике 8, в блоки 3 и 4 памяти, а также через элементы 17, 19, 21, 22 подаются на входы проверяемого блока 67 памяти.

ледующей операции записи проряется с той разницей, что заоки 3 и 4 памяти происхоресу, увеличенному на единивнению с адресом предыдуще- ия, слу

случае, если выполняется опероизведения, элементы 17 и 19 заохождение информации, в то же

где производится ее поразрядное сравнение с эталонной информацией, выдаваемой из блока 4 памяти. При этом адрес обращения к проверяемому блоку 67 памяти равен содержимому соответствующей ячейки блока 3 памяти. При несравнении кодов происходит перевод устройства в состояние «Стоп с индикацией признака ошибки и фиксацией состояния индикаторных регистров. При нажатии переключателя «Блокир. ощ. ПК8 остановка устройства не происходит.

ходами блока управления, выход пуска которого подключен к входам первого и второго генераторов псевдослучайных чисел, выходы первого из которых соединены с одними входами сумматора, другие входы которого подключены к выходам

В том случае, если в блоке управления задана величина Кобр больше единицы, т. е. количество обращений записи

превосходит количество обращений воспро- счетчика математических ожиданий, счетный

изведения, емкость дополнительных блоковвход которого соединен с выходом переполпамяти переполняется быстрее, чем происхонения счетчика записи, информационные выдит воспроизведение. Поэтому при обраще-ходы которого подключены к одним вхониях воспроизведения выборка тестовой ин-дам элементов И первой группы, другие

формации производится только из частивходы которых соединены с выходом заадресов, сформированных генератором 1120 писи блока управления, с одноизменными

случайных чисел, счетчиком 10 математи-входами блока памяти адресов и блока паческих ожиданий и сумматором 13 и зафик-мяти слов, являются выходом записи уссированных в блоке 3 памяти.тройства и подключены к управляющим

Если же задана величина Кобр меньшевходам коммутатора адреса и коммутатора

единицы, происходит повторное многократ--с данных, информационные входы первой

- ....J, - группы которого соединены с входами второй группы блока сравнения и с выходами блока памяти слов, информационное считывание информации из тех ячеек проверяемого блока 67 памяти, адреса которых накоплены в блоке 37.

Во избежание появления ложных ошибок, связанных с неупорядоченным исходные входы которого подключены к информационным входам второй группы коммуным состоянием запоминающих элементов зо татора данных и к выходам второго генепроверяемого блока 67 памяти, блоков 3 и 4 памяти, работу устройства контроля целесообразно начинать в режиме с установкой переключателя ПК9 (фиг. 2) в положение , так как в этом

ратора псевдослучайных чисел, адресные входы блоков памяти адресов и слов соединены с выходами элементов ИЛИ группы, первый и второй входы каждого из которых подключены к выходам соответстратора псевдослучайных чисел, адресные входы блоков памяти адресов и слов соединены с выходами элементов ИЛИ группы, первый и второй входы каждого из которых подключены к выходам соответстслучае обеспечивается опережающая запись 35 вующих элементов И первой и второй тестовой и адресной информации в бло-групп., одни входы элементов И второй

ки 67, 3 и 4.

Формула изобретения

группы соединены с выходами счетчика чтения, а другие входы подключены к выходу чтения блока управления, первый выход выборки которого соединен с одноименными Устройство для контроля блоков опера- входами блоков памяти адресов и слов, тивной памяти, содержащее блок управления, второй рыход выборки и выход стробиро- вход признака результата которого соеди- вания результата блока управления яв- нен с выходом блока сравнения, входы ляются одновременно выходами устройства, первой группы которого являются информа- выходы сумматора соединены с информацион- ционными входами устройства, первый гене- 45 ными входами первой группы коммутатора ратор псевдослучайных чисел, счетчик мате-и с информационными входами блока паматических ожиданий, сумматор, блок памя-мяти слов, выходы которого подключены

ти адресов, коммутатор адреса и комму- к информационным входам второй группы татор данных, выходы которых являютсякоммутатора адреса.

соответственно адресными и информационными выходами устройства, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены блок памяти слов, счетчик записи, счетчик чте- ния, первая и вторая группы элементов И, группа элементов ИЛИ, второй генератор псевдослучайных чисел, причем счетные входы счетчиков записи и чтения соединены с соответствующими синхровы10

ходами блока управления, выход пуска которого подключен к входам первого и второго генераторов псевдослучайных чисел, выходы первого из которых соединены с одними входами сумматора, другие входы которого подключены к выходам

счетчика математических ожиданий, счетный

ные входы которого подключены к информационным входам второй группы коммуратора псевдослучайных чисел, адресные входы блоков памяти адресов и слов соединены с выходами элементов ИЛИ группы, первый и второй входы каждого из которых подключены к выходам соответст вующих элементов И первой и второй групп., одни входы элементов И второй

усг1угтм

сриг.г

61

(JO)

OjfZ

fS5)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля в динамическом режиме оперативных запоминающих устройств (ОЗУ) с произвольной выборкой. Целью изобретения является повышение достоверности контроля. Устройство содержит блок 1 управления, блок 3 памяти адресов, блок 4 памяти слов, счетчик 8 записи, счетчик 9 чтения, счетчик 10 математических ожиданий, первый 11 и второй 12 генераторы случайных чисел, сумматор 13, коммутатор 2 адреса, коммутатор 14 данных, блок 23 сравнения, первую 5 и вторую 6 группы элементов И, элементы ИЛИ 21, 22, элементы И 17-20, элементы НЕ 15, 16. В устройстве реализуется тестовый контроль ОЗУ по алгоритму, заключающийся в том, что в ячейки ОЗУ с адресами, определяемыми нормальным законом распределения, записываются случайные числа, которые при последующем воспроизведении сравниваются с числами-эталонами. Для сохранения текущего массива случайных адресов и чисел используются соответственно блок памяти адресов и блок памяти слов. 3 ил. i (Л со ел 00 со дикацин . ФОТ. 7

Составитель О. Исаев

Техред И. ВересКорректор И. Муска

Тираж 588Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предгтриятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля блоков памяти | 1974 |

|

SU526952A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков памяти | 1977 |

|

SU619968A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-12-07—Публикация

1986-02-12—Подача